# EVALUATING THE POWER OF THE PARALLEL MASC MODEL USING SIMULATIONS AND REAL-TIME APPLICATIONS

A dissertation submitted to Kent State University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

by

Mingxian Jin

August 2004

Dissertation written by

Mingxian Jin

Approved by

| <br>, Chair, Doctoral Dissertation Committee, Member, Doctoral Dissertation Committee |

|---------------------------------------------------------------------------------------|

|                                                                                       |

|                                                                                       |

| Accepted by                                                                           |

| <br>, Chair, Department of Computer Science<br>, Dean, College of Arts and Sciences   |

# TABLE OF CONTENTS

| LIST OF FIGURESvii                              |

|-------------------------------------------------|

| LIST OF TABLESviii                              |

| ACKNOWLEDGMENTSix                               |

| Chapter 1 Introduction1                         |

| Chapter 2 Parallel computational models5        |

| 2.1 Shared-memory based models                  |

| 2.1 Parallel random access machine (PRAM)6      |

| 2.2 Variants of PRAMs9                          |

| 2.2 Network-based models                        |

| 2.3 Bus-based models                            |

| 2.4 Recently proposed general-purpose models    |

| 2.4.1 BSP (Bulk-Synchronous Parallel) model24   |

| 2.4.2 The LogP model27                          |

| 2.4.3. Comparison of the two models             |

| 2.4.4 QSM (Queuing Shared Memory) model         |

| 2.4.5 Summary of relationships among the models |

| Chapter 3 The MASC | C (Multiple Associative | Computing) model |  |

|--------------------|-------------------------|------------------|--|

|--------------------|-------------------------|------------------|--|

| 3.1 The MASC model               | 33 |

|----------------------------------|----|

| 3.2 Properties of the MASC model | 34 |

| 3.3 Previous work on MASC        |    |

| Chapter 4 Timings of the associative operations on the MASC model |    |

|-------------------------------------------------------------------|----|

| 4.1 Introduction                                                  |    |

| 4.2 Motivation for research on timings of MASC                    | 40 |

| 4.3 Broadcast/reduction network                                   | 41 |

| 4.4 Discussion on the basic operations                            | 44 |

| 4.5 Comparison of timings with other models                       | 51 |

| 4.6 Summary                                                       | 54 |

| Chapter 5 Simulations of enhanced meshes with the MASC model | 57 |

|--------------------------------------------------------------|----|

| 5.1 Introduction                                             | 57 |

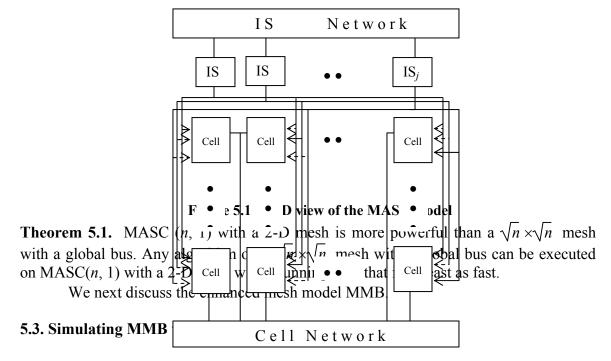

| 5.2 The overview of simulations of enhanced meshes           | 58 |

| 5.3 Simulating MMB with MASC                                 | 60 |

| 5.4 Simulating BRM with MASC                                 | 65 |

| 5.5 Simulating MASC with enhanced meshes                     | 71 |

| 5.6 Simulation between MASC and RM                           | 74 |

| 5.7 Summary                                                  | 78 |

| Chapter 6 Associative computing in real-time processing      | 81 |

| 6.1 Introduction                                             | 82 |

| 6.2 Real-t  | time processing                             | 85  |

|-------------|---------------------------------------------|-----|

| 6.3 Air tra | affic control                               | 88  |

| 6.3.1       | System constraints                          | 88  |

| 6.3.2       | Task characteristics                        | 89  |

| 6.3.3       | The worst case environment of ATC           | 90  |

| 6.3.4       | ATC tasks                                   | 91  |

| 6.3.5       | Task examples                               | 91  |

| 6.4 ASC s   | solution to the ATC problem                 | 97  |

| 6.4.1       | Static schedule solution                    | 97  |

| 6.4.2       | Analysis of the solution                    | 101 |

| 6.5 Comp    | elexity theory and current practice for ATC | 102 |

| 6.6 Summ    | nary                                        |     |

| Chapter 7 Reconsideration of SIMD computation         | 107 |

|-------------------------------------------------------|-----|

| 7.1 SIMD vs. MIMD                                     | 107 |

| 7.2 Advantages of associative SIMDs or ASC            | 109 |

| 7.3 Possible MIMD approaches to solve the ATC problem | 114 |

| 7.4 Difficulties of an efficient MIMD solution        | 119 |

| 7.5 Discriminating simulation of ASC with BSP         | 122 |

| 7.6 Summary                                           | 126 |

| Chapter 8 Final summary and future work |

|-----------------------------------------|

|-----------------------------------------|

| Appendix A Glossary | <br> | <br> |

|---------------------|------|------|

|                     |      |      |

|                     |      |      |

| Bibliography13 | \$5 |

|----------------|-----|

|----------------|-----|

# LIST OF FIGURES

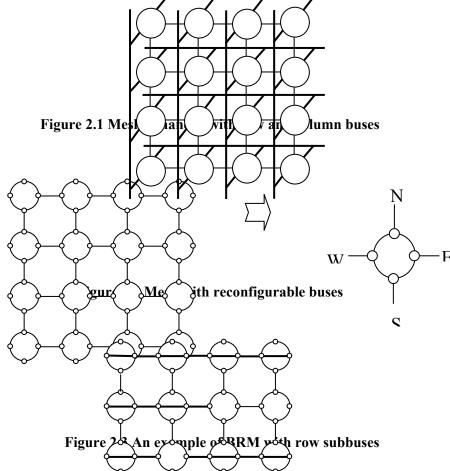

| Figure 2.1 Mesh enhanced with row and column buses                                         |

|--------------------------------------------------------------------------------------------|

| Figure 2.2 Mesh with reconfigurable buses                                                  |

| Figure 2.3 An example of BRM with row subbuses                                             |

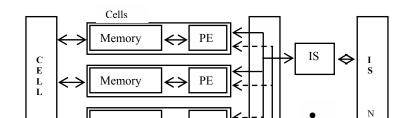

| Figure 3.1. The MASC model                                                                 |

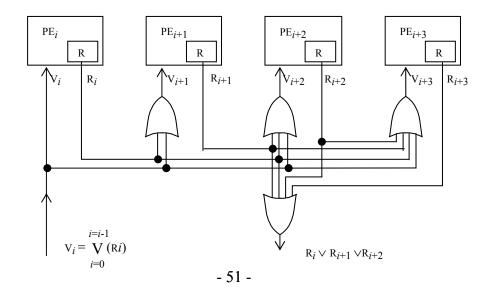

| Figure 4.2 A 4-PE resolver with at most an 1-gate delay from any input to any output43     |

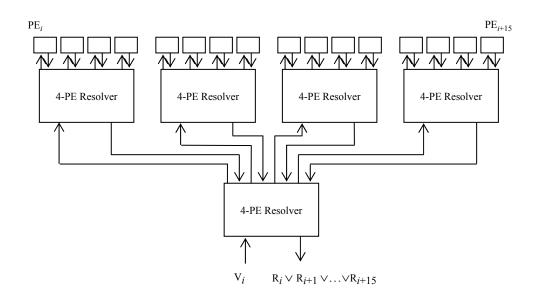

| Figure 4.3 A 16-PE resolver with at most a 3-gate delay from any input to any output43     |

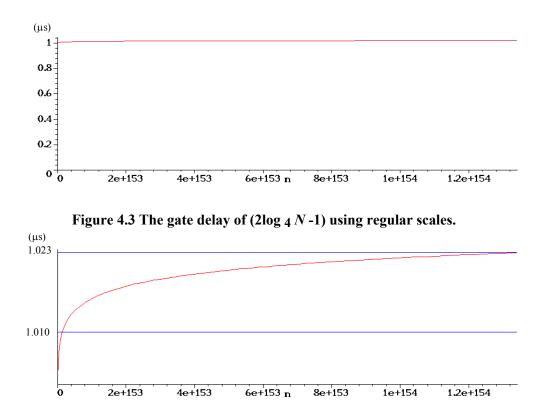

| Figure 4.4 The gate delay of (2log 4 N -1) using regular scales46                          |

| Figure 4.5 The gate delay of (2log4 N-1) with the vertical axis using logarithmic scales47 |

| Figure 5.1 A 2-D view of the MASC model                                                    |

| Figure 5.2 An $8 \times 4$ mesh of processors partitioned with the butterfly topology77    |

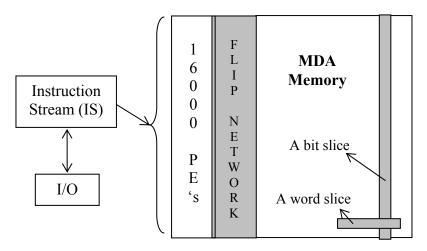

| Figure 6.1 A possible AP architecture for ATC                                              |

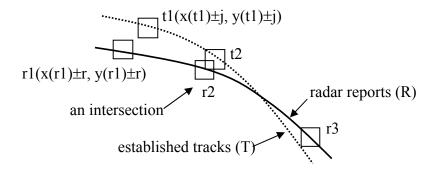

| Figure 6.2 Track/Report correlation                                                        |

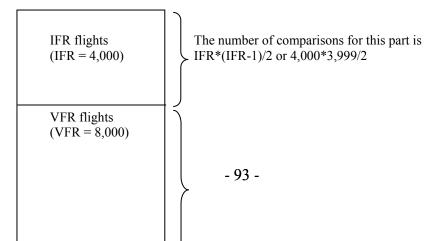

| Figure 6.3. The worst-case number of operations for conflict detection in MP96             |

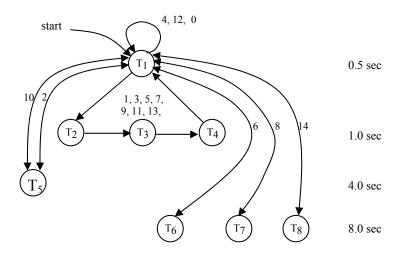

| Figure 6.4. The AP ATC schedule                                                            |

# LIST OF TABLES

| Table 2.1 Degree and diameter of the network topologies.      | 20 |

|---------------------------------------------------------------|----|

| Table 2.2 Simulations between PRAMs and BSP                   | 26 |

| Table 2.3 Simulation results of BSP, LogP and QSM             | 31 |

| Table 4.1 Summary of the timings of the basic MASC operations | 55 |

| Table 6.1 Statically scheduled solution time                  | 99 |

#### ACKNOWLEDGMENTS

I would like to deeply thank Dr. Johnnie W. Baker for his continuing enthusiasm and support for my Ph.D. study. He has been the advisor for my research work throughout these years and also the mentor for my professional career development. Without his encouragement and guidance, this dissertation would be impossible.

I would also like to thank my dissertation committee members for their willingness to serve on the committee and their valuable time.

My special thanks will go to many people who have helped me at various stages of this work – Will Meilander, Kenneth Batcher, Robert Walker, Jerry Potter, Arden Ruttan, Sue Peti, and Anne Martyniuk. In particular, Professor Will Meilander has contributed invaluable information for the real-time part of this dissertation. He has read through the part and provided many useful comments.

Finally, I would like to express my thanks to my husband Chengwei Liu and my children Xilin, Kevin, and Joyce for their support and patience so that I can make a dream come true.

# EVALUATING THE POWER OF THE PARALLEL MASC MODEL USING SIMULATIONS AND REAL-TIME APPLICATIONS (145 pages)

Director of Dissertation: Johnnie W. Baker

The Multiple Associative Computing (MASC) model is a generalized associative-style parallel computation model that was developed at Kent State University in 1990s. It provides a complete paradigm that can be used for both special-purpose and generalpurpose parallel computation. The primary focus in this research is to evaluate the power of the MASC model and to provide a better understanding of it. This work consists of three parts. The first part is to justify the timing assumptions for the basic associative operations of the MASC model in order to establish a firm theoretical foundation for the MASC model. The associative operations are used extensively in MASC algorithms. The second part creates simulations between the MASC model and well-known parallel enhanced mesh models. The simulations of the enhanced mesh models provide an efficient method for converting algorithms designed for enhanced meshes to the MASC model. The third part involves using the ASC model (i.e. MASC with one instruction stream or an associative SIMD computer) to provide an efficient polynomial time solution to the real-time Air Traffic Control problem. However, this type of real-time problem is currently considered to be unsolvable in polynomial time using a MIMD computer (i.e. a multiprocessor). Since the MIMD model of parallel computers is generally believed to be more powerful than the SIMD model due to the fact of MIMD's

asynchronous execution, the preceding anomaly indicates that this belief needs to be reconsidered.

# Chapter 1

#### Introduction

The Multiple Associative Computing (MASC) model is a generalized associativestyle parallel computation model that was developed at Kent State University. Motivated by the STARAN computer built by Goodyear Aerospace in the early of 1970s, the MASC model was formally proposed by J. Potter and J. Baker et. al. in [99] in 1994. Prior to this, an architectural version of the model with one instruction stream named ASC was introduced in [98] in the early of 1990s. But the formal proposal in [99] defines and describes the MASC model systematically, and it especially emphasizes the version of the model with multiple instruction streams. The MASC model applies the concept of associative computing to support not only data parallelism but also control parallelism. Thus it provides a complete paradigm that can be used for special-purpose and generalpurpose parallel computation. It is a model that is easy to program, highly scaleable and currently buildable. The MASC model supports efficient algorithms for a wide range of problems and can be supported on a wide variety of computer platforms with a relatively simple programming language. Since MASC is a strictly synchronous model that supports SIMD computation but allows multiple instruction streams, it is also called a multiple SIMD or MSIMD model. Therefore, it is a hybrid data-parallel/control-parallel computation model. In contrast to a number of other parallel models proposed in the past few decades, the MASC model possesses certain associative properties such as constant

time broadcasting, constant time global reduction operations, and constant time associative search. These associative properties have made it possible to solve some realtime problems in an especially efficient manner.

In order to further evaluate the power of the MASC model and give a better understanding of this model, we have conducted the extensive research on this model. The work presented in this dissertation consists of three parts. The first part is to justify the timings assumed for the basic associative operations of the MASC model to build a solid fundamental theoretical background for associative properties assumed for MASC. These associative properties have been widely used in MASC algorithm design and complexity analysis. Our detailed timing justification for the MASC basic operations is not only based on their hardware implementation in the STARAN, the architectural ancestor of the MASC model, but is also based on comparison with timings of basic operations for other well-established models such as PRAM and bus-based architectures.

The second part of our work is the simulations between the MASC model and enhanced meshes. Enhanced meshes are attractive parallel computational models that have received a lot of attention from researchers in the past. We create three simulation algorithms to simulate between the MASC model and two classes of enhanced meshes, namely, MMB (Meshes of Multiple Broadcasting) and BRM (Basic Reconfigurable Meshes). In particular, a constant time simulation algorithm using MASC to simulate MMB is developed. Simulations between MASC and RM (Reconfigurable Meshes), a general case of BRM, are also explored. We show that these two models are dissimilar. Neither of them can simulate the other efficiently due to their distinguishing features. Our work in this part provides an effective way to understand the power of the MASC model in terms of the comparative power with the popular enhanced mesh models. In particular, the constant time MASC simulation of MMB enables algorithms designed for this enhanced mesh model to be transferred to the MASC model with the same running time.

The third part of our work involves using MASC with one instruction stream (called ASC) to solve real-time problems. It is shown that an efficient polynomial time solution to a real-time problem for Air Traffic Control can be obtained. However, these type of real-time problems are currently considered unsolvable in polynomial time using a MIMD computer, which is generally believed to be the more powerful type of parallel computers. The existence of a feasible polynomial time solution for the ATC problem using an associative SIMD leads us to identify and analyze some of the most important features of both associative SIMDs and MIMDs with regard to real-time processing. Our work raises serious questions concerning the validity of the general belief that MIMDs are more powerful than SIMDs and can solve any problems as efficiently as SIMDs. Based on this fact, it is suggested that the importance and efficiency of SIMD computation should be reconsidered.

This dissertation is organized into seven chapters. First, Chapter 2 surveys a number of parallel computation models and the related research on simulations and comparisons among them. Chapter 3 gives an overview of the MASC model, its properties, and previous work on the model. Chapter 4 addresses justification of timings of the basic associative operations on the MASC model, based on a theoretical analysis of one possible implementation and comparison with timings of basic operations for other

well-established computational models. Chapter 5 presents simulations of the enhanced meshes, e.g., MMB, BRM, and RM models, with the MASC model, and the reverse simulations, respectively. Chapter 6 discusses how to use an ASC, i.e., the MASC with one instruction stream, computer to solve a real-time problem for Air Traffic Control, in polynomial time. Chapter 7 extends our results in Chapter 6 to reevaluate the computation power of SIMD computers by comparing it with that of MIMD computers, in terms of capabilities of solving real-time problems. Chapter 8 gives the final summary and discusses some work planned for the future.

# Chapter 2

## **Parallel Computational Models**

A parallel computational model is an abstract description of parallel computers with specific type of architecture and specific properties. Such a model extracts the essential features of these computers and provides a framework for researchers to study these computers independent of any real machines. Using a model, algorithms can be developed and analyzed without involving any of unimportant implementation details related to a particular machine. A parallel model has significant impact on designing both parallel systems and parallel algorithms. Therefore, developing effective models for parallel computation at proper levels of abstraction is fundamental in parallel processing. A good model must correctly reflect essences of the parallel computers while balancing briefness, accuracy, and broad applicability.

A number of models for parallel computation have been proposed and studied in the past two decades. According to different communication schemes between processors, models are usually divided into two categories, shared-memory based and interconnection network based. In the first two sections of this chapter, we give a survey of models to provide a background for the later chapters. A few popular models are emphasized. Also, adding a certain number of buses to a particular model gives another category of parallel models, i.e., bus-based models, which we will discuss in Section 2.3. Then, in Section 2.4, we study three recently proposed parallel models. These models are based on either shared-memory or networks and have been developed for generalpurpose parallel computation.

#### 2.1. Shared-Memory Based Models

A shared memory model consists of a collection of processors communicating by reading and writing to locations in a shared memory that is equally accessible by all processors. In some cases, the processors may have local memory that can be used for local storage and computational uses, but often only shared memory is available. Its primary advantages are ease of use and portability of algorithms.

# 2.1.1. Parallel Random Access Machine (PRAM)

Primary among all parallel models has been the Parallel Random Access Machine (PRAM) model, in which processors execute synchronously or in *lock-step* and communicate by reading and writing to locations in the shared memory. Lock-step means all processors are synchronized in every single step. (Although asynchronous PRAM was also defined later, synchronous PRAM is usually assumed to be the default.) This is contrast with *bulk-synchronous* model in which processors are synchronized in specific step and we will discuss in later sections.

The PRAM model was first proposed as a general-purpose model for parallel computation by Fortune in 1978 [42]. A PRAM consists of p conventional sequential processors,  $P_1$ ,  $P_2$ ,... $P_p$ , all of which are connected to a large shared random access memory, M. Each processor has a private, or local, memory for its own computation. All communication among the processors is performed via the shared memory. In one step,

each processor can access one memory location or execute a single RAM operation. The processors synchronously execute the same program through the central main control. The processors generally operate on different data but perform the same instructions. Hence, the model is sometimes called *shared-memory single instruction stream, multiple data stream* (SM SIMD) machine. A PRAM time step is defined as consisting of three phases: *read phase*, in which the processor may read from a shared memory cell; *computation phase*, in which the processor does some calculations; and *write phase*, in which the processor memory cell.

Based on restrictions on shared memory access, PRAMs are classified as three categories: EREW PRAM, CREW PRAM and CRCW PRAM, where E is for exclusive, C for concurrent, and R for read, W for write. ERCW PRAM is usually not considered, since a machine with enough power to support concurrent writes should be able to support concurrent reads. Here, we recall three important varieties of CRCW PRAMs, which depend on how concurrent writes are handled. The **common** CRCW PRAM allows concurrent writes only when all processors that attempt write the same value to the same location at the same time. The **arbitrary** CRCW PRAM allows an arbitrary processor to succeed. The **priority** CRCW PRAM allows only the processor with the highest (or lowest) priority to succeed. The priority CRCW PRAM is the most powerful among these variants, and the EREW PRAM is the weakest. Simulations and further relationships between different PRAM models have been explored by researchers. They can been found in [11,52,57].

The PRAM model is an idealized model and draws its power from its simplicity. The model ignores the algorithmic complexity of communication-related issues and allows the algorithm designer to focus on the fundamental computational difficulties of the problem. Until recently, there were few attractive alternatives for the PRAM. As a result, numerous efficient algorithms have been developed for this model [10,11,57]. On the other hand, it has been criticized for years for being too high level and failing to accurately model realistic parallel machines. In particular, the PRAM model has been faulted for completely failing to model memory contention, communication bandwidth limitations, and synchronization cost of parallel processing that are typical for asynchronous computation. PRAM uses synchronous computation and a simplified method for communications that often underestimates the cost and avoids the details of having to specify a particular communication network and to design appropriate routing algorithms for asynchronous network.

One way to avoid these criticisms of PRAMs is to develop methods that allow the execution of PRAM algorithms on more realistic machines. The problem is to simulate a CRCW PRAM on a realistic parallel machine, namely, one with distributed memory and an interconnection network of fixed degree. According to the summary in [52], this central problem can be generally separated into three fundamental sub-problems that can be solved individually. The three sub-problems are the concurrent access problem, the memory management problem, and the routing/interconnection problem. We denote (n, m) PRAM to be a PRAM with n processors and m memory locations. In a (n, m)-CRCW PRAM, a processor may request concurrent access to any of m memory locations. The

first problem is to service these multiple concurrent requests correctly and as efficiently as possible on hardware that disallows concurrent access, namely, an EREW PRAM. The solution to the second problem of memory management, is to simulate a (n, m)-EREW PRAM on a machine with M memory modules in which the processors are fully connected, so that any processor can communicate with any other in constant time. This machine is called *Module Parallel Computer* (MPC). It allows us to focus on how to layout memory so that the amount of module contention is minimized for any given set of n requests to be serviced. The solution to the third problem is to specify a fixed-degree interconnection network (referred as a *Bounded Degree Network* (BDN)) and a routing algorithm that will allow servicing of all requests from n PRAM processors with minimum slowdown. This step is used to precisely measure the communication cost for a specific PRAM algorithm. It is assumed that memory management scheme has handled the memory requests already before the router takes control.

The authors of [52] have given the results for each of the above steps both by deterministic simulation (mapping processors deterministically) and by randomized simulation (mapping processors randomly). These results indicate the simulation cost of PRAM on currently more realistic asynchronous parallel machines in a general way.

# 2.1.2. Variants of PRAMs

Instead of simulating PRAMs on more realistic machines, a considerable amount of effort has been spent to propose and differentiate between variants of PRAMs in the past. In this section, we study several models developed from the original PRAM model.

#### • Local-Memory PRAM (LPRAM)

The *Local-Memory PRAM* (LPRAM) was proposed by Aggarwal in [7]. It focuses on exploring communication complexity of asynchronous PRAMs. Based on a CREW PRAM, it models the communication delay and computation time separately. At each step, the processors do one of two things as follow. In a communication step, a processor can write, or read a word from global shared memory. Or, in a computation step, a processor can perform an operation on at most two words that are present in its local memory. Usually, a communication step is viewed as taking several times longer than a computation step. This communication delay is also called *latency*. Assuming one computation step takes unit time, LPRAM defines a parameter *l* that specifies the length of time taken by one communication step. The total running time of an algorithm is defined as the sum of the computation and communication times.

The parameter *l* is the latency for shared memory access. An LPRAM with *p* processors can be simulated on a butterfly with the same number of processors, with each computation step being simulated in constant time and each communication step requiring O(log *p*) time; thus here  $l = O(\log p)$ . Similarly, an LPRAM can be simulated on a 2-D mesh with each communication taking time  $l = O(\sqrt{p})$ . The work results in the equivalence of the LPRAM model with communication cost  $l = \log p$  and the butterfly model and the equivalence of the LPRAM model with  $l = \sqrt{p}$  and the 2-D mesh model.

In [7], the authors present several problems solved on an LPRAM. For example, two  $n \times n$  matrices can be multiplied in  $O(n^3 / p)$  computation time and  $O(n^2 / p^{2/3})$ communication delay using p processors (for  $p \le n^3 / (\log 3/2 n)$ ). Also, sorting n words takes  $\Theta((n \log n) / p)$  computation steps and  $\Theta((n \log n) / (p \log (n / p)))$  communication delay.

Obviously, if a communication step takes time *l*, then the total running time of an algorithm is  $T + l \times C$ , where *T* is the number of computation steps and *C* is the number of communication steps. Thus, the total running time for the above matrix multiplication is  $\Theta(n^3/p + ln^2/p^{2/3})$ . It is further known that, when  $n = \Omega(lp^{1/3})$ , the algorithm is computation-bound (i.e., computation time dominates) and will be running more efficiently. Thus, for  $l = \log p$ , *n* should be  $\Omega(p^{1/3} \log p)$ , and for  $l = \sqrt{p}$ , *n* should be  $\Omega(p^{5/6})$ . The *n*-word sorting problem can be analyzed in a similar manner. These indicate how a problem can be executed efficiently on an LPRAM with communication delay when the input size is different; the value of *l* dictates how large a problem should be in order to obtain maximum efficiency.

#### • Block PRAM (BPRAM)

The *Block PRAM* was introduced by the same authors that proposed LPRAM in [6]. It is essentially another version of LPRAM since it uses the same parameter l for communication delay. Besides that, it takes into consideration that a processor may read or write a block contiguous locations from or to the shared memory in one step. Such an operation is charged l + b time, where l is the startup time or latency and b is the length of the block. An access to a location of the local memory is assumed to take unit time. Any number of processors may access shared memory simultaneously, but the blocks that are being accessed need to be disjoint.

BPRAM captures spatial and temporal locality of reference for the design of more efficient algorithms. Algorithms for some problems such as matrix transposition and multiplication have been designed to take the reduced cost of block access in order to obtain a better running time.

#### • **PRAM**(*m*)

PRAM(m) is a variant of the PRAM where the shared memory size is limited to m. It has been pursued by many researchers in [76,63,2,3,4,125]. Unlike the unbounded shared memory size in the unrestricted PRAM, the small size m of the shared memory relative to the number p of processors restricts the number of messages that can be concurrently accessed. The reason to develop this model is that many existing parallel machines allow a relatively low level of **c**ommunication throughput (CT for short) while many parallel algorithms developed appear to need a relatively high level of CT. There appears to be a typical gap between some algorithmic needs and the capability of many computer systems concerning CT. Since increasing CT may be very expensive, it makes sense to use the PRAM(m) model to quantitatively analyze CT and how the efficiency of an algorithm can be affected by a limited communication channels.

In [76], a case is studied in which the size *n* of a problem is relatively big compared to the number *p* of processors. With PRAM(*m*), the lower bound of running time for concrete problems such as the list reversal, sorting, finding unique elements, convolution, or universal hashing is established as  $\Omega(n/\sqrt{mp})$ . Also, a nearly optimal algorithm for the list reversal problem is derived. Since such a problem can be solved in O(1) time on a PRAM with *n* processors and *n* shared memory locations, this indicates that it may be very inefficient to implement a high-CT algorithm on a low-CT parallel system. It may further imply that parallel computers with a low-CT level will be handicapped as general purpose computing systems.

The PRAM(*m*) model has been compared to other limited communication bandwidth models such as BSP and QSM. Both BSP and QSM will be discussed in Section 2.4 in more details and are two typical general-purpose parallel models with parameters to measure the communication limitation. BSP deals with message passing and barrier synchronization while QSM is focused on shared memory and concerns memory contention. By using an aggregate parameter *m* as the global communication restriction, QSM(*m*) is a variant of the QSM model that can only handle at most *m* global messages in one step [3,63]. It is shown that one step of the CRCW PRAM(*m*) can be simulated on the QSM(*m*) in time O(*p*/*m*) provided  $m = O(p^{1-\varepsilon})$  and  $0 < \varepsilon < 1$ . Even if every processor in the QSM(*m*) model is given the entire input in advance, the CRCW PRAM(*m*) is faster than the QSM(*m*) by a factor of  $\Omega(\frac{p \log m}{m \log p})$ . Consider the only difference of latency parameter *L* between QSM and BSP, this simulation can be transferred to BSP(*m*). (BSP(*m*) is defined in the same way as a variant of BSP. )

# • Phase PRAM

The PRAM assumes that processors execute in synchronously, which causes difficulties in mapping PRAM algorithms onto realistic asynchronous MIMD machines. Supporting a synchronous model such as PRAM on an asynchronous machine is inherently inefficient since the ability of the machine to run asynchronously is not fully exploited and there is a (potentially large) overhead in synchronizing processors as part of each instruction. These observations have resulted in some asynchronous PRAM models being proposed [34,48,90] as variants of the PRAM. Unlike PRAM, the processors of an asynchronous PRAM run asynchronously, i.e., each processor executes its instructions independently of timing of the other processors. There is no global clock.

The *Phase PRAM* is one such model that is defined by Gibbons in [48]. It considers that a computation is a series of global, program-wide phases in which the processors run asynchronously separated by synchronization steps that involve all the processors. The processors cannot begin their next phase until the synchronization step has completed. Consider a phase that is followed by a synchronization step among a set *S* of processors. The cost of a synchronization step is B(p), a non-increasing function of *p* where p = |S|. The running time of a program is defined to be the maximum over all processors of the completion time for its local program.

This definition leads to different time complexity for some algorithms for Phase PRAM, when compared to their PRAM versions. For example, the prefix sum computation runs on a *n* EREW PRAM in O(log *n*) time in binary tree fashion. By inserting a synchronization step after each PRAM read or write step, an EREW Phase PRAM algorithm for prefix sum rums in O(*B* log *n*) time. Generally, a PRAM algorithm running in time *t* using *p* processors can be simulated by a Phase PRAM algorithm using  $p_0$  processors and running in time  $t+B(p_0)s$ , where *s* is the number of synchronization steps, can be simulated by a Phase PRAM using  $p < p_0$  processors in time  $O((p_0/p)t + B(p)s)$ .

## • XPRAM

*XPRAM* is an extension of the PRAM family that was proposed by L. G. Valiant in [123,124]. It is essentially an early version of the BSP model that we shall discuss later. An XPRAM with p processors performs its execution in *supersteps*. In each superstep each processor executes a number of local instructions and sends or receives some messages that implement global read or write instructions. In an execution of a superstep, suppose that processor i performs  $a_i$  local operations, sends  $b_i$  messages and receives  $c_i$  messages from other processors. Assume that each local operation takes unit time, while typically each global operation takes time  $g \ge 1$ . Let  $r_i = g^{-1}a_i + b_i + c_i$ . Then if  $t = \max\{r_i\}$ , the runtime of this superstep is considered to be that of  $(\lceil t/L \rceil)L$ standard global operations, or time  $(\lceil t/L \rceil)Lg$ , where L is the periodicity parameter All the processors know whether a superstep is complete or not at the end of each period of Lglobal operations. Within each such period, however, there is no synchronization among the processors.

A primary goal for XPRAM is to capture communication costs by charging a higher cost for global reads or writes than PRAM so as to make its predicted asynchronous communication cost more realistic than PRAM does. It embodies the principle of *bulk-synchrony*, that is, the processors should be barrier synchronized at regular time intervals. A time interval is defined to be long enough for several packets to be transmitted between a pair of processors.

Simulations of EPRAMs (EREW PRAM) and CPRAMs (CRCW PRAM) with XPRAM are given in [124]. These simulations have been shown to be *optimally efficient*.

This means that there is a fixed constant such that, if an algorithm is running on the simulating model with cost  $c_1$  and is running on the simulated model with cost  $c_2$ , the difference between  $c_1$  and  $c_2$  is less than this fixed constant.

# • QRQW PRAM

The *Queue-Read Queue-Write (QRQW) PRAM* model was proposed by Gibbons et al. in [50]. This model solves the memory access contention issues in the PRAM by adding queues for each of processors as queued-read and queued-write.

There are two QRQW models defined. One is the SIMD-QRQW PRAM, running in the lock-step style on SIMD machines. The other is QRQW PRAM, running in bulksynchronous on MIMD machines. A single step of a PRAM consists of a read operation, a compute operation, and a write operation. The maximum contention of the step is the maximum, over all locations x, of the number of processors reading x or the number of processors writing x. As a boundary case, a step with no reads or writes is defined to have maximum contention of 1. The time cost for a step with maximum contention k is k. The QRQW-PRAM model consists of a number of processors, each with its own private memory, communicating by reading and writing locations in a shared memory. The processors execute a sequence of synchronous steps, each consists of three substeps: processor *i* reads  $r_i$  shared memory locations (read); processor *i* performs  $c_i$  local RAM operations (compute); processor i writes  $w_i$  shared-memory locations (write). Concurrent reads and writes to the same location are permitted in a step. In the case of multiple writes to a location x, an arbitrary write to x succeeds in writing the value in x at the end of the step. If its maximum contention is k, let  $m = \max\{r_i, c_i, w_i\}$ , then the time costs

for the step is  $\max\{m, k\}$ . The time of a QRQW PRAM algorithm is the sum of the time costs for its steps.

A *p*-processor QRQW PRAM algorithm running in time *t* can be simulated on a *pt*-processor SIMD-QRQW PRAM in time O(*t*) [50]. In addition, simulations between other variants of the PRAMs and QRQW PRAM have been discussed. From CRCW PRAM to QRQW PRAM, there exists  $\Omega(\log n)$  time cost; and from SIMD-QRQW PRAM, there exists  $\Omega(\sqrt{\log n})$  time cost. Hence, relationships between these models are established as follow, EREW PRAM  $\leq$  SIMD-QRQW PRAM  $\leq$  QRQW PRAM  $\leq$  CRCW PRAM where " $\leq$  " is read as "is weaker than".

Comparison and simulations of QRQW PRAM to BSP (discussed in Section 2.4.1) have been given in [50,3]. A *p*-processor QRQW PRAM algorithm (or SIMD-QRQW PRAM algorithm) running in time *t*, where *t* is polynomial in *p*, can be simulated on a ( $p/\log p$ )-component BSP(g, L) model in ( $t\log p$ ) time with high probability, when *g* is a constant and *L* is  $\Theta(\log p)$ .

## • Broadcasting with Selective Reduction (BSR)

Another shared memory model is *Broadcasting with Selective Reduction* (BSR), which is also basically an extension of the PRAM. It was first proposed by Akl in [8,9,11]. It consists of N processors numbered 1, 2, ..., N, sharing M memory locations  $u_1, u_2, ..., u_M$ . The model has all of the features of CRCW PRAM. In particular, during the execution of an algorithm, several processors may read from or write into the same memory location simultaneously, such that each processor accesses at most one location. However, an additional type of memory access is permitted in BSR, namely, a

BROADCAST instruction, by means of which *all* processors may access *all* memory locations at the same time for the purpose of writing. At each memory location, a subset of the incoming broadcast data is selected and reduced to one value (using an appropriate reduction operator such as minimization) and this value is finally stored in the memory location. The selection process is carried out as follows. Along with each data item  $d_i$ , a tag  $t_i$  is also broadcast, while each memory location  $u_i$  is associated with a limit  $l_j$ . A selection rule  $\xi$  (e.g., <) is used to test the condition  $t_i \xi l_j$ : if the latter is true, then  $d_i$  is selected for reduction; otherwise,  $d_j$  is rejected. This is done simultaneously for all broadcast data  $d_i$  with  $1 \le i \le N$ , and all memory locations  $u_j$  with  $1 \le j \le M$ .

The BSR model is a PRAM augmented with an additional form of concurrent access to shared memory. The feature that distinguishes BSR from other models is the so-called BROADCAST instruction that is executed in three constant-time phases:

- 1. Broadcast phase, in which each processor broadcast a data item

- 2. *Selection* phase, in which a subset of the broadcast data is selected for each memory location if they meet a predefined selection rule

- 3. *Reduction* phase, in which the subset of data, selected in Phase 2, is reduced to one value and stored in that location

The BROADCAST instruction is assumed to require only O(1) time, so it is equivalent to *M* CW instructions of a PRAM with the same number of processors and memory locations, since this kind of memory access in the PRAM would require O(M)time. This shows that BSR is strictly more powerful than the PRAM. Possible implementations of BSR, e.g., the particular memory access unit (MAU) design, have been discussed in [9,11]. They include using memory buses, using a mesh of tree and using a circuit for sorting and prefix computation. With this model, a variety of problems have been solved in constant-time, such as prefix sums, element uniqueness, sorting, maximal subsequence in one or two dimensions, and convex hull. However, algorithms on PRAM for these problems usually require non-constant time.

#### 2.2. Network-based models:

Another way for processors to communicate is via direct links connecting them, with no shared memory. Instead, the memory locations are more realistically distributed among the all processors as local memory belonging to individual processors. If any processor wishes to access the local memory of another processor, it has to route the data via a network. Depending on the structure and topology, there are different classifications of the interconnection networks. A detailed description can be found in [11]. In Table 2.1, we list them based on their two primary criteria, i.e., degree and diameter. *Degree* is the maximum number of neighbors of a processor, and *diameter* is the longest distance between all pairs of processors in a given network, where the distance of a pair of processors is the number of links on the shortest path between the pair. The network models can also be either synchronous or asynchronous. These two groups of network models are very distinct and have different characteristics. The types of algorithms designed for these groups are also very distinct and involve different issues.

| Network               | Degree      | Diameter              |

|-----------------------|-------------|-----------------------|

| Linear Array          | 2           | O( <i>N</i> )         |

| Mesh                  | 4           | O(N <sup>1/2</sup> )) |

| Tree                  | 3           | O(log N)              |

| Mesh of Trees         | 6           | O(log N)              |

| Pyramid               | 9           | O(log N)              |

| Shuffle-Exchange      | 3           | O(log N)              |

| Hypercube             | O(log N)    | O(log N)              |

| Cube-Connected Cycles | 3           | O(log N)              |

| De Bruijn             | 2 <i>d</i>  | K                     |

| Star                  | <i>m</i> -1 | O( <i>m</i> )         |

#### Table 2.1 Degree and diameter of the network topologies

#### 2.3 Bus-based models

Among network-based models listed in last section, the mesh model is a particularly attractive model for parallel computation. Its advantages include regular structure and simple interconnection topology, which make it particularly suitable for VLSI implementation. However, a serious disadvantage of the mesh is its large diameter. For example, a  $\sqrt{n} \times \sqrt{n}$  mesh takes  $\Theta(\sqrt{n})$  time to route a data item in the worst case.

In order to overcome this disadvantage, researchers have considered a variety of enhancements for the mesh model. One such approach is to add buses and give the processors the ability to broadcast data over buses. Such meshes are bus-based models and we referred them to as *enhanced meshes*. At any given time, only one processor is allowed to broadcast an item on a bus. The data will be read by all of the remaining processors on that bus in O(1) time.

The two types of electronic buses used for enhanced meshes are *fixed buses* and *reconfigurable buses*. A mesh can be enhanced with a fixed bus using the single global bus model in which all processors are connected to a single bus [11,31]. Another fixed mesh model is the *mesh with multiple buses* (MMB) in which the basic mesh architecture is enhanced with row and column buses (see Figure 2.1) [27,28,32,92,100,101,112]. At each step, broadcasts can occur along one or more rows or else along one or more columns. The row and column buses cannot be used in the same step. The *reconfigurable bus* models allow buses to be created dynamically on the mesh while an algorithm is executed (Figure 2.2) [25,39,78,85,86,88,91,114,127]. The number, connection, and length of these buses are not fixed and are created by the algorithm as needed. Let each processor have four ports, referred to as N, S, E, and W. By setting local connections

between pairs of such ports, several disjoint subbuses can be established. The model that allows up to two disjoint pairs of ports to be connected is referred to as the *general reconfigurable mesh* (RM).

If every processor in a RM may set at most one connection involving one of the reconfigurable pairs  $\{N, S\}$  (N, S) (N, S)

Simulations between enhanced meshes and CRCW PRAM has been given in [71]. The authors show that a  $\sqrt{n} \times \sqrt{n}$  MMB can be simulated by a CREW PRAM(n, m) in O(1) time with O(n) extra memory. Similarly, if  $\alpha$  denotes the inverse Ackermann function, they show that a  $\sqrt{n} \times \sqrt{n}$  BRM can be simulated by a Common CRCW PRAM(n, m) with O $(\alpha(n))$  extra time and O(n) extra memory.

Another way to augment a network-based model is using an *optical bus*. An optical bus allows multiple processors to broadcast data on the bus simultaneously and each data can have one or more destinations. These models provide a much wider bandwidth for data transmission than the electronic bus. This capability provides a completely new technique for parallel algorithm design. Since it is not related to our

current research work, additional details are omitted in this dissertation and can be found in [11, 70].

# 2.4. Recently proposed general-purpose models

Both shared-memory models and network-based models have their advantages and disadvantages. The shared-memory model has its major drawback in the fact that there is no way to assign costs for communication between processors that enables accurate performance prediction of realistic machines. The network-based model seems to be better suited to measuring both computation and communication costs. However, it also has two drawbacks. First, it is difficult to describe and analyze algorithms for the network models, in which routing steps are asynchronous and can involve congestion, making prediction of running time difficult. Second, the network model depends heavily on the particular topology under consideration. Different topologies may require completely different algorithms to solve the same problem. This prevents algorithms being general enough and software being portable enough across a wide range of architectures. As a result, no single parallel model has yet dominated parallel computation in the way that the von Neumann model has dominated sequential computation so far.

In recent years, there have been a few models for general-purpose parallel computation proposed [35,49,123,124]. Among these, BSP [123,124] and LogP [35] have attracted most attention from researchers. We discuss them first, and then describe QSM, another general-purpose parallel model [49]. Finally, we give comparison among the three models, along with their relationships to the PRAMs.

#### 2.4.1 BSP (Bulk-Synchronous Parallel) Model

The BSP model was first put forward by Valiant [123]. It is suggested as a candidate for a universal model for parallel computation. It arguably provides a robust model on which to base the future development of general-purpose parallel computing systems [29,47,62,104,123]. A BSP computer consists of three major components:

- 1. A set of processor-memory pairs, each performing processing and/or memory functions

- 2. A communication network that transmits messages between processor-memory pairs in the manner of point-to-point.

- 3. A mechanism performing efficient barrier synchronization of all or a subset of the processors at regular intervals.

A time step is defined to be the time required for a single local operation such as addition or multiplication on local data values. The performance of a BSP computer is predicted using the following three parameters:

- *p*: the number of processors

- *I*: the time interval for synchronization (i.e., minimal number of time steps between successive synchronization operations)

- *g*: the ratio of the total number of local operations performed by all processors in one second to the total number of words delivered by the communication network in one second

A computation consists of a sequence of parallel *supersteps*. During a superstep, each processor is allocated a task consisting of some combination of local computation

steps, message transmissions and (implicitly) message arrival from other processors. Each superstep is followed by a global check (barrier synchronization) to determine whether the superstep has been completed by all the components. If synchronized, the machine proceeds to the next superstep. Otherwise, the next period of a fixed number of time units is allocated to the unfinished superstep. In this model, the tasks of computation and communication are separated. The basic task of the communication router is to realize arbitrary *h*-relations, which means that each component in a superstep sends and receives at most *h* messages. Varied algorithms that have been developed for the BSP model, including broadcasting, prefix sum, and sorting, can be found in [47,123].

The BSP model has been advocated to be a bridging model between software and hardware in parallel machines, that is, between abstract models for algorithm design and realistic parallel architectures. This approach is supported in [123,124] by providing both efficient simulations (on an average) of the BSP model on hypercube networks (synchronous) and of the EREW PRAM (synchronous) model on the BSP. In particular, it is shown that the EREW PRAM can be simulated efficiently with logarithmic slowdown on the BSP model. It is also shown that the BSP can be simulated efficiently with a constant slowdown on the multiport hypercube (on an average). In the multiport hypercube with *p* nodes, each node can receive a message on each of its log *p* incoming wires and route them along the appropriate outgoing wires in constant time (with the constraint that at most one message can be sent along each outgoing wire). In order to hide the latency, synchronization, and memory granularity overheads occurring in the simulation, the choice  $l = \Theta(\log p)$  and  $g = \Theta(1)$  can be used in the BSP.

above simulation between EREW PRAM and BSP, the most powerful model of PRAMs, CRCW PRAM, is also simulated on BSP. It is shown in [123,124] that if  $v = p^{1+\varepsilon}$  for any  $\varepsilon > 0$ , a *v*-processor CRCW PRAM can be simulated on a *p*-processor BSP machine with  $l \ge \log p$  in time O(*v*/*p*) (where the constant multiplier grows as  $\varepsilon$  diminishes.) Table 2.2 gives average time costs of simulating the PRAM family using BSP.

| Simulated<br>Model | Simulating<br>Model | Simulation<br>Slowdown              | Ref.      |

|--------------------|---------------------|-------------------------------------|-----------|

| EREW PRAM          | BSP(g, l)           | $\geq \max(\log p, l/g)$            | [123,124] |

| QRQW PRAM          | BSP(g, l)           | $\geq \max(\log p, l/g)$            | [50]      |

| CRCW PRAM          | BSP(g, l)           | $\geq \max(p^{1+\varepsilon}, l/g)$ | [123,124] |

## Table 2.2 Simulations between PRAMs and BSP

# 2.4.2 The LogP Model

Proposed by D. Culler et al. in 1993 [35], the LogP model is a model of a distributed-memory multiprocessor in which processors communicate by point-to-point messages. It uses several parameters to describe the performance characteristic of the interconnection network, but does not specify the structure of the network. These parameters in the LogP model are:

- *L*: an upper bound on the *latency*, or delay, incurred in transmitting a message containing a word (or small number of words) from its source module to its target module

- *o*: the *overhead*, the length of time that a processor is engaged in sending or receiving of each message. During this time, the processor cannot perform other operations

- *G*: the *gap*, the minimum time interval between successive message sending or successive message receiving at a processor. Thus, the reciprocal of *G* corresponds to the available per-processor communication bandwidth

- **P**: the number of processor/memory modules

In a LogP model, at each step a processor can be either *operational* or *stalling*. When operational, a processor can execute an operation on local data, send a message, or receive a message. Conceptually, for each processor there is an output register temporarily holding a message that is to be submitted to the communication network. The preparation of a message for submission requires *o* time units. Once submitted, a message is accepted by the network, possibly with some time elapsed, eventually delivered to its destination processor. Between the submission and acceptance of a message, the sending processor is assumed to be *stalling*. When a submitted message is accepted, the submitting processor reverts to the operational state.

Although the exact delivery time of a message is unpredictable, the model guarantees that the message arrives at its destination at most L time steps after its acceptance. In order to capture network capacity limitations, the model requires that any time there are no more than  $\lfloor L/G \rceil$  messages in transit for the same destination (*capacity constraint*). Therefore, the parameter G corresponds to the reciprocal of the maximum message injection (hence reception) rate per processor that the communication network can sustain, while parameter L provides an upper bound on network latency when the system is operating within capacity.

Algorithms such as broadcasting and summation have been developed for the LogP model [35,64,62]. These algorithms are substantially different from those developed for the PRAM model and others. For example, the single item-broadcasting problem can be optimally solved in the LogP model by using a Fibonacci-type broadcasting tree. Most of the described algorithms are quite involved and require low-level handling of messages.

#### 2.4.3 Comparison of the two models

For the BSP and LogP models both, the communication capabilities of the machine are summarized by a few parameters that broadly capture the bandwidth and latency properties. However, there are significant differences between the two models. For BSP, its fundamental features are global barrier synchronization and the routing of arbitrary message sets. For LogP, it lacks explicit synchronization but imposes a more constrained message-passing style to keep the load of the underlying communication network below a specified capacity limit. Intuitively, BSP offers a more convenient abstraction for algorithm design and programming, while LogP provides better control of machine resources.

Comparisons and evaluations between the two models have been made in [29,62,104]. In [29], a variant of LogP that disallows the so-called stalling behavior is considered. The authors create cross simulations between the two models showing their equivalence in algorithmic design when using asymptotic analysis. A non-stalling LogP(*L*, *o*, *G*, *P*) algorithm can be simulated on BSP(*l*, *g*) with slowdown O(1+g / G + l/L). When  $l = \Theta(L)$  and  $g = \Theta(G)$ , the slowdown is constant. On the other hand, a BSP

superstep involving at most *w* local operations per processors and the routing of an *h*-relation can be simulated in non-stalling LogP with worst-case time O(w + (Gh + L)S(L, G, p, h)). Here S(L, G, p, h) is a function of *L*, *G*, *p*, *h* with the value of O(1) when  $h = \Omega(p^{\varepsilon} + L \log p)$  and  $O(\log p)$  otherwise. This indicates that, when the bandwidth and latency parameters have the same value in both models, BSP can simulate LogP with constant slowdown and LogP can simulate BSP with at most logarithmic slowdown. Hence, within the asymptotic limits, BSP and non-stalling LogP can be viewed as closely related variants within the bandwidth-latency framework for modeling parallel computation. BSP seems somewhat preferable due to its greater simplicity and portability, and slightly greater power.

Recently, the authors of [104] improve the above results to the stalling LogP model. A non-stalling LogG algorithm can be simulated deterministically efficiently on BSP with slowdown l/L. However, for a stalling LogP, any deterministic step-by-step simulation of LogP on BSP can have arbitrary large slowdown and there is no deterministic step-by-step simulation of stalling LogP on BSP that is efficient.

It has also been shown that the two models can be implemented with similar performance on most point-to-point network [29,35,62,123]. BSP could outweigh the advantages by more convenient programming abstraction and better software portability. On the other hand, BSP assumes special hardware support to synchronize all processors at the end of superstep. This may not be available on many parallel machines, especially in the generality where not multiple arbitrary subsets of the processors can synchronize.

Instead, LogP does all synchronization by messages, although at a higher cost but more realistically.

#### 2.4.4 QSM (Queuing Shared Memory) Model

Instead of message passing, the QSM (Queuing Shared Memory) model [49,104] is based on shared memory. It employs the QRQW strategy mentioned in Section 2.1.2 and has been further extended towards a general-purpose parallel model. It provides one more parameter,  $g (\geq 1)$ , to reflect the limited communication bandwidth on most parallel machines. Here g is the communication bandwidth gap, i.e., the rate at which processors can perform local operations divided by the rate at which the processors can perform inter-processors or processor-memory communication. Instead of charging the time cost for a step as max(m, k) as a QRQW PARM does, it charges the time cost as follows. Let  $m_{op} = \max\{c_i\}, m_{rw} = \max\{1, \max_i \{r_i, w_i\}\}$  in one step (defined as the same as QRQW PRAMs). The time cost for the step is max{ $m_{op}, g^* m_{rw}, k$ }.

Besides dealing with memory contention as QRQW PRAM does, QSM also accounts for limited communication bandwidth while providing the shared-memory abstraction. This QSM model is intended to take advantages of shared-memory and serve as a bridging model by providing efficient simulations on both the BSP, and the LogP [49,104]. The results are included in the summary of next section.

### 2.4.5 Summary of relationships among the models

Table 2.3 summarizes the relationships among all of the above three models, where l and g are parameters for BSP; L and G are parameters for LogP; G is also assumed for QSM; and p is the number of processors assumed for all of the models.

| Simulating Model<br>Simulated<br>Model | BSP                       | LogP(stalling)                                | QSM                                            |

|----------------------------------------|---------------------------|-----------------------------------------------|------------------------------------------------|

| BSP                                    |                           | $O(\log 4 p + (L/G) \log 2 p)$<br>[104]       | $O(\left\lceil G \log p/l \right\rceil)$ [49]  |

| LogP<br>(nonstalling)                  | O(1+g/G+l/L)<br>[29, 104] | 1                                             | $O(\left\lceil G \log p/L \right\rceil)$ [104] |

| QSM                                    | $O((l/G) + G\log p)$ [49] | $O(\log^4 p + (L/G)\log^2 p + G\log p)$ [104] |                                                |

Table 2.3 Simulation results of BSP, LogP and QSM

## Chapter 3

## The MASC (Multiple Associative Computing) Model

As summarized in last chapter, a number of parallel computation models have been proposed during past decades. Even though a few of them are claimed to work for general parallel computation, none of these models have been efficiently suited to capture associative/SIMD computation well. This is because none of these models have been defined with strict synchronous execution and instruction-level associative properties. Due to broadcast, SIMD computation is very fine-grained and it usually intermingles computation and communication. This feature has not been well captured by other models either. On the other hand, associative SIMD computers have existed since 1970s. They have been used efficiently to solve many problems in various fields. In order to accurately describe associative SIMD computation performed in these computers, the MASC model was proposed by Baker and Potter at Kent State University [99].

In this chapter, we introduce a formal definition of the MASC model and its properties. The original information for this part can be found in [99]. We give them here for the purpose of completion of presenting our research work. Following the definition of the MASC model and its properties, we discuss previous related work on the model.

## 3.1. The MASC model

The MASC (stands for Multiple ASsociative Computing) model is a generalized associative-style computational model for parallel computation. Motivated from the associative computers STARAN and ASPRO that were successfully built by Goodyear Aerospace in the early of 1970s and 1980s, this model has been developed at Kent State University to be a practical model. The MASC model applies the concept of associative computing to support not only data parallelism but also control parallelism. Thus it provides a complete paradigm that can be used for general-purpose parallel computation. It is a model that is easy to program, highly scaleable and currently buildable. Essentially, the MASC model is a multiple SIMD (or MSIMD) type model that operates synchronously. In the MASC model, one or more instruction streams are allowed. Each of these instruction streams is sent to a unique set in a dynamic partition of processing elements (PEs). This allows a task currently in execution to be partitioned into multiple tasks using control parallelism. The associative feature of the model allows data in the local memories of processors to be located by content rather than by address.

As shown in Figure 3.1, the MASC model consists of an array of processing elements (PEs) and one or more instruction streams (ISs). A PE essentially acts as an ALU (Arithmetic and Logic Unit) in a conventional computer, as it does not store any copy of a program, neither decoding nor executing the program independently. Each PE, paired with its local memory, is called a *cell*. (In this thesis, we exchange to use PEs and cells when there is no conflict involved.) The array of MASC machine with *n* PEs and *j* ISs is written as MASC(n, j). Normally, *j* is expected to be much smaller than *n*. Each PE is capable of performing local arithmetic, logical operations, and the other usual functions of a conventional processor other than issuing instructions. There are three real or virtual networks; namely, a PE network used for communications among PEs, an IS network used for IS communications, and a broadcast/reduction network between ISs and PEs used for communication between an IS and a set of cells.

#### Figure 3.1 The MASC model

#### 3.2. Properties of the MASC model

A detailed description of the MASC properties can be found in [99]. Here we briefly list them as a summary.

## Cell properties

A cell is composed of a PE and its local memory. Each PE can only access its own local memory and shares no memory with other cells. PEs may obtain data stored in other cells either from the IS broadcast network or from the (synchronous) cell network.

## IS properties

An IS is logically a processor with a bus connection to each cell. Each IS has a copy of the program being executed and issue an instruction to the cells that listen to by broadcasting. Each cell listens to only one IS at any given time and initially all cells listen to the same IS. A cell can switch to another IS in response to commands from the current IS. A cell can is active, inactive, or idle. An active cell executes the program issued from the IS to which it is currently assigned while an inactive cell listens to but does not execute these instructions. An idle cell contains no data needed. All idle cells are managed by a special IS and may be reassigned to some IS later. An IS can instruct any of its inactive cells to become active again. By issuing multiple instruction streams simultaneously, the MASC model supports control parallelism in a synchronous manner.

### Associative properties

Assuming the word length is considered to be a constant, the MASC model supports the global reduction operations of OR and AND of binary values and of maximum and minimum of integer or real values for each IS and its active PEs in constant time. Additionally, the MASC model supports a constant time associative search (assuming the word length is a constant) due to data in the local memories of processors to be located by content rather than by address. The cells whose data values match the search pattern are called *responders* and the unsuccessful ones are called *non-responders*. The IS can activate either the responders or the non-responders. Each IS can select (or "pick one") arbitrary responder from the set of active cells in constant time. This IS can also instruct the selected cell to broadcast a data item on the bus and all other cells listening to this IS receive this value in constant time.

Following this chapter, Chapter 4 will be dedicated to analyze why these associative operations can be justified to take constant time.

#### 3.3. Previous work on MASC

A large amount of research work has been done for the MASC model. It has involved in multiple research projects such as developing programming techniques, designing MASC algorithms, model simulations, associative instruction implementation, etc.

A declarative associative language called ASC has been implemented for MASC(n,1) on many platforms including Goodyear's STARAN, Goodyear/Loral/Martin-Marietta's ASPRO, WaveTracer, and Thinking Machine's CM-2, and provides true portability for parallel algorithms[98,99]. In addition, an efficient ASC simulator has been implemented on both PCs and workstations running UNIX. It provides an efficient and easy way to design programs for algorithms that primarily utilize data parallelism while retaining the MASC associative properties.

A wide range of different types of algorithms and several large programs has been developed, analyzed, and implemented using ASC language. Some examples of algorithms are as the following. In [98], an optimal algorithm is given for a minimal spanning tree for an undirected graph. In [13,14], MASC versions of different convex hull algorithms have been designed and analyzed; they have optimal average costs. In [37], a MASC string matching algorithm is given that supports variable length "don't care" symbols (VLDC), using MASC with one IS and a linear network. This algorithm has the same lowest cost as established by other well-known parallel algorithms (using EREW PRAM). In addition, it has the unique feature of identifying all continuation points after each "don't care" character. More than the above algorithms, many other algorithms have also been analyzed in various application fields such as graph

algorithms, image processing, database management programs, compiler optimization, and air traffic control task processing [98,99,102, 82,83,84].

Previous MASC simulations include simulation of PRAM with MASC [117,119] and self-simulation [118,119]. Let MASC( $n_ij$ ) denote a MSC with n PEs and j ISs and PRAM(n, m) denote a PRAM with n processors and m shared memory locations. Without a cell network, MASC(n, j) can simulate priority CRCW PRAM(n, O(j)) in constant time with high probability. Also, MASC(n, 1) can simulate priority CRCW PRAM(n, O(j)) in constant time ocustant time when m is a constant number. Using both network algorithms and ISs to move data, MASC(n, j) can simulate priority CRCW PRAM(n,m) in O(min {n/j, m/j, route(n)}) with high probability, where route(n) is the average time for a general network routing. The self-simulation ability of MASC also allows the model to support a virtual machine with more PEs and ISs than are actually available. MASC(n, j) can simulate MASC(N,J) in O(N/n + J) extra time and with O(N/n + J) extra memory, where  $N \ge n$ and  $J \ge j$ . This has established that MASC algorithms are highly scaleable.

Implementation of associative processing and associative operations at the instruction-level has also been explored in [126,129,131]. Using field-programmable logic device (FPLDs), the authors of [126] designed an initial version of an associative processor based on the earlier the STARAN computer but being updated with modern design practices. The design consists of an associative array of 8-bit RISC PEs, operating in byte-serial fashion with one IS. It can execute assembly language code produced by a machine-specific back-end compiler. Furthermore, experiments on implementing associative instructions including associative search and responder resolution have been

shown in details in [131]. The authors of [129] have explored how to implement ASC in regard with scalability. The research work on the hardware implementation has provided very useful information about building the MASC machine using modern VLSI hardware design technology.

Chapter 4

Timings for Associative Operations on the MASC Model

# 4.1. Introduction

As mentioned in Chapter 3, a large amount of research work has been undertaken for the MASC model. However, it has been long noticed that some of the research on the MASC model has identified certain important issues regarding the cost assigned to basic associative MASC operations such as the broadcast and reduction operations. Both the accuracy of the cost assigned to these operations and its fairness with respect to the costs assigned on other parallel models are extremely important, as they determine the accuracy of the comparison between MASC and other models. Likewise, the accuracy and the fairness are essential in determining the ability of MASC to efficiently support applications in different areas, both for programming and complexity analysis of algorithms. In making fair cost assignments, it is necessary to consider the theoretical asymptotic rate of increase in the cost that occurs as the data size increases. However, it is equally important to also consider how these operations can be implemented in hardware and the running time of the implementations of these operations. The theoretical asymptotic rate of increase, together with the running times for hardware implementations can be used to produce graphs that project feasible running time for an operation on data sets of varying size. When this graph is bounded above by a small constant even when the number of processors exceeds what is considered to be feasible in the foreseeable future, we explore the option of assigning a constant running time to these basic MASC operations.

In this chapter, we investigate these issues based on the implementation details of Goodyear's STARAN, which is the architectural ancestor of the MASC model. Its broadcast/reduction network that was designed by K. Batcher [18,19,21,23] is the basis of our work in this chapter. We will discuss and analyze comparative fairness for the timings of certain basic operations on the MASC with respect to those on other parallel models.

This chapter is organized as follows. Section 4.2 presents motivation for the research on timings of MASC. Section 4.3 describes the hardware implementation from STARAN to support these basic operations. Section 4.4 discusses the individual operations based on the implementation facts. Section 4.5 compares the costs of these basic operations on other models and addresses the issue of what costs should be assigned to MASC when it is compared (using simulations) to the related models. The last section is a summary.

## **4.2. Motivation for research on timings of MASC**

When we assume that the word length is considered to be a constant, the MASC model supports the following important constant time operations for an IS:

- Broadcasting an instruction stream or a data item to the set of PEs listening to the IS

- Global reduction of a binary value stored in each active PE using logic OR or AND

- Global reduction of an integer (or real) value stored in each active PE using

maximum or minimum

• Associative search to find the cells whose data values match the search pattern (called responders) or do not match the search pattern (called non-responders)

- The AnyResponder operation to determine if there is any existing responder after an associative search

- The PickOne operation to select (or "pick") an arbitrary responder from its set of

### active PEs

These basic operations are fundamental to support the associative style of computing. With more advanced research on MASC involving in algorithm complexity analysis, especially comparative to other parallel models, the MASC timings, in particular, with those involving constant time operations have drawn more attention and been questioned. While these constant time assumptions were initially viewed as "self-evident", it is now important to provide justification for them. The correctness of the timings assigned to each of these operations depends on both possible hardware implementations and comparative fairness with respect to other parallel models. While other hardware implementations are possible, we will establish the feasibility of implementing a bit-serial broadcast/reduction network that support these operations. Also, we will analyze the fairness of the costs assigned to these operations with respect to the costs assigned on other well-accepted models such as RAM, PRAM, and bus-based architectures. We will discuss these topics in the following sections.

## **4.3.** Broadcast/reduction network

In this section, we take a close view on a possible hardware implementation of the broadcast/reduction network based on the STARAN computer [18,19,80,107], which is the architectural motivation for the MASC model. The STARAN was an associative SIMD computer with 512 to 4096 PEs, depending upon the size of a particular installation. The STARAN was built in the early 1970's and the ASPRO [74], its architectural descendent, was built in 1980's by Goodyear Aerospace. Currently, the ASPRO is produced by Martin-Marietta and is used by the U.S. Navy. Their hardware implementation of associative operations through the broadcast/reduction network provides a possible implementation for these basic associative operations on the MASC model.

The broadcasting/reduction network on the STARAN is constructed using a group of resolver circuits [23,18]. A *N*-PE resolver consists of *N* PEs labeled PE<sub>0</sub>, PE<sub>1</sub>, ..., PE<sub>*N*-1</sub> and each PE<sub>*i*</sub> has a responder bit R<sub>*i*</sub> that is equal to 0 or 1. The resolver is designed to be able to tell each PE whether or not any earlier PE has a responder bit equal to 1. Thus for each *i*, it computes  $V_i = R_0 \lor R_1 \lor R_2 \lor ... \lor R_{i-1}$ , where  $\lor$  is the logic-OR operator and  $0 < i \le N$ . The resolver also sends  $V_N$  to the control unit to tell it whether or not any responder bits are set to 1. A 4-PE resolver is illustrated in Figure 4.1.

In practice, by using the parallel prefix idea, a resolver for *N* PEs can be built as a  $\log_4 (N)$ -level tree of 4-PE resolvers. Each leaf represents a PE and the PEs are partitioned into groups of 4 PEs, which are fed into the first level of 4-PE resolvers. A reduction operation is executed by sending the signals down the tree to the PE leaves and then back up to the root of the tree to obtain the final result, while accumulating partial results in middle. Obviously, the delay from any input to any output is at most (2  $\log_4 N$ -1) gates. A 16-PE resolver tree is shown in Figure 4.2.

#### Figure 4.1 A 4-PE resolver with at most an 1-gate delay from any input to any output

## 4.4. Discussion on the basic operations

In this section, we discuss the timings on the individual basic MASC operations given in Section 4.2.

We consider broadcasting first. Broadcasting on bus-based architectures provides a fast way to transmit data between processors that are far apart. The assumption that an arbitrary subset of broadcasts on a bus-based architecture can occur in constant time, regardless of the number of processors or the length of buses, has been generally accepted in the literature [5,25,27,31,32,71,72,75,79,85,92,100,101,112,113]. This provides consistency among researchers in the field and is supported by experimental evidence even for very large architectures by today's standards [77,96]. For example, in today's architectures with at most tens of thousands of processors, the time to broadcast a data item over a bus is usually no more than that to perform a basic operation such as an addition by a sequential processor. Hence it can be bounded within one or a few machine cycles [25,96]. This constant time assumption for broadcasting greatly simplifies calculation of running times of algorithms and comparison of various models without loss of prediction accuracy.<sup>1</sup>

Based on the preceding paragraph, we assume the timing for a broadcast on the MASC model from an IS to its PEs to be constant. On the MASC model, broadcasting is used to send an instruction stream from an IS to its PEs and transmit data between these PEs. Broadcasting a bit or a word on the MASC model is performed through the broadcast network.

Practically, the broadcast network may be implemented as a separate network from the reduction network yet with the same structure (like in the STARAN), or they may share the same network. It is easy to observe that it takes  $\log_4 N$  gate delay for a bit to travel from the root of the tree network to the *N* PE leaves at the bottom. Recall that the time required for broadcasting on a bus-based architecture increases linearly with respect to the bus length and the number of the processors. However, the time required for broadcasting using a tree-based network is logarithmic, so it increases asymptotically slower than when using a bus-based architecture.