### NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

1505

CR-161732

#### **FINAL REPORT**

# EVALUATION OF ADVANCED MICROELECTRONIC FLUXLESS SOLDER-BUMP CONTACTS FOR HYBRID MICROCIRCUITS

(NASA-CR-161732) EVALUATION OF ADVANCED MICROELECTRONIC FLUXLESS SCLUER-BUMP CONTACTS FOR HYBRID MICROCIRCUITS Final Report (Applied Technology) 144 p HC A07/MF A01 CSCL 09C G3/33

NU1-22283

Unclas 42140

Prepared For

GEORGE C. MARSHALL SPACE FLIGHT CENTER

MARSHALL SPACE FLIGHT CENTER

ALABAMA 95812

In Response To

**CONTRACT NAS 8-31496**

**June 1976**

# **Applied Technology**

A Division of Itek Corporation

645 Almanor Avenue, Sunnyvale, California 94086 (408) 732-2710

## NASA CONTRACTOR REPORT

NAS 8-31496

# EVALUATION OF ADVANCED MICROELECTRONIC FLUXLESS SOLDER-BUMP CONTACTS FOR HYBRID MICROCIRCUITS

By: R. P. Mandal, Principal Investigator

Applied Technology A Division of Itek Corporation 645 Almanor Avenue Sunnyvale, California 94086

June 1976

**Final Report**

NASA Technical Manager: S. V. Caruso, Electronics and Control Laboratory

Prepared for

NASA – GOERGE C. MARSHALL SPACE FLIGHT CENTER Marshall Space Flight Center, Alabama 35812

## EVALUATION OF ADVANCED MICROELECTRONIC FLUXTESS SOLDER-BUMP CONTACTS FOR HYBRID MICROCIRCUITS

#### TABLE OF CONTENTS

|      |                                             |         |                                                                            | PAGE |

|------|---------------------------------------------|---------|----------------------------------------------------------------------------|------|

|      | LIST                                        | OF FIG  | URES                                                                       | iii  |

|      | ABST                                        | RACT    |                                                                            | V    |

| 1.   | INTR                                        | ODUCT   | ION                                                                        | 1    |

| II.  | PROC                                        | RAM C   | OBJECTIVES AND GENERAL APPROACH                                            | 4    |

| 111. |                                             |         | SE OF FLIP-CHIP TECHNOLOGY BY THE TRONICS INDUSTRY                         | 7    |

|      | Α.                                          | Curre   | ent Use of Flip-Chip Technology                                            | 7    |

|      | В.                                          | Limit   | ations of Flip-Chip Techniques Currently in Use                            | 14   |

|      | c.                                          |         | ntages and Disadvantages of Flip-Chip Technology<br>pared to Other Methods | 19   |

| IV.  | FLUX                                        | LESS SC | OLDER-BUMP TECHNOLOGY                                                      | 34   |

| ٧.   | META                                        | ALLURG  | ICAL INVESTIGATION                                                         | 39   |

| VI.  | FABR                                        | ICATIO  | N OF BUMP CONTACTS ON INTEGRATED CIRCUIT CHIPS                             | 48   |

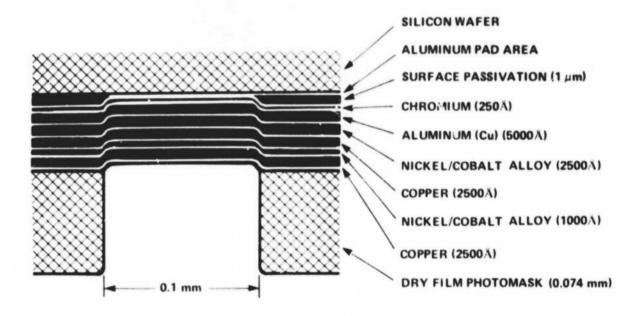

|      | Α.                                          | Simu    | lated Integrated Circuit Chips                                             | 48   |

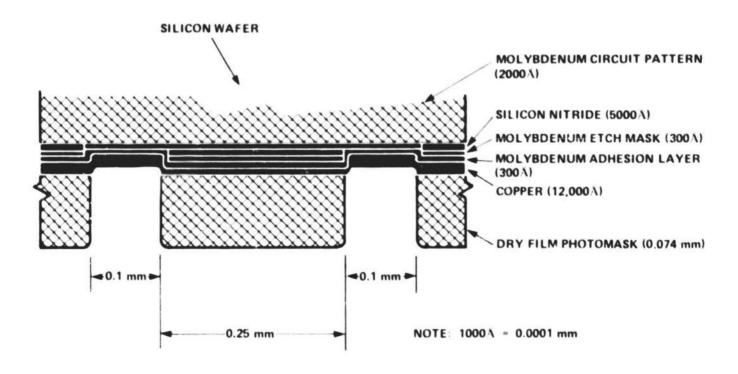

|      |                                             | 1.      | Base Metallization and Photomask                                           | 48   |

|      |                                             | 2.      | Bump Formation Process                                                     | 53   |

|      |                                             | 3.      | Device Separation                                                          | 62   |

|      | В.                                          | Comp    | olementary MOS Integrated Circuit Chips                                    | 62   |

|      |                                             | 1.      | Base Metallization and Photomask                                           | 62   |

|      |                                             | 2.      | Bump Formation Process                                                     | 67   |

|      |                                             | 3.      | Device Separation                                                          | 68   |

| VII. | ASSEMBLY TO THICK- AND THIN-FILM SUBSTRATES |         |                                                                            | 69   |

|      | Α.                                          | Subst   | rate Materials and Interconnect Patterns                                   | 69   |

|      | В.                                          | Attac   | chment Processes                                                           | 71   |

## TABLE OF CONTENTS - (Continued)

|       |           |                                                                                          | PAGE       |

|-------|-----------|------------------------------------------------------------------------------------------|------------|

|       |           |                                                                                          |            |

| VIII. | BOND      | QUALITY AND RELIABILITY                                                                  | 75         |

|       | Α.        | Introductory Discussion                                                                  | 75         |

|       | В.        | Centrifuge                                                                               | 76         |

|       | C.        | Thermal Cycle                                                                            | 77         |

|       | D.        | High Temperature Storage                                                                 | <i>7</i> 8 |

|       | Ε.        | Concluding Discussion                                                                    | 83         |

| IX.   | COND      | JCTIVE EPOXY ASSEMBLY                                                                    | 84         |

| х.    | APPLICA   | ABILITY TO VARIOUS DEVICE TYPES                                                          | 91         |

| XI.   |           | SS SOLDER-BUMP CONTACT TECHNOLOGY<br>ATION WITH RESPECT TO DEFINED CRITERIA              | 99         |

| XII.  | CONCI     | LUSIONS AND RECOMMENDATIONS                                                              | 103        |

|       | BIBLIO    | GRAPHY                                                                                   | 104        |

| APPE  | VDIX I    | STRESS/STRAIN CURVES FOR SELECTED SOLDER ALLOYS                                          | 106        |

| APPE  | NDIX II   | DRY FILM PHOTOMASK APPLICATION PROCEDURE: SIMULATED INTEGRATED CIRCUIT WAFERS            | 114        |

| APPE  | NDIX III  | PREPLATE PROCESS PROCEDURE FOR SIMULATED INTEGRATED CIRCUIT WAFERS                       | 116        |

| APPE  | NDIX IV   | ELECTROFORM PROCEDURE: GOLD/LEAD/SILVER SOLDER-BUMPS AND INDIUM/LEAD/SILVER SOLDER-BUMPS | 117        |

| APPE  | NDIX V    | POSTPLATE PROCEDURE: SIMULATED INTEGRATED CIRCUIT WAFERS                                 | 125        |

| APPE  | NDIX VI   | WAFER SAWING PROCEDURE                                                                   | 129        |

| APPEI | NDIX VII  | PREPLATE PROCESS PROCEDURE FOR CMOS WAFERS                                               | 130        |

| APPE  | NDIX VIII | POSTPLATE PROCEDURE: CMOS WAFERS                                                         | 132        |

## LIST OF FIGURES

|           |                                                                      | PAGI       |

|-----------|----------------------------------------------------------------------|------------|

| FIGURE 1  | CURRENT USE OF FLIP-CHIP TECHNOLOGY BY THE MICROELECTRONICS INDUSTRY | 13         |

| FIGURE 2  | VAPOR PRESSURES OF SELECTED METALS AT 1105°K                         | 17         |

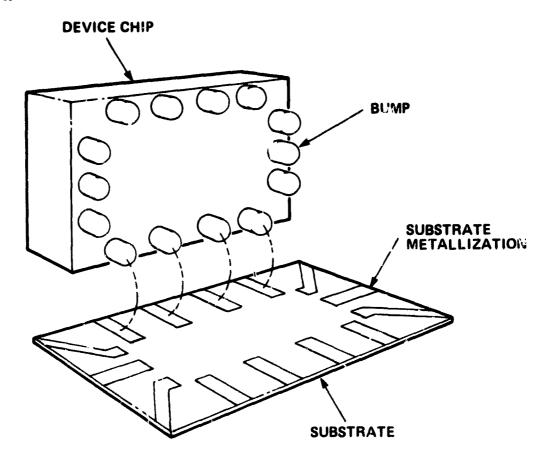

| FIC URE 3 | FLIP-CHIP ATTACHMENT                                                 | 20         |

| FIGURE 4  | SOLDER BUMP ATTACHMENT                                               | 21         |

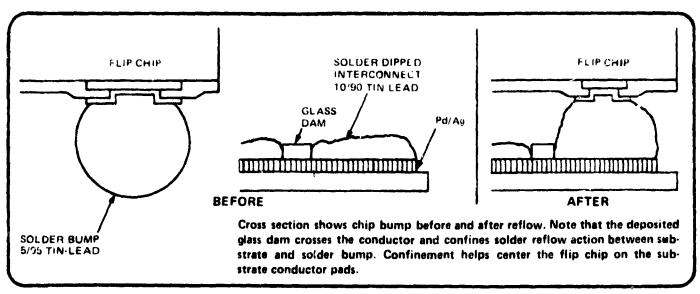

| FIGURE 5  | BEAM LEAD ATTACHMENT                                                 | 23         |

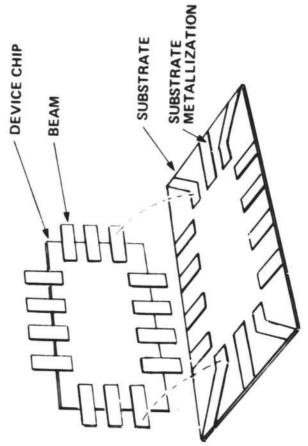

| FIGURE 6  | BEAM TAPE INNER LEAD BONDING SCHEMATIC                               | 24         |

| FIGURE 7  | BEAM TAPE BONDING MACHINE                                            | 25         |

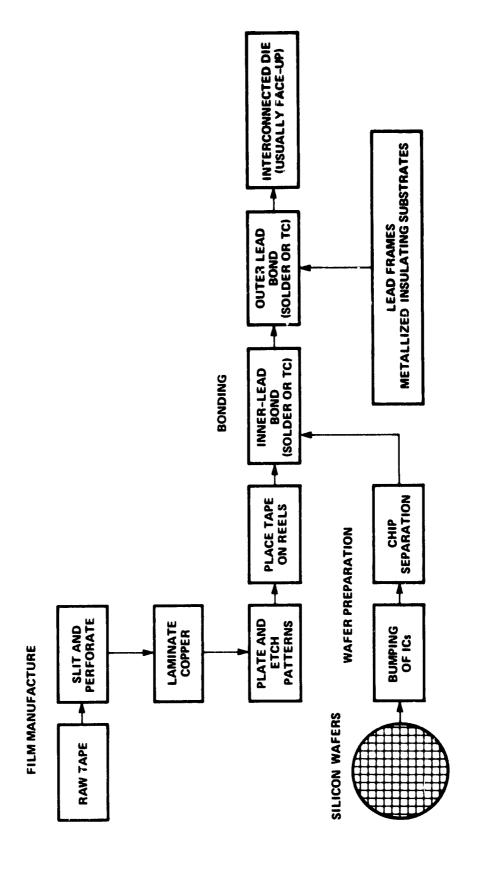

| FIGURE 8  | BEAM TAPE INTERCONNECTION PROCESS SEQUENCE                           | <b>?</b> 6 |

| FIGURE 9  | FLUX LESS SOLDER-BUMP TECHNOLOGY                                     | 35         |

| FIGURE 10 | SOME METALLURGICAL PROPERTIES OF SELECTED SOLDER ALLOYS              | 40         |

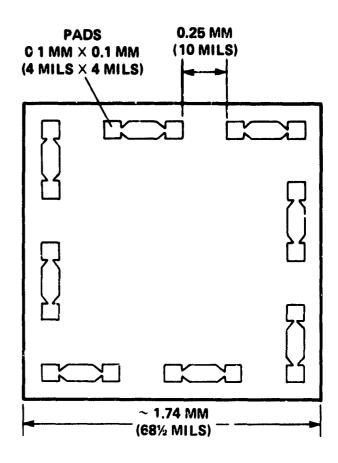

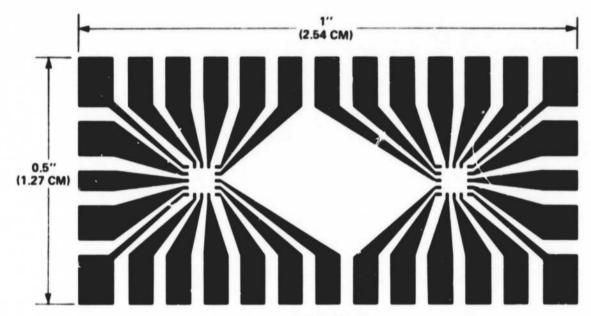

| FIGURE 11 | SIMULATED SEMICONDUCTOR CHIP METALLIZATION GEOMETRY                  | 49         |

| FIGURE 12 | BASE METALLIZATION AND PHOTOMASK CROSS-SECTION                       | 52         |

| FIGURE 13 | BASE METALLIZATION AND PHOTOMASK PHOTOGRAPH                          | 54         |

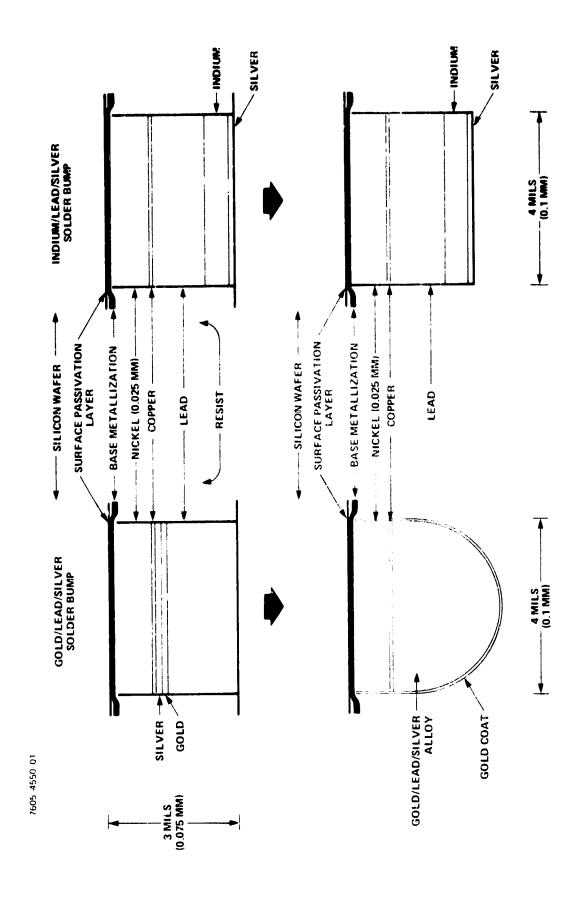

| FIGURE 14 | FLUX LESS SOLDER-BUMP CROSS-SECTION                                  | : 1        |

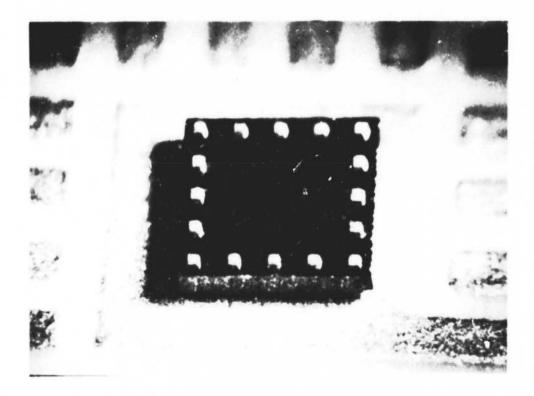

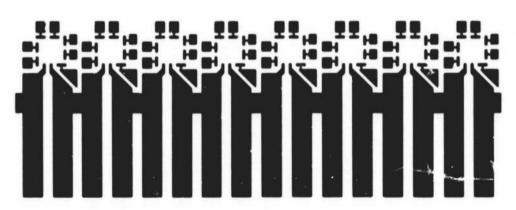

| FIGURE 15 | SOLDER-BUMPS ON SIMULATED IC CHIP                                    | <b>გ</b> ვ |

| FIGURE 16 | BASE METALLIZATION AND PHOTOMASK CROSS-SECTION: CMOS WAFER           | 66         |

| FIGURE 17 | THICK- AND THIN-FILM INTERCONNECT PATTERNS                           | 70         |

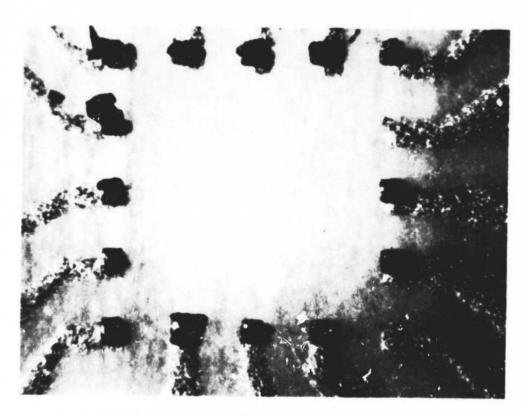

| FIGURE 18 | THICK-FILM SUBSTRATE METALLIZATION AFTER DEVICE SHEAR TESTS          | 79         |

| FIGURE 19 | THIN-FILM SUBSTRATE METALLIZATION AFTER DEVICE SHEAR TESTS           | 80         |

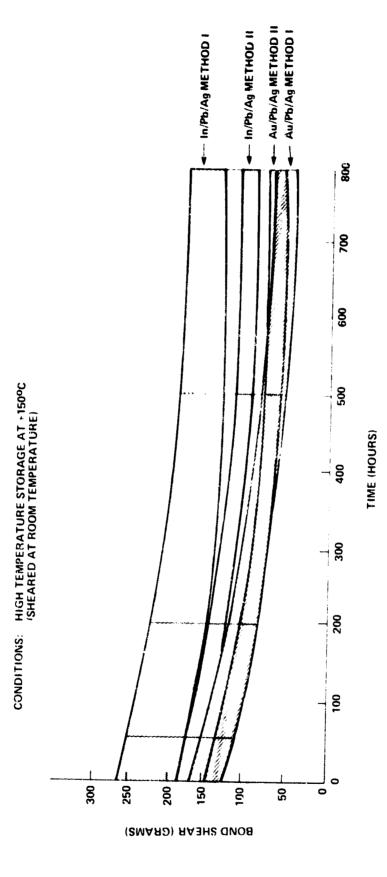

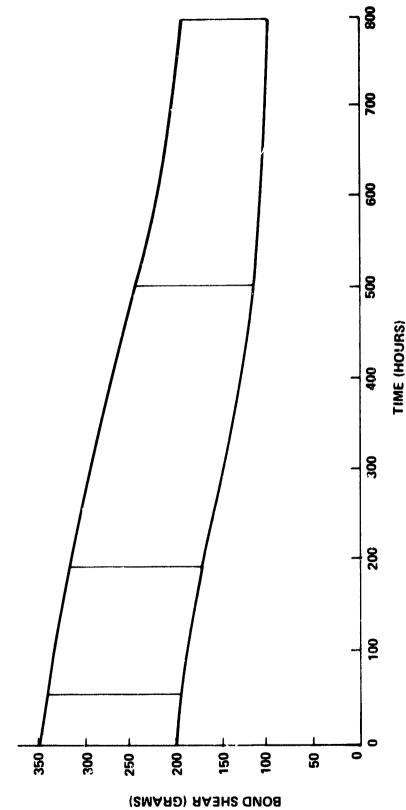

| FIGURE 20 | HIGH TEMPERATURE STORAGE                                             | 81         |

| FIGURE 21 | CONDUCTIVE EPOXY ATTACHMENT                                          | 86         |

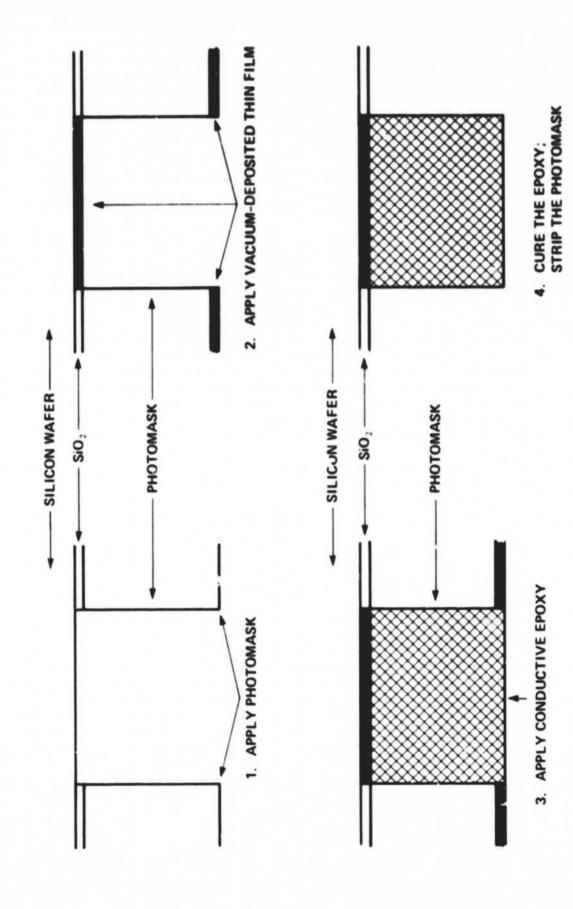

| FIGURE 22 | CONDUCTIVE EPOXY BUMPING PROCESS                                     | 89         |

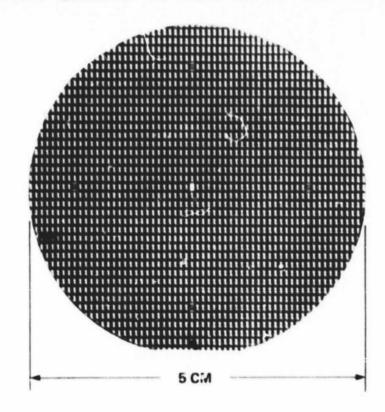

| FIGURE 23 | CMOS WAFER                                                           | 92         |

| FIGURE 24 | MM4601A SPECIFICATIONS                                               | 93         |

## LIST OF FIGURES - (Continued)

|           |            | PAGE |

|-----------|------------|------|

|           |            |      |

| FIGURE 25 | CMOS WAFER | 94   |

| FIGURE 26 | CMOS WAFER | 95   |

| FIGURE 27 | CMOS WAFER | 96   |

#### **ABSTRACT**

The trend in advanced electronic systems packaging is toward LSI hybrid microcircuitry in which a large number of monolithic integrated circuit chips of various types are incorporated with other active and passive components in a dense, multilevel, large-area module. However, such a circuit implementation requires a very large number of fine wire interconnections – 500 to 1,000 or more. The substantial cost associated with such a large number of independent, sequential operations, including the cost of required quality assurance procedures, is well known.

Alternative interconnection technologies have found application during the past few years, but various shortcomings have prevented them from becoming widely employed for most hybrid microcircuit requirements.

An in-depth study on the current use of flip-chip technology by the microelectronics industry was performed as part of this work and is presented herein. The advantages and disadvantages of this approach as compared to other methods are outlined, and the limitations of flip-chip techniques currently in use are discussed.

In the work described herein, a fluxless solder-bump contact technology was evaluated. Multiple solder-bump contacts were formed on silicon integrated circuit chips, which were then bonded directly to thick-film gold pads and to thin-film gold pads. No flux whatsoever was used in any part of the attachment process, thus precluding device degradation and failure due to flux residues.

These solder-bumps were electroformed onto device pads with the aid of thick dry film photomasks. Bump dimension was approximately 3 mils high and 4 mils by 4 mils in cross-sectional area  $(0.075 \text{mm} \times 0.1 \text{mm})$ .

Each bump was comprised of a rigid nickel underlayer and a compliant solder overlayer. The nickel underlayer served as a percestal for collapse control during chip attachment. Two different solder alloys were evaluated; a gold-coated gold/lead/silver alloy, and a silver-coated indium/lead alloy.

Bump processing details are given herein.

The devices were interconnected to gold bonding pads by means of ultrasonic die attachment/solder reflow processes.

Fluxless solder-bump bond quality and reliability were evaluated by observing and measuring the effects of centrifuge, thermal cycling, and high temperature storage on bond visual characteristics, bond electrical continuity, and bond shear tests. The results of this evaluation are presented herein.

The feasibility of joining fluxless solder-bump contacts to thick-film pads by means of conductive epoxy was explored.

Applicability to CMOS device processing was investigated.

The applicability and suitability of this interconnection technology for hybrid microelectronic packaging, with special attention given to joining reliability, low-cost, economical processing, adaptability to currently available devices, adaptability to automated processing, and implementability by both manufacturers of semiconductor devices and hybrid users is discussed.

#### I. INTRODUCTION

The electrical and mechanical interconnection of microcircuit chip devices to form integrated electronics currently presents a reliability and economic problem in the microelectronic packaging industry. The traditional and most commonly used method for single device and multichip (hybrid) packaging is achieved by first mechanically attaching the back side of the chip to a substrate. Then, small diameter wires are used to provide interconnections between the device and substrate metallizations.

This approach results in versatile interconnection with respect to routing flexibility, but it also produces fundamental reliability and cost difficulties. For each wire interconnection, two bonds must be made. For a multiplicity of interconnections, all performed one at a time by a human operator, each bond becomes somewhat unique, and, even with a high level of quality control, the probability that a complex microcircuit will contain at least one unacceptable bond becomes appreciable.

To improve circuit reliability, a series of complex screening procedures have been developed, including thermal cycling, centrifuging, high-temperature burn-in, etc. In addition, a technique has been developed for non-destructive pull-testing of each individual wire after it has been bonded to test for bond integrity, but this procedure nearly doubles the cost of the wire-bonding operation, which is very high already, and the test is a very delicate one, requiring a very careful operator in order to improve bond quality assurance rather than reduce bond quality. As a result, the cost of reliable wire-bonded interconnections constitutes a major part of the cost of fabricating reliable microcircuits.

Further, it has been shown by both NASA and DOD that interconnections produce the greatest single failure rate in high reliability electronic systems. It is perhaps somewhat ironic that although the development of microelectronic technology has resulted in reducing the relative number of discrete interconnections significantly, interconnections remain a major reliability problem for microelectronics.

The trend in advanced electronic systems packaging will continue toward larger-scale integration and increased component density. This trend will be sustained by a combination of larger-scale integrated monolithic devices incorporated into increasingly complex hybrids.

Ultra-large-scale integrated monolithic devices will not provide the total answer to advanced packaging requirements because of:

#### o Cost

Greater complexity requires more area for both the increased number of devices and for the associated interconnect routing. Very large monolithic chip size results in lower yield, which in turn results in higher cost. Eventually, a point of rapidly diminishing returns is reached as complexity is increased on a single chip, with respect to yield and therefore of cost.

#### o Design Flexibility and Lead Time

Very large-scale monolithic devices do not provide design flexibility, and require very long lead times. For relatively small quantities, unit cost is very high.

#### o Integration of Different Types of Devices

Hybrid integration is usually the best way to combine various types of technologies for required and/or optimum performance, such as bipolar and MOS, low power and high voltage, specialized photo-detection properties, integrated surface acoustic wave processing, etc.

#### o Final Utilization

The more complex monolithic chips would be incorporated into advanced hybrid microcircuits.

High density LSI hybrid microcircuits, employing substrates with multilevel interconnections, are being designed and fabricated now with more than 400 interconnection wires, or over 800 wire bonds per microcircuit. In addition, LSI hybrids are being designed with as many as 1500 wires, or 3000 wirebonds per microcircuit. For these microcircuits, none of the required wirebonds can be missing, and each one must be of sarisfactory quality. Thus, the demands on the wirebonding operators and on the quality assurance methods and implementation procedures are becoming critical.

Progress has been made toward automating or semi-automating the wire bonding process, but the problems (and costs) of required quality assurance procedures remain. The current absence of a practical, readily implementable alternative to wire-bonded interconnections is adversely affecting the microelectronics industry, and is overdue.

Three alternatives to wirebonding have been developed and include: (1) beam lead technology; (2) plastic film carrier technology and (3) flip chip technology. Each of these are viable methods and have been used with varying amounts of success. There are major objections to each of these approaches and therefore none have been developed to a degree that any has seriously competed with or replaced the wire-bonding technology.

However, the flip-chip technique appears to be a very promising general method for advanced development as an alternate to wire bonding for interconnection technology. The study reported herein concerns an investigation and evaluation of an advanced flip-chip interconnection method for application to high reliability low cost hybrid microcircuitry.

#### II. PROGRAM OBJECTIVE AND GENERAL APPROACH

#### A. Program Objective

The objective of this study is to evaluate an improved method for forming contacts on semiconductor devices, permitting all required mechanical and electrical interconnections to the device to be performed in a single, convenient, economical and reliable bonding operation, compatible with automated processing.

#### B. General Approach

This program was conducted in two phases, as follows:

#### 1. Phase I

An in-depth study was performed on the current use of flip-chip technology by the microelectronics industry. The advantages and disadvantages of this approach as compared to other methods was determined. A list of the various flip-chip techniques currently used was compiled, and the limitations of each was outlined.

#### 2. Phase II

A test program to evaluate microelectronic fluxless solder-bump interconnect technology was conducted, as follows:

- a. The evaluation was comprised of the following tasks:

- (1) Collect/measure appropriate solder metallurgical data

- (2) Fabricate arrays of simulated integrated circuit chips on silicon wafer blanks; fabricate solder bumps on the simulated IC contact pads, with minimum of sixteen contacts per chip, and separate the chips

- (3) Fabricate thick-film and thin-film flip-chip bonding puds

- (4) Demonstrate fluxless assembly compatibility to thickfilm gold pads and thin-film gold pads

- (5) Demonstrate that this technology can be applied to several types of devices (PNP, NPN, CMOS, 5OS, etc.)

- (6) Test bond quality and reliability by means of visual examination and characterization, electrical continuity, and bond shear strength of bonded chips, for the following environmental test conditions:

- (a) 10 temperature cycles from -65°C to +150°C

- (b) 10,000 G and 15,000 G centrifuge

- (c) High temperature storage at +150°C up to 1000 hours.

- b. The microelectronic fluxless solder-bump interconnect technology was evaluated on the basis of the following criteria:

- (1) Reliability of electromechanical interconnection of semiconductor chips

- (2) Low cost processing

- (3) Implementability by both manufacturers of semiconductor products and purchasers of these products

- (4) Compatibility with available bonding equipment and materials

- (5) Economy for both large and small volume production

- (6) Adaptability to automatic procedures

- (7) Compatibility with a large number of bump contacts per chip.

# III. CURRENT USE OF FLIP-CHIP TECHNOLOGY BY THE MICROELECTRONICS INDUSTRY

#### A. Current Use of Flip-Chip Technology

Data gathered in a technology and utilization survey as part of this study shows that there are primarily five organizations currently employing flip-chip technology to a significant extent; namely IBM, Delco Electronics, General Electric, Motorola, and Micro Components Corporation.

Two of these organizations – IBM and Delco – are strictly internal manufacturer/consumers of flip-chipped devices; that is, they consume all of their own internal production of flip-chip devices, neither procuring nor selling such parts external to the organization itself.

A brief description and discussion of the technology employed by each of these five organizations follows.

#### 1. IBM

IBM has been the most prominent and most consistent promoter of flip-chip technology to date. However, because of the relative isolation of IBM in the hybrid microelectronics world (due to the special business circumstances peculiar to IBM), IBM has had only a second-order influence on flip-chip technology external to IBM until comparatively recently (i.e., until the 1970's). However, IBM's internal usage of this technology is and has been enormous, relatively speaking.

Current IBM chip joining technology employs solder reflow processes, and is termed "Controlled Collapse" by IBM.

Bump metallization is basically done as follows. A thin molybdenum metal mask, with through-holes etched through the mask to coincide with device interconnection pads on the silicon wafer, is aligned and clamped to the wafer. Within a vacuum chamber, glow discharge bombardment is used to clean the contact surface areas. Then metallization layers are deposited through the metal mask onto the contact pad areas, comprised of approximately 1000 Å chromium, 500 Å chromium/copper alloy, 5000 Å – 10,000 Å, copper, and finally 1000 Å gold. At this point, the mask is changed; another molybdenum mask, with an identical through-hole pattern, but with larger diameter holes, is aligned and clamped to the wafer. Within a vacuum chamber, lead-tin alloy is deposited over the gold dot pattern, to a thickness of approximately 0.05mm. Considerable fractionation of the lead/tin alloy source material takes place, resulting in a bomp which is tin-rich at it's surface, but the equivalent composition of the bump alloy is 95 wt.% lead, 5 wt.% tin. The bumps are subsequently melted by heating the wafers in a reducing atmosphere, forming hemispheres of a relatively uniform solder alloy composition.

The oversize solder deposit, achieved by means of larger through-holes in the solder deposition mask, achieves a useful purpose in that, when the bumps are melted to form hemispheres, the diameter of the solder constricts to the diameter of the underlying metallization layers; thus, the final height of the solder bump increases to more than 0.075mm from the original thickness of 0.05mm, without requiring additional deposition time and while minimizing problems with the mask. The diameter of completed bumps is approximately 0.1 to 0.125mm (4 to 5 mils).

Finally, the wafer is sawed into individual devices.

In this process, it is reported that 40 to 50 wafers are processed at a time, and that 30 minutes of labor is required for each batch in order to build up the required thicknesses of metallization.

The counter-substrates employed are comprised of alumina, with palladium/silver thick-film conductors, coated with 90 lead/ 10 tin solder. Glass dams

over selected portions of the conductor surfaces are used to restrict solder flow. The total volume of solder on the semiconductor devices and on the substrate bonding pads is controlled in order to achieve reliable joints. A white rosin flux is applied over the substrate bonding pad surface before chip placement, to act as a tenderary adhesive and to promote wetting during solder reflow. Joining is performed in reflex for access in a nitrogen atmosphere.

The flip-chip bumped devices are manipulated and bonded automatically at high handling rates.

A major reason for employing 90 lead: 10 tin on the substrate pads is to maintain the melting point of this joint above that of the lead/tin eutectic, which is used in subsequent module processing steps, and to achieve proper joining at the flip-chip bump.

#### 2. Delco Electronics

At Delco, flip-chip devices are processed as follows. Thin chromium and gold layers are vacuum-deposited over the aluminum contact pads which constitute the silicon wafer metallization, to serve as the bump underlayer. An electroforming process, using a photoresist mask, is used to form the pure silver bumps. Final bump dimensions are approximately 5 mils diameter and 3 mils high (0.125mm diameter by 0.075mm high).

The counter-substrates employed are alumina with thick-film conductors. The bonding areas are coated with lead/tin eutectic, applied primarily by means of solder screening, or alternatively by means of solder dipping. Chip joining is done by means of solder reflow, with the aid of a fluxing agent.

Delco uses a single 6-bump chip on each voltage regulator microcircuit produced by Delco, and a single 9-bump chip on each electronic ignition module. Total flip-chip device usage rate is approximately 60,000-80,000 flip-chip devices per day.

These same two device types have been produced and used by Delco for the past several years, at approximately the same rate, with little or no change in the rechnology or the numbers and types of flip-chip devices used.

#### 3. General Electric

Flip-chip devices are manufactured at GE's Integrated Circuits Center at Syracuse, NY. Little data can be gathered regarding the particular processes and construction employed in these devices because GE considers their process to be proprietary. However, the flip-chip solder metallization is 95 lead: 5 tin, and bump geometry is very similar to that of the corresponding IBM parts. GE claims that all of their flip-chip parts are passivated with silicon nitride.

Devices currently being supplied are bipolar, although it is claimed that MOS devices have been processed on an experimental basis with good results.

GE's Mobile Radio Products Division at Lynchburg, VA is a volume user of flip-chip parts from GE's Integrated Circuits Center, from Motorola Semiconductor Products Division, and from Micro-Components Corporation. The flip-chip parts are joined to eutectic tin-lead solder-coated thick-film conductors on alumina substrates. Solder reflow with the aid of flux is employed. GE claims that bonding yields approach 100%.

GE's Heavy Military Electronic Systems Division at Syracuse, NY has reportedly started using flip-chip technology in very moderate volume on a highly classified project within the last year.

#### 4. Motorola

Motorola has made flip-chipped devices available on a commercial basis during the last 2 or 3 years. The flip-chip metallization process and bump structure appears to be similar or identical to that of IBM.

Motorola is primarily a manufacturer of flip-chip devices rather than a user, although it is rumored that the Ft. Lauderdale Communications Division of Motorola will begin employing flip-chip technology in 1976.

At the present time, Motorola offers only bipolar integrated circuits in flip-chip form, although the feasibility of supplying MOS and CMOS devices in flip-chip form is being investigated. The recent move of much of Motorola's MOS and CMOS operations to a facility in Austin, Texas seems to be affecting this feasibility verification work. A major process problem affecting the successful processing of MOS and CMOS parts at Motorola will probably involve a step in which Motorola cleans the base aluminum contact pads with a glow discharge prior to depositing additional metallization layers, in order to achieve a reliable low-resistance electrical contact. An alternative method for assuring a reliable low-resistance contact will have to be employed.

#### 5. Micro Components Corporation

At Micro Components, flip-chip devices are processed as follows, starting with oxide-passivated wafers, with windows opened at the contact pads.

A clean aluminum metallization pad surface is assured by means of careful processing at the time that windows are opened in the surface oxide passivation layer. Then a series of metal layers is deposited over the entire wafer; first aluminum (approximately) 2500 Å); then aluminum/nickel alloy (approximately 5000 Å); and finally nickel (approximately 3000 Å). A photomask is applied, and nickel is etched away everywhere except at the contact pad areas, leaving the continuous aluminum layer in place over the entire wafer. The photomask is then removed and a second "reverse" photomask is applied, such that only the contact pad areas remain exposed. Then electrolytic copper (approximately 15 ¼ m thick) and finally a 95 lead / 5 tin solder alloy (approximately 0.075mm thick) is electroformed onto the contact pad areas. The photomask is then removed, the exposed aluminum film is etched away, and the solder terminals are formed into hemispheres by melting in an inert atmosphere.

The purpose of the copper layer is to form a surface readily wetted by solder. The purpose of the nickel and nickel/aluminum layers is to provide a surface which would remain intact in the event that the entire copper layer were entirely converted to copper/tin intermetallic, thus providing some final measure of adhesion to the solder during repeated solder reflow cycles. The aluminum layer provides adhesion to the wafer surface.

Micro Components presently has available 8 families of devices in flip-chip form, and is reportedly producing hundreds of thousands of such devices per month.

In addition to the five organizations employing flip-chip technology to a significant extent as outlined above, others might be mentioned that have pursued the technology in the past, and more that some indications suggest may be joining what appears to be a rapidly growing reviving interest in this technology. However, available data regarding current important users  $\alpha^{\mu}$  flip-chip technology indicate that the list shown in Figure 1 is essentially complete.

When reviewing Figure 1 it becomes evident that the IBM technology has now achieved a marked impact on current flip-chip technology. Delco's technology, which is the major exception, has apparently been applied to only two devices of note, both of which were first developed several years ago; accordingly, even though volume usage continues to be impressive, and reliability is excellent under the extremely difficult operational environment associated with proximity to automible engines, Delco appears to have stagnated somewhat in this technology.

During the 1960's, IBM employed what they referred to as the "SLT" technology which was applied to their System/360 computer. This technology was notable in that copper spheres were incorporated into the solder bump structure to provide chip stand-offs. During the beginning of the 1970's the SLT technology evolved into the so-called

| ORGANIZATION/LOCATION                                                                                                                                               | VOLUME | VOLUME<br>USER | GENERAL FLIP-CHIP<br>BUMP TECHNOLOGY DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      | COMMENTS                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBM, INCLUDING IBM<br>COMPONENTS DIVISION<br>EAST FISHKILL FACILITY<br>HOPEWELL JUNCTION, NY                                                                        | ×      | ×              | CHROMIUM, CHROMIUM/COPPER ALLOY, COPPER, AND GOLD LAYERS ARE VACUUM-DEPOSITED OVER THE ALUMINUM DEVICE METALLIZATION THROUGH METAL MASKS. 96 LEAD: 5 TIN BUMPS, APPROXIMATELY 0.06 MM HIGH, ARE THEN VACUUM-DEPOSITED ONTO THE GOLD LAYER THROUGH METAL MASKS, AND SUBSEQUENTLY REFLOWED TO FORM HEMISPHERES APPROXIMATELY 0.075 MM HIGH. CHIP ATTACHMENT BY REFLOWING 90:10 LEAD/TIN SOLDER IN NITROGEN, USING FLUX. | TOTALLY IN-HOUSE MANUFACTURER/<br>USER. IBM HAS BEEN THE MOST PROM-<br>NENT PROMOTER OF FLIP-CHIP TECH-<br>NOLOGY OVER THE PAST 10 TO 12 YEARS                                                                                                             |

| DELCO ELECTRONICS<br>KOKOMO, IN                                                                                                                                     | ×      | ×              | CHROMIUM AND GOLD LAYERS ARE VACUUM-<br>DEPOSITED OVER THE ALUMINUM DEVICE<br>METALLIZATION. PURE SILVER BUMPS, 0.125 MM<br>IN DIAMETER AND 0.075 MM HIGH, ARE ELCTRO-<br>FORMED OVER THE GOLD LAYERS. CHIP ATTACH-<br>MENT 6Y REFLOWING TIN/LEAD EUTECTIC<br>SOLDER, USING FLUX.                                                                                                                                     | TOTALLY IN-HOUSE MANUFACTURER/<br>USER. DELCO USES A 6-BUMP FLIP-CHIP<br>ON THEIR VOLTAGE REGULATOR<br>MACROCIRCUIT AND A 9-BUMP FLIP-CHIP<br>ON THEIR ELECTRONIC IGNITION<br>MODULE. TOTAL USAGE IS ABOUT 40: 000<br>TO 80,000 FLIP-CHIP DEVICES PER DAY. |

| GENERAL ELECTRIC: A. MOBILE RADIO PRODUCTS DIVISION, LYNCHBURG, VA B. INTEGRATED CIRCUITS CENTER, SYRACUSE, NY C. MILITARY ELECTRONIC SYSTEMS DIVISION SYRACUSE, NY | ×      | ×              | THE GE FLIP-CHIP BUMPING PROCESS IS CONSIDERED TO BE PROPRIETARY BY GE, AND LITTLE TECHNOLOGY DATA IS AVAILABLE. GE'S DEVICES ARE PASSIVATED WITH SILICON NITRIDE, AND THE BUMPS ARE PRIMARILY COMPRISED OF LEAD/TIN SOLDER WITH HIGH LEAD CONTENT.                                                                                                                                                                   | GE PURCHASES FLIP-CHIP DEVICES FROM MOTOROLA AND MICRO-COMPONENTS CORPORATION, IN ADDITION TO SUPPLY-ING SOME OF THEIR OWN IN-HOUSE DEVICE REQUIREMENTS. G: IS A VOLUME USER OF FLIP-CHIPS.                                                                |

| MOTOROLA SEMI-<br>CONDUCTOR PRODUCTS DIV.<br>PHOENIX, AZ & MESA, AZ                                                                                                 | ×      |                | FLIP-CHIP METALLIZATION TECHNOLOGY IS ESSENTIALLY IDENTICAL TO THAT OF IBM, DESCRIBED ABOVE.                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            |

| MICRO COMPONENTS<br>CORPORATION<br>CRANSTON, RI                                                                                                                     | ×      |                | ALUMINUM, ALUMHINUM/NICKEL ALLOY, AND NICKEL LAYERS ARE VACUUM-DEPOSITED OVER THE WAFERS, AND THE NICKEL IS PATTERNETCHED. ELECTROFORMED BUMPS OF COPPER AND 95:5 LEAD/TIN ALLOY ARE THEN PLATED OVER THE NICKEL. EXPOSED ALUMINUM IS THEN ETCHED AWAY, AND THE SOLDER IS MELTED. FORMING BUMPS APPROXIMATELY 0.1 MM HIGH.                                                                                            |                                                                                                                                                                                                                                                            |

Figure 1. Current Use of Flip-Chip Technology by the Microelectronic Industry

"controlled collapse" technology described above, with the chief advantage that the joints which resulted were much more ductile and therefore more reliable.

The Motorola technology appears to be essentially identical to that of IBM for all practical purposes. The Micro Components technology is substantially different from that of IBM in many details, but the general characteristics of the final product is essentially identical to that of IBM. General Electric's technology, no doubt, falls within this same classification range also. Thus, in summary, the current leading flip-chip technologies employ lead/tin solder bumps, lead/tin bonding pads, and solder reflow joining with the aid of a fluxing agent, as first pioneered by IBM.

#### B. Limitations of Flip-Chip Techniques Currently in Use

The flip-chip bumping technology employed by IBM, Motorola, and (probably) General Electric are essentially identical. This technology basically consists of vacuum-depositing thin metal bump base layers onto wafer contact pad areas through a special metal shadow-mask, followed by vacuum-deposition of thick lead-tin solder bumps onto the base layers using a second special metal shadow-mask.

The flip-chip bumping technology at Micro Components is somewhat different in that the thin metal base layers are applied by means of vacuum deposition followed by subtractive etching. Thick lead-tin solder bumps are then applied onto the metal base layers by means of an electroforming process. However, the final bump structure is very similar to that of IBM/Motorola/GE.

The flip-chip bumping technology at Delco is rather unique among these five. The thin metal base layers for the bumps are applied by means of vacuum deposition followed by subtractive etching. Thick bumps of pure silver are then formed over the metal base layers by means of electroforming process. The Delco technology can also be classified as a solder bump technology because, in common with IBM/Motorola/GE/Micro Components, solder present on the counter-substrate is used for chip joining by means of solder reflow.

Thus, all currently prevalent flip-chip joining techniques employ solder chip joining, as opprised to ultrasoric or thermocompression chip joining.

All of the flip-chip bumping and joining technologies currently employed, as outlined above, require complex processing, both for the bumping processes and the chip joining processes. Complex processes are objectionable from both reliability and yield/cost viewpoints.

For these bumping processes, either two sequential metal-shadow masking steps are required, or two sequential photoresist masking steps.

The IBM process requires two special metal shadow-masks for each wafer type. Metal shadow-mask making involves relatively expensive, complex processes. Mask handling and alignment is critical, and the metal masks used during solder deposition require cleaning after each deposition. In general, vacuum deposition processes are relatively complex and time-consuming, requiring relatively expensive equipment. However, it should be noted that vacuum deposition processes employing metal shadow-masking is relatively very clean, provided that intimate mask contact is assured during the deposition process in order to prevent metal from reflecting between the mask and the wafer, which could otherwise result in metal "halos" and consequent device shorting or other problems.

Chip joining associated with these flip-chips is also complex, in that substrate bonding pads must first be pre-coated with solder, and then coated with solder flux.

Solder flux is especially objectionable in that, following solder reflow chip joining, a second process step is required in order to remove the flux residue. However, it is difficult to reliably remove flux residues after they have been heated to soldering temperatures (for flux materials which are sufficiently active to permit reliable joining), especially in the close spacings between bonded devices and substrate. It is well known that flux residues can lead to subsequent device degradation and failure.

Circuit rework requires a second application of flux, solder reflow, and a second cleaning step to remove flux residue.

In addition, the IBM "Controlled Collapse" chip joining technology requires the use of both solder dams and closely-controlled volumes of solder on the substrate bonding pads, which is an additional complication factor.

A further disadvantage of these technologies is that, to minimize leaching by the solder, thick-film materials containing either palladium or platinum are employed, in conjunction with high-lead solders. Thick-film inks containing palladium or platinum are expensive because of the high cost of these precious metals. The use of high-lead solders requires relatively high-temperature processing.

IBM's selection of lead/tin for their thermally deposited solder bump alloy rather than lead/indium is puzzling. As shown in Figure 2, the extent of lead/tin alloy fractionation during evaporation is 500 times greater than that for lead/indium. Thus, process control for lead/indium alloy deposition would be much simpler than that for lead/tin, resulting in improved, more reliable composition control for lead/indium. Indium depresses the melting point of lead in a manner very similar to tin; e.g., the liquidus of both 90 wt.% lead/10 wt.% tin and 90 wt.% lead/10 wt.% indium is 300°C. Lead/indium alloys are much less likely to attack solderable bump base metallization layers than lead/tin. The mechanical properties of lead/tin and lead/indium are nearly identical and they form compatible solder joints when joined to each other.

Finally, it might be mentioned that glow discharge cleaning of wafer device pads prior to deposition of the initial bump base metallization layer may not be compatible with MOS device process requirements.

FIGURE 2

VAPOR PRESSURES OF SELECTED METALS AT 1105°K.

| Element | Approximate Vapor<br>Pressure at 1105 K. | Fractionation Ratio at 1105° K for Lead Alloys $\left(\begin{array}{c} p^{\circ} \\ p^{\circ} \end{array}\right) \qquad \frac{M_{\text{Pb}}}{M}$ | Component<br>Preferentially<br>Evaporated |

|---------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Lead    | 1 × 10 <sup>-1</sup> torr                | 1                                                                                                                                                | -                                         |

| Tin     | 2 x 10 <sup>-6</sup> torr                | $2.6 \times 10^{-5}$                                                                                                                             | РЬ                                        |

| Indium  | $1 \times 10^{-3}$ torr                  | 1.3 x 10 <sup>-2</sup>                                                                                                                           | Pb                                        |

| Silver  | 1 × 10 <sup>-4</sup> torr                | $1.4 \times 10^{-3}$                                                                                                                             | РЬ                                        |

| Gold    | 2 × 10 <sup>-8</sup> torr                | 2 × 10 <sup>-7</sup>                                                                                                                             | Pb                                        |

In summary, flip-chip techniques currently in use feature the traditional advantages of solder-bump flip-chip joining, including the following features:

- o High speed gang-bonding

- o Rugged terminals

- o No special tooling required in order to handle each device size

- o Automatic chip alignment and leveling during solder reflow

- o Ductile, annealed chip joints

The major limitations and disadvantages of prevalent flip-chip techniques are outlined below:

- 1. Complex solder bump processing

- o Two masking steps are required, with critical alignment.

- 2. Complex chip joining processing

- o Substrate bonding pads must be pre-coated with solder, which must in turn be pre-coated with flux.

- o The amount of solder at the bonding pad area must be closely controlled, by using solder dams and closely-controlled solder thickness.

- o To minimize leaching, thick-film conductors containing either platinum or palladium must be used, which are expensive, in combination with high-lead solders.

- o The use of high lead solders requires relatively high temperature processing.

- o Flux residues must be removed.

#### 3. Flux residues

o It is difficult to reliably remove flux residues after they have been heated to soldering temperatures, especially in the close spacings between bonded devices and substrates. Flux residues can lead to subsequent device degradation and failure.

# C. Advantages and Disadvantages of Flip-Chip Technology Compared to Other Methods

The three major alternatives ro gang-bonded interconnections are the flipchip, beam-lead, and beam-tape technologies.

In flip-chip technology, metal bumps integrated with the chip and extending well above the chip surface are used to interconnect the chip in a face-down position to substrate circuit pads, as illustrated in Figure 3.

Flip-chip technology can be divided into two major categories, distinguished by the method of attachment; namely, ultrasonic-bump and solder-bump. Ultrasonic-bump flip-chips may employ aluminum as the chief bump metallization, formed by means of vacuum deposition through a metal mask or by means of photolithography. Solder-bump flip-chips typically employ 95% lead/5% tin as the solder metallization. Solder-bump flip-chip attachment is depicted in Figure 4.

Figure 3. Flip Chip Attachment

7605 4550 36

Figure 4. Solder Bump Attachment

7605-4550-08

Beam Lead

Figure 5.

POECEDING PAGE BLANK NOT FILMET

7605-4550-12

## INNER LEAD BONDING SCHEMATIC

Figure 6. Beam Tape

7605-4550-11

Figure 7. Beam Tape Bonding Machine

# INTERCONNECTION PROCESS SEQUENCE

Figure 8. Beam Tape

- 2. Disadvantages of beam-lead technology compared to flip-chip technology.

- o Special circuit layouts must be used on the silicon wafer, in order to provide room for beam formation; and, if chips are separated by means of anisotropic etching, specific silicon crystallographic orientation is required. Thus, the technology cannot employ the great majority of circuit layouts currently available, and the semiconductor manufacturer's basic process might need to be modified. Also, most of the latest high-performance devices cannot be obtained in beam-lead form.

- o Fewer circuit chips can be formed on a silicon wafer of a given size, because of the need to allow room for the beams, resulting in fewer devices per wafer and increased device cost.

- o Beam-lead processing is complicated, involving two or three additional photomasking steps, resulting in increased device cost and reliability impact in small volume production.

- o Beam-leads are fragile (susceptable to bending), creating handling and shipping problems.

- o Beam-lead device attachment is difficult to reliably automate.

Automatic handling and bonding is difficult, and a lignment to bonding pads is critical.

- o For gang-bonding processes, a special-size bonding tool is required for each die size.

- 3. Advantages of beam-tape technology compared to flip-chip technology.

- o Convenient bond inspection.

- o Long lead-lengths are readily provided (well suited for packaging single devices in plastic-encapsulated DIP's).

- 4. Disadvantages of beam-tape technology compared to flip-chip technology.

- o Electrical and mechanical interconnections are made in two separate mechanical steps, rather than the single step of flip-chip (or beam-lead) interconnection. Twice as many discrete joints are required.

- o For reliable joining, it is desirable to form raised bumps on the chip pads, somewhat similar to that employed in flip-chip interconnections, to which the beam-tape is bonded.

Thus, processing and attachment is more complex than for flip-chip technology.

- The process is difficult and expensive to automate. The critical alignment requirements of both the etched film over the chip devices and the beam-tape assembly to external circuit pads dictates that specialized, elaborate equipment must be used.

- The extensive tooling requirements, comprising both mechanical equipment and custom etched beam-tape patterns, necessitates very high unit production in order to be cost effective.

- o Special bonding tools are required for each die size.

- o Packaging is not as dense as for flip-chip.

- 5. Disadvantages of flip-chip technology.

- a. Ultrasonic-bump

- o Considerable pressure must be applied to multiple-bumped chips during bonding, in order to achieve high bond strength, which can cause chip breakage or crack propagation. Also, bumps can be scrubbed right through thin-film metallization, resulting in poor interconnection reliability, unless care is exercised.

- o Ultrasonic waves can propagate through the substrate material during device attachment, which can affect bond strengths of previously-bonded chips.

- o Alignment to bonding pads is critical.

- o The integrity of the multiplicity of bonds cannot be verified by optical inspection alone.

### b. Solder-bump

o Substrate bonding pad construction is complex, requiring pre-coating with solder and flux and requiring solder dams to restrict solder flow and closely controlled volumes of solder on the solder pads.

- o Flux residues must be removed from the close spacing between chip and substrate. Flux residue contamination is a reliability risk.

- o Lead-tin solder is not metallurgically compatible with the formation of joints with films containing gold.

- o Relatively high temperature processing is required.

- o Bump processing can be complex, comprising multiple photolithographic operations.

- 6. Advantages of flip-chip technology compared to beam-lead technology.

- o Special wafer layouts are not required in order to provide space for beam-lead formation.

- o Wafer chip density is not reduced, which would otherwise result in fewer devices per wafer and increased device cost.

- o Chip separation by means of anistropic etching is not required, so that wafer crystallographic orientation constraints are relaxed.

- o Flip-chip processing is simpler and less expensive than beam-lead processing.

- o Flip-chip bumps are more rugged than beam-leads, thus facilitating handling and shipping.

- o A special tool is not required for each flip-chip die size, as is the case for beam-lead gang-bonding.

- o Flip-chip devices cost less to process than beam-lead devices.

- 7. Advantages of flip-chip technology compared to beam-tape technology.

- o Half as many discrete joints are required for flip-chip interconnections, as compared to beam-tape interconnections. For beam-tape, two discrete joining operations are required for each device.

- o Silicon wafer processing is nearly as complex for beam-tape as for flip-chips, because raised bumps should be provided on device pads for reliable beam-tape joining. Overall, chip joining is more complex for beam-tape.

- o Beam-tape is both difficult and very expensive to automate, as compared to flip-chip.

- o Special tooling is not required for each flip-chip die size.

- o Flip-chips can be packaged to the densely than beam-tape interconnected devices.

- 8. Disadvantages of solder-bump technology compared to beam-lead and beam-tape technology.

- o Flip-chip bond joints are not as easy to inspect as beam-lead or beam-tape bond joints.

- o Solder-bump flip-chip joining may require the use of solder flux.

- o Flip-chip substrate bonding pads may have to be fabricated from expensive materials containing palladium or platinum in order to minimize solder leaching.

#### Further discussion.

With reference to ease of bond joint inspection, as mentioned above, it should a pointed out that there is a great deal of similarity between beam-lead and beam-tape bond joints and wire bond joints, as far as the basic mechanism of joint formation and the subsequent optical impection procedure are concerned. It should be noted that it may be so difficult to assure the bond integrity of wire bond joints by means of certified bonding equipment, processes, and operators in conjunction with optical inspection, in addition to other reliability assurance procedures such as thermal cycling, high temperature burn-in, and centrifuge, that some organizations have resorted to 100% non-destruct wire bond pull testing for additional quality assurance. Thus, the intrinsic value of optical inspection of beam-lead or beam-tape joints in itself is of limited quality assurance significance.

Unless special provisions are made to extend flip-chip bumps to the edge of the chip, the joint is much more difficult to inspect than beam-lead joints, but the visual appearance of the solder meniscus, and the assurance of an annealed joint may be more meaningful than the information conveyed by the deformation pattern on the surface of a beam-lead or beam-tape joint.

An intriguing future potential exists for chip devices supplied pre-bonded to beam-tapes in a standard fan-out pattern; however, (1) a substantial device handling problem would still be present, similar to the situation for beam-leaded devices; and (2) it is not clear that it would be faster to interconnect such beam-tape devices than wire-bonded devices, unless a special gang-bonding tool is used for each beam-tape size.

A great deal has been said of the advantages of the so-called sealed junction properties of the beam-leaded devices. The sealed junction devices employ a platinum silicide ohmic contact, a silicon nitride surface passivation, and a titanium/platinum/gold-layered metallization overlapping the edges of the silicon nitride windows. This construction has proved to be effective in resisting contamination in humid environments. However, it should be recognized that an analogous device construction applied to another type of interconnection technology would be equally effective in resisting contamination in humid anvironments. This desirable characteristic need not necessarily be associated only with beam-leads.

### IV. FLUXLESS SOLDER-BUMP TECHNOLOGY

In fluxless solder-bump technology, flip-chip solder-bumped devices are bonded to gold circuit pads without the use of any flux whatsoever.

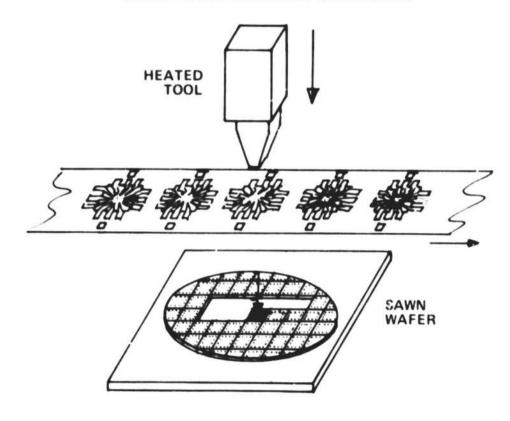

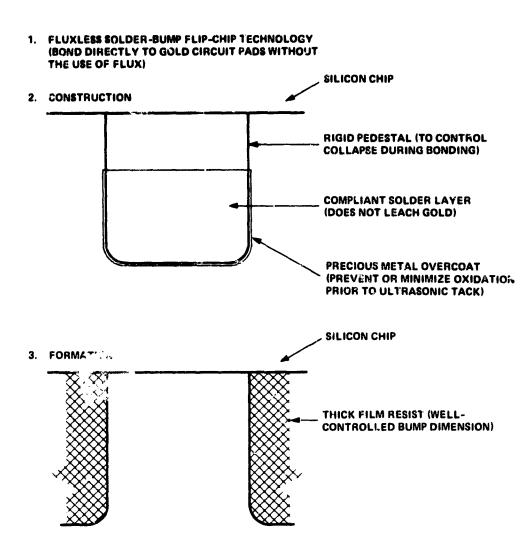

A schematic of fluxless solder-bump construction is shown in Figure 9.

The bump structure consists of two chief metallization layers. First, a relatively hard metal or alloy layer of relatively high melting point is applied adjacent to the base semiconductor device metallization. Then a relatively soft solder alloy layer of relatively low melting point is applied as the bump extremity.

The solder layer has the function of forming a solder bond to gold circuit bonding pads for device mechanical and electrical interconnection. The compliant properties of the solder layer permits multiple-bumped devices to be reliably interconnected despite some degree of non-planarity of the joining surfaces. It also accommodates disparate thermal expansion between bonded chip and substrate. A thin precious metal coating over the solder layer prevents or minimizes environmental effects on the bonding surface, to permit reliable fluxless solder attachment.

The chief function of the hard underlying metal layer is to serve as a rigid pedestal to control bump distortion characteristics during bonding. Without this pedestal layer, much of the solder distortion during bonding might take place at the semiconductor device surface. This pedestal layer assures that bump dimensions at the device surface remains constant, and that any solder bump collapse which occurs during bonding, prior to solder reflow, takes place at the bonding surface. The pedestal layer also serves as a metallurgical transition layer between the semiconductor device metallization and the solder layer.

The pedestal comprises approximately 1/3 of the bump height, and the solder layer the remaining 2/3. Total bump height is approximately 3 mils (0.075mm).

Figure 9. Fluxless Solder-Bump Technology

For low-cost processing, electroforming techniques are used to form the solder bumps. Since electroforming processes require electrical contact to every bump position, a continuous metal film is first coated over the entire wafer, over the device base metallization and surface passivation layer. Then a thick-film photomask is applied over the metal surface film, and windows are opened in the photomask at the future bump sites. The thick-film photomask helps to assure very well-controlled bump diameters.

For the solder layer material, lead alloys were selected, primarily because lead forms compliant, corrosion-resistant, low temperature solders. In addition, some lead alloys are compatible with the formation of reliable, metallurgically-composible joints to precious metal bonding pads such as gold.

In general, two types of alloy mechanisms can minimize gold leaching from bonding pads. In each case, the solidus temperature of the solder must exceed the bonding temperature at the bonding interface when some small incremental quantity of gold is absorbed into the solder at the bonding interface, or when some small incremental quantity of solder diffuses into the gold bonding pad, or both.

In this regard, two different solder alloys are especially notable for application to fluxless solder-bumps. For solder alloys containing both lead and gold, the solidus temperature for certain compositions increases dramatically as the gold content is increased. The same is true for solder alloys containing both lead and indium.

As part of this program, chips metallized with both gold/lead/silver and indium/lead/silver solder-bumps were evaluated. It is believed that these two solder compositions, of all possible solder compositions, are best suited for fluxless solder-bump materials, on the basis of their particular combination of desirable material properties, including softness, ductility, convenient melting point, good corrosion resistance, low vapor pressure, and minimization of gold leaching effects.

During assembly, the chips are tacked down to bonding pads by means of an ultrasonic die bonder equipped with a combination ultrasonic/vacuum pick-up tool. This bonding operation deforms the soft-solder portion of the bumps, giving reliable contact to multiple-bumped devices. A heating operation then reflows the solder, forming annealed, alloyed bonds to the interconnection pads. Solder wetting is localized at the ultrasonically-scrubbed regions of the bonding pads.

This flux less solder-bump method is not penalized by any of the objections outlined in Section III C for beam-lead or beam-tape technologies. In addition, most of the disadvantages of flip-chip technology are also eliminated.

### Advantages of fluxless solder-bump technology include:

- o Simplified solder-bump processing

Maximum of one masking step (might be combined with window etch mask step).

- o Simplified chip joining.

Uncoated gold bonding pads are used (no solder pre-coat, no flux pre-coat, no solder dams, lower temperature processing, no flux residue removal).

- o No flux residues

Simplifies contamination control.

- o Metallurgically-compatible interfaces with gold films.

- Well-controlled bump dimensions.

Well-controlled bump dimensions are provided, with the potential for bump extension to the edge of the chip for easier chip alignment and bond inspection.

o Bumps with magnetic properties can be provided to facilitate chip handling and storage.

It is convenient to employ either nickel or nickel/cobalt alloy as the pedestal material, thus imparting magnetic properties to the bumps. These metals are easy to plate, in addition to being rigid and corrosion-resistant.

Magnetic properties are useful for convenience of chip handling and storage.

The general fluxless solder-bump metallization process itself is conceptually quite flexible, and can be modified to suit particular process preferences.

### V. METALLURGICAL INVESTIGATION

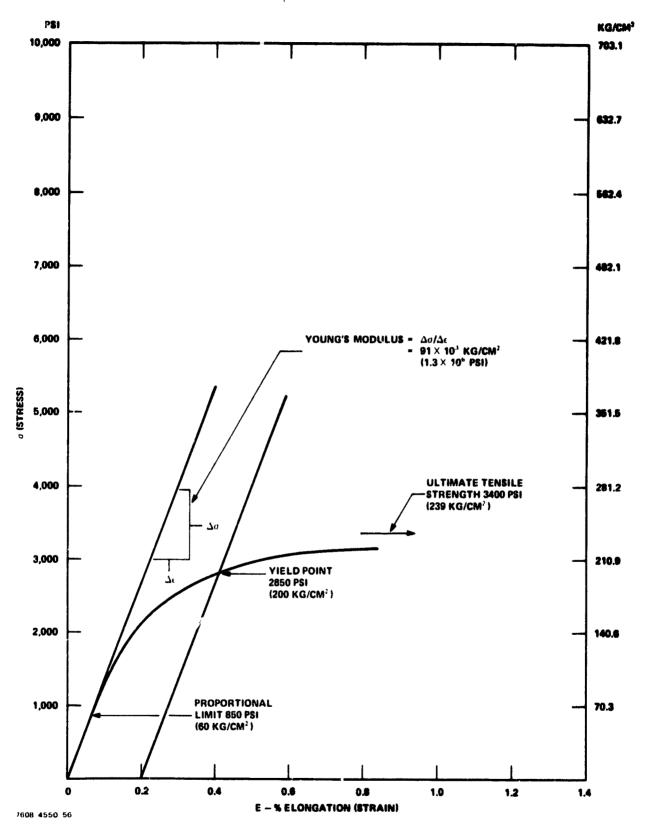

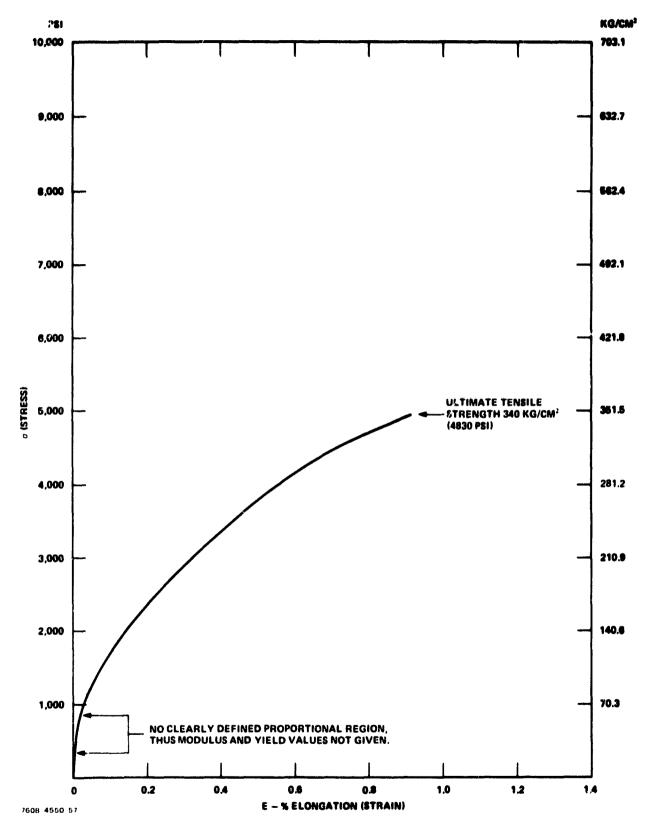

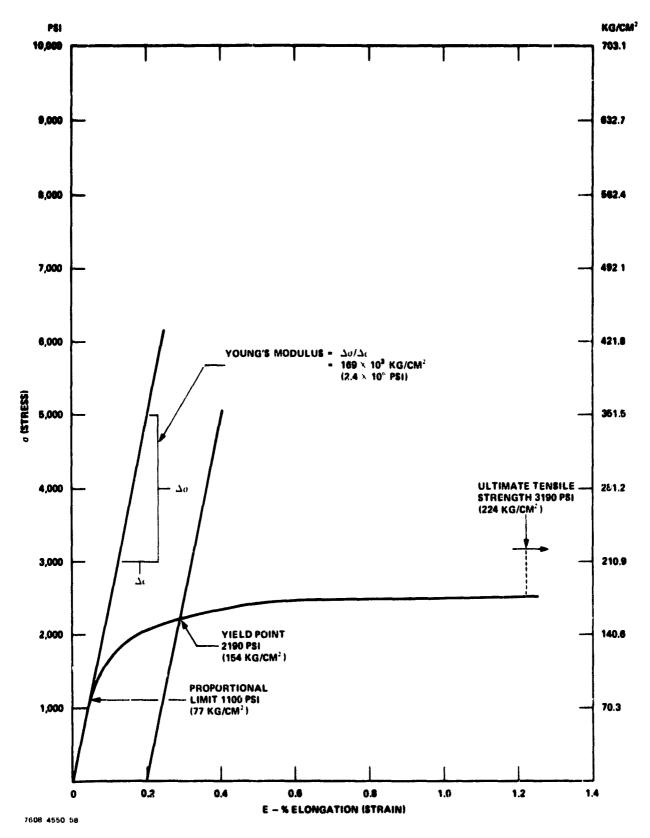

Data has been gathered on metallurgical properties of five selected solder alloys containing gold/lead and indium/lead, in addition to 90 lead/10 tin for the purpose of comparison, as shown in Figure 10. These measurements were necessary because of a paucity of pertinent available published data. For most trinary alloys especially, such data is not available.

The first three columns give alloy composition, liquidus/solidus temperatures, and tensile strength. The fourth column shows Young's Modulus, which is the stress required to produce unit strain (or unit change-of-length). The fifth column gives hardness (Rockwell W). Since the equipment available could not reliably measure hardnesses greater than 100 Rockwell W, quantitative measurements are shown for only three alloys, and relative order of hardness for all six. The last column shows percent elongation at the break point.

The measured liquidus/solidus temperatures of the binary lead/indium alloy are lower than expected, and are at variance somewhat with published data.

### A. Test Sample Preparation Method

The starting materials used are detailed below.

### Starting Materials

| Metal  | Purity | Supplier        | Comments                                       |

|--------|--------|-----------------|------------------------------------------------|

| Lead   | M5N5   | Alfa Products   | Remelted to further eliminate oxide formation. |

| Indium | M5N    | Apache Chemical |                                                |

| Tin    | M5N    | Apache Chemical |                                                |

| Gold   | M5N    | Apache Chemical |                                                |

| Silver | M6N    | Apache Chemical |                                                |

| ALLOY<br>(COMPOSITION IN WEIGHT %)    | MELTING POINT OR<br>LIQUIDUS/SOLIDUS<br>TEMPERATURE | TENSILE<br>STRENGTH<br>@ 25°C       | YOUNG'S<br>MODULUS<br>@ 25°C                               | HARDNESS @ 25°C<br>(3.18 MM DIAMETER<br>TOOL)     | ELONGATION<br>AT BREAK<br>POINT @ 25°C |

|---------------------------------------|-----------------------------------------------------|-------------------------------------|------------------------------------------------------------|---------------------------------------------------|----------------------------------------|

| 15.0 GOLD, 82.9 LEAD,<br>2.1 SILVER   | 213°C                                               | 5,450 PSI<br>383 KG/CM <sup>2</sup> | 2.9 × 10 <sup>6</sup> PSI<br>200,000<br>KG/CM <sup>2</sup> | S                                                 |                                        |

| 15.3 GOLD, 84.7 LEAD                  | 215°C                                               | 9,180 PSI<br>645 KG/CM <sup>2</sup> | 3.0 × 10° PSI<br>210,000<br>KG/CM <sup>2</sup>             | ٧                                                 | <b>%</b> 8:0                           |

| 12.5 GOLD, 85.0 LEAD,<br>2.5 SILVER   | 214ºC                                               | 4,830 PSI<br>340 KG/CM²             | (2.7 × 10° PSL)<br>(190,000<br>KG/CM²)                     | •                                                 | 1.5%                                   |

| 32.9 INDIUM, 64.4 LEAD,<br>2.7 SILVER | 199–247°C                                           | 4,126 PSI<br>290 KG/CM <sup>2</sup> | 1.3 × 10° PSI<br>91,000<br>KG/CM²                          | 3<br>110 ROCKWELL W<br>@ 15 KG LOAD               | *                                      |

| 33.8 INDIUM, 66.2 LEAD                | 202-241°C                                           | 3,283 PSI<br>231 KG/CN <sup>2</sup> | 1.3 / 10° PSI<br>91,000<br>KG/CM²                          | 85 ROCKWELL W<br>@ 15 KG LOAD                     | 2.5%                                   |

| 90.0 LEAD, 10.0 TIN                   | 277–303°C                                           | 3,190 PSI<br>224 KG/CM <sup>2</sup> | 2.3 × 10° PSI<br>160,000<br>KG/CM <sup>2</sup>             | (1)<br>(SOFTEST)<br>60 ROCKWELL W<br>@ 15 KG LOAD | 70%                                    |

Some Metallurgical Properties of Selected Solder Alloys Figure 10.

The appropriate amount of each metal was weighed on a Mettler Balance and transferred to a  $15 \times 20$  mm quartz vacuum tube having a 12 mm O.D. restricted neck. The tubes were then evacuated to a pressure no greater than 5 microns and then sealed while under vacuum. The sealed ampules were then continuously coated in a small oven for one (1) hour at  $500^{\circ}$  –  $550^{\circ}$ C. After this fire period, the tubes were removed from the oven and allowed to reach room temperature.

The alloys were cast into the dumbbell-shaped samples required for Instron stress-straining analysis using a graphite mold.

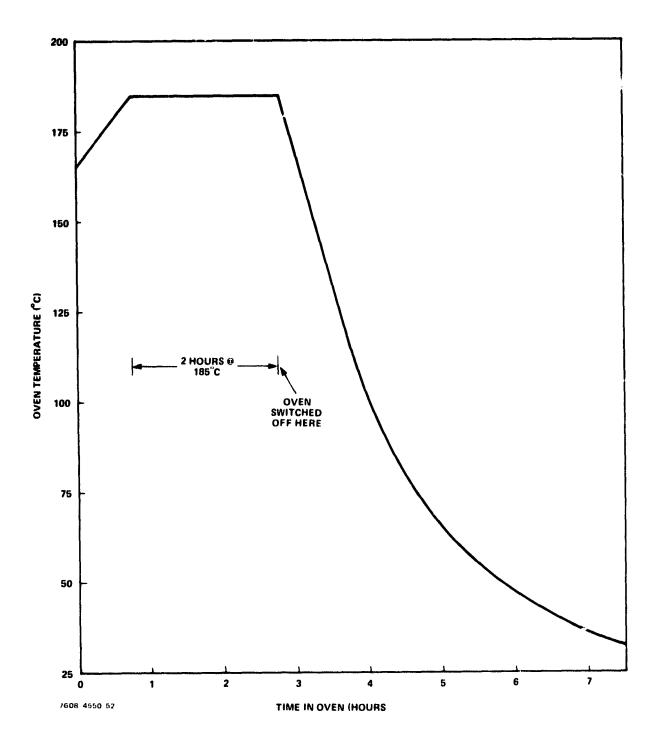

To cast the sample, the evacuated tubes were cracked at the top, and quickly reheated to 400°C. along with the graphite mold. The mold was removed from the oven, and the liquid alloy poured into the mold and allowed to cool to room temperature. The cast sample was then removed from the mold, sanded to remove flashing, and drilled to accept the pins on the Instron machine. All samples were then annealed at 185°C. for 2 hours in a vacuum oven followed by overnight cooling in the turned-off oven. A time-temperature schedule of the annealing process is shown in Appendix I, Graph A.

The samples were then submitted for stress/strain analysis in the Instron machine. Following these tests, the samples were cut apart and subjected to hardness and melting temperature determinations.

## B. <u>Liquidus/Solidus Temperatures</u>

Liquidus/solidus temperatures were determined by using a differential scanning calorimeter (DSC). These results are listed below.

## Liquidus/Solidus Determination (DSC)

| Allo | y # Composition - Wt. %    | Liquidus/Solidus Temp. OC. | Type of Melting Point |

|------|----------------------------|----------------------------|-----------------------|

| 1    | 15.0 Au - 82.9 Pb - 2.1 Ag | 213                        | Sharp with tail       |

| 2    | 15.3 Au - 84.7 Pb          | 215                        | Sharp                 |

| 3    | 12.5 Au - 85.0 Pb - 2.5 Ag | 214                        | Sharp with tail       |

| 4    | 32.9 In - 64.4 Pb - 2.7 Ag | 199 - 247                  | Broad                 |

| 5    | 33.8 In - 66.2 Pb          | 202 - 241                  | Broad                 |

| 6    | 90.0 Pb - 10.0 Sn          | 277 - 303                  | Medium wide           |

Alloy #2 is a gold-lead eutectic and thus has a very sharp melting point. Adding silver to the eutectic mixture (alloys #1 and #3) reduced the melting temperature only slightly and produced a small broadening of the melting range. The lead-indium alloy #5 exhibited a rather broad melting range (202 - 241°C) and adding a small amount of silver (alloy #4) expanded this range slightly at both ends (199 - 247°C). The lead-tin (alloy #6) had a medium wide melting range (277 - 303°C) as expected.

# C. Stress/Strain Analysis

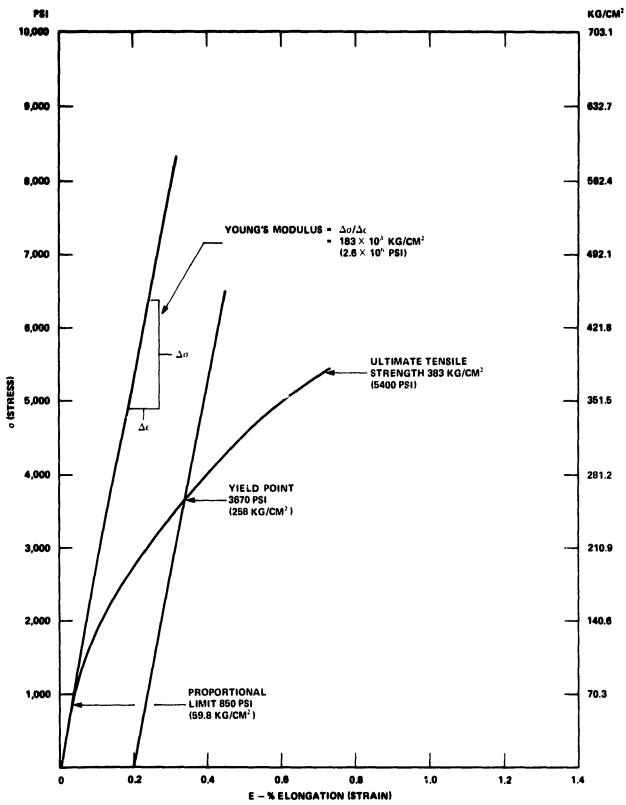

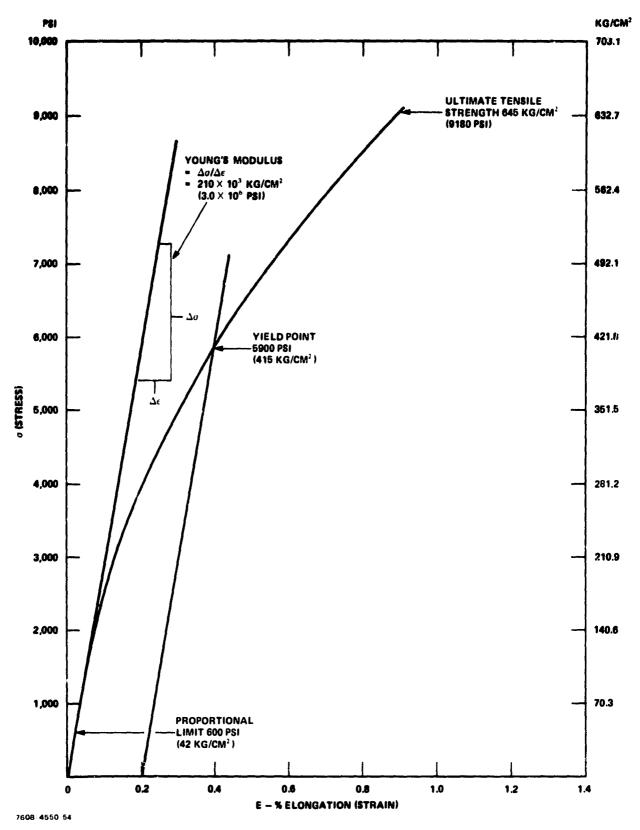

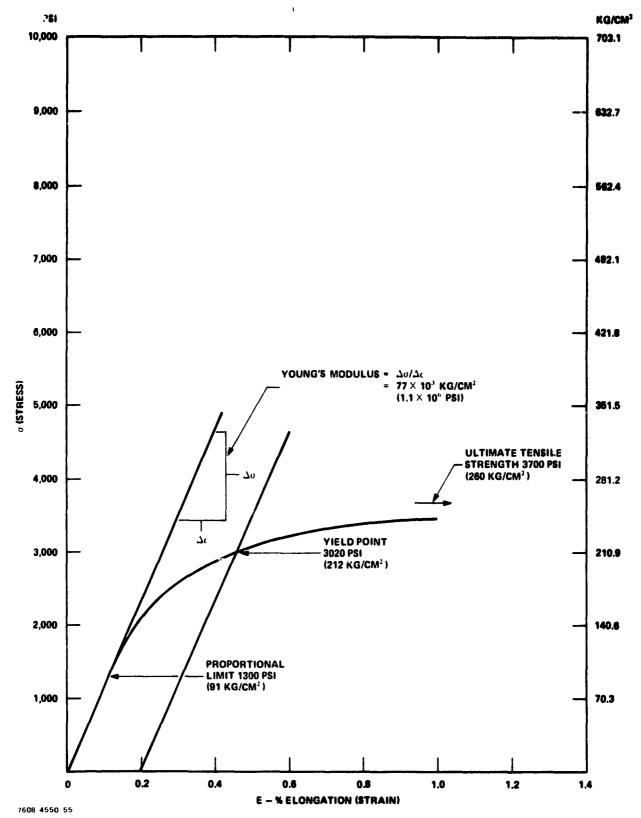

All stress/strain analysis work was performed using dumbbell-shaped samples in conjunction with an Instron machine. To supplement the numerical data, a representative graph is shown in Appendix I for stress/strain measurements on each alloy. Since three samples of each alloy were prepared, individual numbers on the graphs may not agree with the value in the data chart, which represents the average value of all readings taken. The numerical data is summarized below.

## Stress/Strain Analysis

| Alloy # | Composition (wt.%)         | Young's Modulus<br>X 10 <sup>3</sup> kg/cm <sup>2</sup> | Ultimate Tensile Strength (kg/cm²) |

|---------|----------------------------|---------------------------------------------------------|------------------------------------|

| 1       | 15.0 Au - 82.9 Pb - 2.1 Ag | 200                                                     | 383                                |

| 2       | 15.3 Au - 84.7 Pb          | 210                                                     | 645                                |

| 3       | 12.5 Au - 85.0 Pb - 2.5 Ag | 190 (est)*                                              | 340                                |

| 4       | 32.9 In - 64.4 Pb - 2.7 Ag | 91                                                      | 290                                |

| 5       | 33.8 In - 66.2 Pb          | 91                                                      | 231                                |

| 6       | 90 0 Pb - 10.0 Sn          | 160                                                     | 224                                |

<sup>\*</sup>No real proportional limit from which to calculate Young's Modulus.

In discussing this data in more detail, refer to Appendix 1. Graph #4 shows the stress/strain curve for the lead-indium alloy #5. By examining the stress/strain curve in Graph #4, it can be seen that the first point reached is the proportional limit, in this case 60 kg/cm<sup>2</sup>. In this region, strain is proportional to stress up to the proportional limit. The slope of the stress/strain curve is, by definition, the Young's Modulus of the material in this example 91,000 kg/cm<sup>2</sup>. The next point on the graph is the yield point (200 kg/cm<sup>2</sup>). The region between the proportional limit and the yield point is referred to as the elastic region. In other words, if the stress is removed at any point up to the yield point, the material should return to its original length. Beyond the yield point, should the stress be removed, the material will exhibit a "permanent set". The yield point is arbitrarily defined to occur at 0.2% elongation for the purpose of this work. A line drawn parallel to the proportional region of the curve and intersecting the percent elongation axis at 0.2% then defines the yield point of the alloy. However, the arbitrary nature of the 0.2% criterion, especially as applied to soft alloys, must be emphasized. The final point on the graph is the ultimate te. sile strength or breaking point of the sample and indicates the stress required to break the dumpbell-shaped sample into two halves (239 kg/cm $^2$  in Graph  $^{\#}4$ ).

By comparing each of the six graphs, some insight can be gained into the nature of each of the materials. In general, the greater the modulus of the alloy, the more brittle is the sample. For example, all alloys containing gold tended to be substantially more brittle than those without gold; thus Graphs #1, #2, and #5 indicate higher modulus readings. It may be noted on Graph #5 that no clearly defined proportional region occurred, thus preventing computation of a modulus for this alloy. This lead-gold-silver alloy is very "rubbery" in nature and thus has no proportional region. Note also that the two lead-gold-silver alloys (Graphs #1 and #5) tend to be more elastic than the lead-gold alloy (Graph #2) as is evidenced by a greater tangential slope in the elastic region of the lead-gold alloy (Graph #2) as opposed to the lead-gold-silver alloys (Graphs #1 and #5).

Comparing ultimate tensile strengths, it can be seen that addition of gold to the lead alloys substantially increases tensile strength. The lead-gold alloy #2 has the highest strength reading (645 kg/cm<sup>2</sup>). Addition of silver (alloys #1 and #3) reduced the tensile strength to approximately 340 kg/cm<sup>2</sup>. The lead-indium alloy #5 had a tensile strength of 231 kg/cm<sup>2</sup> and addition of silver to this alloy increased the reading to 290 kg/cm<sup>2</sup>. The lead-tin alloy #6 has a tensile strength of 224 kg/cm<sup>2</sup>, similar to that of the lead-indium alloy.

Some insight can also be gained into the brittleness of the alloys by comparing the total percent elongation of the material at the breaking point. These values are given in order of decreasing stretch before break in the table below.

### Percent Total Elongation at Breaking Point

| Alloy # | Composition - wt. %        | % Total Elongation at Break Point |

|---------|----------------------------|-----------------------------------|

| 6       | 90.0 Pb - 10.0 Sn          | 10.0                              |

| 4       | 32.9 In - 64.4 Pb - 2.7 Ag | 4.0                               |

| 5       | 33.8 In - 66.2 Pb          | 2.5                               |

| 3       | 85.0 Pb - 12.5 Au - 2.5 Ag | 1.5                               |

| 1       | 82.9 Pb - 15.0 Au - 2.1 Ag |                                   |

| 2       | 84.7 Pb - 15.3 Au          | 0.9                               |

The lead-tin alloy exhibits the greatest strain before breaking. Note that adding silver to the lead-indium alloy increased the total percent elongation compared to the lead-indium alloy alone. Again, the alloys containing gold have the least percent elongation at break. The silver-lead-gold alloys clearly show more elastic behavior as compared to the lead-gold alloy alone.

### D. Hardness Measurements

All hardness tests are Rockwell Superficial Hardness measurements. The Rockwell Superficial hardness test involves applying first a minor load to a hard steel ball, of known diameter, into the surface of the metal being tested. Next a major load of 15, 30, or 45 kg is applied and then released. After a specific time period has elapsed, a reading is taken with the major load released, but the minor load still applied. This reading represents the difference in penetration between the minor load alone and the minor load after the major load has been applied and released. The larger the number, the harder the material. Due to the fact that the largest diameter ball available was 3.18mm, the six alloy samples had to be run using 3 different major load scales. This makes the data more difficult to compare. The alloys have been listed below in order of increasing hardness based on the data taken.

Superficial Rockwell Hardness Values (3.18 mm Diameter Ball - W Scale)

| Alloy # | Composition - wt.%         | Major Load | Reading |         |

|---------|----------------------------|------------|---------|---------|

| 6       | 90.0 Pb - 10.0 Sn          | 15 Kg.     | 50      | Softest |

| 5       | 66.2 Pb - 33.8 In          | 15 Kg.     | 85      |         |

| 4       | 64.4 Pb - 32.9 In - 2.7 Ag | 15 Kg.     | 110     |         |

| 3       | 85.0 Pb - 12.5 Au - 2.5 Ag | 30 Kg.     | 80      |         |

| 1       | 82.9 Pb - 15.0 Au - 2.1 Ag | 45 Kg.     | 55      |         |

| 2       | 84.7 Pb - 15.3 Au          | 45 Kg.     | 109     | Hardest |