# Evaluation of Level-Shifted and Phase-Shifted PWM Schemes for Seven Level Single-Phase Packed U Cell Inverter

Mohd Tariq, Mohammad Meraj, Abdul Azeem, Ali I. Maswood, Atif Iqbal, and Bharatiraja Chokkalingam

Abstract—An evaluation of level shifted and phase shifted triangular and sawtooth carrier modulation schemes for a seven level packed U cell (PUC) inverter is presented in this paper. The investigated PUC is the recently introduced topology for multilevel inverter having reduced switch count in comparison to the conventional topologies of multilevel inverters. The PUC inverter has six switches for 7 level inverter which is very less in comparison to the conventional topologies. In this paper, the level-shifted pulse width modulation (LS-PWM) and phase-shifted PWM (PS-PWM) for triangular and sawtooth carrier are presented and compared. A comparative harmonic analysis for all the cases is performed and results are presented in the paper. The difference in harmonics of the two modulation methods given by the theoretical approach for both the carrier is validated by the experimental results. DC voltage controller and load current controller of the PUC inverter are also designed and presented. The investigated PUC topology is tested in dynamic and steady state conditions and results obtained are presented. The analysis is done and validated using simulation in MATLAB<sup>®</sup> Simulink environment and experimental approaches using FPGA platform.

*Index Terms*—Level shift, multilevel inverter, modulation, phase shift, PI controller, PUC inverter.

#### I. INTRODUCTION

In the last two decades the risk and reality of environmental degradation have become more apparent. Fossil fuel which is the main source of energy, has led to the degradation of environment. For all these degradation and problem in environment, renewable energy sources can provide a solution [1], [2]. To meet the environmental challenges and depletion of fossil fuels, Photovoltaic (PV) source presents a highly attractive energy source

during the last two decades. Multilevel inverter is required for connecting the PV sources which generates DC power to AC loads. Multilevel inverter circuits switch multiple DC sources in sequence at fundamental frequency to generate nearly sinusoidal stepped AC output voltage [3], [4].

In literature many traditional multilevel converters topologies like neutral point clamped converters (NPC), flying capacitors converters (FCC) and classic cascaded H-bridges [4]-[6] are available which enhanced the harmonic profile of the voltage and current but they offers high number of switching devices and capacitors which increases the cost and decreases the reliability. In [7], many new topologies of multilevel converter is given which offers less no. of switching device but the Packed U Cell (PUC) multilevel inverter topology is symmetrical and easy to control. For low and medium power applications where a PV panel installed at home is connected to local grid etc., a single-phase transformer-less DC-AC converter with minimum number of switch devices, capacitors and DC sources are required [8], [9]. PUC topology introduced in [10], [11] is working with only one DC source and having high power quality using a small number of passive and active components. The capacitors acts as auxiliary DC source in the PUC inverter. PUC inverter is suggested for PV application in [12] as it offers high efficiency. Many papers on control of PUC inverter are available in literature [13], [14], but a comparative analysis of different modulation carrier schemes is missing in the literature. Analysis of different carriers is essential as in local grid connected PV applications, the total harmonic distortion (THD) generated by the switching element should be minimum [15].

There are two modulation methods in the multicarrier PWM schemes: level shifted PWM (LS-PWM) [16] and phase shifted PWM (PS-PWM) [17]. Combination of the level-shifted PWM (LS-PWM) and the phase-shifted PWM (PS-PWM) is reported in [18]. It is called "level- and phase-shifted PWM (LPS-PWM)". The LPS-PWM realizes low voltage ripple on the capacitors. In [19], the comparison between the Phase-Shifted PWM and Level-Shifted PWM is done on a Modular Multilevel Single Delta Bridge Converter (SDBC) Inverter whereas in the proposed work the comparison is done on recently introduced Packed U Cell (PUC) Inverter. Since till date no such work is available on PUC inverter wherein different modulation techniques have been evaluated, hence in the proposed work, the authors wanted to investigate the effects of different modulation techniques/methods on the PUC inverter. In this paper a comparison between triangular and sawtooth carrier is done

Manuscript received January 3, 2018. This work is supported by NPRP-EP grant # X-033-2-007 from the Qatar National Research Fund (a member of Qatar Foundation). (Corresponding author: Atif Iqbal.)

M. Tariq and A. I. Maswood are with the School of Electrical and Electronic Engineering, Nanyang Technological University, 639798, Singapore, and M. Tariq is presently with the Department of Electrical Engineering, Aligarh Muslim University, Aligarh, 202002, India (e-mail: tariq.iitkgp@gmail.com; eamaswood@ntu.edu.sg).

M. Meraj and A. Iqbal are with the Department of Electrical Engineering, Qatar University, Doha, 2713, Qatar (e-mail: meraj@qu.edu.qa; atif.iqbal@ qu.edu.qa).

A. Azeem is with the Department of Electrical Engineering, Aligarh Muslim University, Aligarh,202002, India (e-mail: azeem.abdul25@gmail.com).

B. Chakkolingam is with the Department of Electrical Engineering SRM University, Chennai, 603203, India (e-mail: bharatiraja@gmail.com).

Digital Object Identifier 10.24295/CPSSTPEA.2018.00023

using level shifted and phase shifted PWM methods for PUC inverter. This study is important keeping in view the need to understand the operation of PUC inverter under different modulation schemes for achieving low THD.

The rest of the paper is organized as follows: In Section II operation of PUC inverter is explained. The generalized PWM spectral modeling is presented in Section III. Analysis of phase shifted and level shifted for triangular carrier is presented in Section IV whereas in Section V, analysis of phase shifted and level shifted for sawtooth carrier is presented. Section VI details the controller design for dc link and capacitor voltages and load current. Simulation and experimental results are presented in Section VII and VIII respectively. Conclusion is given in Section IX.

#### II. OPERATION OF PUC INVERTER

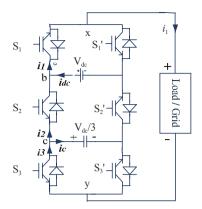

A seven level single-phase voltage source inverter with packed U-cell topology is shown in Fig. 1. This is called Packed U-cell because each unit of the inverter is of U shape. Depending upon the number of capacitors in the PUC topology different level of voltages can be achieved. In the PUC topology two capacitors (one is DC link capacitor and the second is the floating or flying or auxiliary capacitor) have been used to obtain seven levels (V<sub>dc</sub>, 2V<sub>dc</sub>/3, V<sub>dc</sub>/3, 0, -V<sub>dc</sub>/3, -2V<sub>dc</sub>/3, -V<sub>dc</sub>). The Voltage across second capacitor (C<sub>2</sub>) i.e. V<sub>b</sub> must be maintained at one-third of the voltage of the first capacitor (C<sub>1</sub>) i.e. V<sub>a</sub>. The relation between number of voltages level achieved and number of auxiliary capacitors used can be represented by (1).

$$N_{v} = 2^{Nc+2} - 1 \tag{1}$$

Where:  $N_v$  is number of voltage levels and  $N_c$  is number of auxiliary capacitors used.

The numbers of devices for different types of inverters (NPC, FLC, CHB and PUC) are shown in TABLE I. Six IGBTs have been used in the PUC topology for achieving 7 levels. These 6 IGBTs are subdivided into two legs, hence only three switches form one leg. Number of possible states can be given by (2).

$$N_{\rm p} = 2^{\rm Ns} \tag{2}$$

Where,  $N_p$  is number of possible states and  $N_s$  is number of switches in one leg.

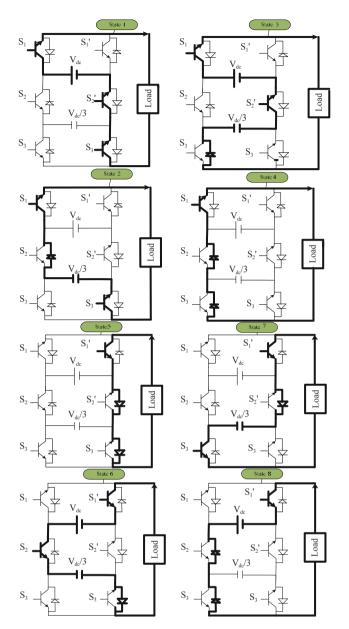

There are 8 possible switching states in a single-phase PUC inverter as shown in Fig. 2 and listed in TABLE II. It is seen that there are three positive levels and three negative levels while two states yield zero voltage, namely state 4 and state 5. Zero voltage is produced when load is short circuit either though main switches or complimentary switches.

The switching function of the PUC inverter can be defined by (3) and the inverter output voltage can be defined by (4). The points x, b, c and y are shown in Fig. 1.

Based on the switching function shown in TABLE II, each voltage can be represented as given in (5) to (8).

Fig. 1. Packed U-cell converter topology.

TABLE I

Seven Level Single Phase Inverter Topologies

| Components             | NPC | FLC | CHB | PUC |

|------------------------|-----|-----|-----|-----|

| Power Switches (IGBTs) | 24  | 24  | 12  | 6   |

| Capacitors             | 6   | 30  | 3   | 2   |

| Clamping Diodes        | 20  | 0   | 0   | 0   |

$$\begin{array}{ccccccc} S_{j}=0 & \text{if} & S_{j} & \text{is} & \text{Off} \\ 1 & \text{if} & S_{j} & \text{is} & \text{On} \end{array} \qquad j=1,2,3 \tag{3}$$

$$V_{xy} = V_{xb} + V_{bc} + V_{cy}$$

(4)

$$V_{xb} = V_1 (S_1 - 1)$$

(5)

$$V_{bc} = (V_1 - V_2)(1 - S_2)$$

(6)

$$V_{cy} = V_2 (1 - S_3) \tag{7}$$

$$V_{xy} = V_1 (S_1 - S_2) + V_2 (S_2 - S_3)$$

(8)

#### III. GENERALIZED PWM SPECTRAL MODELING

The distortion in the output current or voltage waveform with respect to an ideal sine wave is often used in comparing the effectiveness of different modulation processes. Since the output voltage of an inverter is a periodic function having time period (T), the root-mean-square (RMS) value of the function can be defined as:

$$V_{rms} = V_{1,rms} \sqrt{1 + THD^2}$$

(9)

From (9), it is to be noted that if the THD is zero then the RMS value of the waveform is equal to the fundamental RMS voltage. Hence, it is clear that the modulation technique has to be designed in such a way so as to obtain the minimum THD or ideally zero THD. Moreover, when the inverter is connected to the induction motor operating pump for standalone solar PV pumping application, it is to be noted that the total copper loss

Fig. 2. Switching states for single-phase AFLC/PUC.

TABLE II Switching Combination for One Leg of PUC

| State | Voltage                         | $\mathbf{S}_1$ | $S_2$ | $S_3$ |

|-------|---------------------------------|----------------|-------|-------|

| 0     | $V_a$                           | 1              | 0     | 0     |

| 1     | Va-Vb                           | 1              | 0     | 1     |

| 2     | $V_b$                           | 1              | 1     | 0     |

| 3     | 0                               | 1              | 1     | 1     |

| 3'    | 0                               | 0              | 0     | 0     |

| 4     | -Va                             | 0              | 0     | 1     |

| 5     | V <sub>b</sub> - V <sub>a</sub> | 0              | 1     | 0     |

| 6     | -V <sub>b</sub>                 | 0              | 1     | 1     |

due to the harmonic content in the quasi-square-wave inverter can be 0.5-1% of the rating. Hence all these leads to the formulation of modulation strategies for reducing the component of harmonics in the inverter output voltage.

The mathematical model is developed for PWM triangular and sawtooth carrier signals for the defined reference here for better understanding of the subject. The PWM output spectrum is described using the analytical models when different carrier signals (triangular/sawtooth) are used.

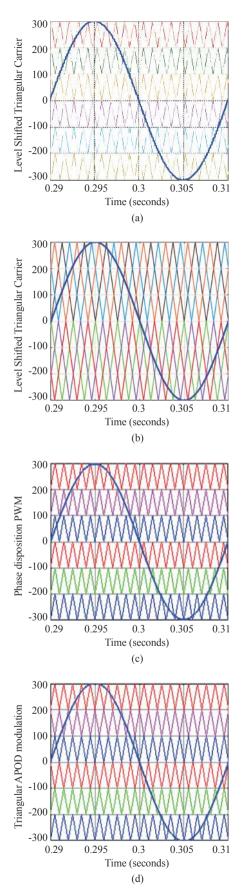

Fourier series is used to represent a periodic function. For the presented application, Fourier analysis is performed on the PWM waveform for 50 Hz (20 milliseconds period) which corresponds to one cycle of the reference. The switching point as shown in the pulse width modulation waveform of Fig. 6(I)(a), Fig. 6(I)(b), Fig. 6(I)(c), and Fig. 6(I)(d) is described using the trigonometry equation given in (10). The trigonometric equation involves both the linear function of time (which basically represent carrier signal) and a sinusoidal reference.

$$s(t) = S_0 + S_1 \cos(2\pi f_1 t + \theta_1)$$

(10)

In the next two sections, (10) is used for doing the spectral analysis of various pulse width modulation methods. Depending upon the application under study, in (10),  $S_0$  and  $S_1$  are set to zero. For solving (10), a new two-dimensional function (double Fourier series for decomposing the function) given in (11) is introduced in the literature wherein the reference fundamental and the carrier frequency are corresponding to an independent variable respectively [20]. A periodical 2 (two) dimensional function f (x, y) having periodicity in x and y both, with a time period equal to  $2\pi$  for both the axes, is represented by a double Fourier series which is mathematically expressed here in (11).

$$f(x, y) = \frac{A_{00}}{2} + \sum_{n=1}^{+\infty} \left( A_{0n} \cos ny + B_{0n} \sin ny \right) + \left( A_{m0} \cos mx + B_{m0} \sin mx \right) + \sum_{m=1}^{+\infty} \sum_{n=\pm 1}^{\pm\infty} \left( A_{mn} \cos(mx + ny) + B_{mn} \sin(mx + ny) \right)$$

(11)

Where the coefficients  $A_{mn}$  and  $B_{mn}$  are defined as follows in (11) and (12)

$$A_{mn} = \frac{1}{2\pi^2} \int_{0}^{2\pi} \int_{0}^{2\pi} f(x, y) \cos(mx + ny) \, dx \, dy, \quad (12)$$

$$B_{mn} = \frac{1}{2\pi^2} \int_{0}^{2\pi} \int_{0}^{2\pi} f(x, y) \sin(mx + ny) \, dx \, dy.$$

(13)

In (11), the PWM waveform contains the fundamental sine, the DC and many harmonics components described (grouped) as follows:

- (i) Carrier frequency and its associated harmonics.

- (ii) Sideband harmonics of the carrier and its associated harmonics. The sideband harmonics appears because of the modulated reference.

For sawtooth carrier modulation the sideband harmonic amplitude at frequency  $f = mf_c + nf_1$  equals to as given in (14),

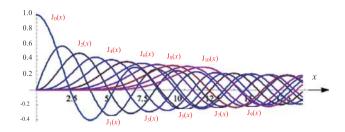

whereas for triangular carrier modulation it equals to as given in (15). In (14) and (15), the  $J_n(z)$  which is a Bessel function is defined as given in (16):

$$\frac{J_n(m\pi M)}{m\pi} \tag{14}$$

$$\frac{2}{m\pi}J_n\left(\frac{m\pi M}{2}\right) \tag{15}$$

$$J_{n}(z) = \frac{j^{-n}}{\pi} \int_{0}^{2\pi} e^{jz\cos\theta} e^{jn\theta} d\theta$$

(16)

In (16), the argument z can be a complex or real number. If z is real, the function will also be real. Whereas, "n" will be an integer always. Bessel functions  $J_0(x)$  through  $J_{10}(x)$  is shown in the Fig. 3. The double Fourier series and Bessel functions are used in the analysis of the triangular and sawtooth carrier modulation techniques in the next two sections.

# IV. TRIANGULAR CARRIER LEVEL SHIFTED AND PHASE SHIFTED PWM ANALYSIS

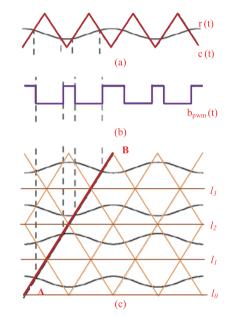

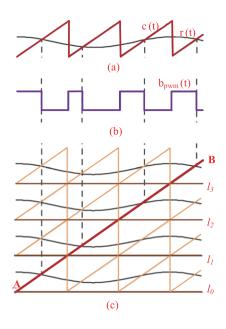

The triangular carrier based modulation scheme is given in Fig. (4) wherein the formulation of double Fourier series is shown. Fig. 4(a) shows the triangular and reference signals. Fig. 4(b) shows the resulting PWM output which is expressed mathematically in (17). As shown in Fig. 4(c) the original carrier along with the reference are sequenced in the correct and inverted position alternatively. The stacked carriers are mathematically written as c(t),  $2C_m-c(t)$ ,  $2C_m+c(t)$ ,  $4C_m-c(t)$ , whereas the stacked references can be mathematically expressed as r(t),  $2C_m - r(t)$ ,  $2C_m + r(t)$ ,  $4C_m - r(t)$ . As seen in Fig. 4(c), line AB is the extension of the rising edge of the first triangle of the original carrier, c(t). It can be observed that the PWM generated by the interaction between the original carrier and reference signal and PWM generated with the intersection of the line AB with the references shifted (stacked).

$$b_{pwm}(t) = D + \frac{M}{2} \cos\left(\omega_{l}t + \theta_{1}\right) + \sum_{m=1}^{+\infty} \frac{2}{m\pi} J_{0}\left(\frac{m\pi M}{2}\right) \sin\left(Dm\pi\right) \cos\left[m\left(\omega_{c}t + \theta_{c}\right)\right]$$

(17)

$$+ \sum_{m=1}^{+\infty} \sum_{n=\pm 1}^{\pm\infty} \frac{2}{m\pi} J_{n}\left(\frac{m\pi M}{2}\right) \sin\left(\frac{(2Dm+n)\pi}{2}\right) . \cos\left[m\left(\omega_{c}t + \theta_{c}\right) + n\left(\omega_{l}t + \theta_{1}\right)\right].$$

The phase voltage of an inverter with natural sampled PWM and triangular carrier can be described by (18). (18) is derived in [21] using the expression given in the works of Black in [22]. The three terms in (18) are explained as: a) Term 1 is directly proportional to the modulation index and it represents the fundamental frequency amplitude; b) Term 2 represents the carrier frequency harmonics amplitude and multiples of the carrier frequency and it is due to the presence of the sin (mt/2); c) Term 3

Fig. 3. Bessel functions plot for  $J_0(x)$  to  $J_{10}(x)$  [20].

Fig. 4. Triangular carrier and development of a double Fourier series.

gives the amplitudes of the harmonics in the sidebands around each multiple of the carrier frequency.

$$F(t) = \frac{MV}{2} \cos\left(\omega_F t\right) + \frac{2V}{\pi} \sum_{m=1}^{\infty} J_o\left(mM\frac{\pi}{2}\right) \sin\left(m\frac{\pi}{2}\right) \cdot \cos\left(m\omega_c t\right)$$

$$+ \frac{2V}{\pi} \sum_{m=1}^{\infty} \sum_{n=\pm 1}^{\pm \infty} \frac{J_n\left(mM\frac{\pi}{2}\right)}{m} \cdot \sin\left((m+n)\frac{\pi}{2}\right) \cos\left(m\omega_c + n\omega_F t\right)$$

(18)

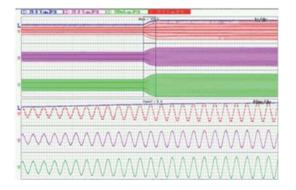

Fig. 6(I)(a), Fig. 6(I)(b), Fig. 6(I)(c), and Fig. 6(I)(d), shows level shifted and phase shifted triangular carrier and sinusoidal reference signal generation of PWM signals for IGBT switches of inverter.

## V. Sawtooth Carrier Based Level Shifted and Phase Shifted PWM Analysis

The sawtooth carrier based modulation scheme is given in Fig. 5 wherein the formulation of double Fourier series is shown. Fig. 5(a) shows the triangular and reference signals. Fig. 5(b) shows the resulting PWM output which is expressed mathematically in (19). As shown in Fig. 5(c) the original carrier along with the reference are stacked equidistantly. The stacked carriers are

Fig. 5. Sawtooth carrier and development of a double Fourier series.

mathematically written as c(t),  $C_m + c(t)$ ,  $2C_m + c(t)$ , whereas the stacked references can be mathematically expressed as r(t),  $C_m + r(t)$ ,  $2C_m + r(t)$ . As seen in Fig. 5(c), line AB is the extension of the first slope of the original sawtooth signal. The lines  $l_1$ ,  $l_2$ ,  $l_3$  and  $l_4$  (shown horizontally) is separating the different stacked carriers with a spacing of  $C_m$  between them. It can be observed that the PWM generated by the interaction between the original carrier and reference signal and PWM generated with the intersection of the line AB with the references shifted (stacked).

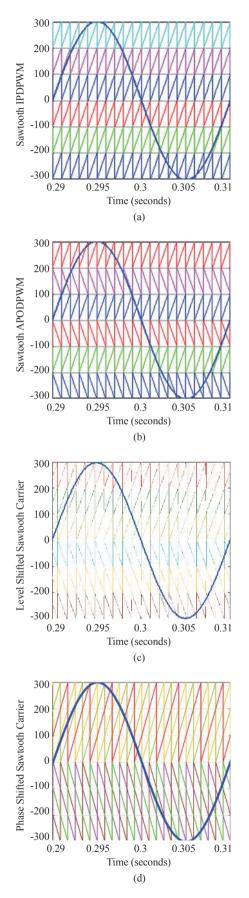

The sawtooth carrier wavesas shown in Fig. 6(II)(a), Fig. 6(II) (b), Fig. 6(II)(c), and Fig. 6(II)(d) consists of sawtooth carrier as well as inverted sawtooth carrier. This arrangement is done so as to produce the trailing edge modulation in the positive cycle and to produce the leading edge modulation in the negative cycle. The trailing-edge modulation scheme has a wave having the leading (rising) edge of PWM output occurs at fixed instants in time while the position of the trailing (falling) edge is modulated as the reference signal level varies. Similarly, for leading edge modulation scheme has the trailing (falling) edge of PWM output occurs at fixed instants in time while the position of the leading (rising) edge is modulated as the reference signal level varies.

$$b_{pwm}(t) = D + \frac{M}{2} \cos(\omega_{l}t + \theta_{1})$$

$$+ \sum_{m=1}^{+\infty} \frac{1}{m\pi} \begin{cases} \sin[m(\omega_{c}t + \theta_{c})] \\ -J_{0}(m\pi M) \sin[m(\omega_{c}t + \theta_{c}) - 2mD\pi] \end{cases} (19)$$

$$+ \sum_{m=1}^{+\infty} \sum_{n=\pm 1}^{\pm\infty} \frac{J_{n}(m\pi M)}{m\pi} \sin\left[\frac{n\pi}{2} - m(\omega_{c}t + \theta_{c}) \\ -n(\omega_{l}t + \theta_{1}) + 2mD\pi \right]$$

Fig. 6(I). Triangular carrier waves. (a) Phase opposition disposition. (b) Phase shifted. (c) Phase disposition. (d) Alternate phase opposition disposition.

$$F(t) = \frac{MV}{2} \cos\left(\omega_{F}t\right) + \frac{V}{\pi} \sum_{m=1}^{\infty} \frac{\sin\left(m\omega_{c}t\right)}{m}$$

$$- \frac{V}{\pi} \sum_{m=1}^{\infty} \frac{J_{o}\left(mM\pi\right)}{m} \left[\cos\left(m\pi\right)\sin\left(m\omega_{c}t\right)\right]$$

$$- \frac{V}{\pi} \sum_{m=1}^{\infty} \sum_{n=\pm 1}^{\pm \infty} \frac{J_{n}\left(mM\pi\right)}{m} \left[\cos\left(m\pi + n\pi/2\right).\sin\left(m\omega_{c} + n\omega_{F}t\right)\right]$$

$$- \sin\left(m\pi + n\pi/2\right).\cos\left(m\omega_{c}t + n\omega_{F}t\right)\right].$$

(20)

The phase voltage of an inverter with natural sampled PWM and sawtooth carrier can be described by (20).

(10) is derived in [21] using the expression given in the works of Black [22]. Here again, the amplitude of the fundamental is directly proportional to modulation index. Whereas the second and third term shows that all harmonics of the carrier frequency is existing in the phase voltage.

- In (18) and (20):

- $\omega_{\rm F}$  = frequency of the fundamental (reference)

- $\omega_{\rm c}$  = frequency of the carrier signal (rad/s),

- M = modulation index, V= value of the dc supply voltage,

- $J_0$ ,  $J_n$  = Bessel functions of the first kind.

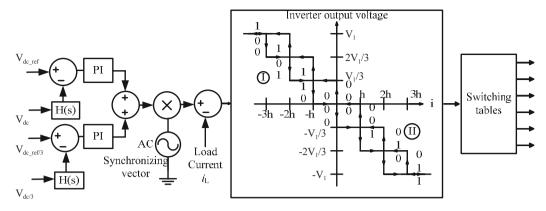

# VI. DESIGN OF DC-LINK VOLATGE, AUXILIARY CAPACITOR VOLTAGE AND LOAD CURRENT CONTROLLERS

#### A. Voltage Controllers

The solar PV is considered as the source (DC link) of the analysed PUC inverter. In PV applications, using capacitors of electrolytic type will be less desirable because of short lifetime mainly when installed in outdoor temperatures. Film capacitors have very long life time hence these can replace electrolytic capacitors, however they have very high prices. This makes practical limitation for dc link capacitor, establishing significant doubly frequency ripple on dc link and clamping capacitor voltages. This doubly frequency ripple further couples with control loop & causes distortions in output current.

Therefore, a notch filter (stop band filter) is placed on the feedback signal of DC voltage to attenuate ripple component. Notch filter is given as in (21).

$$H(s) = \frac{s^2 + 2\varepsilon_1 \omega_n s + \omega_n^2}{s^2 + 2\varepsilon_2 \omega_n s + \omega_n^2}$$

(21)

Where  $\omega_n$  is double of fundamental frequency. For getting maximum number of output voltage levels from the inverter, the auxiliary capacitor or holding capacitor voltage should be held at one third of dc link voltage. A simple PI controller is used to control the voltage of the auxiliary capacitor voltage and dc link voltage. The load current is represented as in (22).

$$i_L = c \, \frac{dv_c}{dt} \tag{22}$$

Fig. 6(II). Sawtooth carrier waves. (a) Phase disposition. (b) Alternate phase opposition disposition. (c) Phase opposition disposition. (d) Phase shifted.

Assuming a phase margin of 75° and critically damped system with damping factor  $\varepsilon$ =1.The transfer function of the system

Fig. 7. Control block diagram for generation of gate pulses.

tem is given as in (23), (24):

$$G(s) = \left(K_p + \frac{K_I}{s}\right) * \left(\frac{1}{sC}\right)$$

(23)

$$G(j\omega) = \frac{K_l + j\omega K_p}{-\omega^2 C}$$

(24)

The phase of the system can be written as in (25):

Phase

$$(G(j\omega)) = -180^\circ + \tan^{-1}\left(\frac{\omega K_p}{K_I}\right)$$

(25)

$$-180^{\circ} + 75^{\circ} = -180^{\circ} + \tan^{-1}\left(\frac{\omega K_p}{K_I}\right)$$

$$(3.73^2 + 1) K_I^2 = (10)^4 * 2.2^2 * 10^{-6}$$

(26)

The phase margin of the system is 75°. Thus,  $K_I = 0.06$ ,  $K_p = 0.02$  as calculated from (26).

#### B. Current Controller

From Fig. 1, on applying KVL on the load or grid side, (27) and (28) are achieved:

For RL load:

$$V_{an} = R * i_L + L \frac{di_L}{dt}$$

(27)

For grid load:

$$V_{an} = R_f * i_L + L_f \frac{di_L}{dt} + V_{ac}$$

(28)

Here R & L are load resistor & reactor and  $R_f \& L_f$  are filter inductor internal resistance & inductance. For generation of seven level output voltage, one should control the DC-link & auxiliary capacitor voltages to  $V_{dc}$  and  $V_{dc}/3$ , respectively. This has been done by voltage controllers as shown in Fig. 7. When actual injected current into grid or load is lower than reference (current error) then positive voltage across the load is applied thus Fig. 7 sector I are applied. When actual injected current into grid or load is greater than reference (current error) then negative voltage across the load is applied thus Fig. 7 sector II are applied.

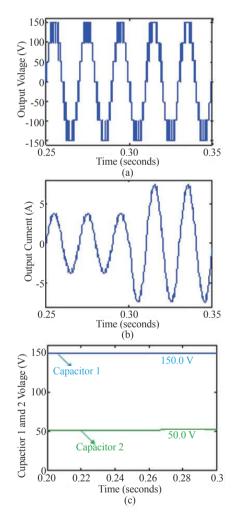

Fig. 8. (a) Output voltage; (b) Output current; (c) Capacitor voltage.

## VII. SIMULATION RESULTS AND DISCUSSION

The PUC inverter model is built using MATLAB<sup>®</sup>/Simulink simulation software package to verify the performance of different triangular and sawtooth carrier-based PWM modulation schemes. In line to the above, single DC source is selected of 150 V. The second capacitor has the voltage rating of 1/3rd of the DC source. Fig. 8(c) shows the capacitor voltages to be 150 V

TABLE III THE OPERATING CONDITIONS FOR SIMULATION

| Simulation Set up Parameters | Rating      |

|------------------------------|-------------|

| Capacitors                   | 4700 μF     |

| Load Resistance              | 40 Ω        |

| Load Inductance              | 12 mH       |

| Modulating Frequency         | 1 kHz       |

| Load Change (at time)        | 0.3 seconds |

Fig. 9. Experimental set up.

and 50 V. Seven level output voltage (shown in Fig. 8 (a)) is obtained using TABLE II switching combination. TABLE III outlines the operating condition of PUC inverter for simulation. The value of inductor andresistance at the load is 12 mH and 40 ohm respectively. At 0.3 seconds the load was doubled, hence the current doubles at 0.3 seconds (as shown in Fig. 8(b)). At 0.3 seconds, two 40 ohm resistors were connected in parallel to make 20 ohm effective resistance. It can be observed that the output voltage is unchanged at 0.3 seconds thus verifying the effectiveness of the closed loop control.

#### VIII. EXPERIMENTAL RESULTS AND DISCUSSION

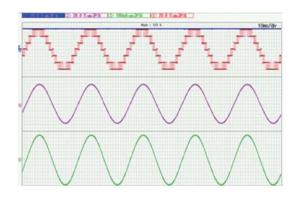

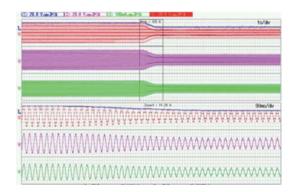

Experimental investigation is done to validate the theoretical findings and simulation results presented in the paper so far. Experiment is conducted with customised hardware comprising of Semikron modules SKM75GB12T4 as shown in Fig. 9. Control code is written in system generator and processed using FPGA board Vortex 5. Fluke 42B power analyser is used to to record the total harmonic distortion (THD) in the voltage and current waveform. The experimental parameters is presented in TABLE IV where the parameters are chosen to match with the available components. Fig. 10 shows the experimental result showing 7 level waveform and sinusoidal fundamental of PUC inverter output voltage and sinusoidal load current. It can be observed from the figure that the load current is in phase with the fundamental output of the PUC waveform. The dynamics of DC link voltage control loop and load current loop is tested and the resulting waveforms are presented in Fig. 11, Fig. 12, Fig. 13. The DC link voltage is ramped down from 54 V to 36 V (33% decrease in the initial value) and the transients are recorded in Fig. 11. The DC link voltage is seen to quickly drops to the new value and correspondingly the auxiliary capacitor volt-

TABLE IV Experimental, Set up Parameters

| Parameter                      | Value   |

|--------------------------------|---------|

| Auxiliary Capacitor            | 4700 μF |

| Load Resistance                | 4 Ω     |

| Load Inductance                | 10 mH   |

| Modulating Frequency           | 1 kHz   |

| Sinusoidal Reference Frequency | 50 Hz   |

| DC link voltage                | 54 V    |

| Dead-band period               | 2µS     |

|                                |         |

Fig. 10. Experimental result showing 7 level waveform and sinusoidal fundamental of PUC inverter output voltage and sinusoidal load current.

Fig. 11. Experimental result showing dynamic condition when load current is decreased.

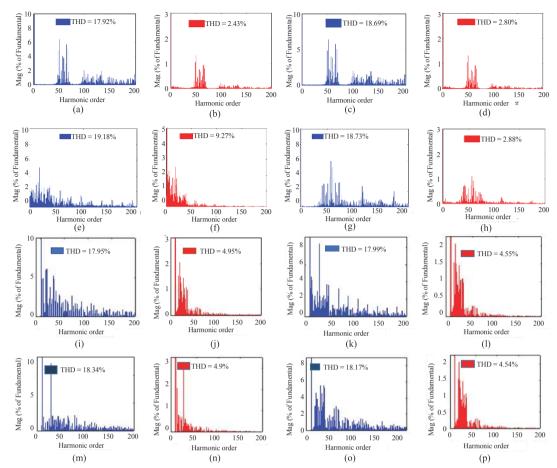

age follows the change. The output voltage level drops and the current magnitude drops accordingly. Further test is conducted by increasing the DC link voltage value and the corresponding results are shown in Fig. 13. The DC link voltage is ramped up from 36 V to 54 V (50% increase in the initial value). The auxiliary capacitor voltage is seen to follow the change and settle to the new value and the voltage and current follows the change quickly. Hence it is concluded that both the DC voltage control loop and load current loop have large control bandwidth with fast dynamics. The THD is calculated using Fluke 42B power analyser for different modulation schemes and are shown in Fig. 12(a) to Fig. 12(p). The THD obtained are tabulated in TABLE V wherein the THD for voltage and current both are shown to be minimum for the case of level shifted triangular carrier.

Fig. 12 (a) FFT of voltage for triangular PD-PWM scheme; (b) FFT of current for triangular PD-PWM scheme; (c) FFT of voltage for triangular phase shifted scheme; (d) FFT of current for triangular phase shifted scheme; (e) FFT of voltage for sawtooth PD-PWM scheme; (f) FFT of current for sawtooth PD-PWM scheme; (g) FFT of voltage for sawtooth phase shifted scheme; (h) FFT of current for sawtooth phase shifted scheme; (i) FFT of voltage for sawtooth AOPD; (j) FFT of current for sawtooth APOD; (k) FFT of voltage for sawtooth IPD; (l) FFT of current for sawtooth IPD; (m) FFT of voltage for triangular IPD; (n) FFT of voltage for triangular APOD; (p) FFT of current for triangular APOD.

Fig. 13. Experimental result showing dynamic condition when load current is increased.

#### IX. CONCLUSION

The paper has presented the comparison of different PWM schemes which can be applied to the PUC inverter. Investigating the suitable modulation schemes is very essential with respect to local grid integration, as the power quality is directly dependent on THD. Triangular carrier based PWM schemes is exhibiting the better result than the sawtooth carrier based PWM schemes

TABLE V FFT Results for Different Modulation Schemes

| Particulars   | THD (in %)        |         |  |

|---------------|-------------------|---------|--|

| Ti            | riangular Carrier |         |  |

| PWM Schemes   | Voltage           | Current |  |

| PD-PWM        | 18.34             | 4.90    |  |

| POD-PWM       | 17.92             | 2.43    |  |

| APOD-PWM      | 18.17             | 4.54    |  |

| Phase-Shifted | 18.69             | 2.80    |  |

| S             | awtooth Carrier   |         |  |

| PD-PWM        | 17.99             | 4.54    |  |

| POD-PWM       | 19.18             | 9.27    |  |

| APOD-PWM      | 17.95             | 4.54    |  |

| Phase-Shifted | 18.73             | 2.88    |  |

as the triangular level shifted carrier PWM scheme is better as compared to sawtooth level shifted carrier because in triangular level shifted carrier both edges (falling and rising) of pulses are modulated which improves the harmonic spectrum. However, in the sawtooth level shifted carrier only rising edges are modulated. Hence triangular level shifted carrier PWM scheme can be applied for integrating the PUC inverter with PV and local grid systems. Triangular level shifted carrier PWM scheme for PUC inverter has been suggested based on observing the THD in voltage and current which are respectively just 17.92% and 2.43%. The whole system i.e. solar panel, boost converter with PUC inverter will be very cost effective, besides having good reliability and power quality as it has the minimum number of power electronics devices compared to previously introduced multilevel inverter topologies. With reduced number of capacitors and power switches seven levels of voltages have been achieved for PUC inverter.

#### REFERENCES

- [1] F. A. Rahman, M. M. A. Aziz, R. Saidur, W. A. A. Bakar, M. R. Hainin, R. Putrajaya, and N. A. Hassan, "Pollution to solution: Capture and sequestration of carbon dioxide (CO2) and its utilization as a renewable energy source for a sustainable future", *Renewable and Sustainable Energy Reviews*, vol. 71, pp. 112-126, May 2017.

- [2] Y. Yang, A. Sangwongwanich, and F. Blaabjerg, "Design for reliability of power electronics for grid-connected photovoltaic systems," in *CPSS Transactions on Power Electronics and Applications*, vol. 1, no. 1, pp. 92-103, Dec. 2016.

- [3] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *Industrial Electronics, IEEE Transactions on*, vol. 49, pp. 724-738, 2002.

- [4] Q. M. Attique, Y. Li, and K. Wang, "A survey on space-vector pulse width modulation for multilevel inverters," in *CPSS Transactions on Power Electronics and Applications*, vol. 2, no. 3, pp. 226-236, Sept. 2017.

- [5] Z. Mohzani, B. P. McGrath, and D. G. Holmes, "A generalized natural balance model and balance booster filter design for three-level Neutral-Point-Clamped converters," in *IEEE Transactions on Industry Applications*, vol. 51, no. 6, pp. 4605-4613, Nov.-Dec. 2015.

- [6] A. Kulkarni and V. John, "HF transformer based grid-connected inverter topology for photovoltaic systems". *IETE Technical Review*. Vol. 33, no. 1, pp. 69-75, Jan 2016.

- [7] K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A rReview," in *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- [8] S. Daher, J. Schmid, and F. L. M. Antunes, "Multilevel inverter topologies for stand-alone PV systems," *Industrial Electronics, IEEE Transactions on*, vol. 55, pp. 2703-2712, 2008.

- [9] H. Vahedi, P.-A. Labbe, and K. Al-Haddad, "Sensor-Less five-level packed U-Cell inverter operating in stand-alone and grid-connected modes," *Industrial Informatics, IEEE Transactions on*, vol. 12, no. 1, pp. 361-370, 2017.

- [10] K. Al-Haddad, Y. Ounejjar, and L.-A. Gregoire, "Multilevel electric power converter," U.S. Patent 2743085, 2010ed: Google Patents, 2009.

- [11] Y. Ounejjar, K. Al-Haddad, and L. A. Gregoire, "Packed U cells multilevel converter topology: theoretical study and experimental validation," *Industrial Electronics, IEEE Transactions on*, vol. 58, pp. 1294-1306, 2011.

- [12] A. Sheir, M. Orabi, M. E. Ahmed, A. Iqbal, and M. Youssef, "A high efficiency single-phase multilevel packed U cell inverter for photovoltaic applications," in *Telecommunications Energy Conference (IN-TELEC), 2014 IEEE 36th International*, 2014, pp. 1-6.

- [13] Y. Ounejjar, K. Al-Haddad, and L. A. Dessaint, "A novel six-band hysteresis control for the packed U cells seven-level converter: experimental validation," *Industrial Electronics, IEEE Transactions on*, vol. 59, pp. 3808-3816, 2012.

- [14] A. Iqbal, M. Tariq, K. Rahman, and A. Al-qahtani, "Control of packed U-cell multilevel five-phase voltage source inverter," *Qatar Founda*-

tion Annual Research Conference, p. ITPP0493, 2014.

- [15] M. Sidrach-de-Cardona, and J. Carretero, "Analysis of the current total harmonic distortion for different single-phase inverters for grid-connected pv-systems," *Solar Energy Materials and Solar Cells*, vol. 87, pp. 529-540, 5// 2005.

- [16] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *Industrial Electronics, IEEE Transactions on*, vol. 49, pp. 858-867, 2002.

- [17] Y. Hinago and H. Koizumi, "A modulation method for capacitor voltage ripple reduction of the switched-capacitor inverter using series/ parallel conversion," in *Industrial Technology (ICIT), 2011 IEEE International Conference on*, 2011, pp. 105-109.

- [18] A. Tsunoda, Y. Hinago, and H. Koizumi, "Level-and phase-shifted PWM for seven-level switched-capacitor inverter using series/parallel conversion," *Industrial Electronics, IEEE Transactions on*, vol. 61, pp. 4011-4021, 2014.

- [19] P. Sochor and H. Akagi, "The oretical and experimental comparison between phase-shifted PWM and level-shifted PWM in a modular multilevel SDBC inverter for utility-scale photovoltaic applications," in *IEEE Trans. Ind. Appl.*, vol. 53, no. 5, pp. 4695-4707, Sept.-Oct. 2017

- [20] J. Sun, (Jan. 2012), "Pulse-width modulation," in *Dynamics and Control of Switched Electronic Systems (Advances in Industrial Control Series), F. Vasca and L. Iannelli, Eds. London, U.K.: Springer*, [Online].Jan. 2012, pp. 25–61. [Online]. Available: http://link.springer. com/chapter/10.1007/978-1-4471-2885-4\_2.

- [21] J. Hamman and F. S. Van Der Merwe, "Voltage harmonics generated by voltage-fed inverters using PWM natural sampling,"*Power Electronics, IEEE Transactions on*, vol. 3, pp. 297-302, 1988.

- [22] H. S. Black, Modulation theory: van Nostrand, 1953

Mohd Tariq obtained a B. Tech in electrical engineering from Aligarh Muslim University and M. Tech in machine drives and power electronics from the Indian Institute of Technology (IIT)-Kharagpur. He pursued his Ph.D. from Nanyang Technological University, Singapore. Before joining his PhD, he has worked as a Scientist in an autonomous institute (NIOT, Chennai) under ministry of earth sciences, govt. of India and also worked as an Assistant Professor at National Institute of Technology

(NIT) – Bhopal, India. Currently, he is working as an Assistant Professor at Department of Electrical Engineering, Aligarh Muslim University, Aligarh, India.

He is a recipient of the best paper award from the IEEE Industrial Applications Society's (IAS) and Industrial Electronic Society, Malaysia Section – Annual Symposium (ISCAIE-2016) held in Penang, Malaysia. His research interest includes power converters, energy storage devices and its optimal control for the electrified transportation and renewable energy application.

**Mohammad Meraj** has completed M.Tech from IIT Kharagpur. Presently he is pursuing his Ph.D. from Qatar University, Qatar. His interest is in the area of power electronics converters and its control.

Abdul Azeem has completed his M.Tech from Aligarh Muslim University, Aligarh, India. His interest is in the area of power electronics converters and its control. He has published a number of papers in international journals and conferences.

Atif Iqbal, Ph.D. (UK), Senior Member IEEE, Fellow IET (UK), Fellow IE (India)- Associate Professor at Electrical Engineering, Qatar University and Former Full Professor at Electrical Engineering, Aligarh Muslim University (AMU), Aligarh, India. Recipient of Outstanding Faculty Merit Award AY 2014-2015 and Research excellence award at Qatar University, Doha, Qatar. He received his B.Sc. (Gold Medal) and M.Sc. Engineering (Electrical) degrees in 1991 and 1996, respectively, from the

Aligarh Muslim University (AMU), Aligarh, India and PhD in 2006 from Liverpool John Moores University, Liverpool, UK. He has been employed as a Lecturer in the Department of Electrical Engineering, AMU, Aligarh since 1991 where he served as Full Professor until Aug. 2016. He is recipient of Maulana Tufail Ahmad Gold Medal for standing first at B.Sc. Engg. Exams in 1991 from AMU. He has received best research papers awards at IEEE ICIT-2013 and IET-SESICON-2013. He has published widely in International Journals and Conferences his research findings related to Power Electronics and Renewable Energy Sources. Dr. Iqbal has authored/ co-authored more than 270 research papers and one book and two chapters in two other books. He has supervised several large R&D projects. His principal area of research interest is modeling and simulation of power electronic converters, control of multi-phase motor drives and renewable energy sources.

He is an Associate Editor of IEEE Transaction of Industrial Applications and Guest Associate Editor of IEEE Transaction of Power Electronics.

Ali I. Maswood received the B.Eng. and M.Eng. degrees (with first class honors) from the Moscow Power Engineering Institute, Moscow, Russia, and the Ph.D. degree from Concordia University, Montreal, QC, Canada. Having taught in Canada for a number of years, he joined Nanyang Technological University, Singapore, in 1991, where he is currently an Associate Professor. His research interests include power electronics, particularly in converter generated harmonics, novel inverter topologies,

advanced PWM switching, and power quality. He has authored numerous international journal and conference publications. He is also the Chapter Author of the Power Electronics Handbook(Academic, 2002).

Dr. Maswood is actively involved in the local IEEE Industry Applications Society/Power Electronics Society Chapter.

**Bharatiraja Chokkalingam** was born in Namakkal, India on Jan 08, 1980. B. Eng. from KCT, Coimbatore, India, M. Eng. from GCT, India, and Ph.D. degree from the SRM University, India (all in electrical engineering) in 2002, 2006 and 2015, respectively. He completed his Postdoctoral Fellow at Centre for Energy and Electric Power, Faculty of Engineering and the Built Environment, Tshwane University of technology, South Africa in 2016. He is currently working as an Assistant Professor

at SRM University, Kattankulathur, Chennai, India. His research interest includes multilevel inverters, control of power converters, SVPWM techniques for power converters and adjustable speed drives, electrical vehicle and smart grid. He has authored several International Journal and Conference publications on these topics.