Article

# **Evaporated nanometer chalcogenide films for scalable high-performance complementary electronics**

Received: 30 June 2022

Accepted: 13 October 2022

Published online: 26 October 2022

Check for updates

Ao Liu  $\mathbb{D}^1$ , Huihui Zhu  $\mathbb{D}^1$ , Taoyu Zou<sup>1</sup>, Youjin Reo  $\mathbb{D}^1$ , Gi-Seong Ryu<sup>1</sup> & Yong-Young Noh  $\mathbb{D}^1 \boxtimes$

The exploration of stable and high-mobility semiconductors that can be grown over a large area using cost-effective methods continues to attract the interest of the electronics community. However, many mainstream candidates are challenged by scarce and expensive components, manufacturing costs, low stability, and limitations of large-area growth. Herein, we report wafer-scale ultrathin (metal) chalcogenide semiconductors for high-performance complementary electronics using standard room temperature thermal evaporation. The n-type bismuth sulfide delivers an in-situ transition from a conductor to a high-mobility semiconductor after mild post-annealing with self-assembly phase conversion, achieving thin-film transistors with mobilities of over 10 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>, on/off current ratios exceeding 10<sup>8</sup>, and high stability. Complementary inverters are constructed in combination with p-channel tellurium device with hole mobilities of over 50 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, delivering remarkable voltage transfer characteristics with a high gain of 200. This work has laid the foundation for depositing scalable electronics in a simple and cost-effective manner, which is compatible with monolithic integration with commercial products such as organic light-emitting diodes.

Thin-film transistor (TFT) technology has promoted the rapid development of inexpensive and large flat-panel displays. It is being applied widely in microprocessors, sensors, radio-frequency identification tags, wearable electronics, and other Internet-of-Things devices<sup>1–7</sup>. Unlike state-of-the-art high-performance silicon metal-oxide-semiconductor field-effect transistors (which involve stringent process restrictions), TFT technology is unique in that it can be manufactured with high yield on various large-area substrates via cost-effective process<sup>4</sup>. Decades of research has been devoted to the examination of TFT channel semiconductors including metal chalcogenides/oxides/halides, organics, and low-dimensional nanomaterials<sup>7–11</sup>. Metal oxides and chalcogenides show high electrical performance and stability. However, the use of expensive components (e.g., In and Ga) and toxic metals such as Cd and Pb involve high manufacturing costs and hazards to environmental safety. Notwithstanding the potential functionalities of emerging lowdimensional nanomaterials, it is difficult to achieve wafer-scale homogeneous deposition via an inexpensive and high reproducible way, limiting their application in large-area TFTs<sup>12</sup>.

Among the various thin-film deposition methods for large-area electronics, thermal evaporation provides remarkable deposition scalability and reproducibility, and enables precise film thickness control, homogeneous deposition on textured substrates, and highly customized multilayer stack growth. The commercialization of eighth generation ( $2200 \times 2500$  mm) organic light-emitting diodes (OLED) using thermal evaporation shows the feasibility of mass production of TFTs. In addition, film patterning with a size of several tens of micrometers can be achieved conveniently over a large area using fine metal masks. Among potential semiconductors capable of thermal evaporation, bismuth sulfide ( $Bi_2S_3$ ) shows great potential for TFT channels due to its eco-friendliness and cost-effectiveness in conjunction

<sup>&</sup>lt;sup>1</sup>Department of Chemical Engineering, Pohang University of Science and Technology, 77 Cheongam-Ro, Nam-Gu, Pohang 37673, Republic of Korea.

with high electron mobilities of up to 640 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1 13-16</sup>. Bi<sub>2</sub>S<sub>3</sub> has been studied extensively in photoelectric and thermoelectric devices benefiting from the suitable optical bandgap of 1.3-1.7 eV and high heat/ electricity conversion<sup>13,17-20</sup>. As a p-type candidate, tellurium (Te) has recently attracted substantial attention for high-performance TFT fabrication owing to its high hole mobility and stability<sup>21-23</sup>. In the efforts to deposit (metal)chalcogenide thin films over a large area in a cost-effective manner, the main attention has been paid to the solution process<sup>24–27</sup>. However, the strong covalent bonding of these solids requires complex and toxic synthetic processes and has been challenging to integrate with the conventional complementary metaloxide-semiconductor (CMOS) technology. Another noteworthy solution approach is liquid-phase exfoliation. It is used widely to obtain layered two-dimensional (2D) metal chalcogenide nanosheets<sup>7,28,29</sup>. Recent studies achieved high-performance molybdenum sulfide (MoS<sub>2</sub>) TFTs with an electron mobility ( $\mu_e$ ) of up to ~10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off current ratio  $(I_{on}/I_{off})$  of  $10^4$ – $10^6$  by controlling the defect healing and intercalation chemistry<sup>28,30</sup>. However, the structural surface defects from the high-energy exfoliation process, non-uniform number of lavers in each nanoflake, and inter-flake electrical resistance may limit large-area uniformity and further performance optimization<sup>28</sup>.

In this Article, we report sub-nanometer (metal)chalcogenide thin films deposited over large areas through industry-compatible room temperature (RT) thermal evaporation and explore their applications in TFTs and complementary electronics. Aided by the high vapor pressure of (metal)chalcogenides, thermally evaporated Bi<sub>2</sub>S<sub>3</sub> exhibits uniform films over large areas with nanometer-level precise thickness control. The as-deposited Bi<sub>2</sub>S<sub>3</sub> provides an amorphous structure containing sulfur-rich components with conductor-like behavior. Mild post-annealing can modulate the composition and drive self-assembly crystallization with the conversion to a high-mobility stable channel for TFT with  $\mu_e$  of over 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and  $I_{on}/I_{off}$  exceeding 10<sup>8</sup>. The highgain complementary inverter is further realized with the high-mobility p-channel Te TFT, indicating the great potential of thermally evaporated (metal)chalcogenides for large-area CMOS circuit integration.

#### Results

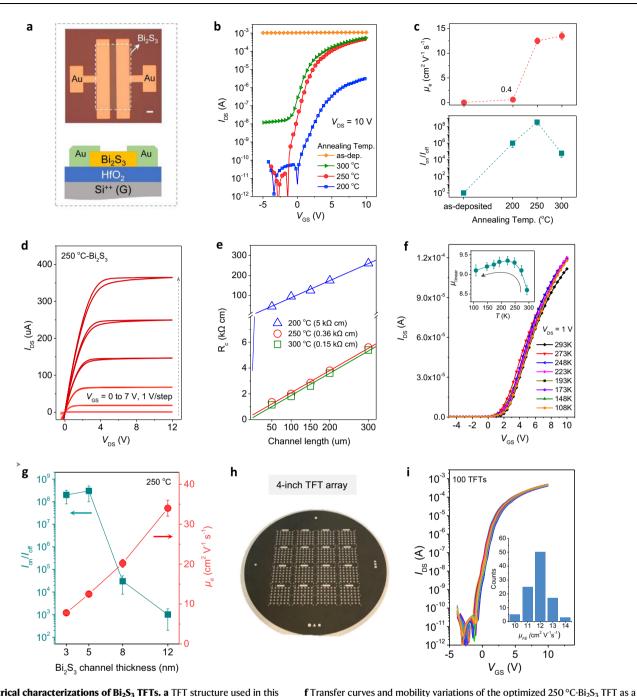

Electrical characterizations of thermally-evaporated Bi<sub>2</sub>S<sub>3</sub> TFTs The Bi<sub>2</sub>S<sub>3</sub> channel layers were deposited by RT thermal evaporation on atomic layer deposition HfO2 (40 nm)/p<sup>+</sup>-Si substrates. This was followed by post-annealing at 200-300 °C for 30 min (see the Methods section for further details). The gold source/drain electrodes were then deposited on the patterned Bi2S3 to construct bottom-gate topcontact TFTs (Fig. 1a). Typical transfer curves of Bi<sub>2</sub>S<sub>3</sub> TFTs are shown in Fig. 1b. The TFTs with the as-evaporated Bi<sub>2</sub>S<sub>3</sub> channel exhibited conductor-like behavior with a constant source-drain current (IDS) of ~1 mA. Such characteristics are generally caused by the excessive concentration of charge carriers in the channel layer and thus, the negligible gate bias modulation capability. It is noteworthy that mild post-annealing achieved the significant n-channel transistor characteristic with the desired enhancement operation mode (threshold voltage,  $V_{\rm TH} > 0$  V). The improved  $\mu_{\rm e}$  at higher annealing temperatures can be attributed to the enhanced long-range ordering of the microstructures. Among these, the post-annealing at 250 °C yielded a wellbalanced TFT performance, including a high  $\mu_e$  of 12.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, high  $I_{\rm on}/I_{\rm off}$  of 2×10<sup>8</sup>,  $V_{\rm TH}$  of 1.1 V, subthreshold swing (SS) of 0.2 V dec<sup>-1</sup>, small hysteresis <1 V, and high stabilities (Fig. 1c, Supplementary Fig. 1). The corresponding output curves show significant current linearity at low source-drain voltages, indicating the Ohmic contact between  $Bi_2S_3$  channel and Au electrodes (Fig. 1d). The transmission-line method<sup>31</sup> was employed to evaluate the contact resistance ( $R_c$ ) and it was calculated to be 360  $\Omega$  cm for the 250 °C-Bi<sub>2</sub>S<sub>3</sub> TFT (Fig. 1e). We then performed temperature-dependent measurements to investigate the charge transport properties of the optimized 250 °C-Bi<sub>2</sub>S<sub>3</sub> channel (Fig. 1f). The TFT mobilities first increased as the temperature decreased from 293 to 223 K. This is a typical band-like transport commonly observed in highly crystalline and high mobility semiconductors<sup>32-35</sup>. Therefore, we could infer a high degree of order in post-annealed  $Bi_2S_3$  thin films. When the measurement temperatures decreased further, the electron transport became thermally activated. This was dominated by shallow traps in  $Bi_2S_3$ , which caused a marginal reduction in mobility. Such temperature-dependent characteristics differ from the observations of solution-based liquid-phase exfoliated metal chalcogenide TFTs in that the thermal activation is governed over the temperature range, which is likely to be associated with activated interflake hopping<sup>36,37</sup>.

In addition to facile post-annealing, the Bi<sub>2</sub>S<sub>3</sub> channel thickness had a significant effect on the key TFT parameters, e.g.,  $\mu_e$  and  $I_{on}/I_{off}$ (Fig. 1g, Supplementary Fig. 2). A suitable Bi<sub>2</sub>S<sub>3</sub> thickness of 5 nm was used for the above device characterization. When the Bi<sub>2</sub>S<sub>3</sub> channel was downscaled to 3 nm, the remarkable electrical performance was maintained with a similarly high  $I_{on}/I_{off}$  of 10<sup>8</sup> and a marginally reduced  $\mu_{\rm e}$  of ~9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. During transistor operation, the accumulated charge carriers were confined to a narrow region (3-5 nm) close to the channel/dielectric interface. In channel layers that were excessively thin, the carrier transport could undergo backscattering owing to roughness, dangling bonds, and defects<sup>21</sup>. When the channel thicknesses exceeded 5 nm,  $\mu_{\rm e}$  increased monotonically from 20.2 to 34.5  $cm^2\,V^{\scriptscriptstyle -1}\,s^{\scriptscriptstyle -1}$  for the TFTs based on 8 and 12 nm  $Bi_2S_3$  channel layers. A downward trend from  $10^5$  to  $10^3$  was observed for  $I_{on}/I_{off}$ . This can be interpreted as a reduced electrostatic control for TFTs based on thicker channel layers, which is commonly observed in different material systems<sup>21,38,39</sup>. Finally, to examine the scalability of thermally evaporated Bi<sub>2</sub>S<sub>3</sub>, we fabricated a TFT array on a 4 inch  $HfO_2/p^+$ -Si substrate and randomly measured 100 TFTs (Fig. 2h). The devices exhibited remarkable uniformity and a narrow performance distribution with  $\mu_e$  in the range of 10.8–14.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of 1–4 × 10<sup>8</sup> (Fig. 2i). It is noteworthy that such wafer-scale deposition of  $5 \text{ nm Bi}_2S_3$ film requires only 40 mg of Bi<sub>2</sub>S<sub>3</sub> powder (-USD 0.28), representing a significantly low material cost.

#### Bi<sub>2</sub>S<sub>3</sub> thin-film characterizations

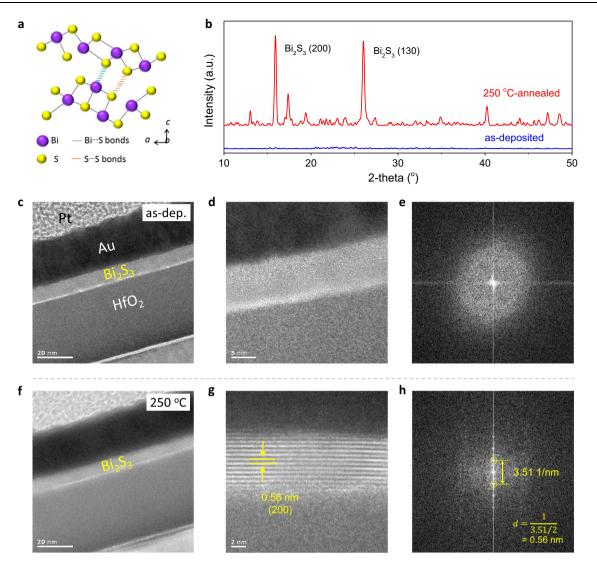

A series of film analyses were performed to clarify the effects of postannealing on the significantly different TFT performance. First, the crystal structure of the film was analyzed. Bi2S3 is theoretically composed of a lamellar structure with (Bi<sub>4</sub>S<sub>6</sub>)<sub>n</sub> ribbons stacked along the c-axis through van der Waals interactions (Fig. 2a)<sup>13,40</sup>. This atomic chain configuration ensures an intrinsically benign grain boundary and efficient charge transport<sup>41</sup>. Based on X-ray diffraction (XRD), the asevaporated Bi<sub>2</sub>S<sub>3</sub> film showed an evident amorphous characteristic, and a polycrystalline texture was observed after post-annealing at 250 °C (Fig. 2b). Cross-sectional high-resolution transmission electron microscopy (HRTEM) was performed to obtain more precise information regarding the microscopic crystal structure. As shown in Fig. 2c-e, the TEM image and selected area electron diffraction (SAED) pattern exhibit the typical amorphous structure of as-deposited Bi<sub>2</sub>S<sub>3</sub> without a perceptible long-range order. This initial amorphous state is favorable to subsequent scalable growth owing to its superior uniformity. After the post-annealing at 250 °C, a well-defined laminar texture was observed without visible defects (Fig. 2f, g). A lattice spacing of 0.56 nm corresponding to the (200) crystalline plane of  $Bi_2S_3$ was measured. It was also verified by the fast Fourier transform (FFT) spot patterns of the marked frames (Fig. 2h). The thickness of the  $Bi_2S_3$ film (i.e., the number of layers) could be controlled precisely by manipulating the evaporation time and rate. It was noted that the efficient evaporation process enabled the deposition of a 5 nm Bi<sub>2</sub>S<sub>3</sub> thin film in -25 s (rate:  $-2 \text{ Å s}^{-1}$ ). This provided a high throughput compared with other film deposition methods.

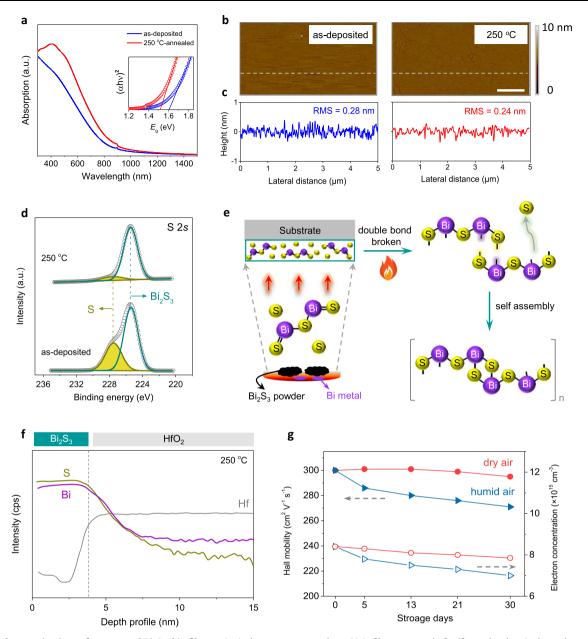

The optical spectra exhibited increased light absorption after the annealing at 250 °C, with the bandgap ( $E_g$ ) marginally reduced from 1.6

**Fig. 1** | **Electrical characterizations of Bi<sub>2</sub>S<sub>3</sub> TFTs. a** TFT structure used in this study and optical image of typical Bi<sub>2</sub>S<sub>3</sub> TFT (scale bar: 100 µm). **b** Transfer curves of Bi<sub>2</sub>S<sub>3</sub> TFTs as a function of post-annealing temperature. **c** Corresponding summarization of values of electron mobility ( $\mu_e$ ) and  $I_{on}/I_{off}$ . The error bars were calculated from 10 individual TFTs. **d** Output curves of the optimized Bi<sub>2</sub>S<sub>3</sub> TFT annealed at 250 °C. **e** Transmission-line method (TLM) plots with different channel lengths. Here, contact resistance ( $R_c$ ) is determined from the *y*-axis intercept.

devices. **h** Optical image of TFT arrays on a 4-inch HfO<sub>2</sub>/p<sup>+</sup>-Si substrate. **i** Transfer curves of 100 randomly measured 250 °C-Bi<sub>2</sub>S<sub>3</sub> TFTs. The inset shows the statistical results of  $\mu_{e}$ . spectra showed two peaks at 163.5 and 158.2 eV. These match closely with the characteristic Bi<sup>3+</sup> peaks in Bi<sub>2</sub>S<sub>3</sub> (Supplementary Fig. 4)<sup>40,42</sup>. This indicates that the Bi<sup>3+</sup> existed in phase-pure Bi<sub>2</sub>S<sub>3</sub> without other

function of the measurement temperature in vacuum. The error bars were obtained

from 5 individual devices. **g** Summarization of  $\mu_e$  and  $I_{op}/I_{off}$  for 250 °C-Bi<sub>2</sub>S<sub>3</sub> TFTs

with different channel thicknesses. The error bars were obtained from 10 individual

to 1.5 eV (Fig. 3a). The atomic force microscope (AFM) images displayed a substantial uniformity and ultra-smooth surface morphology, with small root mean square (RMS) values of 0.28 and 0.24 nm for the as-deposited and 250 °C-Bi<sub>2</sub>S<sub>3</sub> thin films, respectively (Fig. 3b, c). Such atomically smooth topography allows for a high-quality interface and high device yield over a large area. The typical polycrystalline texture is observed in the 250 °C-annealed film with the average grain size of hundred nanometers (Supplementary Fig. 3). We then performed X-ray photoelectron spectroscopy (XPS) to analyze the film components. For both as-deposited and 250 °C-annealed samples, the Bi 4f

This indicates that the  $Bi^{3+}$  existed in phase-pure  $Bi_2S_3$  without other forms. Figure 3d exhibits the corresponding S 2*s* spectra. It could be split into two subpeaks at 225.4 and 227.6 eV, respectively. The lowerbinding-energy peak can be assigned to the chemical bond between Bi and S in Bi<sub>2</sub>S<sub>3</sub>. Another peak, however, is derived from elemental S<sup>40</sup>. During the thermal evaporation, most Bi<sub>2</sub>S<sub>3</sub> powder was evapo-

During the thermal evaporation, most  $Bi_2S_3$  powder was evaporated as the  $Bi_2S_3$  molecular form. Meanwhile, partial  $Bi_2S_3$  powder was thermally decomposed. Owing to the low vapor pressure of S, both S

**Fig. 2** | **Microstructure analysis of Bi<sub>2</sub>S<sub>3</sub> thin films. a** Crystal structure of Bi<sub>2</sub>S<sub>3</sub>. **b** XRD spectra of as-evaporated Bi<sub>2</sub>S<sub>3</sub> thin film and of that annealed at 250 °C. **c**-**e** HRTEM images and SAED pattern of as-evaporated Bi<sub>2</sub>S<sub>3</sub> thin films. **f-h** HRTEM

images and SAED pattern of  $Bi_2S_3$  thin film annealed at 250 °C. FFT patterns obtained from the entire area of (g). The length of 3.51 1/nm corresponds to a d-spacing of 0.56 nm.

and Bi<sub>2</sub>S<sub>3</sub> were evaporated onto the substrates, resulting in the sulfurrich Bi<sub>2</sub>S<sub>3</sub> thin films (Fig. 3e). Residual metallic Bi was observed in the tungsten boat after evaporation (Supplementary Fig. 4). The asobtained films showed an amorphous structure, resulting from the random distributions of elemental S and Bi2S3 molecules. After annealing at 250 °C, the amorphous films turned to crystalline. During annealing, most residual S sublimated, as revealed by the reduced XPS peak intensity. The Bi:S atomic ratio was 2:3.6. Meanwhile, one of the double bonds in Bi<sub>2</sub>S<sub>3</sub> was thermally broken, and then the molecules reassembled into crystalline (Bi<sub>4</sub>S<sub>6</sub>)<sub>n</sub> ribbons. This explains the laminar crystalline structure in HRTEM images. Secondary-ion mass spectrometry (SIMS) was used to track the elemental distribution in the films. A uniform Bi distribution was observed in both the samples throughout the bulk. With regard to sulfur, significant enrichment at the bottom was observed in the as-grown Bi<sub>2</sub>S<sub>3</sub>, which became homogenous after annealing at 250 °C (Supplementary Fig. 6, Fig. 2f).

We then assessed the intrinsic electrical properties of different Bi<sub>2</sub>S<sub>3</sub> samples by conducting Hall measurements. The as-grown Bi<sub>2</sub>S<sub>3</sub> film showed a high electron concentration of  $6.7 \times 10^{19}$  cm<sup>-3</sup> with a low Hall mobility of -1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The high electron concentration can be attributed to the strong n-doping effect of interstitial sulfur<sup>16</sup>. This is also consistent with the conductor-like behavior of TFTs fabricated

based on the as-evaporated Bi<sub>2</sub>S<sub>3</sub> channel. This low mobility can be ascribed to two main factors. One is the strong scattering caused by the high electron concentration and sulfur content. The other is the amorphous state, which generally exhibits a high degree of structural disorder. The electron concentration decreased to  $8 \times 10^{15}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> after the annealing at 250 °C. The elimination of scattering in conjunction with the enhanced crystalline orientation and film densification contributed to the high Hall mobility of 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. It is noteworthy that such extensive electrical property modulation can be achieved conveniently through gentle post-annealing without further processing or doping.

The high mobility remained almost constant even after exposure to air for 30 d, particularly under dry air conditions (Fig. 3g). This indicated remarkable ambient durability. Humid air conditions caused a marginal degradation of mobility. This can exacerbate charge transport owing to moisture absorption at the grain boundaries. This physisorption of moisture is weakly coordinated, and the electrical performance can be recovered rapidly after the baking process at 100 °C. Such ambient stability differs significantly from previous reports on metal chalcogenide films grown by mechanical cleavage or chemical vapor deposition, which show that their electrical properties are sensitive to  $O_2$  molecules<sup>43,44</sup>. These film-growth techniques

Fig. 3 | Basic characterizations of evaporated Bi<sub>2</sub>S<sub>3</sub> thin films. a Optical absorption spectra of as-grown and 250 °C-annealed Bi<sub>2</sub>S<sub>3</sub> thin films. *E*<sub>g</sub> was calculated by fitting  $(\alpha h\nu)^2$  to  $h\nu$  curves using the standard Tauc plot method, as shown in the inset. **b**, **c** Corresponding AFM images and height profiles (scale bar: 1 µm). **d** Corresponding XPS S 2 s spectra. **e** Schematic of the fabrication of

generally introduce chalcogen vacancies that induce doping effects through the chemisorption of O<sub>2</sub> molecules. For our thermally evaporated Bi<sub>2</sub>S<sub>3</sub>, the intrinsic marginally sulfur-rich component indicates negligible sulfur vacancies. Thereby, the interaction with O<sub>2</sub> reduced. This is supported by the negligible variation in the electron concentration of  $(7-8) \times 10^{15}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> after long-term air exposure (no doping occurs).

# Electrical characterizations of p-channel Te TFTs and CMOS inverters

We finally explored p-channel devices to realize complementary circuits using thermally evaporated chalcogenide TFTs. The fabrication of high-mobility p-type semiconductors by an inexpensive scalable method is also an urgent task in the electronics community<sup>11,45,46</sup>. Among different candidates, element chalcogenide Te is receiving

amorphous Bi<sub>2</sub>S<sub>3</sub> film composed of sulfur molecules via thermal evaporation. **f** SIMS spectra of 250 °C-Bi<sub>2</sub>S<sub>3</sub> thin film. **g** Variations in Hall mobility and electron concentrations of 250 °C-Bi<sub>2</sub>S<sub>3</sub> thin films as functions of ambient exposure period and condition (the relative humidity in dry and humid air conditions are <10% and 50–70%, respectively).

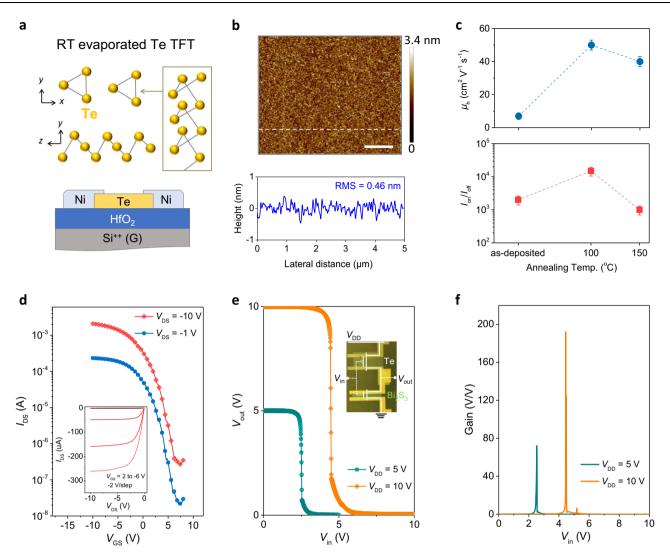

increased attention owing to its high hole mobility and remarkable stability<sup>23</sup>. Thermal evaporation of Te TFT at a cryogenic temperature of -80 °C was reported to yield a uniform Te channel layer with a large domain size<sup>21</sup>. To enable a more conveniently reproducible film deposition process, we develop the RT thermal evaporation process to deposit Te thin film, which displays a high uniformity, with an RMS value of 0.47 nm (Fig. 4a, b). After mild post-annealing at 100 °C, the Te TFT showed a remarkably high hole mobility ( $\mu_h$ ) of 52 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of 10<sup>4</sup> (Fig. 4c, d, Supplementary Fig. 7). The high current linearity and saturation in the output curves indicated Ohmic contact between the Ni electrodes and Te channel (inset in Fig. 4d). Finally, we monolithically integrated CMOS inverters with n-channel Bi<sub>2</sub>S<sub>3</sub> and p-channel Te TFTs in a chip. Figure 4e exhibits full-swing characteristics and rapid voltage transitions with a high peak gain of nearly 200 at a supply voltage ( $V_{DD}$ ) of 10 V (Fig. 4f). This indicates the high

**Fig. 4** | **Electrical characterizations of RT evaporated Te TFTs and inverters. a** TFT structure and crystal structure of Te with spiraling chain. **b** AFM image and height profile of as-evaporated Te thin film (scale bar: 1 µm). **c** Summarization of  $\mu_h$  and  $I_{on}/I_{off}$  of Te TFTs as functions of post-annealing temperature. The error bars were calculated from 10 individual TFTs. **d** Transfer curves of optimized 100 °C-

annealed Te TFT measured at linear and saturation regions. The inset shows the corresponding output curves. **e**, **f** Voltage transfer and gain voltage curves of complementary inverter based on n-channel  $Bi_2S_3$  and p-channel Te TFTs at different  $V_{DD}$ .

potential of thermally evaporated (metal)chalcogenide TFTs for integrating more complex large-area logic circuits.

#### Discussion

This work demonstrated the wafer-scale growth of nanometer-scale (metal) chalcogenide thin films and the integration of complementary electronics via standard RT thermal evaporation. Compared with organic semiconductors (which are also compatible with thermal evaporation), (metal)chalcogenides show higher commercial potential as TFT channels because of their higher mobility and stability. Thermal evaporation significantly reduces the use of masks compared with metal oxides deposited by sputtering. In addition to CMOS circuit integration for various applications, thermally evaporated (metal)chalcogenide TFTs provide an opportunity to replace current expensive metal oxide/polycrystalline silico<sup>6,47</sup>. This would also enable further integration with thermally evaporated OLEDs in the same chamber and thereby, substantially reduce manufacturing procedures and costs.

The exploration of high-mobility p-type semiconductors capable of large-area deposition in a low-temperature and cost-effective manner

has received substantial attention owing to the highly advanced n-channel TFT technology. Te is becoming an emerging candidate for creating high-performance, stable p-channel transistors<sup>23</sup>. Thermal evaporation provides a simple means to grow scalable, high-quality Te films for laboratory and industrial applications. Our study demonstrates the feasibility of RT growth via the standard thermal evaporation of high-quality Te films. A common issue for Te TFTs is a marginally low  $I_{\rm on}/I_{\rm off}$  of 10<sup>4</sup>–10<sup>5</sup> with a relatively high OFF current owing to the small  $E_{\rm g}$ of the Te channel (-0.35 eV). In general, an  $I_{on}/I_{off} > 10^3$  is feasible for logic circuit operation<sup>7</sup>. However, this results in increased static power consumption. The following are proposed to overcome this issue: (1)  $E_{g}$ enlargement through Se alloying<sup>48</sup> or dimension down to the quantum limit<sup>22</sup> and (2) device engineering through external doping or dielectric encapsulation<sup>49</sup>. In addition, it is worthwhile to consider optimization of the deposition procedures (e.g., substrate temperature, nucleation layer, and deposition rate) and associated film quality in conjunction with contact/dielectric interface engineering, to further improve electrical properties<sup>50-52</sup>.

We report wafer-scale growth of nanometer (metal)chalcogenide semiconductors through simple RT thermal evaporation for highperformance complementary electronics. The n-type  $Bi_2S_3$  exhibits unique S-rich-dominated electrical properties with self-assembly crystallization under mild thermal post-annealing conditions. This enables the fabrication of high-performance TFTs with high stability and reproducibility. The combination of high-mobility p-channel Te TFTs further realizes high-gain CMOS inverters. Considering the low vapor pressure and substantially large library of the (metal)chalcogenide family, we anticipate that thermal evaporation would provide a robust and reliable pathway for the scalable production of high-quality functional thin films for large-area and flexible nanoelectronics.

#### Methods

#### Thin-film fabrication and characterizations

The Bi<sub>2</sub>S<sub>3</sub> powder (99%) and Te (99.8%) were purchased from Sigma-Aldrich and used directly as evaporation sources. Bi<sub>2</sub>S<sub>3</sub> and Te films were deposited using the same thermal evaporator via a standard procedure. The substrate temperature was maintained at RT, and the vacuum pressure before evaporation was  $-3 \times 10^{-6}$  Torr. The distance between the substrate and Bi<sub>2</sub>S<sub>3</sub>/Te-loaded tungsten boat was ~20 cm. The thickness of the Bi<sub>2</sub>S<sub>3</sub>/Te film was monitored during deposition. The as-deposited samples were then annealed at different temperatures for 30 min in a N<sub>2</sub>-filled glove box. The crystal structures of the films on glass were analyzed using XRD with Cu Ka radiation (Bruker D8 ADVANCE). AFM images were obtained using a Nanoscope V Multimode 8 (Bruker, Newark, DE, United States of America) on Si substrates. Optical absorption spectra were obtained using a UV-visible spectrophotometer (V-770, JASCO). Samples for HRTEM characterization were prepared using a focused ion beam (FIB). The images and FFT patterns were obtained using HRTEM (JEOL JEM 2100 F). XPS analysis was performed using a PHI 5000 VersaProbe instrument (Ulvac-PHI, Japan). The depth element distribution was measured by SIMS (IMS 6 F, CAMECA). The Hall measurements of the films were performed in an N<sub>2</sub>-filled glove box using the van der Pauw method with a 0.51 T magnet at RT.

#### TFT fabrication and characterizations

A heavily doped Si wafer (resistivity:  $1-100 \Omega$  cm) was used as the substrate and gate electrode. The 40 nm HfO<sub>2</sub> grown by ALD at 200 °C was used as the dielectric layer. Bi<sub>2</sub>S<sub>3</sub> and Te films were deposited on HfO<sub>2</sub> as the channel layers, using the procedure described above. The shadow mask was covered with HfO<sub>2</sub>/Si to obtain patterned Bi<sub>2</sub>S<sub>3</sub> and Te channel layers for reliable device characterization. Au and Ni source/drain electrodes (40 nm) were deposited on the Bi<sub>2</sub>S<sub>3</sub> and Te channel layers, respectively, with a shadow mask by using thermal evaporation to construct the bottom-gate, top-contact TFT. The channel length and width (L/W) were 100/800 µm. All the TFTs were characterized at RT in an N<sub>2</sub>-filled glove box using a Keithley 4200 SCS. The TFT mobilities were calculated in the saturation region using the following equation:

$$\mu_e = \frac{2L}{WC_i} \left(\frac{\partial \sqrt{I_{DS}}}{\partial V_{GS}}\right)^2 \tag{1}$$

$V_{\rm TH}$  was calculated by linearly fitting  $I_{\rm DS}^{1/2}$  to  $V_{\rm GS}$ . SS is the inverse of the maximum slope of the  $I_{\rm DS}$ - $V_{\rm GS}$  plot.

#### Data availability

The data that support the findings of this study are available within the paper and Supplementary Information. Additional relevant data are available from the corresponding authors upon reasonable request.

#### References

Myny, K. The development of flexible integrated circuits based on thin-film transistors. *Nat. Electron.* 1, 30 (2018).

- Biggs, J. et al. A natively flexible 32-bit Arm microprocessor. *Nature* 595, 532–536 (2021).

- 3. Shim, G. W. et al. TFT channel materials for display applications: From amorphous silicon to transition metal dichalcogenides. *Adv. Mater.* **32**, 1907166 (2020).

- 4. Franklin, A. D. Nanomaterials in transistors: From high-performance to thin-film applications. *Science* **349**, aab2750 (2015).

- Dai, Y., Hu, H., Wang, M., Xu, J. & Wang, S. Stretchable transistors and functional circuits for human-integrated electronics. *Nat. Electron.* 4, 17–29 (2021).

- Wager, J. F. TFT technology: advancements and opportunities for improvement. *Inf. Disp.* 36, 9–13 (2020).

- 7. Lin, Z., Huang, Y. & Duan, X. Van der Waals thin-film electronics. *Nat. Electron.* **2**, 378–388 (2019).

- 8. Woods-Robinson, R. et al. Wide band gap chalcogenide semiconductors. *Chem. Rev.* **120**, 4007–4055 (2020).

- 9. Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thinfilm transistors: A review of recent advances. *Adv. Mater.* **24**, 2945–2986 (2012).

- Yu, X., Marks, T. J. & Facchetti, A. Metal oxides for optoelectronic applications. *Nat. Mater.* 15, 383–396 (2016).

- 11. Liu, A. et al. High-performance inorganic metal halide perovskite transistors. *Nat. Electron.* **5**, 78–83 (2022).

- 12. Choi, S. H. et al. Large-scale synthesis of graphene and other 2D materials towards industrialization. *Nat. Commun.* **13**, 1484 (2022).

- Biswas, K., Zhao, L.-D. & Kanatzidis, M. G. Tellurium-free thermoelectric: The anisotropic n-type semiconductor Bi<sub>2</sub>S<sub>3</sub>. Adv. Energy Mater. 2, 634–638 (2012).

- 14. Li, D.-B. et al. Low-temperature-processed amorphous  $Bi_2S_3$  film as an inorganic electron transport layer for perovskite solar cells. ACS *Photon.* **3**, 2122–2128 (2016).

- 15. Miller, N. C. & Bernechea, M. Research update: Bismuth based materials for photovoltaics. *APL Mater.* **6**, 084503 (2018).

- Han, D., Du, M.-H., Dai, C.-M., Sun, D. & Chen, S. Influence of defects and dopants on the photovoltaic performance of Bi<sub>2</sub>S<sub>3</sub>: Firstprinciples insights. *J. Mater. Chem. A* 5, 6200–6210 (2017).

- Nishikubo, R. & Saeki, A. Solution-processed Bi<sub>2</sub>S<sub>3</sub> photoresistor film to mitigate a trade-off between morphology and electronic properties. J. Phys. Chem. Lett. 9, 5392–5399 (2018).

- 18. Martinez, L., Bernechea, M., de Arquer, F. P. G. & Konstantatos, G. Near IR-sensitive, non-toxic, polymer/nanocrystal solar cells employing  $Bi_2S_3$  as the electron acceptor. *Adv. Energy Mater.* **1**, 1029–1035 (2011).

- Rath, A. K. et al. Solution-processed inorganic bulk nanoheterojunctions and their application to solar cells. *Nat. Photon.* 6, 529–534 (2012).

- 20. Konstantatos, G., Levina, L., Tang, J. & Sargent, E. H. Sensitive solution-processed  $Bi_2S_3$  nanocrystalline photodetectors. *Nano Lett.* **8**, 4002–4006 (2008).

- 21. Zhao, C. et al. Evaporated tellurium thin films for p-type field-effect transistors and circuits. *Nat. Nanotechnol.* **15**, 53–58 (2020).

- 22. Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. *Nat. Electron.* **1**, 228–236 (2018).

- 23. Qiu, G. et al. The resurrection of tellurium as an elemental twodimensional semiconductor. *npj 2D Mater. Appl* **6**, 17 (2022).

- Kwon, S. M. et al. High-performance and scalable metalchalcogenide semiconductors and devices via chalco-gel routes. *Sci. Adv.* 4, eaap9104 (2018).

- Mitzi, D. B., Kosbar, L. L., Murray, C. E., Copel, M. & Afzali, A. Highmobility ultrathin semiconducting films prepared by spin coating. *Nature* 428, 299–303 (2004).

- Dutta, N. S. & Arnold, C. B. Scalable solution processing of amorphous and crystalline chalcogenide films. *Trends Chem.* 3, 535–546 (2021).

#### https://doi.org/10.1038/s41467-022-34119-6

# Article

- 27. Lin, Z. et al. Cosolvent approach for solution-processable electronic thin films. *ACS Nano* **9**, 4398–4405 (2015).

- Ippolito, S. et al. Covalently interconnected transition metal dichalcogenide networks via defect engineering for high-performance electronic devices. *Nat. Nanotechnol.* 16, 592–598 (2021).

- Nicolosi, V., Chhowalla, M., Kanatzidis, M. G., Strano, M. S. & Coleman, J. N. Liquid exfoliation of layered materials. Science 340, 1226419 (2013).

- Lin, Z. et al. Solution-processable 2D semiconductors for highperformance large-area electronics. *Nature* 562, 254 (2018).

- Liu, C., Xu, Y. & Noh, Y.-Y. Contact engineering in organic fieldeffect transistors. *Mater. Today* 18, 79–96 (2015).

- Sakanoue, T. & Sirringhaus, H. Band-like temperature dependence of mobility in a solution-processed organic semiconductor. *Nat. Mater.* 9, 736 (2010).

- Ji, D. et al. Band-like transport in small-molecule thin films toward high mobility and ultrahigh detectivity phototransistor arrays. *Nat. Commun.* **10**, 12 (2019).

- 34. Liu, A. et al. High-performance p-channel transistors with transparent Zn doped-Cul. *Nat. Commun.* **11**, 4309 (2020).

- Dong, R. et al. High-mobility band-like charge transport in a semiconducting two-dimensional metal-organic framework. *Nat. Mater.* 17, 1027 (2018).

- Kelly, A. G. et al. All-printed thin-film transistors from networks of liquid-exfoliated nanosheets. Science 356, 69–73 (2017).

- Piatti, E. et al. Charge transport mechanisms in inkjet-printed thinfilm transistors based on two-dimensional materials. *Nat. Electron.* 4, 893–905 (2021).

- Wu, Z. et al. Large-scale growth of few-layer two-dimensional black phosphorus. *Nat. Mater.* 20, 1203–1209 (2021).

- Wu, J. et al. High electron mobility and quantum oscillations in nonencapsulated ultrathin semiconducting Bi<sub>2</sub>O<sub>2</sub>Se. Nat. Nanotechnol. 12, 530–534 (2017).

- Rahman, A. A., Huang, R. & Whittaker-Brooks, L. Distinctive extrinsic atom effects on the structural, optical, and electronic properties of Bi<sub>2</sub>S<sub>3-x</sub>Se<sub>x</sub> solid solutions. *Chem. Mater.* 28, 6544–6552 (2016).

- Shi, H., Ming, W. & Du, M.-H. Bismuth chalcohalides and oxyhalides as optoelectronic materials. *Phys. Rev. B* 93, 104108 (2016).

- Kim, Y., Jeong, E., Joe, M. & Lee, C. Synthesis of 2D semiconducting single crystalline Bi<sub>2</sub>S<sub>3</sub> for high performance electronics. *Phys. Chem. Chem. Phys.* 23, 26806–26812 (2021).

- Lin, Z. et al. Defect engineering of two-dimensional transition metal dichalcogenides. 2D Mater. 3, 022002 (2016).

- Guo, Y., Zhou, S. & Zhao, J. Oxidation behaviors of two-dimensional metal chalcogenides. *ChemNanoMat* 6, 838–849 (2020).

- Liu, A., Zhu, H. & Noh, Y.-Y. Solution-processed inorganic p-channel transistors: Recent advances and perspectives. *Mat. Sci. Eng. R.* 135, 85–100 (2019).

- Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. *Nat. Electron.* 1, 442–450 (2018).

- Zhu, H. et al. Printable semiconductors for backplane TFTs of flexible OLED displays. Adv. Funct. Mater. 30, 1904588 (2020).

- Tan, C. et al. Evaporated Se<sub>x</sub>Te<sub>1-x</sub> thin films with tunable bandgaps for short-wave infrared photodetectors. *Adv. Mater.* 32, 2001329 (2020).

- Kim, T. et al. Growth of high-quality semiconducting tellurium films for high-performance p-channel field-effect transistors with waferscale uniformity. npj 2D Mater. Appl 6, 4 (2022).

- Okuyama, K., Yamamoto, H. & Kumagai, Y. Effect of Au nucleation centers and deposition rate on crystallinity and electronic properties of evaporated Te films. J. Appl. Phys. 46, 105–111 (1975).

- 51. Zhang, X. et al. All-van-der-Waals barrier-free contacts for highmobility transistors. *Adv. Mater.* **34**, 2109521 (2022).

- 52. Yang, P. et al. Growth of tellurium nanobelts on h-BN for p-type transistors with ultrahigh hole mobility. *Nano-Micro Lett.* **14**, 109 (2022).

# Acknowledgements

This study was supported by the Ministry of Science and ICT through the National Research Foundation, funded by the Korean Government (NRF-2020M3D1A1110548), Samsung Display Corporation, and LG Display Corporation.

### **Author contributions**

A.L. and Y.Y.N. conceived the study. A.L. performed the experiments and analyzed the data. H.H.Z. and Y.R. assisted in film characterization and analysis. A.L., T.Y.Z., H.H.Z., and G.S.R. designed the circuit and performed the measurements. A.L. and Y.Y.N. wrote the paper. All the authors have contributed to the final version of this paper.

### **Competing interests**

The authors declare no competing interests.

## **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-022-34119-6.

**Correspondence** and requests for materials should be addressed to Yong-Young Noh.

**Peer review information** *Nature Communications* thanks the anonymous reviewers for their contribution to the peer review of this work. Peer reviewer reports are available.

# **Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/ licenses/by/4.0/.

© The Author(s) 2022