Hindawi Publishing Corporation Journal of Engineering Volume 2016, Article ID 2490926, 18 pages http://dx.doi.org/10.1155/2016/2490926

## Research Article

# **Experimental Evaluation on the Influence of RCD Snubbers in a 3-Level Thyristor Based MLCR CSC**

# Bhaba P. Das, 1 Neville R. Watson, 2 and Yonghe Liu<sup>2,3</sup>

<sup>1</sup>The Engineering Department, ETEL Ltd., Auckland 0640, New Zealand

Correspondence should be addressed to Bhaba P. Das; bhaba.das@eteltransformers.co.nz

Received 27 September 2015; Accepted 18 May 2016

Academic Editor: Jiun-Wei Horng

Copyright © 2016 Bhaba P. Das et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Multilevel current reinjection (MLCR) concept provides self-commutation capability to thyristors, enabling thyristor based current source converters (CSC) to operate under negative firing angle. It also lowers the input current harmonic distortion. This is achieved by using an auxiliary reinjection bridge. Extensive experimental results are presented in this paper to analyse the performance of the 3-level MLCR CSC for different snubber components across the reinjection bridge. The trade-off in the choice of the snubber circuit is illustrated, with its influence on the AC side line current and DC side output voltage of the 3-level MLCR CSC.

## 1. Introduction

In order to reduce the harmonic content in the line current caused by High Voltage Direct Current (HVDC) converters, different strategies have been proposed. These are (i) multipulse methods, (ii) multilevel methods, and (iii) pulse-width modulation (PWM) methods.

Different methods for increasing the number of pulses using multipulse converters have been investigated [1]. The simplest method is by increasing the pulse number by using phase-shifting transformers. Multipulse converters such as 12-, 18-, 24-, and 36-pulse converter are used nowadays and the total harmonic distortion (THD) of the input line current of these converters has been reduced to around 15.2%, 10.1%, 7.5%, and 5.3%, respectively. Many modelling techniques for phase-shifting converter transformers have been also proposed in [2–4] to meet the IEEE 519 standards. However, the weakness of these methods is the increase in size and complexity of the transformer and the high costs involved due to multiple 6-pulse bridges. A DC side current injection method [5] improves the quality of the AC side line currents by using a three-phase current-controlled inverter which injects compensation currents in the AC side of the converter. However, this method uses a complex 18-pulse phase-shifting transformer.

Multilevel converters give significantly lower switching losses and better harmonic performance [6-8] than equivalent series-connected converters operating at the same rating and carrier frequency but advantages of multilevel converter are counterbalanced by the need for self-commutated switches instead of thyristors, balancing of capacitors, and so forth. Modular current source converters (MCSC) utilise PWM techniques just like the PWM-voltage source converters (VSC). Two-level PWM-VSC or Modular Multilevel Converter (MMC) [9] has been used by the industry, for example, HVDC-light and HVDC-plus, respectively. However, they are only being used for medium voltage HVDC transmission. MCSC utilise selective harmonic elimination [10] as the PWM strategy but the use of thyristors in the main bridge is still not possible. Ongoing research in the field of MMC converters includes direct power control [11], neural network based sliding mode control [12], and fuzzy logic based control [13].

It is now established that PWM-VSC/MMC/MCSC technology is well suited for the medium voltage levels but will not be able to catch up with the thyristor based technology in terms of high power handling capacity in the very near future. Thus, there is a clear incentive for research in the thyristor based HVDC technology to achieve the following:

$<sup>^2</sup>$ The Department of Electrical and Computer Engineering, University of Canterbury, Christchurch 8140, New Zealand

<sup>&</sup>lt;sup>3</sup>Inner Mongolia University of Technology, Hohhot, China

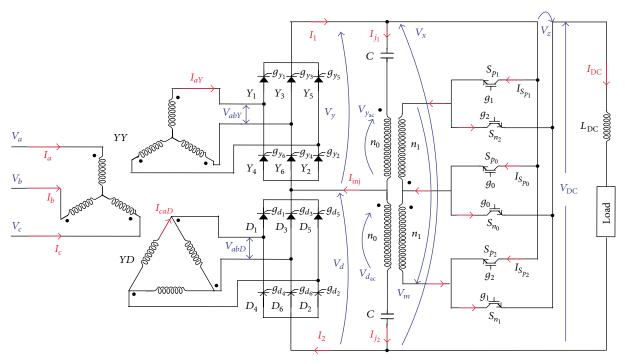

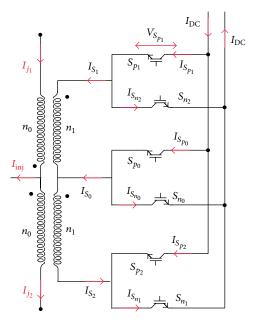

FIGURE 1: Three-level thyristor based MLCR CSC with Linear Reinjection.

- (i) Achieve force commutation with thyristors.

- (ii) Operate at negative firing angles enabling reactive power export.

- (iii) Operate the thyristors under zero-current switching lowering the switching losses, voltage stress, and costs.

- (iv) Reduce harmonic distortion caused by thyristor based systems.

The new concept of multilevel current reinjection (MLCR) [14] combines the advantages of DC-ripple reinjection [15, 16] and multilevel conversion and soft switching technique. Thyristor based MLCR current source converter (CSC) was proposed in [17] where the magnitude and duration of the reinjection current, used to minimize the harmonic content, were adjusted to ensure that the currents through the main bridge thyristors are forced to zero during the main bridge commutations instants. This possibility had the important implication that the thyristors do not need to rely on the line voltage to commutate and are capable of operating with firing angles that provide leading power-factor just like self-commutating switches. Based on this, the self-commutated HVDC MLCR CSC was introduced in [18].

However, questions have been raised about the ability to force the main thyristors off using the reinjection bridge. In a real world implementation, there are inevitable stray capacitance and inductances which may influence the thyristor turn-off and simulation switching model may not fully represent the switching characteristics accurately. The question that needed answering was whether these would hinder the self-commutation ability with thyristors. For this proof of concept, a small-scale prototype of a 3-level MLCR CSC has

been built in the laboratory. The experimental investigation (under steady-state conditions), presented here, shows that the line currents in AC side of MLCR CSC follow the theoretical current wave-shape well. This has clearly demonstrated that self-commutation ability is achievable in a practical system by the use of an auxiliary reinjection bridge.

RCD snubber is necessary across the reinjection bridge switches to limit the sharp rise in voltage across it due to the sudden interruption of current flowing through it. This paper presents the experimental investigation of the influence of the RCD snubber across the reinjection switches in a 3-level thyristor based MLCR CSC performance. This paper is divided into the following sections: Section 2 provides the brief introduction to the 3-level thyristor based MLCR CSC; Section 3 provides the PSCAD/EMTDC simulation results, with and without the RCD snubber circuit, of the performance of the 3-level MLCR CSC. Section 4 presents some of the main hardware modules while Section 5 presents the experimental results obtained. The trade-off in choice of the snubber circuit is explained clearly with respect to AC side line current and DC side voltage waveforms.

## 2. Three-Level Thyristor Based MLCR CSC

Figure 1 shows the 3-level thyristor based MLCR CSC along with the reinjection circuit. The reinjection transformer is a single-phase two-winding transformer with 1:1 turns ratio. The primaries of the two single-phase transformers are connected across the DC bus through DC blocking capacitors (C). The DC current ( $I_{\rm DC}$ ) flows through the reinjection IGBTs and load inductance ( $L_{\rm DC}$ ) and the load. It is chopped into AC waveforms in the secondary windings

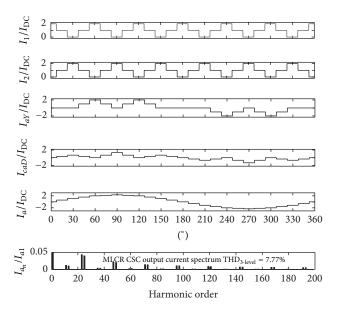

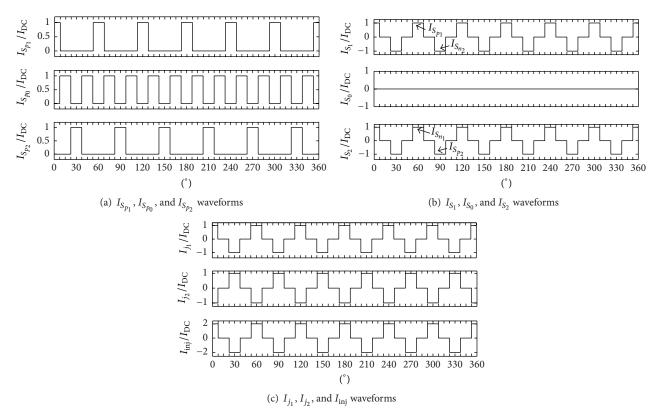

FIGURE 2: Current waveforms for 3-level thyristor based MLCR CSC with Linear Reinjection.

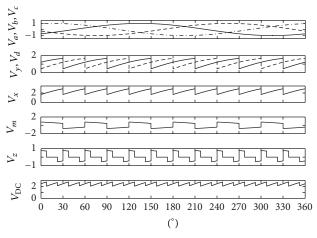

Figure 3: Theoretical DC voltage waveforms for 3-level thyristor based MLCR CSC for  $\alpha = -45^{\circ}$ .

of the reinjection transformer with the help of reinjection switches  $(S_{p_1}/S_{n_1},$  etc.). These currents are coupled to the reinjection transformer primary winding to form multilevel currents  $I_{j_1}$  and  $I_{j_2}$  which combine with  $I_{\rm DC}$  to shape the DC bus currents  $I_1$  and  $I_2$  into multilevel waveforms. This reinjection circuit generates three current steps in  $I_1$  and  $I_2$ . Two levels are generated due to reverse connected switches  $(S_{p_1}/S_{n_1}$  and  $S_{p_2}/S_{n_2})$  and one additional level is obtained by firing  $S_{p_0}/S_{n_0}$  when  $I_{j_1}$  and  $I_{j_2}$  are both zero.

2.1. AC Side Current Waveforms. The theoretical analysis of the circuit shown in Figure 1 allows  $I_a(\omega t)$  to be determined from the time domain components of the AC side secondary currents  $I_{aY}(\omega t)$  and  $I_{caD}(\omega t)$ . This gives

$$I_{a}(\omega t) = \frac{1}{k_{n}} \left[ I_{aY}(\omega t) + \sqrt{3} I_{caD}(\omega t) \right], \tag{1}$$

where  $k_n$  is interface transformer turns ratio. The corresponding current waveforms are shown in Figure 2 where the resulting current  $(I_a)$  THD<sub>3 level</sub> of 7.77% is obtained.

2.2. DC Side Voltage Waveforms. The DC side voltage waveforms (Figure 3) are time referenced with respect to the AC side current waveform  $I_a$  (Figure 2). The DC side voltages across the individual bridges  $(V_y(\omega t) \text{ and } V_d(\omega t))$  are plotted in Figure 3 with respect to the peak phase source voltage  $(V_{p_k})$  and can be expressed as for the first  $\pi/6$  interval as

$$\begin{split} V_{y}\left(\omega t\right) &= \frac{\sqrt{3}}{k_{n}} V_{p_{k}} \cos\left(\omega t + \alpha\right), \\ V_{d}\left(\omega t\right) &= \frac{\sqrt{3}}{k_{n}} V_{p_{k}} \cos\left(\omega t + \alpha - \frac{\pi}{6}\right), \\ V_{x}\left(\omega t\right) &= V_{y}\left(\omega t\right) + V_{d}\left(\omega t\right), \end{split} \tag{2}$$

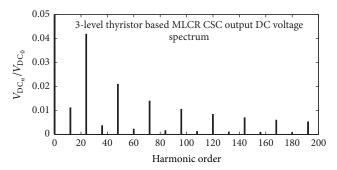

FIGURE 4: Harmonic spectrum of  $V_{\rm DC}$  of 3-level thyristor based MLCR CSC for  $\alpha = -45^{\circ}$ .

FIGURE 5: Reinjection current flow for a 3-level MLCR CSC.

where  $\alpha$  is firing angle. The DC load voltage  $(V_{\rm DC})$  is calculated as

$$V_{\rm DC}(\omega t) = V_x(\omega t) + V_z(\omega t) \approx 3.39 \frac{V_{p_k}}{k_n} \cos \alpha.$$

(3)

The harmonic spectrum of  $V_{\rm DC}$  is shown in Figure 4. It can be clearly seen that the dominant harmonics are 24th, 48th, 72nd, 96th, and 120th which represents 24-pulse operation. A small amount of 12-pulse related harmonics such as 12th, 36th, and 60th can also be seen but the magnitude is negligible.

- 2.3. Reinjection Current Waveforms. Figure 5 labels the various current waveforms in the reinjection circuit. The "chopping" of load current  $I_{\rm DC}$  occurs with the help of the reinjection IGBTs. The injection current  $I_{\rm inj}$  is a 3-level waveform composed of the following:

- (i) When reinjection IGBT pair  $S_{p_1} S_{n_1}$  conducts,  $I_{j_1} = (n_1/n_0)I_{\rm DC} = I_{\rm DC}.$

- (ii) When reinjection IGBT pair  $S_{p_0} S_{n_0}$  conducts,  $I_{j_1} = 0$ .

(iii) When reinjection IGBT pair  $S_{p_2} - S_{n_2}$  conducts,  $I_{j_1} = -(n_1/n_0)I_{\rm DC} = -I_{\rm DC}$ .

Reinjection currents  $I_{j_1}$  and  $I_{j_2}$  add up to form  $I_{\rm inj}$  which is injected back to the midpoint of the 12-pulse converter. The theoretical current waveforms in the reinjection circuit are shown in Figure 6.

## 3. PSCAD/EMTDC Verification

This section presents the PSCAD/EMTDC simulation results of the thyristor based 3-level MLCR CSC. The converter is directly connected to a balanced 3-phase voltage source with series resistance and series inductance. The simulation is carried out under the conditions listed in the Appendix.

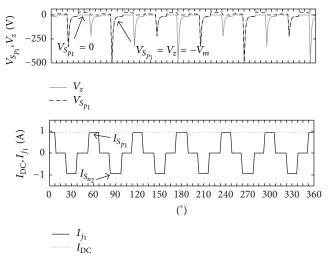

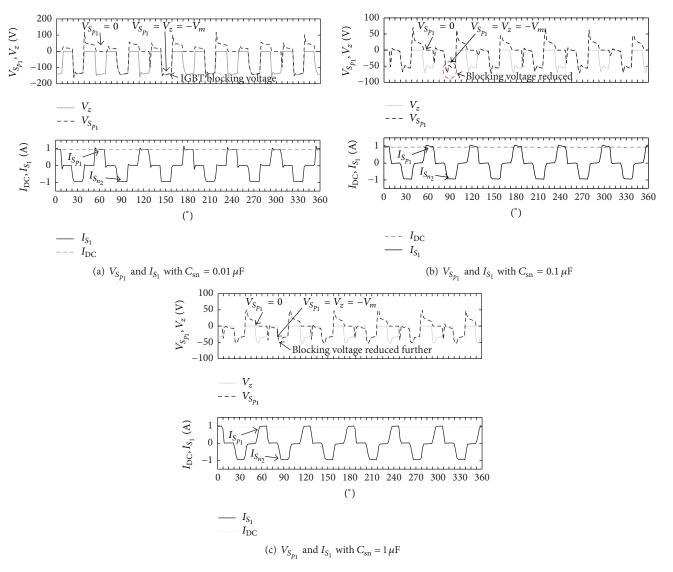

3.1. Waveforms without RCD Snubber. The voltage waveform across the reinjection IGBT  $S_{p_1}$  as well as the current flowing through it, without the RCD snubber, is shown in Figure 7. It can be clearly seen that there is a sharp rise in voltage across  $V_{S_{p_1}}$  whenever there is a current transition through

FIGURE 6: Theoretical waveforms in the reinjection circuit.

Figure 7:  $V_{S_{p_1}}$  and  $I_{S_1}$  with no snubber.

it, that is, current transition from 0 to  $-I_{\rm DC}$  or 0 to  $I_{\rm DC}$ . This effect was not considered while deriving the theoretical waveforms. As seen from Figure 8, these voltage spikes occur across the individual DC voltage waveform of the two 6-pulse bridges which in turn affect the voltages  $V_m$  and  $V_z$ . The spikes occur exactly 7.5° before and after the theoretical main bridge switching instant. Thus there is a need to limit the voltage dv/dt using RCD snubber to an acceptable value so that the voltage across the main bridge switches and DC

blocking capacitor and the reinjection transformer are within their rated values.

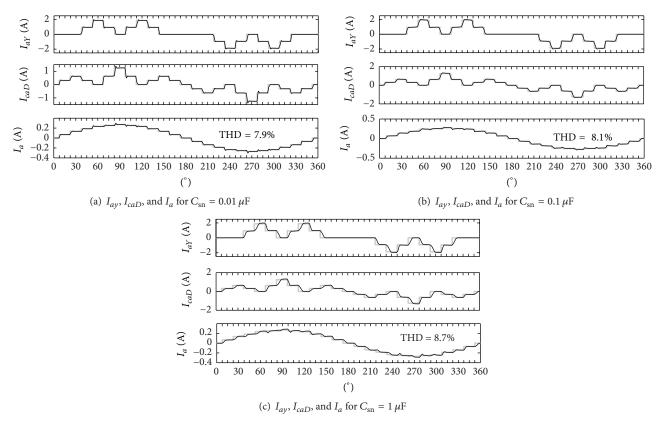

The simulated AC side current waveforms are shown in Figure 9. The simulated line current THD of 7.8% is very close to the calculated theoretical value.

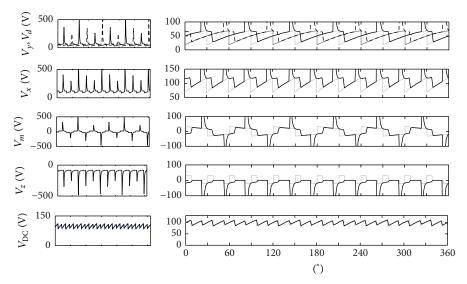

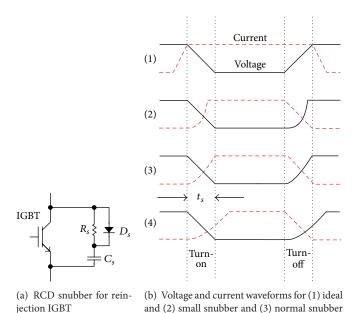

3.2. Waveforms with RCD Snubbers. As illustrated in Figure 10(b), the snubber capacitor size is a trade-off between dv/dt across the reinjection switches and switching

Figure 8: Simulated DC voltage waveforms for 3-level thyristor based MLCR CSC for  $\alpha = -45^{\circ}$  without RCD snubber.

Figure 9: Simulated AC current waveforms for 3-level thyristor based MLCR CSC for  $\alpha = -45^{\circ}$  without RCD snubber.

time. A "normal" snubber is defined as the one which allows the current to reach the rated level at the same time the voltage reaches zero. A small snubber allows the current to rise faster while a large snubber slows the current rise rate. However, large capacitor values will provide overclamping. When the RCD snubber is used to control the rate of voltage rise at the IGBT, the capacitor must be completely charged and discharged during each cycle to be able to control the rate-of-rise of the drain voltage. The RC time constant of the snubber should be much smaller than the switching period. Usually, the time constant ( $\tau_{\rm RC}$ ) should be (1/10)th of the switching period. The value of snubber capacitor  $C_{\rm sn}$  is given by the following equation [19]:

$$C_{\rm sn} = \frac{It_s}{2E},\tag{4}$$

where *I* is maximum IGBT current (assumed) = 2 A,  $t_s$ :  $\approx 1.65 \, \mu s$  (3 times the value given in the datasheet of the IGBT), and *E* is the maximum expected voltage across IGBT:  $\approx 0.9 (V_{p_b}/k_n) \approx 36.72 \, \text{V}$  for the present application.

Substituting these values in (4) gives  $C_{\rm sn}=0.045\,\mu{\rm F}$ . The value of  $R_{\rm sn}$  is determined by allowing the switching time constant ( $\tau_{\rm RC}$ ) to be less than 166.66  $\mu{\rm s}$  ((1/10)th of 600 Hz). With  $C_{\rm sn}=0.05\,\mu{\rm F}$  and  $R_{\rm sn}=1\,{\rm k}\Omega$ ,  $\tau_{\rm RC}=50\,\mu{\rm s}$ .

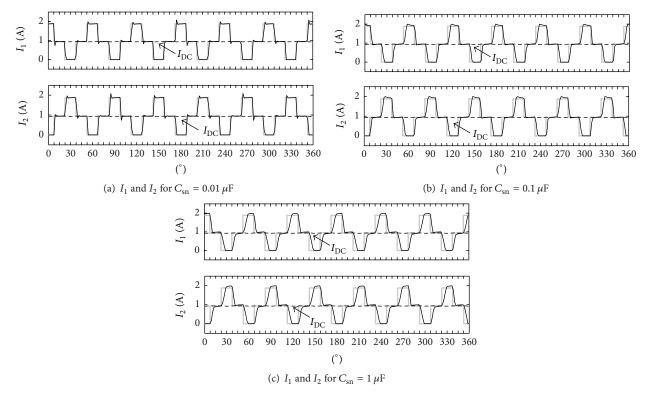

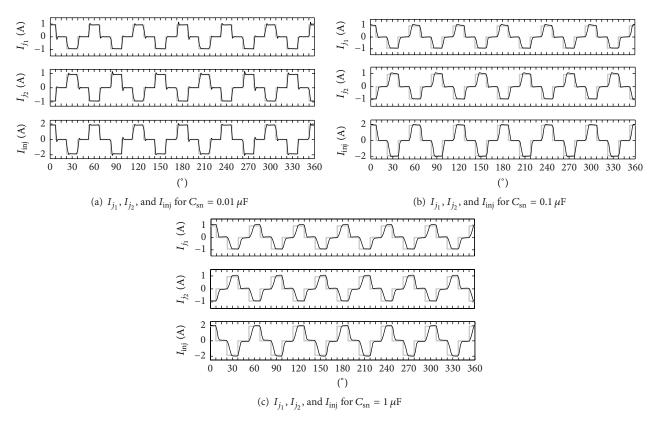

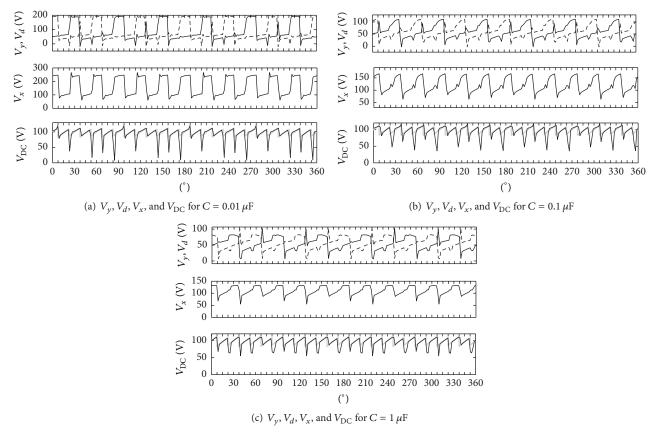

Three different cases are considered in this study, small  $C_{\rm sn}=0.01\,\mu{\rm F}$ , large  $C_{\rm sn}=0.1\,\mu{\rm F}$ , and very large  $C_{\rm sn}=1\,\mu{\rm F}$ . The PSCAD/EMTDC results are presented in Figures 11–15. From Figure 11, with  $C_{\rm sn}=1\,\mu{\rm F}$  the voltage across  $V_{S_{p_1}}$  is closest to its calculated value; however the rate of current rise for the switch  $S_{p_1}$  is slowest.  $C_{\rm sn}=0.01\,\mu{\rm F}$  provides higher rate of current rise in  $S_{p_1}$  and the current reinjection current resembles the theoretical current more closely. THD for line current  $I_a$  is obtained as 7.9%, 8.1%, and 8.7%, respectively, with  $C_{\rm sn}=0.01\,\mu{\rm F}$ ,  $0.1\,\mu{\rm F}$ , and  $1\,\mu{\rm F}$  (Figures 12–14). The effectiveness of the MLCR scheme depends on the modification of the constant DC bus current into a 3-level DC bus current using reinjection current  $I_{\rm inj}$ . The use of small  $C_{\rm sn}$  is found to be the best even though it requires overrated reinjection switches as shown in Figure 11.

FIGURE 10: Snubber consideration for reinjection switches.

and (4) large snubber

## 4. Hardware Modules

The major components of the experimental set-up consist of voltage sensing, thyristor driver circuit, IGBT driver circuit, and so forth. Each will be discussed in the following sections.

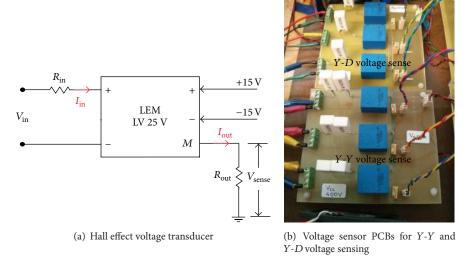

4.1. Voltage Transducer Circuit. Voltage sensors LEM LV25-P [20] are used to convert power level voltage into low voltage signals by scaling down the measured voltage to 5  $V_{\rm RMS}$  The Hall effect transducers provide the isolation between the high power system and the control electronic circuit. For a 12-pulse converter, six voltage sensors are used. The line voltages sensed are  $V_{an}$ ,  $V_{bn}$ ,  $V_{cn}$ ,  $V_{ab}$ ,  $V_{bc}$ , and  $V_{ca}$ . The triggering signals for the Y-Y and Y-D connected converters are derived from the low voltage sensed signals  $V_{ca_Y}$  and  $-V_{an_Y}$ , respectively.

The LV25-P scales down the power level voltage into low level signal when a current proportional to the measured voltage is passed through the resistor  $R_{\rm in}$  (Figure 16(a)). For the best accuracy of LV25-P,  $R_{\rm in}$  should be so selected that the voltage measured corresponds to a primary current ( $I_{\rm in_{RMS}}$ ) of 10 mA. The current conversion ratio is 2.5; hence, the nominal secondary current is 25 mA. This secondary current flows through an output series resistance  $R_{\rm out}$  to give the scaled down voltage. The fabricated PCB for this purpose is shown in Figure 16(b). The maximum and minimum value of the series resistance  $R_{\rm out}$  with a ±15 V supply are between 100  $\Omega$  and 350  $\Omega$ .

The 12-pulse interface transformer rating is  $(V_{\rm LL_{RMS}})$  400 V : 50 V. The primary side input resistance is calculated as

$$R_{\rm in} = \frac{400 \,\mathrm{V}}{10 \,\mathrm{mA}} \approx 40 \,\mathrm{k}\Omega. \tag{5}$$

A fixed value resistor of  $40 \text{ k}\Omega/5 \text{ W}$  is used.

The output voltage is fixed at 5  $V_{\rm RMS}$ . Therefore, the output resistance  $R_{\rm out}$  is calculated as

$$R_{\rm out} = \frac{5}{25\,{\rm m\,A}} \approx 200\,\Omega. \tag{6}$$

A variable 500  $\Omega/0.6$  W resistor is used.

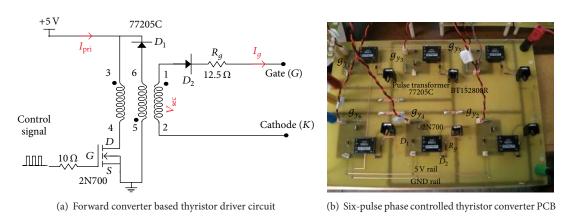

4.2. Forward Converter Based Thyristor Driver Circuit. The thyristor driver circuit is based on the forward converter topology with isolation between the control and power circuit being provided by the 77205C pulse transformer [21] (Figure 17(a)).

When the MOSFET is on, diode  $D_2$  conducts and  $V_{\rm sec}=5\,{\rm V}$  is available across the secondary winding of the pulse transformer.  $V_{\rm sec}$  drives gate current  $I_g$  in the gate-cathode junction of the thyristor to turn it on. For  $I_g\approx 200\,{\rm mA}$ , the gate drive resistor  $R_g=12.5\,\Omega$ . When the MOSFET is off, diode  $D_1$  returns the energy stored in the pulse transformer back to the supply. The 6-pulse thyristor PCB is shown in Figure 17(b) which uses BT152800R thyristors [22].

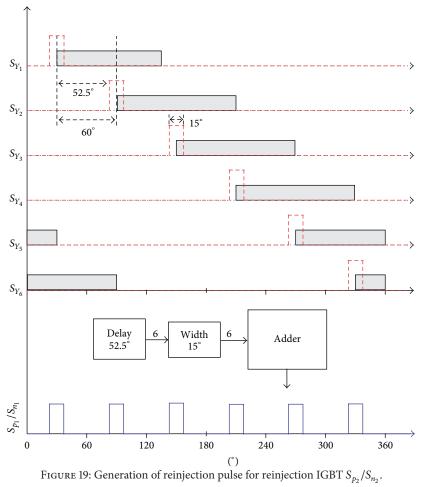

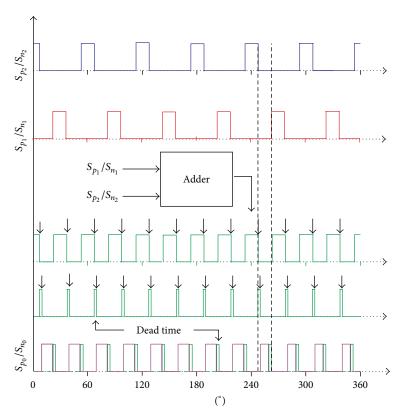

4.3. Generating of Reinjection Pulses for 3-Level MLCR. In order to produce the firing sequence needed to generate the 3-level  $I_{\rm inj}$ , the firing sequences of the reinjection IGBTs are synchronised with the main bridge switching. In Figure 18 it is shown that each reinjection turn-on pulse is delayed from the main bridge switching pulse by 52.5° and the width of the turn-on pulse is 15°. Based on the six main bridge switching pulses, six reinjection turn-on pulses are derived and these are added together from the reinjection pulse for reinjection IGBT pair  $S_{p_1}/S_{n_1}$ . Following a similar procedure, the reinjection pulse for reinjection IGBT pair  $S_{p_2}/S_{n_2}$  is also derived as shown in Figure 19. A minimum dead time of 10  $\mu$ s is selected between  $S_{p_1}/S_{n_1}$  and  $S_{p_0}/S_{n_0}$  and  $S_{p_2}/S_{n_2}$  and the

Figure 11: Voltage across reinjection IGBT  $S_{p_1}$  for different  $C_{\rm sn}$ .

derivation of the reinjection pulse for  $S_{p_0}/S_{n_0}$  is shown in Figure 20.

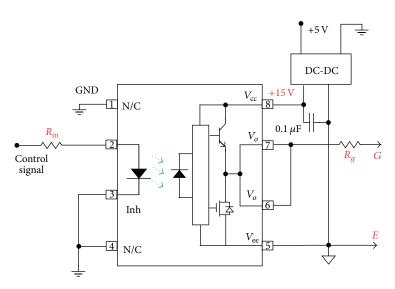

4.4. Optocoupler Based IGBT Driver Circuit. The isolated gate driver ACPL-312T [23] is used for this purpose. The response of optocoupler depends on the value of gate resistance ( $R_g$ ).  $R_g$  is calculated from the peak gate current ( $I_{G_{\rm peak}}$ ) of 2.5 A (from ACPL-312T datasheet).  $V_{\rm OL}$  is obtained from Figure 6 in the ACPL-312T datasheet, assuming temperature = 25°. Consider

$$R_g \ge \frac{V_{\rm cc} - V_{\rm OL}}{I_{G_{\rm peak}}} = \frac{15 - 3.5}{2.5} = 4.6 \,\Omega.$$

(7)

The value of the gate resistance has a significant impact on the dynamic performance of IGBTs. A smaller gate resistor charges and discharges the power transistor input capacitance faster, reducing switching times and switching losses. The trade-off is that this could lead to higher voltage oscillations.

At lower  $R_g$  values, the voltage supplied by the ACPL-312T is not an ideal voltage step. Since the maximum peak gate current of the driver must be equal to or lower than  $I_{G_{\rm peak}}$ , choosing  $R_g=10~\Omega$  is a good trade-off.

Once the logical signals (reinjection pulses for reinjection switches) are available, these are fed to the IGBT driver circuit. The driver circuit is shown in Figure 21. Since there are six reinjection switches (IXGP20N [24]) for a 3-level MLCR CSC, six isolated DC-DC converters are required for the ACPL-312T. The isolated DC-DC converter 0515S [25] from Tracopower is used here.  $V_{\rm cc}=15\,\rm V$  is chosen because the output voltage ( $V_o$ ) of ACPL-312T goes high when  $V_{\rm cc}-V_{\rm ee}$  is between 13.5 V and 30 V. Input resistance for ACPL-312T,  $R_{\rm in}$ , is calculated as follows (input current  $I_{\rm in}$  of ACPL-312T needs to be limited between 7 mA and 16 mA):

$$R_{\rm in} = \frac{15 - 1.5}{10 \,\mathrm{mA}} \approx 1.5 \,\mathrm{k}\Omega.$$

(8)

FIGURE 12: Simulated AC side current and DC bus waveforms for the 3-level thyristor based MLCR CSC.

FIGURE 13: Simulated AC side current and DC bus waveforms for the 3-level thyristor based MLCR CSC.

FIGURE 14: Simulated Reinjection current and DC side voltage waveforms for the 3-level thyristor based MLCR CSC.

FIGURE 15: Simulated Reinjection current and DC side voltage waveforms for the 3-level thyristor based MLCR CSC.

FIGURE 16: Voltage transducer circuit and fabricated PCB.

FIGURE 17: Forward converter based thyristor driver circuit and PCB detail.

A decoupling capacitor of 0.1  $\mu$ F is placed across  $V_{\rm cc}$  and  $V_{\rm ee}$ , very close to the optocoupler itself to filter out any noise coming from the isolated DC-DC converter.

4.5. DC Blocking Capacitor. A 400 V/1 mF (PEH200 Series,  $\pm 20\%$ ) electrolytic capacitor is used as the DC blocking capacitor. This unit is rated for a total of 5.9 A based on an equivalent series resistance (ESR) of 76 m $\Omega$  at a frequency of 100 Hz and equivalent series inductance (ESL) of 16 nH which gives  $Z_{100\,\mathrm{Hz}}=1.59\,\Omega$ . The maximum average steady-state DC voltage for this 3-level MLCR CSC prototype is \$138 V,  $I_{\mathrm{DC}}=1.38\,\mathrm{A}$ . The RMS value of reinjection currents  $I_{j_1}$  and  $I_{j_2}=0.707\times1.38=0.975\,\mathrm{A}\approx1\,\mathrm{A}$  which is well under the rating of PEH200 capacitor. Figure 22 shows the set-up for the reinjection transformer along with the DC blocking capacitors.

## 5. Experimental Results

Real world capacitors often have  $\pm 1\% - \pm 20\%$  variation in the capacitance values while resistors also have  $\pm 1\% - \pm 5\%$

variation; thus exact DC bus currents ( $I_1$  and  $I_2$ ) may not be possible in hardware implementation. However, for comparison with the theoretical waveforms, the experimental and theoretical waveforms are overlapped together. Two different types of PCBs with  $C_{\rm sn}$ : 0.01  $\mu$ F and 1  $\mu$ F (Figure 23) are fabricated and the results are summarized in this section. The experimental  $V_{\rm DC}$  obtained from the prototype is 96.3 V and  $I_{\rm DC}=0.97$  A with  $\alpha=-45^\circ$ .

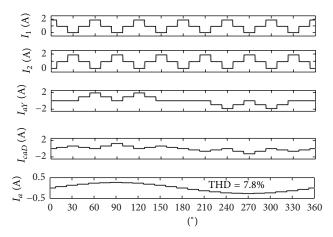

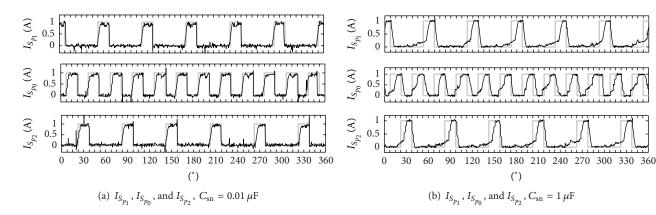

- 5.1. Current through Reinjection IGBTs. Figure 24 shows the current flowing through reinjection IGBTs  $S_{p_1}$ ,  $S_{p_0}$ , and  $S_{p_2}$ . For  $C_{\rm sn}=0.01\,\mu{\rm F}$  (Figure 24(a)), these waveforms follow the theoretical waveform closely with  $I_{S_{p_1}}\approx I_{\rm DC}$  for almost the entire theoretical duration of 15°. As observed from Figure 24(b), with  $C_{\rm sn}=1\,\mu{\rm F}$ ,  $I_{S_{p_1}}\approx I_{\rm DC}$  for less than half of the theoretical duration. These waveforms constitute the "chopping" of  $I_{\rm DC}$  and formation of the reinjection currents.

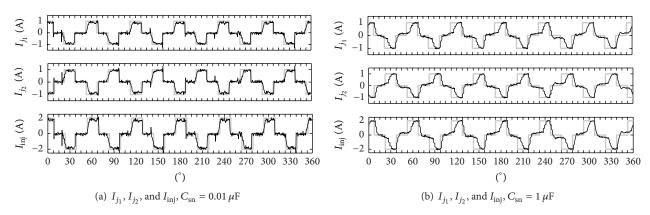

- 5.2. Reinjection Currents Waveforms. Figure 25 shows the reinjection currents  $I_{i_1}$ ,  $I_{i_2}$ , and  $I_{\rm inj}$  on the primary side of the

Figure 20: Generation of reinjection pulse for reinjection IGBT  $S_{p_0}/S_{p_0}$ .

FIGURE 21: ACPL-312T IGBT driver circuit.

reinjection transformer.  $I_{\rm inj}$  is composed of  $I_{j_1}$  and  $I_{j_2}$ . Again, with  $C_{\rm sn}=1~\mu{\rm F}$  reinjection current  $I_{\rm inj}$  is not following the theoretical  $I_{\rm inj}$  "perfectly" whereas, with  $C_{\rm sn}=0.01~\mu{\rm F},~I_{\rm inj}$  follows the theoretical wave-shape.

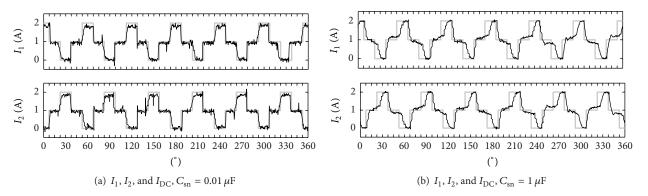

5.3. DC Bus Currents Waveforms. The injected current waveform  $I_{\rm inj}$  modifies the DC bus currents as shown in Figure 26. This DC bus current is a 3-level waveform with  $I_{1,2}=0$ ,

$I_{1,2}=I_{\rm DC}$ , and  $I_{1,2}=2I_{\rm DC}$  as the three different levels of DC bus current waveform.

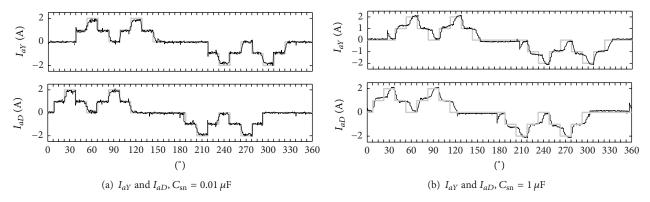

5.4. AC Side Secondary Line Current Waveforms. The modified AC side secondary line currents  $I_{aY}$  and  $I_{aD}$  are shown in Figure 27. With  $C_{\rm sn}=0.01~\mu{\rm F}$ , experimental  $I_{aY}$  and  $I_{aD}$  follow the theoretical current wave-shape. Current spikes are observed in  $I_{aY}$  and  $I_{aD}$  with  $C_{\rm sn}=1~\mu{\rm F}$ . These spikes are

FIGURE 22: Three-level MLCR CSC prototype and associated auxiliaries: the DC side reinjection transformer.

(a) Three-level reinjection PCB,  $C_{\rm sn}$ : 0.01  $\mu{\rm F}$

(b) Three-level reinjection PCB,  $C_{\rm sn}$ :

FIGURE 23: Two reinjection PCBs used in the prototype.

Figure 24: Experimental currents  $I_{S_{p_1}}$ ,  $I_{S_{p_0}}$ , and  $I_{S_{p_2}}$  through reinjection IGBTs.

observed at the same instants when the main bridge thyristors are triggered. However, these spikes are not observed with  $C_{\rm sn}=0.01\,\mu{\rm F}$ .

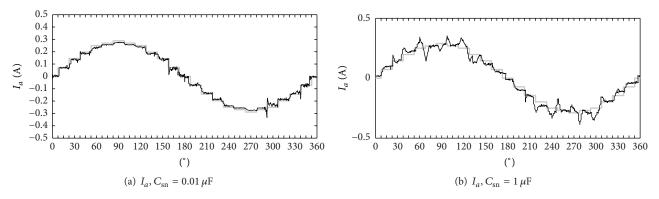

5.5. AC Side Primary Line Current Waveform. The modified primary side line current  $I_a$  is shown in Figure 28. The effect of using a "very large"  $C_{\rm sn}$  is clearly observed (Figure 28(b)).  $I_a$  with  $C_{\rm sn}=1~\mu{\rm F}$  is highly distorted

although a multistep waveform can be observed. With  $C_{\rm sn}=0.01~\mu{\rm F},~I_a$  follows the theoretical waveform closely and a 24-step  $I_a$  is obtained.

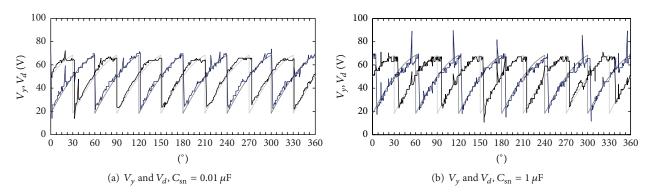

5.6. Y-Y and Y-D Connected DC Voltage Waveform. The DC voltage waveforms for both Y-Y and Y-D connected 6-pulse bridges are shown in Figure 29. With  $C_{\rm sn}=0.01\,\mu{\rm F}$ , the experimental waveform follows the theoretical one while,

FIGURE 25: Reinjected current waveforms  $I_{i_1}$ ,  $I_{i_2}$ , and  $I_{inj}$ .

FIGURE 26: Experimental DC bus currents  $I_1$ ,  $I_2$ , and  $I_{DC}$ .

FIGURE 27: Secondary side line currents  $I_{aY}$  and  $I_{aD}$ .

with  $C_{\rm sn}=1\,\mu{\rm F}$ , the transitions are delayed by about 7.5° which is also observed in PSCAD/EMTDC simulation result. However, very large voltage dv/dt, as predicted by PSCAD/EMTDC, is absent.

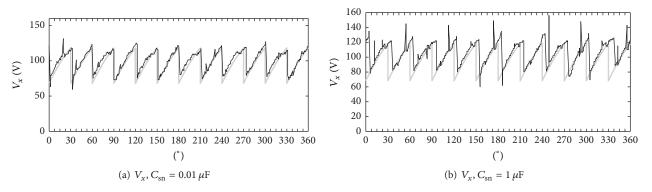

5.7. 12-Pulse DC Voltage Waveform. The 12-pulse DC voltage obtained for both the values of  $C_{\rm sn}$  is shown in Figure 30.

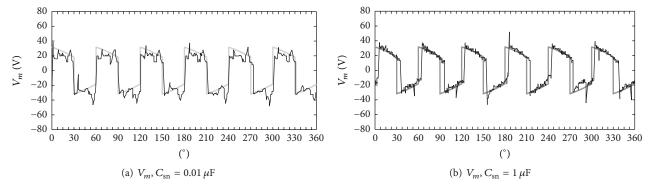

5.8. Reinjection Transformer Secondary Side Voltage Waveform. The reinjection transformer secondary side voltage  $V_m$  obtained is shown in Figure 31.  $V_m$  with  $C_{\rm sn}=1~\mu{\rm F}$  follows

the theoretical  $V_m$  more closely but is delayed by about 7.5°.  $V_m$  with  $C_{\rm sn}=0.01\,\mu{\rm F}$  has higher dv/dt during transitions (Figure 31(a)).

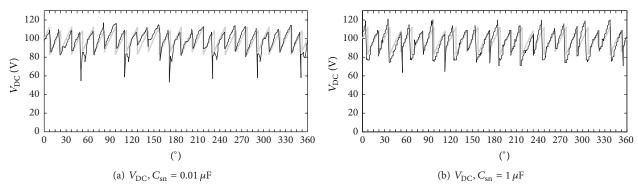

5.9. Three-Level MLCR CSC DC Voltage Waveform. The DC voltage waveform  $V_{\rm DC}$  is shown in Figure 32. Voltage dv/dt observed in  $V_m$  with  $C_{\rm sn}=0.01~\mu{\rm F}$  is clearly reflected across  $V_{\rm DC}$  whereas the voltage dv/dt transitions are not observed in  $V_{\rm DC}$  with  $C_{\rm sn}=1~\mu{\rm F}$ . Nevertheless,  $V_{\rm DC}$  has 24 pulses in both the cases which implies that ripple voltage is getting added to  $V_x$  giving it 24-pulse characteristics.

Figure 28: Primary side line current  $I_a$ .

Figure 29: DC voltage waveforms  $V_y$  and  $V_d$ .

Figure 30: 12-pulse DC voltage waveform  $V_x$ .

FIGURE 31: Reinjection transformer secondary side voltage  $V_m$ .

FIGURE 32: Three-level MLCR CSC DC voltage waveform  $V_{\rm DC}$ .

#### 6. Conclusion

The theory, PSCAD/EMTDC simulation results, hardware prototype, and experimental results of a 3-level thyristor based MLCR CSC have been presented in detail in this paper. The reinjection current forces the main bridge thyristor to commutate under zero current thereby allowing it to be switched at negative firing angles. It is possible to achieve self-commutation for thyristors using an auxiliary reinjection bridge.

From experimental investigation, it is observed that the deviation of the actual waveforms from the theoretical waveforms is mainly due to the use of a "very large" snubber capacitor. With a "very large" snubber capacitor value, interface transformer secondary side current showed current di/dt which happened exactly 7.5° before the current passed through that particular thyristor. This is when the thyristor is switched on. The voltage transitions were also delayed by 7.5° with a "very large" snubber capacitor. With a "small" snubber capacitor value, current waveform follows the theoretical waveforms very closely; however voltage dv/dt can be observed in the output DC voltage waveform.

The use of "small" snubber capacitor value is recommended to reduce line current distortion, as the modification of DC bus current is the key to achieve both self-commutation for thyristors and lower harmonic distortion.

## **Appendix**

## **Experimental/Simulation Parameters**

Source specification is as follows:

- (i) Voltage rating: 415 V @ 50 Hz.

- (ii) Source impedance:  $0.1 \Omega + 5 \text{ mH}$ .

Interface transformer is as follows:

- (i) Type: 3-phase, 3-winding @ 50 Hz.

- (ii) Power rating: 2 kVA.

- (iii) Voltage rating: 415 V: 50 V (1:1 for Y-Y and 1:  $\sqrt{3}$  for Y-D).

Reinjection transformer is as follows:

- (i) Type: 1 phase and 2 windings @ 300 Hz.

- (ii) Nominal impedance: 5%.

- (iii) Power rating: 1 kVA.

- (iv) Voltage rating: 400 V: 400 V.

Load specification is as follows:

- (i) Load resistance:  $100 \Omega$ .

- (ii) Load inductance: 400 mH.

Firing angle ( $\alpha$ ) =  $-45^{\circ}$ .

## **Competing Interests**

The authors declare that they have no competing interests.

## References

- [1] B. Singh, S. Gairola, B. N. Singh, A. Chandra, and K. Al-Haddad, "Multipulse AC–DC converters for improving power quality: a review," *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 260–281, 2008.

- [2] G. N. Bathurst, B. C. Smith, N. R. Watson, and J. Arrillaga, "Harmonic domain modelling of high-pulse converters," *IEE Proceedings: Electric Power Applications*, vol. 146, no. 3, pp. 335–340, 1999.

- [3] M. Abdel-Salam, S. Abdel-Sattar, A. S. Abdallah, and H. Ali, "Symmetrical component analysis of multi-pulse converter systems," *Electric Power Components and Systems*, vol. 34, no. 8, pp. 867–888, 2006.

- [4] M. Peterson and B. N. Singh, "Multipulse controlled ac-dc converters for harmonic mitigation and reactive power management," *IET Power Electronics*, vol. 2, no. 4, pp. 443–455, 2009.

- [5] C.-M. Young, S.-F. Wu, W.-S. Yeh, and C.-W. Yeh, "A DC-side current injection method for improving AC line condition applied in the 18-pulse converter system," *IEEE Transactions on Power Electronics*, vol. 29, no. 1, pp. 99–109, 2014.

- [6] A. Valderrabano and J. M. Ramirez, "A novel voltage source converter behind the StatCom," *Electric Power Components and Systems*, vol. 38, no. 10, pp. 1161–1174, 2010.

[7] C. I. Odeh, D. B. Nnadi, and E. S. Obe, "Three-phase, five-level multi-level inverter topology," *Electric Power Components and Systems*, vol. 40, no. 13, pp. 1522–1532, 2012.

- [8] C. I. Odeh and D. B. N. Nnadi, "Single-phase, 17-level hybridized cascaded multi-level inverter," *Electric Power Components and Systems*, vol. 41, no. 2, pp. 182–196, 2013.

- [9] A. Lesnicar and R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," in *Proceedings of the IEEE Power Tech Conference (POWERTECH '03)*, vol. 3, pp. 1–6, Bologona, Italy, June 2003.

- [10] J. I. Guzman, P. E. Melín, J. R. Espinoza et al., "Digital implementation of selective harmonic elimination techniques in modular current source rectifiers," *IEEE Transactions on Industrial Informatics*, vol. 9, no. 2, pp. 1167–1177, 2013.

- [11] J. Wu, Z.-X. Wang, G.-Q. Wang, S. Li, and D.-G. Wu, "Research on direct power control of modular multi-level converter for power transmission," *Electric Power Components and Systems*, vol. 40, no. 15, pp. 1731–1749, 2012.

- [12] S. Li, Z. Wang, and G. Wang, "Proportional-integral-differential neural network based sliding-mode controller for modular multi-level high-voltage DC converter of offshore wind power," *Electric Power Components and Systems*, vol. 41, no. 4, pp. 427– 446, 2013.

- [13] S. M. Muyeen, R. Takahashi, and J. Tamura, "Operation and control of HVDC-connected offshore wind farm," *IEEE Transactions on Sustainable Energy*, vol. 1, no. 1, pp. 30–37, 2010.

- [14] Y. H. Liu, Multi-level voltage and current reinjection AC-DC conversion [Ph.D. thesis], Electrical and Computer Engineering Department, University of Canterbury, Christchurch, New Zealand, 2003.

- [15] J. F. Baird and J. Arrilaga, "Harmonic reduction in DC-ripple reinjection," *IEE Proceedings C*, vol. 127, no. 5, pp. 294–303, 1980.

- [16] J. Arrillaga, L. Yonghe, C. S. Crimp, and M. Villablanca, "Harmonic elimination by DC ripple reinjection in generatorconvertor units operating at variable speeds," *IEE Proceedings C: Generation Transmission and Distribution*, vol. 140, no. 1, pp. 57–64, 1993.

- [17] J. Arrilaga, Y. H. Liu, L. B. Perera, and N. R. Watson, "A current reinjection scheme that adds self-commutation and pulse multiplication to the thyristor converter," *IEEE Transactions on Power Delivery*, vol. 21, no. 3, pp. 1593–1599, 2006.

- [18] L. B. Perera, N. R. Watson, Y. H. Liu, and J. Arrillaga, "Multilevel current reinjection self-commutated HVDC converter," *IEE Proceedings—Generation, Transmission and Distribution*, vol. 152, no. 5, pp. 607–615, 2005.

- [19] W. McMurray, "Selection of snubbers and clamps to optimize the design of transistor switching converters," *IEEE Transactions on Industry Applications*, vol. IA-16, no. 4, pp. 513–523, 1980.

- [20] LEM, Voltage Transducer, LV25-P datasheet, no. 060315/4, 2012, http://www.lem.com.

- [21] Murata Power Solutions, 772 Series Pulse transformers, datasheet, 2011, http://www.murata-ps.com/.

- [22] NXP Semiconductors, BT152 Series Thyristors, Datasheet, 1997, http://www.nxp.com.

- [23] Avago Technologies, "Automotive IGBT gate drive optocoupler with R<sup>2</sup> coupler isolation and 2.5 Amp output current," ACPL-312T Datasheet, 2011.

- [24] IXYS Semiconductors, IGBT IXGP20N120, datasheet, 2002, http://www.avagotech.com/.

- [25] XP Power, 2 Watts IL Series, IL0515S datasheet, 2012, http:// www.xppower.com.

Submit your manuscripts at http://www.hindawi.com