# Experimental Investigation on the Transient Switching Behavior of SiC MOSFETs Using a Stage-Wise Gate Driver

Georges Engelmann, Tizian Senoner, and Rik W. De Doncker

Abstract—A multiple stage gate driver for SiC MOSFETs based on a switched resistor topology is introduced and a hardware realization is presented. The measurement setup is shown in detail to highlight the quality of the shown measurement results. The evaluation of the stage-wise driver is conducted by comparing the switch and diode peak voltages as well as peak currents with regard to the switching losses to a reference driver. The switching transients are generated using a double pulse test bench. A detailed investigation on two- and three-stage operation for both, the turnon and turn-off events are presented. A variation of gate resistors and different timings is conducted for each stage and evaluated using the resulting measurements. It is shown that the drain-source peak voltage is reduced by 45% while maintaining equal turn-off losses. Analogously, a reduction of 51% of the diode peak voltage and a reduction of 50% of the peak reverse recovery current at the same time is feasible for equal turn-on losses.

*Index Terms*—MOSFET switches, power electronics, semiconductor device measurements, switched resistor circuits, test equipment.

## I. INTRODUCTION

**P**OWER electronic converters are used in a wide field of applications and a growing tendency is seen. Their appearance is growing in low- and medium-voltage applications. They are the key technology for renewable energies or electric traction systems, especially electric vehicles [1]-[3].

Reductions in volume and weight are a crucial aspect to achieve lower costs of the converters. This leads to a higher integration level of the converters [4], [5]. A high integration level creates the need for good thermal power flow by using e.g., thermal interface materials [6]. Furthermore, this integration level of power electronic converters can be increased using the emerging high-temperature wide-bandgap (WBG) power semiconductors [7]-[9] as higher switching frequencies can be achieved, which in turn allows a reduction of the filter size. However, higher switching frequencies and steeper switching slopes are the source for higher electromagnetic interference (EMI) [10].

An extensive comparison of the switching performance between insulated-gate bipolar transistors (IGBTs) and sil-

TABLE I Specifications of the SIC MOSFET and Test Setup

| Description          | Specifier                | Value  |

|----------------------|--------------------------|--------|

| Blocking voltage     | $U_{\rm DSS}$            | 1200 V |

| Rated current        | I <sub>D</sub>           | 63 A   |

| DC-link voltage      | $U_{\rm dc}$             | 700 V  |

| Test current         | $I_{\rm D}$              | 60 A   |

| Junction temperature | $\vartheta_{\mathrm{j}}$ | 35 °C  |

icon carbide (SiC) metal-oxide semiconductor field-effect transistors (MOSFETs) is presented in [11], [12]. Considerable efforts have been made to affect the switching behavior of IGBTs, for example to influence the EMI, voltage stress or switching losses [13]-[16].

As the switching times of SiC MOSFETs are reduced by at least a decade compared to the switching times of IGBTs, the design of an active gate driver (AGD) is more challenging. Nevertheless, various approaches, which are widely known for silicon power semiconductors, are found in literature, such as protection circuitry [17], current controlled gate drivers [18], resonant gate drivers [19] or gate drivers for series connected MOSFETs [20] or medium-voltage SiC MOSFETs [21]. Some investigations tend to handle parasitic turn-on [22], [23] or influence the switching speed using passive components in the gate path [24]-[26]. Very high switching speeds for WBG power semiconductors are achieved using inductive feedback as shown in [27]. Similar to integrated current sense structures for IGBTs, integrated current sense structures of SiC MOSFETs are appearing for protection or current sensing applications [28].

A two-stage AGD using analog circuitry with high bandwidth is presented in [29]. A multi-level AGD influencing the gate voltage during the Miller plateau is shown in [30].

In this work, a multiple-stage AGD for a 1.2 kV SiC MOSFET *CPM2-1200-0040B* based on a switched resistor topology is presented. A similar approach as shown in [15], [30] is followed to influence the switching behavior. The influence on the switching behavior for two- and three-stage operation is shown for the turn-on as well as the turn-off event. The investigations are evaluated against a reference push-pull gate driver. The goal is to show that the voltage peaks and current peaks can be reduced individually without a penalty on switching losses. TABLE I lists the device pa-

Manuscript received January 7, 2018.

The authors are with the Institute for Power Electronics and Electrical Drives, RWTH Aachen University, Aachen, Germany (email: post@isea. rwth-aachen.de).

Digital Object Identifier 10.24295/CPSSTPEA.2018.00008

rameters and test conditions at which the investigations are carried out. The junction temperature  $\vartheta_j$  is given as 35 °C as all measurements are conducted at room temperature inside the test bench. Due to the fast switching slopes of the SiC devices, high bandwidth equipment has to be used and the correct employment of the latter is crucial for accurate measurement results [31]. Therefore, a dedicated section dealing with the measurement setup is included in this paper.

#### II. STAGE-WISE GATE DRIVER TOPOLOGY

The proposed stage-wise driver consists of a state-ofthe-art voltage source gate driver using a variable gate resistance  $R_{gate}$ . The influence on the switching behavior is accomplished by changing the value of the gate resistance during the switching action. The presented topology already led to good results using silicon IGBTs as shown in [15]. In comparison to a switching event using an IGBT, the fall and rise times of voltage and current of a SiC device are at least a decade faster. This means, that if the switching event of an IGBT lasts for 100 ns (e.g., see [15], Fig. 11), it will last for less than 10 ns when using a SiC device. The gate driver, which is presented in [15], has a minimum time resolution of 10 ns due to the limited clock speed of the field-programmable gate array (FPGA). A timing of less than 1 ns is required to be able to influence the switching behavior of SiC devices. The employed topology of the driver is shown in this section. The high resolution timing, which is required as input stage to the driver hardware, is introduced in section III

## A. Topology

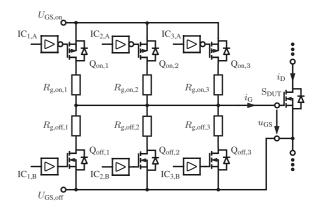

The schematic topology of the driver is shown in Fig. 1. It consists of three parallel branches, of which each constitutes of a push-pull stage configuration. Each branch consists of a turn-on and turn-off gate resistance  $R_{g,on,n}$ ,  $R_{g,off,n}$ , an n-channel and p-channel MOSFET  $Q_{on,n}$ ,  $Q_{off,n}$  as well as a dual lowside driver chip IC<sub>n</sub>. A comparison among several commercial gate driver integrated circuits (ICs) and n- and p-channel MOSFETs is conducted. The ICs with the fastest rise times (n-channel) or fall times (p-channel) using a dummy 10 nF capacitive load are selected. The selected devices are listed in TABLE II including the rise and fall times using the 10% ... 90% borders of the dummy and gate capacitor voltage. The gate-source capacitance  $C_{gs}$  of the selected power semiconductor is 2 nF [32]. Assuming a RC charging curve, the time constant is reduced by a factor of 5 for the given SiC MOSFET compared to the dummy capacitor, resulting in 1.9 ns. However, the rise and fall times are still significant compared to the envisaged time resolution and the expected duration of the switching events. As the aim of the stage-wise driver is to only partially charge (or discharge) the gate capacitance during each stage, only a fraction of the indicated rise/fall time is required and thus within an acceptable range for the presented driver. The gate driver is supplied using the supply voltages  $U_{GS,off} = 0$  V and  $U_{GS,on} = 18$  V.

Fig. 1. Topology of the proposed stage-wise driver.

TABLE II Selected Devices for the Driver Design

| Device                                                                                                     | Part nr.                                | rise/fall time                             |                                            |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------|

| $\operatorname{IC}_n \\ \operatorname{Q}_{\operatorname{on},n} \\ \operatorname{Q}_{\operatorname{off},n}$ | UCC27523<br>BSZ180P03NS3E<br>DMN3035LWN | 1.9 ns <sup>1</sup><br>1.9 ns <sup>1</sup> | 9.4 ns <sup>2</sup><br>9.4 ns <sup>2</sup> |

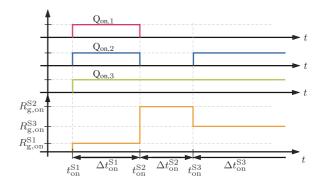

Fig. 2. Operation principle of the stage-wise driver.

#### B. Operation Principle

The operation principle of the stage-wise driver is shown using an exemplary sequence for a turn-on event plotted in Fig. 2. During a state *S*, one or more MOSFETs  $Q_{on,x}$  are turned on resulting in an effective gate resistance  $R_{g,on}^{s}$ . In the plotted exemplary waveforms, the switches  $Q_{on,1}$ ,  $Q_{on,2}$  and  $Q_{on,3}$  are turned on at the same time during stage one. The effective first stage gate resistor results in

$$R_{\mathrm{g,on}}^{\mathrm{S1}} = R_{\mathrm{g,on,1}} \parallel R_{\mathrm{g,on,2}} \parallel R_{\mathrm{g,on,3}}$$

The first stage lasts for a time  $\Delta t_{on}^{S1}$ . Analogously, the gate resistance for the second stage is set to  $R_{g,on}^{S2} = R_{g,on,3}$  for a duration  $\Delta t_{on}^{S2}$ . The third stage is, in this example, the last stage and thus lasts until the device under test (DUT) is switched off. This is indicated by setting the third stage tim-

<sup>&</sup>lt;sup>1</sup> The indicated time is normalized to the gate capacitance  $C_{gs} = 2$  nF.

<sup>&</sup>lt;sup>2</sup> This is the measured rise/fall time using a 10 nF capacitance.

(a) Stage-wise driver.

(b) Reference driver.

Fig. 3. Reference driver circuit.

ing to infinite  $\Delta t_{\rm on}^{\rm S3} = \infty$ .

#### C. Gate Driving Strategy

The goal of manipulating the switching waveforms is to achieve lowest switching losses while reducing the device stress at the same time. A similar approach as used in [15], [30] is employed.

This goal is achieved with an initial fast (dis)charging of the gate. Therefore, the smallest possible gate resistance is chosen for the first stage. However, a small gate resistance results in a high  $u_{DS}$  overshoot (turn-off event) or a high  $i_s$ ,  $u_{Diode}$  overshoot (turn-on event), which are reduced by slowing down the (dis)charging process during the second stage using an increased gate resistance. A third stage, using a small gate resistance, is appended because the second stage resistance would result in very high switching losses for the remaining switching process.

However, besides the qualitative approach, no quantitative approach regarding timing and resistor values is known prior to the investigations. Therefore, a large variation of the different timings and resistor values are conducted to allow the deduction of an optimum driving strategy.

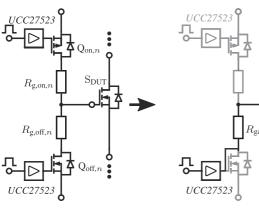

## D. Reference Design

To allow an evaluation of the stage-wise gate driver, a classical single stage reference driver is needed. To avoid any unnecessary influence of, for example, the layout, on the switching behavior, the stage-wise driver is slightly modified, as shown in Fig. 3. One channel of the dual low side gate driver UCC27523 is reconfigured to directly drive the gate resistance  $R_{\text{eate}}$ .

#### III. HARDWARE REALIZATION

Parasitic inductances or capacitances have a high impact on the switching behavior [33]. Especially, when switching using high voltage or current slopes, the influence of these parasitic elements rises. Thus, a good layout of the switching

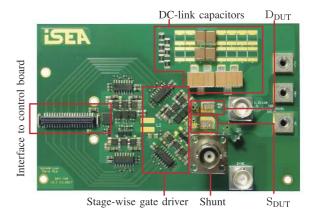

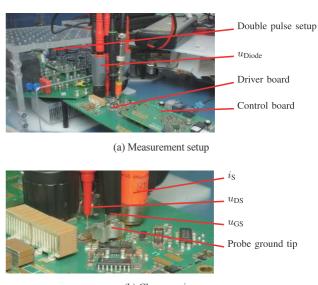

Fig. 4. Photograph of the PCB containing the driver and SiC bare dies.

TABLE III Valuse of the Different Stary Inductances

| Inductance                | Value  | Inductance                | Value  |

|---------------------------|--------|---------------------------|--------|

| $L_{\sigma,\mathrm{DC}}$  | 3.8 nH | $L_{\sigma,Switch}$       | 2.0 nH |

| $L_{\sigma,\text{Diode}}$ | 1.7 nH | $L_{\sigma,\text{Shunt}}$ | 6.8 nH |

cell and driver is crucial to achieve the desired results.

Apart from the switching cell and driver board, the control board is introduced. The control board generates the different gate signals for the different branches.

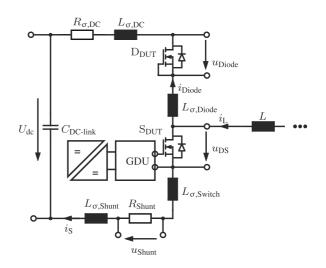

#### A. Switching Cell and Driver Board

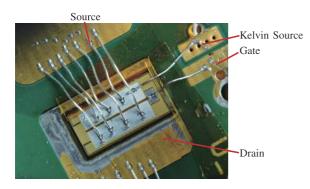

The printed circuit board (PCB) containing the switching cell and gate driver is pictured in Fig. 4. The control signals for the driver chips are transmitted using low-voltage differential signaling (LVDS) from the FPGA on the control board. A LVDS to single ended converter (SN65LVDS048AD) controls the dual low side driver ICs. The high-side gate is short circuited on the PCB (as seen in Fig. 4) as only the low-side MOSFET S<sub>DUT</sub> is switched in the double pulse test. A close-up view on the low-side MOSFET is seen in Fig. 5. The Bayonet Neill-Concelman (BNC) plugs allow a repeatable measurement of the high-side diode voltage  $u_{\text{Diode}}$  and lowside drainsource voltage  $u_{\rm DS}$ . The source current is measured using a T&M SDN-414-10 current viewing resistor (CVR). The different stray inductances of the switching cell are determined using a current pulse generator [34] and methodology as described in [33]. The resulting values, corresponding to the schematic shown in Fig. 8, are listed in TABLE III. It is noticed, that the CVR is responsible for 47.5% of the total stray inductance.

#### B. Control Board

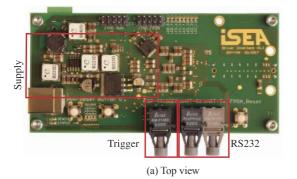

A photograph of the front and back side of the control board is shown in Fig. 6(a) and Fig. 6(b). The board hosts an *AT32UC3A1512* microcontroller (MCU) and a Xilinx Spartan 6 *XC6SLX9* FPGA. The MCU connects to a personal

Fig. 5. Close-up view on the low-side SiC bare die.

Fig. 6. Photograph of the control board.

computer (PC) via *RS232* to allow on the fly configuration of the FPGA. A serial peripheral interface (SPI) bus ensures communication between the FPGA and MCU.

The main function of the FPGA is the generation of the different gate signals for each branch. A precise time resolution of less than 1 ns is required for an appropriate control of the SiC power semiconductors. The maximum clock speed of the employed FPGA of 300 MHz does not allow a higher time resolution than 3.33 ns. To achieve higher time resolutions, the delay-locked loop (DLL) functionality of the digital clock manager (DCM) of the FPGA is used. A very precise timing is achieved using the phase shift  $\phi$ , as shown in Fig. 7. In total, four DCM blocks are available in the FPGA. Using a clock frequency of 50 MHz, the DLL allows a precise timing control of the edge of a signal of up to 23 ps.

#### IV. MEASUPEMENT SETUP

Measuring the voltage and current waveforms of SiC de-

Fig. 7. Delay-locked loop operation principle.

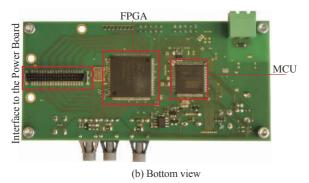

Fig. 8. Schematic of the switching cell used for the double pulse tests.

vices properly is not a trivial task [31]. As the measurement setup influences the resulting measurements to a large extend [35], a detailed description of the employed setup is shown prior to the main investigations on the gate driver.

The evaluation of the driver is made by comparing the resulting transient switching waveforms of the low-side semiconductor to the measurement results achieved using a push-pull reference driver. A double pulse test bench [36] is employed to conduct automated series measurements using different DC-link voltages, currents and temperatures [37].

The waveforms are recorded using a Teledyne LeCroy *HDO6104* oscilloscope using a vertical resolution of 12 bit, 1 GHz bandwidth and a 2.5 <sup>GS</sup>/<sub>s</sub> sample rate. A schematic of the electrical circuit of the switching cell is shown in Fig. 8. Two 900 V, 1.25  $\mu$ F CeraLink capacitors are used in parallel with four ceramic capacitances to form the DC-link capacitor  $C_{\text{DC-link}}$ . The voltage measurements  $u_{\text{DS}}$ ,  $u_{\text{Diode}}$  and  $u_{\text{GS}}$  are made between the drain tab and kelvin source contacts. The low-side switch current  $i_{\text{S}}$  is measured using the indicated CVR.

The high-side diode current  $i_{\text{Diode}}$  is calculated using the low-side current  $i_s$  and inductor current  $i_L$  using (1). As the inductor current is not measured during the double pulse test, it is retrieved using a linear interpolation of the switch current  $i_s$  prior to turning the switch off at the time where it is still fully on ( $t = t_{\text{turn-off}}$ ) and shortly after it is switched back on ( $t = t_{\text{turn-on},+}$ ) as indicated in (2) and (3).

$$i_{\text{Diode}} = i_{\text{L}} - i_{\text{S}} \tag{1}$$

$$i_{\rm L} \left( t = t_{\rm turn-off} \right) = i_{\rm S} \left( t = t_{\rm turn-off,-} \right) \tag{2}$$

G. ENGELMANN et al.: EXPERIMENTAL INVESTIGATION ON THE TRANSIENT SWITCHING BEHAVIOR OF SIC MOSFETS

$$i_{\rm L} \left( t = t_{\rm turn-on} \right) = i_{\rm S} \left( t = t_{\rm turn-on,+} \right) \tag{3}$$

A certain inaccuracy in the given current measurement method is taken into account. First, the measured source current  $i_{\rm S}$  does not exactly represent the MOSFET channel current due to the parasitic output capacitance  $C_{oss}$ . However, literature shows that the influence of the output capacitance  $C_{\rm oss}$  cancel each other when considering the sum of the turnon and turn-off losses [38]. Besides calorimetric switching loss measurements, no accurate MOSFET channel current measurement technique, which is independent of the output capacitance  $C_{oss}$ , is known. For precisely this reason, the later on conducted measurements are compared to reference measurements which are recorded under exactly the same conditions. Second, the high-side diode current  $i_{\text{Diode}}$  is, besides the output capacitance  $C_{oss}$  of the high-side switch, additionally distorted by parasitic capacitances across the load inductance, or generally between the AC terminal and ground. The latter could be improved by using a CVR in the high-side path in combination with isolated low voltage measurement equipment.

As the CVR connects the oscilloscope ground to the source potential of the low-side switch, the utilization of a further passive probe is not envisaged as the grounding terminal of the probe would create a ground loop via the oscilloscope to the CVR. This would facilitate circulating currents through the shielding of the coaxial cables and herewith disturb the measurements [35]. However, as an extensive study between various active differential and passive probes for small and large signal measurements got conducted prior to this work, the passive probe *PP018-2* largely outperforms the remaining probes for gate voltage measurements.

Thus, the following compromise is made: Exactly the same double pulse measurement is conducted twice after each other, first with only the passive probe connected to gate followed by a measurement with only the coaxial cable of the CVR connected. The gate voltage is measured additionally using the active probe for both measurements, which is used to synchronize and merge both measurements. The use of the active probe signal to merge the merging procedure is considered as valid, as the repeatability of the measured signal is very good. Using this procedure, it is guaranteed that no unnecessary distortion occurs due to circulating currents in the coaxial shielding. The only drawback, which is disregarded, is the influence of an eventual jitter of the various ICs used for the AGD. The employed measurement probes are summarized in TABLE IV. A photograph of the setup is pictured in Fig. 9.

As the switching times of the SiC MOSFETs, which are within 10 ns ... 20 ns, are in the same range as the probedelays, a delay compensation is required. As no appropriate information is available in the provided data sheets, the individual propagation delays of the probes are measured using a Tektronix *Type 109* pulse generator and a high-voltage probe calibrator *KHT 1000*. The resulting values are indicated in TABLE IV. The propagation delay of the CVR is due to the coaxial cable (*Radiall R284C0351005*) with a length of 1 m

TABLE IV Measurement Equipment

| Manufacturer    | Part Nr.   | Measured signal            | Probe<br>delay | Bandwidth |

|-----------------|------------|----------------------------|----------------|-----------|

| PMK             | BumbleBee  | $u_{ m DS},  u_{ m Diode}$ | 12.3 ns        | 300 MHz   |

| Testec          | TT-SI 9101 | $u_{ m GS}$                | 11.7 ns        | 100 MHz   |

| Teledyne LeCroy | PP018-2    | $u_{ m GS}$                | 6.3 ns         | 500 MHz   |

| T&M Research    | SDN-414-10 | $i_{ m S}$                 | 5.4 ns         | 2000 MHz  |

(b) Close up view

Fig. 9. Photograph of the measurement setup.

and external 50  $\Omega$  terminator.

#### V. REFERENCE MEASUREMENTS

The measurements using the reference driver are introduced and presented in this section. As the stage-wise gate driver makes use of various gate resistances during a single switching event, the results cannot be simply compared to a reference measurement using a specific gate resistance. Thus, the reference measurements are made using various gate resistances in the range  $R_{gate} = 0.5 \Omega \dots 10 \Omega$ .

#### A. Measurements of the Turn-On Event

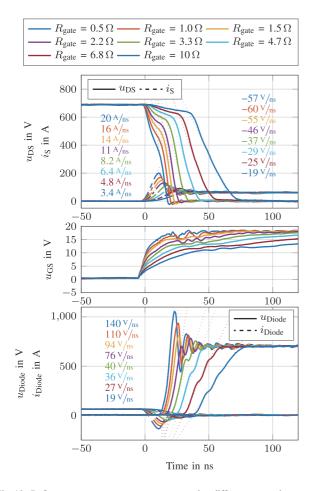

The turn-on measurements cover the turn-on event of the low-side switch as well as the turn-off event of the high-side diode. The measured waveforms using the different gate resistors are shown in Fig. 10. The respective voltage and current slopes are indicated for the current waveforms as well as for the switch and diode drain-source voltage  $u_{\text{DS}}$ ,  $u_{\text{Diode}}$ . The voltage and current fall and rise slopes are indicated in the respective figures. The slopes are calculated using the 10% ... 90% borders of the waveforms, excluding the inductive voltage drop during the turn-on event (see Fig. 10). Depending on the gate resistance  $R_{\text{gate}}$ , current slopes ranging from  $3.4 \, \text{^A}_{\text{ns}} \dots 20 \, \text{^A}_{\text{ns}}$  are reached. The slope of the low-side drain-source voltage  $\frac{du_{\text{DS}}}{dt}$  reaches values from  $-19 \, \text{^V}_{\text{ns}} \dots -57 \, \text{^A}_{\text{ns}}$

Fig. 10. Reference turn-on event measurements using different gate resistors.

whereas the voltage slope of the diode reach higher values ranging from  $19^{\text{A}}/_{\text{ns}} \dots 140^{\text{A}}/_{\text{ns}}$ .

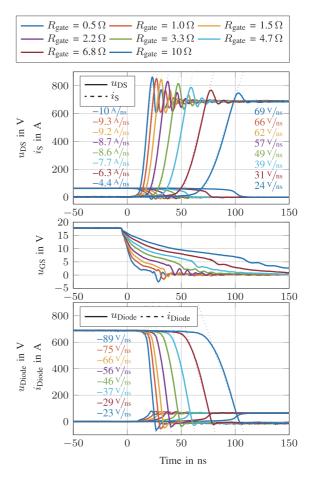

## B. Measurements of the Turn-Off Event

Analogously, the reference measurements of the turn-off event are shown in Fig. 11 together with their corresponding slopes. The current slopes reach from  $-4.4 \,{}^{\text{A}}/_{\text{ns}} \dots -10 \,{}^{\text{A}}/_{\text{ns}}$ . The slope of the diode voltage  $u_{\text{Diode}}$  ranges from  $22 \,{}^{\text{V}}/_{\text{ns}} \dots 82 \,{}^{\text{V}}/_{\text{ns}}$  whereas the switch voltage slope  $\frac{\mathrm{d}u_{\text{DS}}}{\mathrm{d}t}$  ranges from  $-23 \,{}^{\text{V}}/_{\text{ns}}$ .

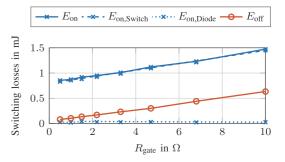

#### C. Switching Losses

The switching losses of the various switching transitions are calculated using

$$E_{\rm sw} = \int_{t_{\rm start}}^{t_{\rm end}} p_{\rm sw} \mathrm{d}t = \int_{t_{\rm start}}^{t_{\rm end}} \left( u_{\rm DS} \cdot i_{\rm S} \right) \mathrm{d}t.$$

The start and end times  $t_{\text{start}}$  and  $t_{\text{end}}$  are chosen using the 3% borders of the peak power. A more detailed description of the switching loss extraction algorithm is given in [15]. The resulting switching losses using the reference driver with various gate resistances are shown in Fig. 12.

Fig. 11. Reference turn-off event measurements using different gate resistors.

Fig. 12. Calculated switching losses using the reference driver with various gate resistances at  $U_{dc} = 700$  V,  $I_D = 60$  A.

# VI. STAGE-WISE DRIVER TURN-ON OPERATION

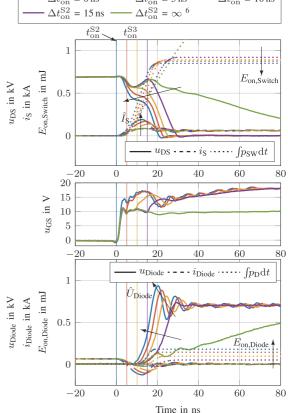

The influence of the stage-wise gate driver on the turn-on event is investigated in this section. At first, a simple change of resistor, from a small value to a larger value, is shown. The aim of slowing down the gate charging is to reduce the diode peak voltage  $\hat{U}_{\text{Diode}}$  and the switch peak current  $\hat{I}_{s}$ . Afterwards, a third stage is introduced, which further improves the switching behavior.

#### A. Investigations on the Two-Stage Turn-On Event

The two-stage turn-on event is investigated using the setup

| Stage S                                                                                       | $R_{ m g,on}^{S}$                                                                                                                                                                                                  | $\Delta t_{ m on}^{S}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2                                                                                        | $\begin{array}{c} 0.5\Omega\\ 2.2\Omega\ldots10\Omega\end{array}$                                                                                                                                                  | $0 \text{ ns } \dots 1.2 \text{ ns, } \infty$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $ \Delta t_{\rm or}^{\rm S}$ $ \Delta t_{\rm or}^{\rm S}$                                     | $\int_{1}^{1} = 0 \text{ ns }^{3} \longrightarrow \Delta t_{\text{on}}^{\text{S1}} = 0.8 \text{ ns}$ $\int_{1}^{1} = 1 \text{ ns } \longrightarrow \Delta t_{\text{on}}^{\text{S1}} = 1.2 \text{ ns}$              | $ \Delta t_{\rm on}^{\rm S1} = 0.86  \rm ns $ $ \Delta t_{\rm on}^{\rm S1} = \infty^{-4} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| u <sub>DS</sub> in kV<br>i <sub>S</sub> in kA<br>E <sub>on.Switch</sub> in                    | $\begin{array}{c} t_{on}^{S2} \\ 1.2 \\ 1 \\ 0.8 \\ 0.6 \\ 0.4 \\ 0.2 \\ 0 \\ 0.2 \\ -20 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\$                                                                          | $f_{p_{SW}dt}$ $E_{on,Switch}$ $E_{00,Switch}$ |

| $u_{\text{Diode}}$ in $k'$<br>$i_{\text{Diode}}$ in $k_I$<br>$E_{\text{on,Diode}}$ in $b_{1}$ | $\begin{array}{c} 25\\ 20\\ 15\\ 10\\ 5\\ 0\\ -20\\ 0\\ 2\\ 0\\ 0.2\\ -20\\ 0\\ 0\\ 2\\ -20\\ 0\\ 0\\ 2\\ -20\\ 0\\ 0\\ 2\\ 0\\ 0\\ 0\\ 2\\ -20\\ 0\\ 0\\ 2\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\ 0\\$ | ĴDiode<br>Eon,Diode<br>40 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

TABLE V TWO-STAGE DRIVER SETUP FOR THE TURN-ON EVENT

TABLE VI THREE-STAGE DRIVER SETUP OF THE TURN-ON EVENT

| 1 | R <sup>S</sup> <sub>g,on</sub> | 0.86 ns   |  |

|---|--------------------------------|-----------|--|

| 2 | 50 Ω                           | 0 ns 15 r |  |

| 3 | 2.2 Ω                          | $\infty$  |  |

Fig. 13. Two-stage turn-on event waveforms using  $R_{\rm g,on}^{\rm S2}$  = 10  $\Omega$ .

as listed in TABLE V. The resulting transient waveforms using a second stage gate resistance  $R_{\rm g,on}^{\rm S2} = 10 \ \Omega$  are plotted in Fig. 13 including two reference waveforms ( $\Delta t_{on}^{S1} = 0$  ns,  $\Delta t_{on}^{S1} =$  $\infty$ ) for comparison. It is seen, that it is possible to manipulate the waveforms between the two reference measurements. It is shown in Fig. 13, that the diode peak voltage  $\hat{U}_{\text{Diode}}$  is reduced down to the DC-link voltage  $U_{\rm dc},$  thus eliminating the overshoot. As it is seen from Fig. 13, that although the turn-on losses are increasing as expected with a shorter duration of the first stage, the losses in the diode are decreasing. As the total turn-on losses include the losses in the diode as well as the switch, an optimum operation point for the turn-on event using a two-stage gate driver has to be found.

#### B. Investigations on the Three-Stage Turn-On Event

To improve the two-stage switching behavior, a third stage

Fig. 14. Three-stage turn-on event waveforms.

using a small gate resistance comparing to the second stage gate resistance  $R_{g,on}^{S3} < R_{g,on}^{S2}$  is appended. The driver setup listed in TABLE VI is applied. A good initial setup is chosen for the first and second stage. The resulting waveforms are plotted in Fig. 14.

It is observed that, by introducing a third stage with a small gate resistance, the losses in the switch decrease comparing to the two-stage operation  $(\Delta t_{on}^{S2} = \infty)$ . However, the diode losses as well as the device stress  $(\hat{I}_{s}, \hat{U}_{Diode})$  increase at the same time. The evaluation of the performance of the three-stage operation is shown in the following section.

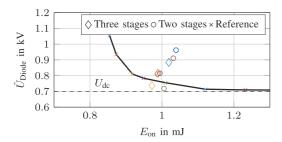

### C. Evaluation of the Stage-Wise Turn-On Operation

The preceding sections showed the ability of the AGD to influence the stress and the switching losses of the power semiconductor. It becomes clear from Fig. 13, that during the

- <sup>5</sup> Equivalents a two-stage turn-on event:  $R_{g,on}^{S1} = 0.5 \Omega$  to  $R_{g,on}^{S2} = 2.2 \Omega$ . <sup>6</sup> Equivalents a two-stage turn-on event:  $R_{g,on}^{S1} = 0.5 \Omega$  to  $R_{g,on}^{S2} = 50 \Omega$ .

<sup>&</sup>lt;sup>3</sup> Equivalents a single-stage turn-on event using  $R_{\text{gate}} = 10 \Omega$ .

<sup>&</sup>lt;sup>4</sup> Equivalents a single-stage turn-on event using  $R_{gate} = 0.5 \Omega$ .

(a) High-side diode overshoot voltage vs. turn-on energy

(b) Reverse recovery peak current vs. turn-on energy

Fig. 15. Device stress vs. turn-on energy.

TABLE VII

Two-Stage Driver Setup of the Turn-Off Event

| Stage $S$ | $R^{S}_{ m g,off}$      | $\Delta t_{ m off}^{S}$ |

|-----------|-------------------------|-------------------------|

| 1         | 0.5 Ω                   | 12 ns 16 ns             |

| 2         | 4.7 Ω, 12 Ω, 15 Ω, 18 Ω | $\infty$                |

first stage, a high precision in the timing is required as very little influence (<1 ns) has a high impact on the remaining switching transient of the power semiconductor.

A quantitative comparison of the stress and the switching energy for the turn-on event is plotted in Fig. 15, containing both, the reference as well as the two- and three-stage measurements. It is seen, that using the two-stage operation, the device stress can be influenced over a wide range, however with additional costs in turn-on losses. A good two-stage parameter selection as a basis for the three-stage operation allows a reduction of the stress and of the losses at the same time, compared to the reference driver. A reduction of the diode peak voltage  $\hat{U}_{\text{Diode}}$  by 51% as well as a reduction of the reverse recovery peak current  $\hat{I}_{\text{S}}$  by 50% is reached for equal turn-on losses  $E_{\text{on}}$ .

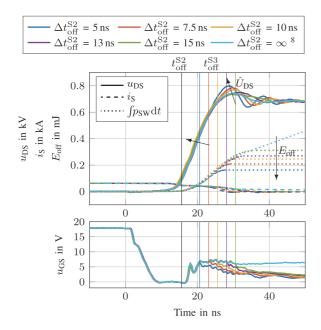

# VII. STAGE-WISE DRIVER TUREN-OFF OPERATION

Analogously to the turn-on event investigations, the influence of the different stages on the turn-off event is investigated. The impact of the two-stage operation on the switching transients is shown first, followed by an investigation of a third stage.

### A. Investigations on the Two-Stage Turn-Off Event

The two-stage analysis is carried out using the driver setup

Fig. 16. Two-stage turn-off event waveforms using  $R_{g,off}^{S2} = 15 \Omega$ .

TABLE VIII Three-Stage Driver Setup of the Turn-Off Event

| Stage $S$ | $R^{S}_{ m g,off}$ | $\Delta t_{ m off}^S$ |

|-----------|--------------------|-----------------------|

| 1         | 0.5 Ω              | 15.6 ns               |

| 2         | 100 Ω              | 5 ns 15 ns            |

| 3         | 4.7 Ω              | $\infty$              |

as shown in TABLE VII. The gate is discharged using a high current in the beginning and is slowed down after a certain time  $\Delta t_{\text{off}}^{S1}$  with switching to a higher gate resistance  $R_{\text{g.off}}^{S2}$ .

The resulting waveforms are plotted in Fig. 16. The twostage operation allows a reduction of the drainsource voltage peak  $\hat{U}_{\rm DS}$ , however with increased turn-off losses.

### B. Investigations on the Three-Stage Turn-Off Event

The influence of a third stage is shown using the setup listed in TABLE VIII. The time  $\Delta t_{\text{off}}^{\text{S2}}$  is increased using a 2.5 ns step size. Fig. 17 shows the resulting waveforms. A slight increase of the peak voltage  $\hat{U}_{\text{DS}}$  together with a reduction of the turn-off losses is observed. The rate of change of both quantities compared to the two-stage operation decides whether an overall improvement is achieved. It is noticed, that a noticeable effect on the waveforms is seen only a certain time after the gate resistance got changed.

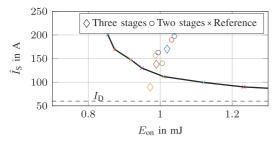

### C. Evaluation of the Stage-Wise Turn-Off Operation

It is shown, that an influence on the switching transients is as well possible during the turn-off event. However, certain delays in the reaction of the transient behavior are seen, as for example in the gate voltage waveform plotted in Fig. 16.

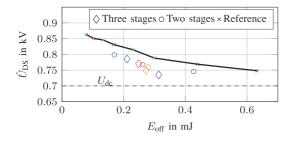

The resulting device stress ( $\hat{U}_{\mathrm{DS}}$ ), extracted from the two

<sup>7</sup> Equivalents a single-stage turn-off event using  $R_{\text{gate}} = 0.5 \Omega$ .

Fig. 17. Three-stage turn-off event waveforms.

Fig. 18. Low-side switch voltage overshoot vs. turn-off energy.

and three-stage measurements, is plotted against the turnoff energy in Fig. 18. It is seen, that implementing a second stage during the turn-off event gives a better performance of the power semiconductor as all measurement points are found below the reference measurements. The introduction of a third stage shows the possibility of further improvement compared to the two-stage operation.

However, the key statement of the investigation is, that the introduction of an initial fast discharging stage is crucial to achieve improved switching behavior. All together, the drain-source peak voltage  $\hat{U}_{\rm DS}$  is reduced by up to 45% while maintaining equal turn-off losses  $E_{\rm off}$ .

# VIII. SUMMARY OF THE SWITCHING BEHAVIOR

A summary of the switching behavior using the variations of timing and resistances of the different stages is given for both, the turn-on as well as for the turn-off event of the SiC MOSFET. TABLE IX shows the influence of rising gate resistance  $R_{\rm g,on}^{\rm S}$  and rising stage time  $\Delta t_{\rm on}^{\rm S}$  on the device stress,  $\hat{I}_{\rm S}$  and  $\hat{U}_{\rm Diode}$ , as well as on the turn-on loss energies

<sup>8</sup> Equivalents a two-stage turn-off event changing from  $R_{g,off}^{S2} = 0.5 \Omega$  to  $R_{g,off}^{S3} = 100 \Omega$ .

TABLE IX SUMMARY OF THE SIC MOSFET TURN-ON BEHAVIOR

|                                           | $\hat{I}_{\mathbf{S}}$ | $\hat{U}_{\text{Diode}}$ | Eon,Switch | $E_{\rm on,Diode}$ | Eon        | Reference        |

|-------------------------------------------|------------------------|--------------------------|------------|--------------------|------------|------------------|

| $R_{\mathrm{g,on}}^{\mathrm{S1}}\uparrow$ | $\searrow$             | $\searrow$               | 7          | $\rightarrow$      | 7          | Fig. 12, Fig. 15 |

| $\Delta t_{\rm on}^{\rm S1}\uparrow$      | $\nearrow$             | $\nearrow$               | $\searrow$ | ~                  | $\searrow$ | Fig. 13          |

| $R_{\mathrm{g,on}}^{\mathrm{S2}}\uparrow$ | $\searrow$             | $\searrow$               | $\nearrow$ | $\searrow$         | $\nearrow$ | Fig. 13, Fig. 15 |

| $\Delta t_{\rm on}^{\rm S2}\uparrow$      | $\searrow$             | $\searrow$               | 7          | $\searrow$         | $\nearrow$ | Fig. 14          |

| $R_{ m g,on}^{ m S3}\uparrow$             | -                      | -                        | 7          | $\nearrow$         | $\nearrow$ |                  |

TABLE X SUMMARY OF THE SIC MOSFET TURN-OFF BEHAVIOR

|                                            | $\hat{U}_{\mathrm{DS}}$ | $E_{\rm off}$ | Reference        |

|--------------------------------------------|-------------------------|---------------|------------------|

| $R_{\mathrm{g,off}}^{\mathrm{S1}}\uparrow$ | $\searrow$              | 7             | Fig. 12, Fig. 18 |

| $\Delta t_{\rm off}^{\rm S1}$ $\uparrow$   | $\nearrow$              | $\searrow$    | Fig. 16          |

| $R_{\rm g,off}^{\rm S2}\uparrow$           | $\searrow$              | 7             | Fig. 18          |

| $\Delta t_{\rm off}^{\rm S2}$ $\uparrow$   | $\searrow$              | 7             | Fig. 17          |

| $R_{\rm g,off}^{\rm S3}$ $\uparrow$        | -                       | 7             |                  |

$E_{\rm on,Switch}$  and  $E_{\rm on,Diode}$ . Analogously, the influence of the gate resistances  $R_{\rm g,off}^{\rm S}$  and timings  $\Delta t_{\rm off}^{\rm S}$  on the transient voltage overshoot  $\hat{U}_{\rm DS}$  and turn-off energy  $E_{\rm off}$  is tabulated in TABLE X.

The mechanism contributing to the performance improvement of the AGD, compared to the reference driver, relies on the modulation of the gate charge during the switching transient. A fast dis-/charging of the gate is envisaged during the switching phase, where the stress on the device is not critical. However, during the critical phases, the gate dis-/ charging is reduced and the measurements show, that this results in less stress on the power semiconductor compared to a single-stage gate driver.

# IX. CONCLUSIONS

In this work, a stage-wise gate driver based on a switched resistor topology for SiC MOSFETs has been presented. A detailed description of the measurement setup as well as the switching loss extraction has been shown as this is crucial to achieve reliable measurement results. The performance of the stage-wise gate driver was evaluated by benchmarking the device stress, resulting from the switching transients, against the switching losses. Furthermore, the evaluation included a comparison to a reference gate driver, based on a standard push-pull stage using various different gate resistances. A detailed analysis of the two- and three-stage operation of the AGD was conducted for the turn-on and the turnoff event.

It has been shown that the drain-source peak voltage  $\hat{U}_{DS}$  got reduced by 45% while maintaining equal turn-off losses  $E_{off}$ . The turn-on event shows a reduction of 51% of the diode peak voltage  $\hat{U}_{Diode}$  and a reduction of 50% of the peak reverse recovery current  $\hat{I}_{S}$  at the same time for equal turn-

on losses  $E_{on}$ . This allows the utilization of a higher DClink voltage, resulting in a higher power rating of a given converter with a given power semiconductor. This is crucial to reduce price per kilowatt of future high density power electronic converters.

The mentioned achievements should not be considered as the total potential of the driver as no optimization or search for an optimum point was carried out. Furthermore, it is noticed that a closed loop control of the switching trajectory is hardly achievable due to the large delays and late reaction of the power semiconductor.

#### ACKNOWLEDGMENT

The work for this paper has been carried out within the framework of the Deutsche Forschungsgemeinschaft (DFG) - GRK 1856.

#### REFERENCES

- A. Stippich, A. Sewergin, G. Engelmann, J. Gottschlich, M. Neubert, C. van der Broeck, P. Schuelting, R. Goldbeck, and R. De Doncker, "From AC to DC: Benefits in *household appliances*," *in International ETG Congress*, Nov. 2017, pp. 1-6.

- [2] R. W. De Doncker, C. Meyer, R. U. Lenke, and F. Mura, "Power electronics for future utility applications," in *International Conference on Power Electronics and Drive Systems (PEDS)*, Nov. 2007, pp. 1-8.

- [3] A. Stippich, C. H. Van Der Broeck, A. Sewergin, A. H. Wienhausen, M. Neubert, P. Schülting, S. Taraborrelli, H. van Hoek, and R. W. De Doncker, "Key components of modular propulsion systems for next generation electric vehicles," *CPSS Transactions on Power Electronics and Applications*, vol. 2, no. 4, pp. 249-258, Dec. 2017.

- [4] C. Neeb, L. Boettcher, M. Conrad, and R. W. De Doncker, "Innovative and reliable power modules: A future trend and evolution of technologies," *IEEE Industrial Electronics Magazine*, vol. 8, no. 3, pp. 6-16, Sep. 2014.

- [5] G. Engelmann, M. Kowal, and R. W. De Doncker, "A highly integrated drive inverter using directfets and ceramic dc-link capacitors for open-end winding machines in electric vehicles," in *Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2015, pp. 290-296.

- [6] G. Engelmann, T. Senoner, H. van Hoek, and R. W. De Doncker, "A systematic comparison of various thermal interface materials for applications with surfacemounted DirectFET<sup>TM</sup> mosfets," in *International Conference on Power Electronics and Drive Systems (PEDS)*, Jun. 2015, pp. 112-117.

- [7] X. She, A. Q. Huang, O. Lucia, and B. Ozpineci, "Review of silicon carbide power devices and their applications," *IEEE Transactions on Industrial Electronics*, vol. PP, no. 99, pp. 1-1, 2017.

- [8] P. Beckedahl, S. Buetow, A. Maul, M. Roeblitz, and M. Spang, "400 A, 1200 V SiC power module with 1nh commutation inductance," in *International Conference on Integrated Power Electronics Systems* (CIPS), Mar. 2016, pp. 1-6.

- [9] H. A. Mantooth, T. Evans, C. Farnell, Q. Le, and R. Murphree, "Emerging trends in silicon carbide power electronics design," *CPSS Transactions on Power Electronics and Applications*, vol. 2, no. 3, pp. 161-169, Sep. 2017.

- [10] A. Nagel and R. W. De Doncker, "Systematic design of emi-filters for power converters," in *Annual Meeting and World Conference on Industrial Applications of Electrical Energy*, vol. 4, Oct. 2000, pp. 2523-2525.

- [11] S. Yin, K. J. Tseng, R. Simanjorang, and P. Tu, "Experimental comparison of high-speed gate driver design for 1.2-kv/120-a si igbt and sic mosfet modules," *IET Power Electronics*, vol. 10, no. 9, pp. 979-986, 2017.

- [12] C. Ionita, M. Nawaz, K. Ilves, and F. Iannuzzo, "Comparative assess-

ment of 3.3kv/400a SiC MOSFET and Si IGBT power modules," in IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, Oct. 2017.

- [13] R. Hemmer, "Intelligent igbt drivers with exceptional driving and protection features," in *European Conference on Power Electronics and Applications (EPE)*, Sep. 2009, pp. 1-4.

- [14] Y. Lobsiger and J. W. Kolar, "Closed-loop di/dt and dv/dt IGBT gate driver," *IEEE Transactions on Power Electronics*, vol. 30, no. 6, pp. 3402-3417, Jun. 2015.

- [15] G. Engelmann, C. Lüdecke, D. Bündgen, R.W. De Doncker, X. Lu, Z. Xu, and K. Zou, "Experimental analysis of the switching behavior of an igbt using a three-stagegate driver," in *International Symposium on Power Electronics for Distributed Generation Systems (PEDG)*, Apr. 2017, pp. 1-8.

- [16] K. Oberdieck, G. Engelmann, and R. W. De Doncker, "Verfahren zur simulativen Modellierung der Gleichtaktanregung," in *Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit* (*EMV*), 1 vols., Düsseldorf: Apprimus Verlag, Feb. 23, 2016, pp. 591-598.

- [17] T. Bertelshofer, A. M"arz, and M.-M. Bakran, "A temperature compensated overcurrent and short-circuit detection method for SiC MOSFET modules," in European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), IEEE, Sep. 2017.

- [18] S. Inamori, J. Furuta, and K. Kobayashi, "MHzswitching- speed current-source gate driver for SiC power MOSFETs," in European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), IEEE, Sep. 2017.

- [19] J. Yu, Q. Qian, P. Liu, W. Sun, S. Lu, and Y. Yi, "A high frequency isolated resonant gate driver for sic power mosfet with asymmetrical on/off voltage," in *Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2017, pp. 3247-3251.

- [20] S. Hazra, K. Vechalapu, S. Madhusoodhanan, S. Bhattacharya, and K. Hatua, "Gate driver design considerations for silicon carbide MOS-FETs including series connected devices," in IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, Oct. 2017.

- [21] J. Gottschlich, M. Schäfer, M. Neubert, and R. W. De Doncker, "A galvanically isolated gate driver with low coupling capacitance for medium voltage sic mosfets," in *European Conference on Power Electronics and Applications (EPE'16 ECCE Europe)*, Sep. 2016, pp. 1-8.

- [22] F. Gao, Q. Zhou, P. Wang, and C. Zhang, "A gate driver of sic mosfet for suppressing the negative voltage spikes in a bridge circuit," *IEEE Transactions on Power Electronics*, vol. PP, no. 99, pp. 1-1, 2017.

- [23] A. März, T. Bertelshofer, M. Helsper, and M.-M. Bakran, "Comparison of SiC MOSFET gate-drive concepts to suppress parasitic turn-on in low inductance power modules," in European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), IEEE, Sep. 2017.

- [24] F. Mo, J. Furuta, and K. Kobayashi, "A low surge voltage and fast speed gate driver for sic mosfet with switched capacitor circuit," in *Workshop on Wide Bandgap Power Devices and Applications (WiP-DA)*, Nov. 2016, pp. 282-285.

- [25] H. Li, Y. M. Abdullah, C. Yao, X. Wang, and J. Wang, "Active gate current control for non-insulating-gate WBG devices," in IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, Oct. 2017.

- [26] T. Shimomura, T. Ikari, A. Okubo, R. Yamada, K. Numakura, and T. Hayashi, "High speed dV/dt control technology for SiC power module for EV/HEV inverters," in IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, Oct. 2017.

- [27] M. Ebli and M. Pfost, "A novel gate driver approach using inductive feedback to increase the switching speed of power semiconductor devices," in European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), IEEE, Sep. 2017.

- [28] A. Niwa, T. Imazawa, R. Kojima, M. Yamamoto, T. Sasaya, T. Isobe, and H. Tadano, "A dead-timecontrolled gate driver using current-sense FET integrated in SiC MOSFET," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 3258-3267, Apr. 2018.

- [29] A. P. Camacho, V. Sala, H. Ghorbani, and J. L. R. Martinez, "A novel active gate driver for improving sic mosfet switching trajectory," *IEEE Transactions on Industrial Electronics*, vol. PP, no. 99, pp. 1-1, 2017.

87

- [30] H. C. P. Dymond, D. Liu, J. Wang, J. J. O. Dalton, and B. H. Stark, "Multi-level active gate driver dorsic mosfets," in IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, Oct. 2017.

- [31] E. Shelton, N. Hari, X. Zhang, T. Zhang, J. Zhang, and P. Palmer, "Design and measurement considerations for wbg switching circuits," in European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), IEEE, Sep. 2017.

- [32] Cree, Inc, Cpm2-1200-0040b silicon carbide power mosfet, CPM2-1200-0040B datasheet, Oct. 2016.

- [33] G. Engelmann, S. Quabeck, J. Gottschlich, and R. W. De Doncker, "Experimental and simulative investigations on stray capacitances and stray inductances of power modules," in *European Conference* on Power Electronics and Applications (EPE'17 ECCE Europe), Sep. 2017, pp.1-10.

- [34] J. Gottschlich and R. W. De Doncker, "Pulse generator for dynamic performance verification of current transducers," in *European Conference on Power Electronics and Applications (EPE)*, Sep. 2015, pp. 1-8.

- [35] C. Schulte-Overbeck, Z. Cao, F. Khan, F. Hussain, S. Grandhi, and D. Weiss, "Comparative analysis of the measurement techniques to characterize sic-powermodules," in *International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe)*, May 2017, pp. 1-8.

- [36] J. Gottschlich, M. Kaymak, M. Christoph, and R. De Doncker, "A flexible test bench for power semiconductor switching loss measurements," in *International Conference on Power Electronics and Drive Systems (PEDS)*, Jun. 2015, pp. 442-448.

- [37] G. Engelmann, M. Laumen, J. Gottschlich, K. Oberdieck, and R. W. De Doncker, "Temperature controlled power semiconductor characterization using thermoelectric coolers," *IEEE Transactions on Industry Applications*, pp. 1-1, 2018.

- [38] Y. Xiong, S. Sun, H. Jia, P. Shea, and Z. J. Shen, "New physical insights on power mosfet switching losses," *IEEE Transactions on Power Electronics*, vol. 24, no. 2, pp. 525-531, Feb. 2009.

Georges Engelmann was born in Wiltz, Luxembourg in 1987. He received the Diploma degree in electrical engineering from RWTH Aachen University, Aachen, Germany in 2012. Since 2013 he has been a Research Associate at the Institute for Power Electronics and Electrical Drives (ISEA) at RWTH Aachen University, Germany. His research interests are in the field of power semiconductor switching characterization as well as active gate drivers for wide-bandgap devices.

**Tizian Senoner** was born in Brixen, Italy in 1992. He received the B.Sc. and M.Sc. degrees in electrical engineering from RWTH Aachen University, Aachen, Germany, in 2014 and 2017. He is currently working as a hardware and system development engineer at alpitronic GmbH-SRL, Bozen, Italy. His research interests include the analysis and design of low and medium power electronic converters as well as wide-bandgap semiconductors.

**Rik W. De Doncker** received the Ph.D. degree in electrical engineering from Katholieke Universiteit Leuven, Leuven, Belgium, in 1986. In 1987, he joined the University of Wisconsin, Madison, WI, USA, as a Visiting Associate Professor. After a short stay as an Adjunct Researcher at the Interuniversity Microelectronics Centre, Leuven, he joined, in 1989, the Corporate Research and Development Center, General Electric Company, Schenectady, NY, USA. In 1994, he joined Silicon Power Corpo-

ration, Malvern, PA, USA, a former division of General Electric Inc., as the Vice President of Technology. In 1996, he became a Professor with RWTH Aachen University, Aachen, Germany, where he currently leads the Institute for Power Electronics and Electrical Drives. Since 2006, he has been the Director of the E.ON Energy Research Center, RWTH Aachen University.

Dr. De Doncker was the President of the IEEE Power Electronics Society (PELS) in 2005 and 2006. He was the founding Chairman of the German IEEE Industry Applications Society PELS Joint Chapter. In 2002, he received the IEEE Industry Applications Society Outstanding Achievement Award. In 2008, he received the IEEE Power and Energy Society Nari Hingorani Custom Power Award. In 2009, he led a Verband der Elektrotechnik, Elektronik, und Informationstechnik (VDE) / Energietechnische Gesellschaft (ETG) Task Force on Electric Vehicles. In 2010, he received the IEEE William E. Newell Power Electronics Award.