# Experimental study on sheet resistivity and thickness measurement in Copper Electroplating

Akshdeep Sharma<sup>\*</sup>, Sumit Kumar Khandelwal<sup>\*</sup>, Deepak Bansal<sup>\*</sup>, Kamaljit Rangra<sup>\*</sup>, Dinesh Kumar<sup>\*\*</sup>

\*Sensors and Nanotechnology Group, Central Electronics Engineering Research Institute (CEERI)/ Council of Scientific and Industrial Research (CSIR), Pilani, Rajasthan, India, <u>akshdeepsharma@gmail.com</u>, <u>kjrangra@gmail.com</u>

\*\*Dept. of Electronics Science, Kurukshetra University, Kurukshetra, Haryana, India, <u>dineshelectronics@gmail.com</u>

# ABSTRACT

Electroplated copper thin films have been extensively used for interconnections in semiconductor devices. In this paper, electroplating of copper has been investigated to study the dependency of plated film thickness, current efficiency and sheet resistivity on current density. Copper film is electroplated on gold seed layer for via filling using different current densities varying from 10mA/cm<sup>2</sup> to 70mA/cm<sup>2</sup> at constant temperature (40°C). Annealing analysis for plated thick film is done at 200°C for 30 minutes. Surface roughness reduces along with resistivity with annealing.

*Keywords*: Electroplating, Current density, Deposition rate, Sheet resistivity, Current efficiency

## 1. INTRODUCTION

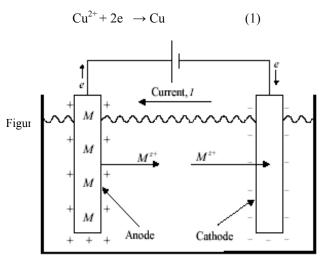

Electroplating is an electro deposition process for producing a dense, uniform and adherent coating, usually of metal or alloys, upon a surface by the act of electric current [1]. The coating produced is usually for decorative and or protective purposes, or enhancing specific properties of the surface. The surface can be conductor, such as metal, or nonconductor, such as plastics. The core part of the electroplating process is the electrolytic cell (electroplating unit). In the electrolytic cell a current is passed through a bath containing electrolyte, the anode, and the cathode as shown in figure 1. In industrial production, pre-treatment and post treatment steps are usually needed [2].

Copper is the most common metal plated, exclusive of continuous strip plating [3]. Major uses of electroplated copper are plating on plastics, printed wiring boards, zinc die castings, automotive bumpers, rotogravure rolls, electro refining, and electroforming [4]. Electroplated Copper is playing a major role in the change from aluminum to copper in semiconductor technology.

Copper is excellent choice for an under plate, since it often covers minor imperfections in the base metal. It is relatively inert in most plating solutions of other common metals, it has very high plating efficiency, resulting in excellent coverage even on difficult to plate parts, and lastly, it is highly conductive, making it an excellent coating for printed wiring boards or as a coating on steel wire used to conduct electricity.

# 2. THEORY AND CALCULATIONS

Electro deposition or electrochemical deposition (of metals or alloys) involves the reduction of metal ions from electrolytes. At the cathode, electrons are supplied to cations, which migrate to the anode. In its simplest form, the reaction in aqueous medium at the cathode follows the equation:

Figure 1 Electrodeposition cell

At the anode, electrons are supplied to the anions, which migrate to the anode. The anode material can be either a sacrificial anode or an inert anode. For the sacrificial anode, the anode reaction is:

$$Cu \to Cu^{2+} + 2e \tag{2}$$

In this case, the electrode reaction is electro dissolution that continuously supplies the metal ions. Deposited Copper thickness calculated as [1]:

$$t = \frac{W}{A * d} \tag{3}$$

Where, W= Weight of deposit, A = Area to be deposited, d = density of copper

The current efficiency CE of the *j*th process is defined as number of coulombs required for that reaction,  $Q_j$ , divided by the total number of coulombs passed,  $Q_{\text{total}}$  [5].

$$CE = \frac{Q_j}{Q_{total}} \tag{4}$$

### **3. EXPERIMENTAL DETAILS**

Here, we have successfully Electroplated Copper metal on gold base. Silicon substrate with gold seed layer of thickness 2000Å has been used as a substrate. Then the Copper was deposited on the gold layer by electroplating. The composition of the base electrolyte used for all plating test was 0.88M CuSO4.5H2O. The temperature of the plating solution was maintained at  $40^{\circ}$ C. Area to be deposited was 70 mm<sup>2</sup> Electroplating time for all the samples was set to 20 min. With temperature and time constant for all the samples, current density was varied from 10mA/cm<sup>2</sup> to 70mA/cm<sup>2</sup>. The thickness of the electroplated copper was measured using surface profiler. Table 1 shows the experimental analysis of sample with current density variations.

| Test<br>Sample | Current<br>Density<br>mA/cm <sup>2</sup> | Q<br><sub>total</sub> =<br>I*t | Qj | Theoretical Thickness, $t_1(\mu m)$ | Actual<br>Thicknes<br>s, $t_2$ (µm) | CE    |

|----------------|------------------------------------------|--------------------------------|----|-------------------------------------|-------------------------------------|-------|

| 1              | 10                                       | 8.4                            | 4  | 4.368                               | 2.08                                | 47.61 |

| 2              | 20                                       | 16.8                           | 8  | 8.736                               | 4.16                                | 47.61 |

| 3              | 30                                       | 25.2                           | 16 | 13.104                              | 8.32                                | 63.49 |

| 4              | 40                                       | 33.6                           | 23 | 17.472                              | 11.96                               | 68.45 |

| 5              | 50                                       | 42                             | 38 | 21.84                               | 19.76                               | 90.47 |

| 6              | 60                                       | 50.4                           | 44 | 26.208                              | 22.88                               | 87.30 |

| 7              | 70                                       | 58.8                           | 49 | 30.576                              | 25.48                               | 83.33 |

#### Table 1 Experimental analysis

# 4. RESULT AND DISCUSSION

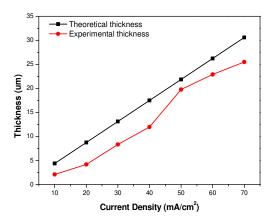

It was observed that with increase in current density, thickness of the deposit increases, as more number of copper ions gets reduced. Also, it was observed that current efficiency increases with current density up to certain current density and there after it starts decreasing as shown in table 1. The variation of theoretical and experimental electrodeposit thickness with respect to current density is shown in figure 2.

Figure 2 Thickness variations with current density

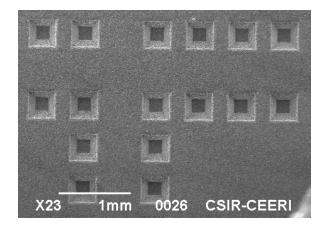

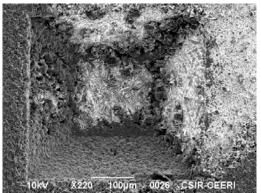

The SEM image of the samples was taken after electroplating, and it was observed that grain size increases with increase in current density. So, at higher rate more roughness was observed. To overcome this problem, we had done annealing on all the samples. Annealing was done at  $200^{\circ}$ C for half an hour. It was interesting to note that along with roughness, sheet resistivity also gets reduced. Surface topographic variations and resistivity measurements with change in current densities were shown in Table 2. Experimentally extracted parameters were used for filling via cavity made of silicon. Figure 3 shows the SEM micrographs of silicon cavities and figure 4 shows cavity during Cu filling.

Figure 3 SEM micrographs of silicon cavities.

Figure 4 SEM micrographs of silicon cavity during Cu filling.

Table 2 SEM micrographs of the samples with resistivity

| CD      | Surface    | Sheet                  | Surface    | Sheet                  |

|---------|------------|------------------------|------------|------------------------|

| (m      | Rougness   | Resisance              | Rougness   | Resistance             |

| A/c     | (Before    | $(\Omega/\Box)$        | (After     | $(\Omega/\Box)$        |

| $m^2$ ) | Annealing) |                        | Annealing) |                        |

| 10      |            | 0.78*10 <sup>-2</sup>  |            | 0.431*10 <sup>-2</sup> |

| 20      |            | 0.445*10 <sup>-2</sup> |            | 0.268*10 <sup>-2</sup> |

| 30      |            | 0.215*10 <sup>-2</sup> |            | 0.194*10 <sup>-2</sup> |

| 40      |            | 0.212*10 <sup>-2</sup> |            | 0.931*10 <sup>-3</sup> |

| 50      |            | 1.17*10 <sup>-3</sup>  |            | 0.786*10 <sup>-3</sup> |

| 60      |            | 0.977*10 <sup>-3</sup> |            | 0.591*10 <sup>-3</sup> |

| 70      |            | 0.926*10 <sup>-3</sup> |            | 0.336*10 <sup>-3</sup> |

### CONCLUSIONS

It is concluded that the deposition rate as well as surface roughness increases while sheet resistivity decreases by increasing the current density during electro deposition. Thus, according to the need and purpose current density can be varied for getting suitable deposition rate and roughness.

For the purpose of via filling in through etched silicon cavity higher deposition rate (high current density) process is desired. But at higher rate more roughness was observed. To overcome this problem annealing was done. It is interesting to note that along with roughness, sheet resistivity also gets reduced which serve the purpose via filling.

### ACKNOWLEDGEMENTS

Authors would like to acknowledge Director, CEERI, Pilani, for providing the fabrication facilities and CSIR New Delhi for financial support. The authors would also like to thank all the members of sensors and nanotechnology group for their help in fabrication.

# REFERENCES

[1] Paunovic, M. and M. Schlesinger, Fundamental of electrochemical deposition 2nd edition. Book 2006.

[2] L. W. Flott, Metal Finishing, 94, 55 (March 1996).

[3] R. Sard, Encyclopedia of materials science and engineering, vol. 2, M. B. Bever, ed., 1423 Wiley, New York, 1986

[4] D. Manessis, S-F.Yen, A. Ostmann, R. Aschenbrenner and H. Reichl, "Technical Understanding of Resin Coated Copper (RCC) lamination processes for realisation of reliable chip embedding technologies", Proc. Electronics Components & Technology Conference (ECTC) 2007, Reno, NV, May 29- June 1, 2007, pp. 278-285.

[5] A. Ostmann, D. Manessis, H. Stahr, M. Beesley, J. De Baets, M. Cauwe, "Industrial and technical Aspects of chip embedding", Proceedings in the 2<sup>nd</sup> Electronics System Integration Technology Conference (ESTC) 2008, Greenwich, September 1-5, 2008, pp. 315-320.