# Extraction of Gate Resistance in Sub-100-nm MOSFETs With Statistical Verification

Xuesong Chen, Mu Kai Tsai, Chih-Hung Chen, Senior Member, IEEE, Ryan Lee, and David C. Chen, Senior Member, IEEE

*Abstract*— This paper presents an improved *z*-parameter based approach to extract the gate resistance at low frequencies. The effectiveness of this approach, compared with other *y*-parameter based approaches, is verified using 430 samples fabricated in 40-, 55-, 90-, and 110-nm CMOS technology nodes. The influence of the nonquasi-static (NQS) effect, resulting from the distributed channel resistance, on the gate resistance extraction is studied, and the optimum processes are suggested to reduce the NQS effect. Finally, the extraction of the channel resistance in the lightly doped drain region is also presented.

*Index Terms*—Distributed channel resistance, distributed poly-silicon gate resistance, gate contact resistance, gate resistance extraction, nonquasi-static (NQS) effect.

#### I. INTRODUCTION

**D** UE to the aggressive scaling in the feature size and its resulting very high cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{\text{max}})$  in hundreds of GHz, nanoscale CMOS technology has already become a potential candidate for sub-THz applications [1]. As predicted in the 2012 International Technology Roadmap for Semiconductors [2], multigate MOSFETs with 15.3-nm gate length can achieve 710 and 622 GHz for  $f_T$  and  $f_{\text{max}}$ , respectively. However, when working at such high frequencies and aiming at low-power applications, the noise from the transistor itself become critically important and therefore accurate noise models are required. In addition to the channel thermal noise, induced gate noise, and their correlations, the noise from the gate resistance is the major noise contributor because its effect is amplified by the transistor itself to the next stage. Therefore, how to accurately extract the gate resistance from experiments and provide a scalable gate resistance model become very crucial for low-noise and low-power applications. In addition, the accuracy of the extracted gate resistance has a great impact on the extraction of the channel thermal noise, induced gate noise, and their correlations [3], the noise evaluation between

Manuscript received February 26, 2014; accepted July 16, 2014. Date of publication July 31, 2014; date of current version August 19, 2014. This work was supported by the National Sciences and Engineering Research Council of Canada. The review of this paper was arranged by Editor C. K. Sarkar.

X. Chen and C.-H. Chen are with the Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON L8S 4L8, Canada (e-mail: chenx79@mcmaster.ca; chench@mcmaster.ca).

M. K. Tsai, R. Lee, and D. C. Chen are with United Microelectronics Corporation, Hsinchu 300, Taiwan (e-mail: mu\_kai\_tsai@umc.com; ryan\_lee@umc.com; david\_chen@umc.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2014.2340871

technologies using the equivalent noise sheet resistance [4], the investigation of device reliability [5]–[7], and the thermal noise modeling of devices [8]–[10].

Due to the gate-to-source and the gate-to-drain capacitances, the gate resistance cannot be directly characterized from the I-V measurements. Z- or y-parameters obtained at high frequencies are therefore used to extract the gate resistance [11]–[21]. For the z-parameter based approaches in [11], [17], and [21], to remove the impact from the frequency-dependent term (e.g.,  $A_{g}/(\omega^{2} + B)$  in [11]), z-parameters measured at very high frequencies (e.g., 35–40 GHz) are needed [21] that put a very high demand on the equipment and the accuracy of the equivalent circuit model. On the other hand, at high frequencies, the total gate resistance  $R_g$  seen at the gate terminal is not only contributed from the gate contact resistance  $R_{gcon}$ and the distributed poly-silicon gate resistance  $R_{\text{gpoly}}$  but also from the distributed channel resistance  $R_{ch}$  [12], [16]. When extracting the gate resistance at such high frequencies, the nonquasi-static (NQS) effect becomes very pronounced and causes the distributed channel resistance  $R_{ch}$  to be the dominant contributor in the extracted gate resistance [16]. The separation of  $R_{ch}$  from  $R_{gcon}$  and  $R_{gpoly}$  is not only important in accurately describing the RF behavior of MOSFETs [20] but also crucial in the thermal noise modeling. Since the thermal noise in the channel is already taken care of by another noise current source [8],  $R_{ch}$  should be modeled as a noise free resistor. If  $R_{ch}$  is included in  $R_g$  as a noisy resistor and used in the thermal noise extraction, it results in an underestimation of the channel thermal noise and, therefore, demonstrates a wrong bias and geometry dependence in the channel thermal noise modeling.

For the *z*-parameter based approach in [18], the algorithm can extract  $R_g$  at low frequencies. However, its equivalent circuit in [18, Fig. 1] cannot be applied at all gate bias conditions and becomes invalid particularly at  $V_{GS} = 0$  V due to the ignorance of the coupling capacitance  $C_{gb}$  between the gate and the substrate [20], [22]. In addition, its algorithm and accuracy are affected by the assumption, i.e.,  $R_i = R_{ch}/6$  [18] or  $R_i = R_{ch}/3$  [23], used in the equation derivation. Therefore, in this paper, we propose an improved *z*-parameter based approach to extract  $R_g$  at low frequencies. Since the lowfrequency extrapolation is applied in the algorithm, we can use a very simple small-signal equivalent circuit for medium high frequencies in [22] and the high-frequency components such

0018-9383 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

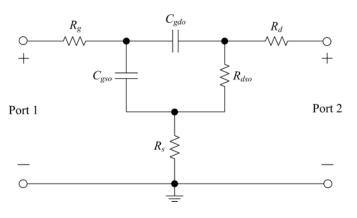

Fig. 1. Equivalent circuit for a MOSFET biased at  $V_{\text{GS}} = V_{\text{dd}}$  (nominal supply voltage) and  $V_{\text{DS}} = 0$  V for medium-high-frequency applications.

as  $C_m$ ,  $C_{mb}$ ,  $C_{mx}$ , and  $C_{sd}$  in [21] and [22] can be all ignored. This low-frequency approach not only reduces the complexity of the equivalent circuit without losing its generality and accuracy but also simplifies its analytical *z*-parameter expressions. In addition, it prevents the impact from the substrate coupled into the experimental results. Finally, to improve the extraction accuracy and avoid the NQS effect, we evaluate the  $R_g$  extracted from devices fabricated in different processes and suggest the optimum processes most suitable for gate resistance extraction.

## II. EXTRACTION OF GATE RESISTANCE

The device under test (DUT) is biased at the condition of  $V_{\rm GS} = V_{\rm dd}$  (nominal supply voltage) and  $V_{\rm DS} = 0$  V. We improve the approach in [18] by choosing  $V_{\rm GS} = V_{\rm dd}$ to physically eliminate the coupling between the gate and the substrate (i.e.,  $C_{\rm gb} \approx 0$  fF [20]). At medium high frequencies, its small-signal equivalent circuit is shown in Fig. 1, where  $R_g$  is the gate resistance to be extracted,  $R_d$  and  $R_s$  are the parasitic resistances at the drain and the source terminals, respectively,  $R_{\rm dso}$  includes the channel resistance  $R_{\rm ch}$ and the resistance  $R_{LDD}$  in the lightly doped drain (LDD) regions. Here,  $C_{gso}$  and  $C_{gdo}$  are the gate-to-source and gateto-drain capacitances, respectively. Because of the symmetry of the drain and source terminals at  $V_{\rm DS} = 0$  V,  $C_{\rm gso}$  and  $C_{\rm gdo}$  are equal in both their intrinsic portion from the oxide capacitance  $(C_{ox}/2)$  [22] and extrinsic portion from the overlap capacitance  $C_{ov}$ . In this paper, we define  $C_{gso} = C_{gdo} = C_{oxv}$ , which can be directly extracted from the measured imaginary part of  $y_{11}$  (i.e.,  $Im(y_{11})$ ) versus frequency characteristics [14]. In addition, we assume that  $R_d = R_s$  due to the symmetry of the MOSFET structure at  $V_{DS} = 0$  V. Based on the equivalent circuit in Fig. 1, its z-parameters can be expressed as

$$Z_{11} = R_g + R_s + \frac{R_{\rm dso}}{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4} - j \frac{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 2}{\omega C_{\rm oxv} (\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4)}$$

$$\cong \left( R_g + R_s + \frac{R_{\rm dso}}{4} \right) - j \left( \frac{1}{2\omega C_{\rm oxv}} \right) \tag{1}$$

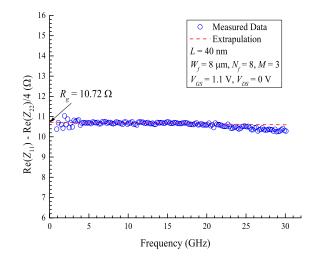

Fig. 2. Re( $Z_{11}$ ) - Re( $Z_{22}$ )/4 versus frequency characteristics for an n-type FET with L = 40 nm,  $W_f = 8 \ \mu$ m,  $N_f = 8$ , and M = 3 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V.

$$Z_{12} = Z_{21} = R_s + \frac{2R_{\rm dso}}{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4} - j \frac{\omega R_{\rm dso}^2 C_{\rm oxv}}{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4}$$

$$\cong \left(R_s + \frac{R_{\rm dso}}{2}\right) - j \left(\frac{\omega R_{\rm dso}^2 C_{\rm oxv}}{4}\right) \tag{2}$$

and

$$Z_{22} = R_d + R_s + \frac{4R_{\rm dso}}{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4} - j \frac{2\omega R_{\rm dso}^2 C_{\rm oxv}}{\omega^2 R_{\rm dso}^2 C_{\rm oxv}^2 + 4}$$

$$\cong \left( R_d + R_s + R_{\rm dso} \right) - j \left( \frac{\omega R_{\rm dso}^2 C_{\rm oxv}}{2} \right)$$

(3)

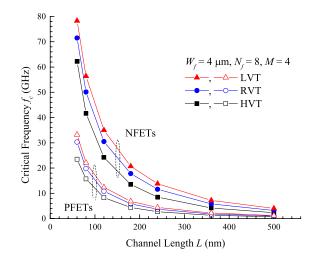

where  $s = j\omega$ . During the derivation, the only assumption we made was that the frequency is low enough such that  $\omega R_{\rm dso}C_{\rm oxv} \ll \sqrt{2}$  can be held. If we define the critical frequency  $\omega_c = 2 \pi f_c$  such that  $\omega_c R_{\rm dso}C_{\rm oxv} = \sqrt{2}/10$ , or

$$f_c = \left(\frac{1}{10}\right) \cdot \frac{1}{\sqrt{2\pi} R_{\rm dso} C_{\rm oxv}} \tag{4}$$

for the technology studied in the paper,  $f_c$  becomes higher when the channel length decreases because of the reduction of  $R_{dso}$  and  $C_{oxv}$ , and is usually in the range of tens of GHz if the channel length is shorter than 240 nm for n-type MOSFETs and 120 nm for p-type MOSFETs.

For matured CMOS technology, the parasitic resistances at the drain and the source sides are always engineered in the way such that  $R_{dso} \gg R_d$  and  $R_s$  to ensure that the applied  $V_{DS}$  voltage is mainly drop across the intrinsic channel (i.e.,  $R_{dso}$ ) in all regions of operation. In practice,  $R_{dso}$  is about 100 times bigger than  $R_d$  and  $R_s$ . We can then further simplify (1) and (3) by

$$Z_{11} \cong \left(R_g + \frac{R_{\rm dso}}{4}\right) - j\left(\frac{1}{2\omega C_{\rm oxv}}\right) \tag{5}$$

and

$$Z_{22} \cong R_{\rm dso} - j \left( \frac{\omega R_{\rm dso}^2 C_{\rm oxv}}{2} \right). \tag{6}$$

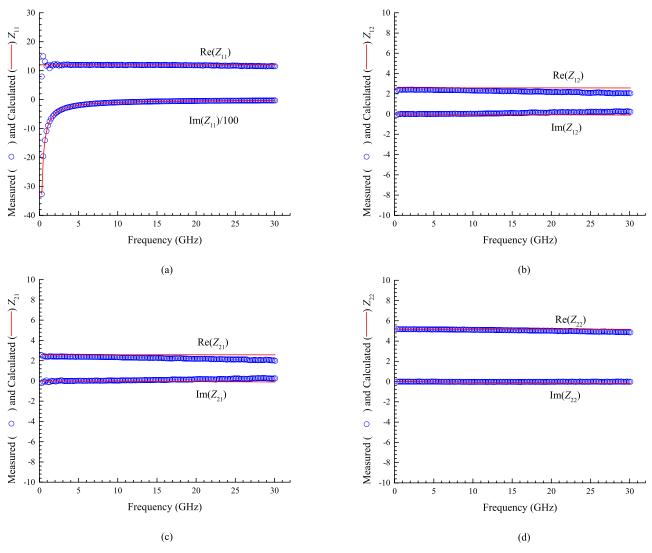

Fig. 3. Measured and calculated intrinsic z-parameters (a)  $Z_{11}$ , (b)  $Z_{12}$ , (c)  $Z_{21}$ , and (d)  $Z_{22}$  versus frequency characteristics for an n-type FET with L = 40 nm,  $W_f = 8 \ \mu$ m,  $N_f = 8$ , and M = 3 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V. The calculation is based on the equivalent circuit in Fig. 1 with  $R_g = 10.72 \ \Omega$ ,  $C_{gso} = C_{gdo} = 80.8$  fF,  $R_{dso} = 5.2 \ \Omega$ , and  $R_s = R_d = 0 \ \Omega$ .

Therefore,  $R_g$  can be extracted by

$$R_g = Re(Z_{11}) - \frac{Re(Z_{22})}{4} \tag{7}$$

where Re() denotes the real part of the parameters.

### **III. RESULTS AND DISCUSSION**

The DUTs were designed in multifuger structures, and the total channel width W is expressed as  $M \times N_f \times W_f \mu m$ , where M is the number of transistors connected in parallel in a DUT,  $N_f$  is the number of transistor fingers, and  $W_f$  is the finger width of each transistor. To verify the extraction procedure, Fig. 2 shows the measured intrinsic (after deembedding the pad parasitics)  $Re(Z_{11}) - Re(Z_{22})/4$  versus frequency characteristics for an n-type FET with L = 40 nm,  $W_f = 8 \mu m$ ,  $N_f = 8$ , and M = 3 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V. Based on (4), the critical frequency  $f_c$  is 53.8 GHz which is much higher than the highest frequency 30.1 GHz in the measurements. In Fig. 2, the measured  $Re(Z_{11}) - Re(Z_{22})/4$  is pretty constant up to 15 GHz. Therefore, the resistance  $R_g$

can be obtained by extrapolating the measured  $Re(Z_{11}) - Re(Z_{22})/4$  versus frequency characteristics down to dc and we get  $R_g = 10.72 \ \Omega$  for this device.

The next step is to verify the accuracy of the equivalent circuit used in this paper (Fig. 1). Fig. 3 shows the measured and calculated intrinsic z-parameters versus frequency characteristics for an n-type FET with L = 40 nm,  $W_f = 8 \mu$ m,  $N_f = 8$ , and M = 3 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V. The calculation is based on the equivalent circuit with  $R_g =$ 10.72  $\Omega$ ,  $C_{\rm gso} = C_{\rm gdo} = 80.8$  fF,  $R_{\rm dso} = 5.2 \Omega$ , and  $R_s = R_d = 0 \ \Omega$ . Very good agreement is obtained for all four parameters up to 15 GHz [as determined by  $Z_{12}$  and  $Z_{21}$  shown in Fig. 3(b) and (c)], which is high enough for our extraction procedure. The excellent agreement in  $Z_{11}$  and  $Z_{22}$  confirms that the strategy using the bias condition at  $V_{\rm GS} = 1.1$  V and  $V_{\rm DS} = 0$  V successfully blocks the impact of substrate parasitics coupled into the measured z-parameters and the simple equivalent circuit shown in Fig. 1 is applicable in the gate resistance extraction. The discrepancy between the measured and calculated  $Z_{12}$  and  $Z_{21}$  above 15 GHz could

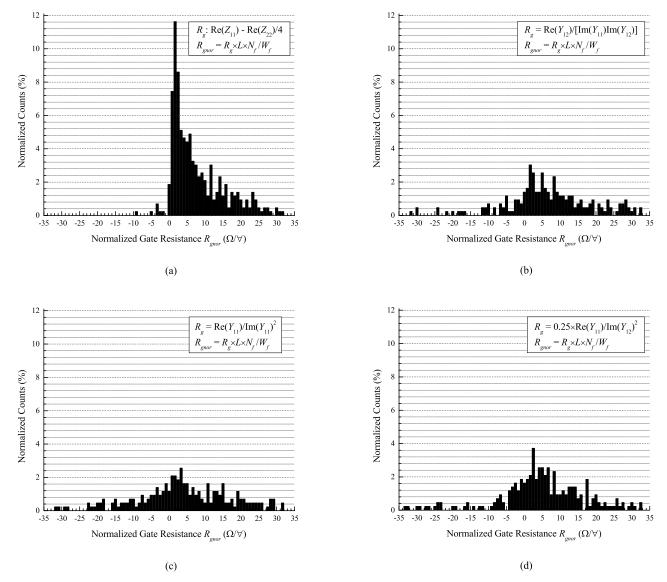

Fig. 4. Normalized histograms (normalized to 430) of the normalized gate resistance  $R_{gNOR}$  ( $\Omega/\forall$ ) using  $R_g$  extracted from the (a) proposed method (i.e.,  $R_g = Re(Z_{11}) - Re(Z_{22})/4$ ), (b)  $R_g = Re(Y_{12})/Im(Y_{11}) \cdot Im(Y_{12})$  [13], (c)  $R_g = Re(Y_{11})/Im(Y_{11})^2$  [14], [21], and (d)  $R_g = Re(Y_{11})/4 \cdot Im(Y_{12})^2$  [20].

result from the ignorance of the high-frequency components such as  $C_m$ ,  $C_{\rm mb}$ ,  $C_{\rm mx}$ , and  $C_{\rm sd}$  in [21] and [22].

For future sub-100-nm technology nodes, process variations, coming from both historical sources and emerging sources, become a very crucial aspect in the device fabrications [24]. Therefore, any proposed parameter extraction routine needs to be robust enough to demonstrate its statistical stability. To verify the robustness of this proposed extraction procedure, we applied our procedure to the experimental data from 430 devices with various L,  $W_f$ ,  $N_f$ , and M combination fabricated in UMCs 40-, 55-, 90-, and 110-nm CMOS technology nodes and compared its stability and robustness against previously published y-parameter based approaches using  $R_g = Re(Y_{12})/Im(Y_{11}) \cdot Im(Y_{12})$  [13] and  $R_g = Re(Y_{11})/Im(Y_{11})^2$  [14], [21]. For the equation from [13], we remove its modulus sign in (34) because it can be deduced directly from (27) and (28), and the modulus sign was proposed by the authors with no reason. We also evaluate another y-parameter based approach in [20], which

directly extracts the distributed gate electrode resistance  $R_{\text{elect}}$ . When  $V_{\text{GS}} = V_{\text{dd}}$ , we can observe from [20] that  $C_{\text{gb}} \approx 0$  fF. In addition, if we substitute (9) (i.e.,  $C_{\text{gso}} = -Im(Y_{12})/\omega$ ) into its  $R_{\text{elect}}$  (i.e., [20, eq. (12)]), we can obtain

$$R_g = R_{\text{elect}} = \frac{Re(Y_{11})}{4 \cdot Im(Y_{12})^2}.$$

(8)

Since these 430 devices have various L,  $W_f$ ,  $N_f$ , and M values, for the purpose of comparison between different methods, we define the normalized gate resistance  $R_{\text{gnor}}$  ( $\Omega/\Box$ ) by

$$R_{\text{gnor}} = R_g \cdot \left(\frac{L \cdot N_f \cdot M}{W_f}\right). \tag{9}$$

Please note that the normalized gate resistance  $R_{gnor}$  is not the same as the sheet resistance  $R_{gsh}$  of the distributed poly-silicon resistance  $R_{gpoly}$  because the extracted  $R_g$ still consists of the distributed channel resistance  $R_{ch}$  and the gate contact resistance  $R_{gcon}$ . Fig. 4 shows the normalized histograms (normalized to 430) of  $R_{gnor}$  obtained

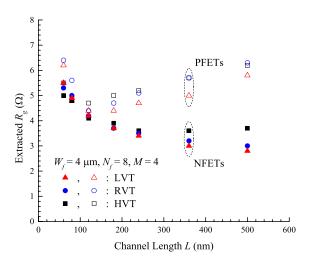

Fig. 5. Extracted  $R_g$  versus channel length characteristics for devices with  $W_f = 4 \ \mu m$ ,  $N_f = 8$ , and M = 4 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V fabricated in a 55-nm node with LVT, RVT, and HVT processes, respectively.

by our proposed method and other methods presented in [13] [Fig. 4(b)], [14], [21] [Fig. 4(c)], and [20] [Fig. 4(d)]. We observed that for our proposed method, 86% of the extracted  $R_{\text{gNOR}}$  (i.e., 370 samples) falls in between 0 and 35  $\Omega/\Box$ , while 38.8% (167 samples) for the method in [13], 34.9% (150 samples) for the approach in [14] and [21], and 42.3% (182 samples) for the method in [20]. In addition, among all the methods, our proposed approach gives the fewest counts for the negative  $R_{\text{gnor}}$ , which is physically incorrect. Therefore, our proposed extraction procedure is statistically most stable and robust among all of the published methods in the literature. Please note that due to the NQS effect resulted from the distributed channel resistance  $R_{\text{ch}}$ , the count distribution of the normalized  $R_{\text{gnor}}$  in the histogram is affected by the technology node and the device geometry.

To evaluate the impact of the NQS effect on the  $R_g$ extraction, one way is to plot the extracted  $R_g$  as a function of channel length [16]. Cheng and Matloubian [16] already investigated the bias and geometry dependence of the NQS effect on the extracted  $R_g$ . In this paper, we want to investigate its dependence on processes. It is well known that the distributed poly-silicon gate resistance  $R_{\text{gpoly}}$  is proportional to  $W_f/L$  [12], while the distributed channel resistance  $R_{ch}$ is proportional to  $L/W_f$  [16]. Therefore, the impact of the NQS effect becomes dominant when the extracted  $R_g$  starts to increase with the channel length. On the other hand, for both n- and p-type FETs, different implants were used to change the threshold voltage  $V_{\rm TH}$  and therefore resulted in different  $R_{\rm dso}$  (or  $R_{\rm ch}$ ). If  $R_{\rm gpoly}$  is dominant, we do not expect that the implants will affect the extracted  $R_g$ . However, if  $R_{ch}$ is dominant, the extracted  $R_g$  will vary monotonically with channel implants. Fig. 5 shows the extracted  $R_g$  versus channel length characteristics for devices with  $W_f = 4 \ \mu m$ ,  $N_f = 8$ , and M = 4 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V fabricated in a 55-nm technology node with low V<sub>TH</sub> (LVT), regular V<sub>TH</sub> (RVT), and high V<sub>TH</sub> (HVT) processes. We observed that p-type FETs suffer from the NQS effect more than the n-type FETs, and therefore the extracted  $R_g$  increases at a

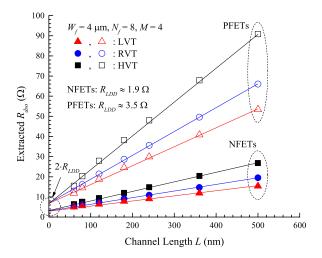

Fig. 6. Extracted channel resistance  $R_{\rm dso}$  versus channel length characteristics for devices with  $W_f = 4 \ \mu m$ ,  $N_f = 8$ , and M = 4 biased at  $V_{\rm GS} =$ 1.1 V and  $V_{\rm DS} = 0$  V fabricated in a 55-nm node with LVT, RVT, and HVT processes, respectively.

Fig. 7. Critical frequency  $f_c$  versus channel length characteristics for devices with  $W_f = 4 \ \mu m$ ,  $N_f = 8$ , and M = 4 biased at  $V_{GS} = 1.1$  V and  $V_{DS} = 0$  V fabricated in a 55-nm node with LVT, RVT, and HVT processes, respectively.

much shorter channel length (around 120 nm in this paper). This is because, p-type FETs have a higher channel resistance  $R_{\rm dso}$  as demonstrated in Fig. 6. For n-type FETs, we observed that RVT and LVT processes have lower channel resistance  $R_{\rm dso}$ , and therefore the channel length dependence of their extracted  $R_g$  follows the trend of  $R_{\text{gpoly}}$  for the devices studied in this paper. In addition, the extracted  $R_g$  values are about the same for devices with the same dimension fabricated in RVT and LVT processes. In Fig. 6, if we extrapolate the extracted  $R_{\rm dso}$  down to L = 0 nm, we can extract the resistance  $R_{\rm LDD}$ in the LDD region at the source (or drain) side, which gives 1.9  $\Omega$  and 3.5  $\Omega$  for n- and p-type FETs, respectively. Higher channel resistance  $R_{dso}$  also results in lower critical frequency  $f_c$  as shown in Fig. 7 and therefore reduces the accuracy of the extracted  $R_g$ . This can be observed from the lower than expected  $R_g$  extracted using  $L = 0.24 \ \mu m$ , 0.36  $\mu m$ , and 0.5  $\mu$ m p-type HVT FETs shown in Fig. 5.

For future technology node using high- $\kappa$  metal gate, the gate-stack combination is more complex than Poly/SiON's and therefore results in higher gate resistance  $R_{\text{gmetal}}$  than  $R_{\text{gpoly}}$ . However, this is beneficial to our extraction algorithm to avoid the NQS effect and enhance the extraction accuracy when using the same device geometry.

#### **IV. CONCLUSION**

An improved *z*-parameter based approach to extract the gate resistance at low frequencies is presented. This improved extraction method demonstrated its statistical stability and robustness compared with all of the published methods in the literature. Its statistical robustness and stability are particularly important for the future technology nodes with smaller feature size and larger process variations. Finally, we observed that for a given device geometry, n-type FETs fabricated in the RVT or LVT processes are more suitable for the gate resistance extraction because of their relatively lower channel resistance compared with p-type FETs or the HVT processes.

#### REFERENCES

- [1] Z. Wang, P.-Y. Chiang, P. Nazari, C.-C. Wang, Z. Chen, and P. Heydari, "A 210 GHz fully integrated differential transceiver with fundamental-frequency VCO in 32 nm SOI CMOS," in *IEEE Int. Solid-State Circuit Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2013, pp. 136–137.

- [2] (2012). International Technology Roadmap for Semiconductors (ITRS).

[Online]. Available: http://www.itrs.net/reports.html

- [3] C.-H. Chen, M. J. Deen, Y. Cheng, and M. Matloubian, "Extraction of the induced gate noise, channel thermal noise and their correlation in sub-micron MOSFETs from RF noise measurements," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2884–2892, Dec. 2001.

- [4] C.-H. Chen, R. Lee, G. Tan, D. C. Chen, P. Lei, and C.-S. Yeh, "Equivalent sheet resistance of intrinsic noise in sub-100-nm MOSFETs," *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2215–2220, Aug. 2012.

- [5] W. S. Kwan, C.-H. Chen, and M. J. Deen, "Hot-carrier effects on radio frequency noise characteristics of LDD *n*-type metal–oxide–semiconductor field effect transistors," *J. Vac. Sci. Technol. A*, vol. 18, no. 2, pp. 765–769, Mar. 2000.

- [6] S. Naseh, M. J. Deen, and C.-H. Chen, "Effects of hot-carrier stress on the performance of CMOS low-noise amplifiers," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 3, pp. 501–508, Sep. 2005.

- [7] S. Naseh, M. J. Deen, and C.-H. Chen, "Hot-carrier reliability of submicron NMOSFETs and integrated NMOS low noise amplifiers," *Microelectron. Rel.*, vol. 46, nos. 2–4, pp. 201–212, Feb. 2006.

- [8] C.-H. Chen and M. J. Deen, "Channel noise modeling of deep submicron MOSFETs," *IEEE Trans. Electron Device*, vol. 49, no. 8, pp. 1484–1487, Aug. 2002.

- [9] C.-H. Chen, F. Li, and Y. Cheng, "MOSFET drain and induced-gate noise modeling and experimental verification for RF IC design," in *Proc. Int. Conf. Microelectron. Test Struct. (ICMTS)*, Awaji Island, Japan, Mar. 2004, pp. 51–56.

- [10] M. J. Deen, C.-H. Chen, S. Asgaran, G. A. Rezvani, J. Tao, and Y. Kiyota, "High-frequency noise of modern MOSFETs: Compact modeling and measurement issues," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2062–2081, Sep. 2006.

- [11] S. Lee, H. K. Yu, C. S. Kim, J. G. Koo, and K. S. Nam, "A novel approach to extracting small-signal model parameters of silicon MOSFET's," *IEEE Microw. Guided Wave Lett.*, vol. 7, no. 3, pp. 75–77, May 1997.

- [12] X. Jin et al., "An effective gate resistance model for CMOS RF and noise modeling," in IEDM Tech Dig., Dec. 1998, pp. 961–964.

- [13] S. H.-M. Jen, C. C. Enz, D. R. Pehlke, M. Schröter, and B. J. Sheu, "Accurate modeling and parameter extraction for MOS transistors valid up to 10 GHz," *IEEE Trans. Electron Devices*, vol. 46, no. 11, pp. 2217–2227, Nov. 1999.

- [14] C. C. Enz and Y. Cheng, "MOS transistor modeling for RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 186–201, Feb. 2000.

- [15] Y. Cheng and M. Matloubian, "On the high-frequency characteristics of substrate resistance in RF MOSFETs," *IEEE Electron Device Lett.*, vol. 21, no. 12, pp. 604–606, Dec. 2000.

- [16] Y. Cheng and M. Matloubian, "High frequency characterization of gate resistance in RF MOSFETs," *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 98–100, Feb. 2001.

- [17] S. H. Lee, C. S. Kim, and H. K. Yu, "A small-signal RF model and its parameter extraction for substrate effects in RF MOSFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 7, pp. 1374–1379, Jul. 2001.

- [18] R. Torres-Torres, R. S. Murphy-Arteaga, and S. Decoutere, "MOSFET gate resistance determination," *Electron. Lett.*, vol. 39, no. 2, pp. 248–250, Jan. 2003.

- [19] Y. Cheng, M. J. Deen, and C.-H. Chen, "MOSFET modeling for RF IC design," *IEEE Trans. Electron Devices*, vol. 52, no. 2, pp. 1286–1303, Jul. 2005.

- [20] M. Kang, I. M. Kang, Y. H. Jung, and H. Shin, "Separate extraction of gate resistance components in RF MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 6, pp. 1459–1463, Jun. 2007.

- [21] K.-L. Yeh and J.-C. Guo, "Narrow-width effect on high-frequency performance and RF noise of sub-40-nm multifinger nMOSFETs and pMOSFETs," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 109–116, Jan. 2013.

- [22] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor, 3rd ed. Oxford, U.K.: Oxford Univ. Press, 2011.

- [23] D. M. M.-P. Schreurs, Y. Baeyens, B. K. J. C. Nauwelaers, W. D. Raedt, M. V. Hove, and M. V. Rossum, "S-parameter measurement based quasistatic large-signal cold HEMT model for resistive mixer design," *Int. J. Microw. Millim.-Wave Comput.-Aided Eng.*, vol. 6, no. 4, pp. 250–258, Jul. 1996.

- [24] K. J. Kuhn et al., "Process technology variation," IEEE Trans. Electron Devices, vol. 58, no. 8, pp. 2197–2208, Aug. 2011.

Xuesong Chen received the B.S. degree in applied physics from the University of Science and Technology of China, Hefei, China, in 2012. He is currently pursuing the Ph.D. degree in electrical and computer engineering with McMaster University, Hamilton, ON, Canada.

His current research interests include the noise modeling of nanoscale MOSFETs for low-power analog/RF ICs.

**Mu Kai Tsai** received the B.S. and M.S. degrees in electrical engineering from National Central University, Jhongli, Taiwan, in 1998 and 2000, respectively.

He joined United Microelectronics Corporation, Hsinchu, Taiwan, in 2002, where he is involved in device characterization and modeling of logic and RF CMOS devices.

Chih-Hung Chen (S'95–M'03–SM'08) is an Associate Professor with the Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada. His current research interests include the noise characterization and modeling of nanoscale MOSFETs and designs of low-noise RF ICs for wireless applications.

**David C. Chen** (SM'93) received the Ph.D. degree in electrical engineering from the University of Southern California, Los Angeles, CA, USA, in 1997.

He has been with the United Microelectronics Corporation, Hsinchu, Taiwan, since 1997. His current research interests include the advanced device modeling and RF characterization.

**Ryan Lee** received the M.S. degree in physics from National Cheng Kung University, Tainan, Taiwan, in 1992, and the M.E. degree in material engineering from the University of Southern California, Los Angeles, CA, USA, in 1996.

He has been with the ATD Modeling Division, United Microelectronics Corporation, Hsinchu, Taiwan, since 1997. His current research interests include the high-frequency device modeling and modeling methodology development.