# Fabrication and characteristics of flexible normally-off AlGaN/GaN HEMTs

Cite as: AIP Advances **10**, 105317 (2020); https://doi.org/10.1063/5.0025587 Submitted: 17 August 2020 • Accepted: 24 September 2020 • Published Online: 08 October 2020

Runze Lin, Desheng Zhao, ២ Guohao Yu, et al.

### ARTICLES YOU MAY BE INTERESTED IN

**Tri-gate GaN junction HEMT**

Applied Physics Letters 117, 143506 (2020); https://doi.org/10.1063/5.0025351

Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures Journal of Applied Physics **85**, 3222 (1999); https://doi.org/10.1063/1.369664

Modulation of the two-dimensional electron gas channel in flexible AlGaN/GaN highelectron-mobility transistors by mechanical bending Applied Physics Letters **116**, 123501 (2020); https://doi.org/10.1063/1.5142546

**AIP Advances**

Mathematical Physics Collection

READ NOW

AIP Advances **10**, 105317 (2020); https://doi.org/10.1063/5.0025587 © 2020 Author(s). 10, 105317

## Fabrication and characteristics of flexible normally-off AlGaN/GaN HEMTs

Cite as: AIP Advances 10, 105317 (2020); doi: 10.1063/5.0025587 Submitted: 17 August 2020 • Accepted: 24 September 2020 • Published Online: 8 October 2020

Runze Lin,<sup>1</sup> Desheng Zhao,<sup>1,2</sup> Guohao Yu,<sup>2</sup> (D) Xiaoyan Liu,<sup>1</sup> (D) Dongdong Wu,<sup>2</sup> Erdan Gu,<sup>3</sup> Xugao Cui,<sup>1</sup> Ran Liu,<sup>1</sup> Baoshun Zhang,<sup>2</sup> (D) and Pengfei Tian<sup>1,a)</sup> (D)

#### AFFILIATIONS

<sup>1</sup>Institute for Electric Light Sources, School of Information Science and Technology, and Academy of Engineering and Technology, Fudan University, Shanghai 200433, China

<sup>2</sup>Nano Fabrication Facility, Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Jiangsu 215123, China <sup>3</sup>Institute of Photonics, University of Strathclyde, Glasgow G1 1RD, United Kingdom

<sup>a)</sup>Author to whom correspondence should be addressed: pftian@fudan.edu.cn

#### ABSTRACT

In this paper, we present a method for removing a high electron mobility transistor (HEMT) silicon substrate using mechanical grinding and deep silicon etching technology and successfully transferred the epitaxial wafer to a PET substrate to achieve the flexible normally-off HEMT. By testing the output characteristics and transfer characteristics of the Si-substrate HEMT and PET-substrate HEMT, we have demonstrated that the PET-substrate HEMT has excellent performance and successfully achieved the mechanical flexibility. Furthermore, we analyzed the physical mechanisms of the change in PET-substrate and Si-substrate HEMT characteristics, as well as flexible HEMT performance under bent and flattened states. The flexible HEMT array demonstrates significant potential in integration with other flexible devices, such as GaN-based micro-LED arrays.

© 2020 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0025587

#### I. INTRODUCTION

In recent years, with the rapid development of electronic technology, flexible electronics, as a branch of it, has attracted more and more attention.<sup>1</sup> In addition to the electrical performance of traditional electronic systems, it also has good mechanical flexibility, which is very suitable for complex working environments.<sup>2</sup> Therefore, whether in the commercial or military applications, the demand for flexible electronic devices is constantly increasing, including flexible displays,<sup>3</sup> flexible lightings,<sup>4</sup> and flexible solar cells.<sup>5</sup> As a critical part of flexible electronic devices, flexible microelectronic devices have also been extensively studied. Among traditional electronic devices, the GaN high electron mobility transistor (HEMT), due to its excellent properties such as high electron mobility, high breakdown electric field, and temperature stability, becomes one of the mainstream research fields of semiconductors.<sup>6-9</sup> Because of its superior high-power and high-frequency characteristics than traditional Si-based and GaAs-based electronic devices, it is the most potential candidate in the fifth-generation wireless communication

(5G).<sup>10</sup> However, because the GaN HEMT is usually grown by metal organic chemical vapor deposition (MOCVD), it can only be grown on inorganic substrates, such as Si, sapphire, and SiC, which is difficult to meet the needs of flexible microelectronic devices.<sup>11–13</sup> In order to fabricate flexible HEMT devices, the technology of substrate transfer is mainly used to realize the bonding of HEMT epitaxial wafers and flexible substrates.<sup>14</sup> Recent research shows that the flexible HEMT devices obtained by the substrate transfer technology can fully realize the combination of mechanical flexibility and excellent electrical performance.<sup>15-19</sup> However, most of these studies only analyze the electrical characteristics of normally-on HEMT devices under different external strain conditions. Considering that the structure of normally-off HEMT devices is more complicated, the transfer process will have a larger effect, so it is necessary to study the electrical performance changes in the flexible normally-off HEMT devices.

In this paper, we developed mechanical grinding and deep silicon etching technology to remove the Si substrate from the normally-off HEMT device and successfully used the bonding technology to transfer the epitaxial wafer without a substrate to a PET substrate. Through detailed measurement of the electrical properties of the device before and after the transfer process, the output characteristics, leakage current characteristics, and corresponding physical mechanisms of the flexible normally-off HEMT device were analyzed. Finally, we tested the performance of the flexible device in the bent state and successfully demonstrated that it has the characteristics of mechanical flexibility while still maintaining excellent electrical characteristics. We believe that the relatively simple transfer steps, feasible process conditions, and mature materials ensure the reproducibility of the experiment, which can be used for large-scale flexible HEMT fabrication in the future.

#### **II. EXPERIMENTAL DETAILS**

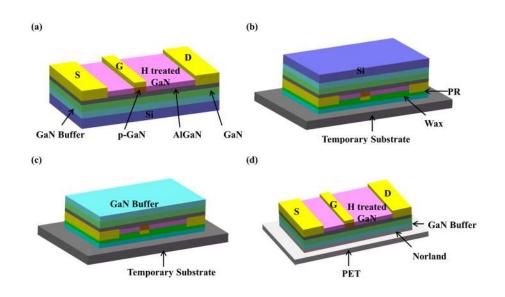

The epitaxial layers were grown on a 2-in Si (111) substrate by MOCVD. After the preparation of the epitaxial wafer, the normallyoff p-GaN/AlGaN/GaN HEMT on a Si substrate was achieved by hydrogen plasma treatment [Fig. 1(a)]. The main structure of the epitaxial wafer includes a 1  $\mu$ m GaN buffer layer, a 100 nm GaN channel layer, a 1 nm AlN spacer layer, an 18 nm undoped Al<sub>0.2</sub>Ga<sub>0.8</sub>N barrier layer, and a 70 nm *p*-GaN cap layer. The gateto-drain spacing (Lgd) and gate-to-source spacing (Lgs) of the device are 10  $\mu$ m and 4  $\mu$ m, respectively. Additional details can be found in Ref. 20. The device surface was protected by a photoresist (PR) layer and bonded to a temporary substrate with wax [Fig. 1(b)]. The Si substrate was thinned to a thickness of about 100  $\mu$ m using mechanical grinding and removed completely by deep silicon etching [Fig. 1(c)]. Based on the inductively coupled plasma (ICP) etching system, the remaining Si substrate was etched by using a mixed gas of SF<sub>6</sub> (90 SCCM) and Ar (10 SCCM). The ICP power and RF power were 1500 W and 50 W, respectively. The back side of the device was coated with Norland Optical Adhesive 63 and bonded on PET by ultra-violet curing. Finally, the temporary substrate was removed [Fig. 1(d)], forming a flexible GaN HEMT on a PET substrate. In order to verify the performance of the flexible substrate

HEMT, we tested the electrical characteristics of the device using a high-precision Keithley SourceMeter (2614B) and a matching probe platform.

#### **III. RESULTS AND DISCUSSION**

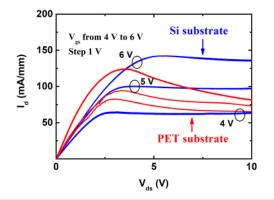

The output characteristic curves of the AlGaN/GaN HEMT on the PET substrates are presented in Fig. 2. The drain-source voltage V<sub>ds</sub> is varied from 0 V to 10 V with a series of gate-source voltage Vgs (from 4 V to 6 V). The output characteristic curves of the Sisubstrate HEMT under the same measurement condition are also plotted in Fig. 2. It can be seen that after transferring the HEMT to the PET substrate, the maximum current of the device dropped. At  $V_{gs} = 6$  V, the maximum current of the PET-substrate HEMT is 123.9 mA/mm, which is 12.9% lower than the 142.2 mA/mm maximum current of the Si-substrate device. Although the maximum operating current of the device is only slightly decreased, in the saturation region of output characteristics, Id of the PET-substrate HEMT decreases significantly with the rise in the drain-source voltage V<sub>ds</sub>, which is known as "current collapse."<sup>21</sup> When the gate is applied with a voltage of 6 V,  $I_d$  ( $V_{ds}$  = 10 V) is only 81.7 mA/mm, which is 42.5% lower than the maximum current. Such a current collapse phenomenon is mainly caused by the self-heating effect of the device.<sup>22</sup> The thermal conductivity of the PET substrate is only 0.15 W/(m K), which is much lower than the 149 W/(m K) thermal conductivity of the Si substrate. The heat generated within the device cannot be effectively spread through the PET substrate. When a high drain-source voltage is applied to the device, the device will quickly deviate from the optimum operating conditions, eventually causing a drop in I<sub>d</sub> in the saturation region.

Unlike the change in the maximum current, the on-resistance  $R_{on}$  of the PET-substrate HEMT shows a small decrease compared to the Si-substrate device. The  $R_{on}$  of the Si-substrate HEMT is 24.07  $\Omega$  mm at  $V_{gs} = 6$  V. However, at the same measurement condition, the  $R_{on}$  of the PET-substrate HEMT drops to 17.16  $\Omega$  mm. Similar phenomena have been reported in previous work.<sup>22</sup> It may be caused by a change in the mechanical stress of the epitaxial layer,

**FIG. 1.** Process of the Si substratetransfer technology. (a) Normally-off *p*-GaN/AIGaN/GaN HEMT on a Si substrate. (b) The temporary substrate bonding to the device surface. (c) Removal of the Si substrate. (d) PETsubstrate HEMT after transferring.

FIG. 2. I–V characteristics of different substrate HEMT devices.  $V_{gs}$  from 4 V to 6 V, step = 1 V.

and thus, the 2DEG density of PET-substrate HEMT increases due to the device transfer process.

Besides the output characteristics, the measurement of transfer characteristics was also carried out. The result is shown in Fig. 3(a). The inset shows  $V_{gs}$ -I<sub>d</sub> and  $V_{gs}$ -I<sub>g</sub> curves in semi-logarithmic coordinates. The drain–source voltage  $V_{ds}$  was fixed at 10 V, and the gate voltage  $V_{gs}$  varied from -3 V to +6 V. Figure 3(b) shows

**FIG. 3.** (a) Comparison of transfer characteristics of different substrate HEMT devices.  $V_{ds} = 10$  V. Inset: transfer characteristic and gate current curves in semi-logarithmic coordinates. (b) Transconductance curves of HEMTs on different substrates.

the transconductance curves corresponding to different substrate HEMTs. It can be seen that the maximum transconductance of the PET-substrate HEMT and Si-substrate HEMT is 32.2 mS/mm (V<sub>gs</sub> = 2.34 V) and 39.3 mS/mm (V<sub>gs</sub> = 6 V), respectively. When V<sub>gs</sub> = 6 V, the PET-substrate device's transconductance g<sub>m</sub> is reduced to 7.5 mS/mm. The PET-substrate HEMT can control the drain–source current I<sub>d</sub> more effectively when the gate voltage is low. However, as the gate voltage rises, the self-heating effect caused by the poor thermal conductivity of the substrate material causes degradation of the device performance, and the transconductance rapidly decreases.<sup>19</sup>

Comparing the devices before and after the transfer process, it can be seen that the leakage current of the device also has a conspicuous change. When the HEMT is turned off, there are usually three types of leakage channels: gate leakage, substrate leakage, and buffer-layer leakage.<sup>23</sup> Due to the electrical insulation of the PET substrate, the substrate leakage is not considered. As shown in the inset of Fig. 3(a), at  $V_{ds} = 10 \text{ V}$ ,  $V_{gs} = -3 \text{ V}$ , the gate current  $I_g$  of the PET-substrate HEMT is  $2 \times 10^{-4}$  mA/mm, which is much higher than  $1.5 \times 10^{-5}$  mA/mm of the drain leakage current I<sub>d</sub>. So, when the PET-substrate HEMT is turned off, the gate leakage current is the main leakage path. In the Si-substrate HEMT, the gate leakage current of the device is smaller than the drain leakage current under the condition of -3 V gate voltage. Obviously, unlike the PET-substrate HEMT, the drain leakage current is the most important factor in the leakage mechanism of the Si-substrate HEMT. This phenomenon may be due to the damage to the surface of the device's GaN cap layer during the temporary bonding process, which increases the surface leakage current at the gate of the device. As the gate voltage gradually rises from -3 V to 0 V, the gate leakage current I<sub>g</sub> decreases rapidly, but the drain leakage current Id does not change significantly. The drain leakage current is mainly composed of two parts: drain-gate leakage current  $I_{\rm dg}$  and drain-source leakage current Ids. Assuming the drain-gate leakage current Idg plays a leading role in the drain leakage current  $I_d$ , then as  $V_{gs}$  changes from -3 Vto 0 V, the change trend of I<sub>d</sub> should be consistent with I<sub>g</sub>. However, the value of I<sub>d</sub> remains unchanged. Therefore, we consider that the drain leakage current is basically independent of the gate leakage, indicating that the drain leakage current of the device is mainly due to the buffer-layer leakage.

In addition, when the gate voltage is -3 V, the drain leakage of the PET-substrate device rises from  $3 \times 10^{-6}$  mA/mm to  $1.5 \times 10^{-5}$  mA/mm compared to the Si-substrate HEMT. The main source of this leakage is the trap state in the buffer layer.<sup>23</sup> Therefore, the increase in drain leakage reflects an increase in the density of the trap state of the device buffer layer. The increased trap state in the buffer layer may be caused by additional dislocations introduced by mechanical grinding and dry etching when the substrate was removed. In fact, mechanical grinding may damage the quality of the epitaxial wafer more severely than deep silicon etching. The thickness of the substrate thinned by the mechanical grinding can be reduced, and then, deep silicon etching is directly used to remove the remaining Si substrate so as to obtain high-quality epitaxial wafers with lower trap density.

Regarding the gate threshold voltage V<sub>th</sub> of the device, the gate threshold voltage is defined as the corresponding gate voltage value when the drain–source current I<sub>d</sub> reaches 10  $\mu$ A/mm.<sup>24</sup> Under the condition that the drain–source voltage is 10 V, the V<sub>th</sub> of the

Si-substrate and the PET-substrate HEMT is 0.76 V and 0.98 V, respectively. The threshold voltage of the device after transfer only changes slightly, which means that after the transfer process, the PET-substrate HEMT still maintains the enhancement-mode device.

To verify the effect of the self-heating effect on the PETsubstrate device, pulse measurements were performed. The drain contact is subjected to pulses with 50 ms duration. The pulse width is 1 ms. The measurement range of  $V_{ds}$  is from 0 V to 10 V.  $V_{gs}$  is fixed at 4 V, 5 V, and 6 V. The I-V characteristics of the Si-substrate and the PET-substrate HEMT were measured under three different gate voltage conditions. The results are shown in Fig. 4. It can be seen from Fig. 4(a) that under the pulse condition, the I-V characteristics of the PET-substrate device have undergone significant changes. The current collapse effect caused by the rise in the drain-source voltage in the saturation region is effectively suppressed. At a gate voltage of 6 V, the drain-source current Id at Vds of 10 V rises from the original 81.7 mA/mm to 153.2 mA/mm. The maximum operating current has also increased by 23.6%, from 123.9 mA/mm to 153.2 mA/mm. The change in device performance is mainly due to the suppression of self-heating effects by the pulse input. The pulse used in this experiment is 1 ms, the period is 50 ms, and the duty cycle is only 2%, so the device does not accumulate heat during the test and thus maintains the optimal operating conditions. For comparison, the Si-substrate HEMT was also tested under the same conditions, and the results are shown in Fig. 4(b). There was no significant change in device performance, and only the maximum current increased from 142.2 mA/mm to 158.4 mA/mm, which was only 11.4% higher. It can be seen that when the thermal conductivity of the substrate rises, the self-heating effect is significantly suppressed. Therefore, new materials with excellent properties such as flexibility and good thermal conductivity can be selected. For example, flexible metals (including Al and AuSn) can be used as substrate materials for flexible HEMTs.<sup>25,26</sup> In addition, a thermally conductive layer (such as graphene, which is currently very popular<sup>27</sup>) can also be added between the flexible plastic substrate and the epitaxial wafer to enhance the heat dissipation performance of the device.

Finally, in order to verify the feasibility of the device as a flexible microelectronic device, the output characteristics and transfer characteristics of the device were tested at the flattened and bent states, respectively. Figure 5 shows the curves of the measurement result. The bent state was achieved by adhering the flexible HEMT to a fixed radius of curvature carrier with a curve radius of R = 12.7 mm, as shown in the inset of Fig. 5(a). Figure 5(a) shows the comparison of the output characteristics of the device at different states. The gate voltage is fixed at 6 V, and the drain–source voltage is scanned from 0 V to 20 V. It can be seen that at the bent state, the I<sub>d</sub> of the PET-substrate HEMT is improved compared to the flattened state. At V<sub>ds</sub> = 20 V, I<sub>d</sub> increased from 56.35 mA/mm to 60.80 mA/mm. Such a phenomenon can also be confirmed from the transfer characteristic curve. In Fig. 5(b), at the same gate voltages, the I<sub>d</sub> of the bent state device is higher than that of the flattened device. In

FIG. 4. DC- and pulse-mode drain I–V characteristics of HEMT devices (a) on a PET substrate (b) and a Si substrate.  $V_{gs}$  from 4 V to 6 V; step = 1 V.

**FIG. 5.** I–V curves in flattened and bent states. (a) Output characteristics;  $V_{gs} = 6$  V. Inset: HEMT at the bent state with the radius of curvature R = 12.7 mm. (b) Transfer characteristic curves;  $V_{ds} = 10$  V. Inset: Transfer characteristic curves in semi-logarithmic coordinates.

the off state, taking the gate voltage  $V_{gs}=-3$  V as an example, the reverse leakage current of the bent state device is  $4\times 10^{-5}$  mA/mm, which is  $1.5\times 10^{-5}$  mA/mm at the flattened state. The leakage current increased by 167%. This is mainly due to the fact that the external stress increases the piezoelectric polarization effect inside the device due to the increase in the two-dimensional electron gas concentration at the bent state.^{28}

When the device is under the stress state and the external force direction with the piezoelectric polarization effect, the polarization effect inside the device will be enhanced, and the bottom of the conduction band at the heterojunction is closer to the Fermi level. The electron concentration of the channel  $\eta_a$  can be estimated by the following formula:<sup>28</sup>

$$\eta_a \propto \varepsilon = \frac{a_B - a_L}{a_B} + \frac{\Upsilon}{R},\tag{1}$$

where  $\varepsilon$  is the introduced strain in 2DEG of the HEMT;  $a_B$  and  $a_L$  refer to the lattice constants of the buffer layer and the barrier layer material, respectively;  $\Upsilon$  is the distance between the heterojunction and the neutral plane; and R is the radius of curvature. When the structure and material of the device are determined, the smaller the radius of curvature of the device, the larger the introduced strain  $\varepsilon$ , so the higher the carrier concentration of 2DEG and the current of the device.

In addition, by defining the gate voltage at  $I_d = 10 \ \mu$ A/mm as the threshold voltage V<sub>th</sub>, the V<sub>th</sub> at the bent state and the flattened state can be obtained, which are 0.89 V and 0.98 V, respectively. It can be seen that at the bent state, the threshold voltage of the device drops slightly. This drop in threshold voltage is also caused by an increase in the polarization effect of the device.<sup>28</sup>

When the device is at the bent state, an external force causes an increase in piezoelectric polarization inside the device, which, in turn, causes the polarization charge density to rise. As a result, the threshold voltage of the device decreases. This means that the PETsubstrate HEMT can be used as a flexible microelectronic device without degrading performance.

#### **IV. CONCLUSIONS**

Using mechanical grinding and deep silicon etching technology, we successfully transferred the normally-off AlGaN/GaN HEMTs on the Si substrate to the PET substrate. The performance of the PET-substrate HEMT was demonstrated by the measurement of I–V characteristics, and the degradation was analyzed compared with the Si-substrate HEMT. Under the DC measurement condition, negative differential resistance was observed in the output characteristic curves, which did not exist in the pulsed measurement. The selfheating effect caused by the poor thermal conductivity of the PET substrate leads to such a phenomenon. Measurement on the effects of mechanical flexibility on device performance was also carried out. Based on such transfer technology, large-area flexible HEMT arrays and further device integration with other semiconductor devices are expected in the future work.

#### AUTHORS' CONTRIBUTIONS

R.L. and D.Z. contributed equally to this work.

#### ACKNOWLEDGMENTS

This work was supported by the National Natural Science Foundation of China (NSFC) (Grant Nos. 61974031 and 61705041), the Fudan University-CIOMP Joint Fund, the Shanghai Technical Standard Program (Grant No. 18DZ2206000), and the Science and Technology on Monolithic Integrated Circuits and Modules Laboratory in Nanjing Electronic Devices Institute (Grant No. 6142803180407).

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

<sup>1</sup>Y. Sun and J. A. Rogers, Adv. Mater. **19**, 1897 (2007).

<sup>2</sup> A. Nathan, A. Ahnood, M. T. Cole, S. Lee, Y. Suzuki, P. Hiralal, F. Bonaccorso, T. Hasan, L. Garcia-Gancedo, A. Dyadyusha, S. Haque, P. Andrew, S. Hofmann, J. Moultrie, D. Chu, A. J. Flewitt, A. C. Ferrari, M. J. Kelly, J. Robertson, G. A. J. Amaratunga, and W. I. Milne, Proc. IEEE 100, 1486 (2012).

<sup>3</sup>L. Zhou, A. Wanga, S.-C. Wu, J. Sun, S. Park, and T. N. Jackson, Appl. Phys. Lett. 88, 083502 (2006).

<sup>4</sup>Y. Altintas, S. Genc, M. Y. Talpur, and E. Mutlugun, Nanotechnology **27**, 295604 (2016).

<sup>5</sup>C. Roldán-Carmona, O. Malinkiewicz, A. Soriano, G. Mínguez Espallargas, A. Garcia, P. Reinecke, T. Kroyer, M. I. Dar, M. K. Nazeeruddin, and H. J. Bolink, Energy Environ. Sci. 7, 994 (2014).

<sup>6</sup>U. K. Mishra, P. Parikh, and Y.-F. Wu, Proc. IEEE **90**, 1022 (2002).

<sup>7</sup> W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, T. Ogura, and H. Ohashi, IEEE Trans. Electron Devices **50**, 2528 (2003).

<sup>8</sup>S. L. Selvaraj, T. Suzue, and T. Egawa, IEEE Electron Device Lett. **30**, 587 (2009).

<sup>9</sup>J. A. Del Alamo and J. Joh, Microelectron. Reliab. **49**, 1200 (2009).

<sup>10</sup>N. R. Glavin, K. D. Chabak, E. R. Heller, E. A. Moore, T. A. Prusnick, B. Maruyama, D. E. Walker, D. L. Dorsey, Q. Paduano, and M. Snure, Adv. Mater. 29, 1701838 (2017).

<sup>11</sup>A. Minko, V. Hoel, E. Morvan, B. Grimbert, A. Soltani, E. Delos, D. Ducatteau, C. Gaquiere, D. Theron, J. C. De Jaeger, H. Lahreche, L. Wedzikowski, R. Langer, P. Bove, and P. Bove, <u>IEEE Electron Device Lett</u>. **25**, 453 (2004).

<sup>12</sup>X. L. Wang, C. M. Wang, G. X. Hu, J. X. Wang, T. S. Chen, G. Jiao, J. P. Li, Y. P. Zeng, and J. M. Li, Solid-State Electron. 49, 1387 (2005).

<sup>13</sup> V. Kumar, A. Kuliev, T. Tanaka, Y. Otoki, and I. Adesida, Electron. Lett. 39, 1758 (2003).

<sup>14</sup>K. J. Lee, M. A. Meitl, J.-H. Ahn, J. A. Rogers, R. G. Nuzzo, V. Kumar, and I. Adesida, J. Appl. Phys. **100**, 124507 (2006).

<sup>15</sup>S. Mhedhbi, M. Lesecq, P. Altuntas, N. Defrance, E. Okada, Y. Cordier, B. Damilano, G. Tabares-Jimenez, A. Ebongue, and V. Hoel, <u>IEEE Electron Device Lett.</u> 37, 553 (2016).

<sup>16</sup>S. Mhedhbi, M. Lesecq, P. Altuntas, N. Defrance, Y. Cordier, B. Damilano, G. Tabares Jimenéz, A. Ebongue, and V. Hoel, Phys. Status Solidi A **214**, 1600484 (2017).

<sup>17</sup>N. Defrance, F. Lecourt, Y. Douvry, M. Lesecq, V. Hoel, A. Lecavelier Des Etangs-Levallois, Y. Cordier, A. Ebongue, and J. C. De Jaeger, <u>IEEE Trans.</u> Electron Devices **60**, 1054 (2013).

<sup>18</sup>M. Lesecq, V. Hoel, A. L. Des Etangs-Levallois, E. Pichonat, Y. Douvry, and J. C. De Jaeger, IEEE Electron Device Lett. **32**, 143 (2011).

<sup>19</sup>T.-H. Chang, K. Xiong, S. H. Park, H. Mi, H. Zhang, S. Mikael, Y. Jung, J. Han, and Z. Q. Ma, in *IEEE MTT-S International Microwave Symposium* (IEEE, 2015).

<sup>20</sup>R. Hao, K. Fu, G. Yu, W. Li, J. Yuan, L. Song, Z. Zhang, S. Sun, X. Li, Y. Cai, X. Zhang, and B. Zhang, Appl. Phys. Lett. **109**, 152106 (2016).

<sup>21</sup> S. C. Binari, K. Ikossi, J. A. Roussos, W. Kruppa, D. Park, H. B. Dietrich, D. D. Koleske, A. E. Wickenden, and R. L. Henry, IEEE Trans. Electron Devices 48, 465 (2001).

<sup>22</sup>B. Lu and T. Palacios, IEEE Electron Device Lett. **31**, 951 (2010).

<sup>23</sup>W. Saito, T. Suwa, T. Uchihara, T. Naka, and T. Kobayashi, Microelectron. Reliab. 55, 1682 (2015).

<sup>24</sup>R. Hao, N. Xu, G. Yu, L. Song, F. Chen, J. Zhao, X. Deng, X. Li, K. Cheng, K. Fu, Y. Cai, X. Zhang, and B. Zhang, IEEE Trans. Electron Devices **65**, 1314 (2018).

<sup>25</sup>T.-I. Kim, Y. H. Jung, J. Song, D. Kim, Y. Li, H.-S. Kim, I.-S. Song, J. J. Wierer,

H. A. Pao, Y. Huang, and J. A. Rogers, Small 8, 1643 (2012).

<sup>26</sup>P. Tian, J. J. D. Mckendry, E. Gu, Z. Chen, Y. Sun, G. Zhang, M. D. Dawson, and R. Liu, Opt. Express 24, 699 (2016).

<sup>27</sup>J. Ding, H. Zhao, Q. Wang, H. Dou, H. Chen, and H. Yu, Nanoscale 9, 16871 (2017).

<sup>28</sup>S. Shervin, S.-H. Kim, M. Asadirad, S. Ravipati, K.-H. Lee, K. Bulashevich, and J.-H. Ryou, Appl. Phys. Lett. 107, 193504 (2015).