PACS 73.40.Qv

# Fabrication and characterization of a 0.14 $\mu m$ CMOS device using ATHENA and ATLAS simulators

## Ibrahim Ahmad<sup>1</sup>, Yeap Kim Ho<sup>2</sup>, Burhanuddin Yeop Majlis<sup>1</sup>

<sup>1</sup>Dept. of Electrical, Electronic and Systems Engineering, Faculty of Engineering

43600 University Kebangsaan Malaysia, MALAYSIA

Phone: 6-03-89296309; fax: 6-03-89296146

E-mail: ibrahim@vlsi.eng.ukm.my; burhan@eng.ukm.my

<sup>2</sup>Dept. of Physical Sciences, Electrical and Electronics, Faculty of Engineering and Science

53300 University Tunku Abdul Rahman, MALAYSIA

Phone: 6-03-41079802; fax: 6-03-41079803

E-mail: yeapkh@mail.utar.edu.my

**Abstract.** A 0.14 μm CMOS transistor with two levels of interconnection was designed and simulated to investigate its functionality and characteristics. ATHENA and ATLAS simulators were used to simulate the fabrication process and to validate the electrical characteristics, respectively. A scaling factor of 0.93 was applied to a 0.13 μm CMOS. The parameters being scaled are the effective channel length, the density of ion implantation for threshold voltage ( $V_{\rm th}$ ) adjustment, and the gate oxide thickness. In order to minimize high field effects, the following additional techniques were implemented: shallow trench isolation, sidewall spacer deposition, silicide formation, lightly doped drain implantation, and retrograde well implantation. The results show that drain current ( $I_D$ ) increases as the levels of interconnection increases. The important parameters for NMOS and PMOS were measured. For NMOS, the gate length ( $L_g$ ) is 0.133 μm,  $V_{\rm th}$  is 0.343138 V, and the gate oxide thickness ( $T_{\rm ox}$ ) is 3.46138 nm. For PMOS,  $L_g$  is 0.133 μm,  $V_{\rm th}$  is -0.378108 V, and  $T_{\rm ox}$  is 3.46167 nm. These parameters were validated and the device was proven to be operational.

**Keywords:** gate length, threshold voltage, gate oxide thickness.

Manuscript received 19.01.06; accepted for publication 29.03.06.

## 1. Introduction

The size of a CMOS transistor has been shrinking dramatically in less than 40 years time. Transistors with the size of 50  $\mu$ m in the 1960s have shrunk to less than 0.18  $\mu$ m in 2000s [1].

In this work, a  $0.14 \,\mu m$  CMOS was simulated and studied. The fabrication process was simulated using the ATHENA module from the Silvaco Virtual Wafer Fab (VWF) tools; whereas, the electrical characteristics were validated via the ATLAS module.

The 0.14  $\mu$ m CMOS was scaled from an existing 0.13  $\mu$ m CMOS [3]. Constant field scaling with a scaling factor of 0.93 was applied to the following parameters: the effective channel length ( $L_g$ ), gate oxide thickness ( $T_{\rm ox}$ ), and threshold voltage ( $V_{\rm th}$ ) adjustment implantation [5]. As the channel length falls within the

submicron regimes, the performance of the device may be susceptible to high field effects. Thus, in order to ensure proper operation, the following techniques have been implemented to minimize high field effects: shallow trench isolation (STI), sidewall spacer deposition, silicide formation, lightly doped drain (LDD) implantation, and retrograde well implantation [5].

## 2. Simulation process

In order to simplify the simulation process, NMOS and PMOS transistors were fabricated separately. The fabrication processes for both transistors were similar. The main differences lie within the types and density of dopant applied to the substrate.

Initially a *p*-type single crystal silicon (Si) wafer was prepared. Screen oxide was first grown on the

© 2006, V. Lashkaryov Institute of Semiconductor Physics, National Academy of Sciences of Ukraine

surface of the substrate. With the substrate tilted by 7° and rotating, a high energy implantation was performed to create a *p*- and *n*-wells for NMOS and PMOS, respectively. The objective of growing screen oxide and tilting the substrate was to minimize the channeling effect; whereas the objective of rotating the wafer was to minimize the shadowing effect [1]. Annealing and drivein was later performed to repair the lattice damage [1].

STI is employed to isolate the neighboring devices. Initially, pad oxide is grown via dry oxidation. Liquid plasma chemical vapor deposition (LPCVD) technique is later applied to deposit silicon nitride Si<sub>3</sub>N<sub>4</sub>. Pad oxide acts as a strain buffer to avoid cracks in the nitride film; whereas the nitride film acts as a mask for silicon etching [1]. A photoresist is then deposited and pattern is developed using photolithography. The nitride film and pad oxide is etched. The area protected under the Si<sub>3</sub>N<sub>4</sub> mask is known as the active region. After stripping the photoresist layer, the substrate was treated by reactive ion etching (RIE) to form trenches. A thin layer of barrier oxide was grown in the trenches so as to block impurities from diffusing into the substrate during chemical vapor deposition (CVD) process. Then tetraethyl-oxy-silane (TEOS) CVD process was applied to fill the trenches with oxide. The oxide at the surface of the substrate was removed using chemical-andmechanical polishing (CMP) technique. STI was completed after annealing was performed and Si<sub>3</sub>N<sub>4</sub> mask and pad oxide were etched.

A thin layer of gate oxide was grown via dry oxidation. Then  $V_{\rm th}$  adjust implantation was performed; after which the substrate was annealed. Subsequently, a layer of polysilicon was deposited on the substrate. Then the substrate was etched and annealed to form a polysilicon gate. LDD was implanted to suppress hot electron effect in submicron MOSFET [1]. After that, CVD was applied to deposit a layer of  $Si_3N_4$ . Then the nitride film was etched to form a sidewall spacer. This was followed by source/drain implantation. Annealing process was performed to activate the dopants. A layer of titanium was deposited on the substrate surface. Rapid thermal annealing (RTA) was employed to form a titanium silicide on the gate. Then the unreacted titanium was etched.

Premetal dielectric (PMD) was formed by depositing a layer of boron phosphor silicate glass (BPSG) on the substrate surface. PMD acts as an insulator for multilevel interconnection [2]. After that the annealing is performed, BPSG is etched to form source/drain contacts. The first level of metallization is formed by depositing and etching aluminum on the contacts. The second level of interconnection can be achieved by depositing another layer of BPSG on the surface. This layer is also known as intermetal dielectric (IMD) [2]. The simulation process is completed when Al is deposited onto the contacts formed by etching IMD. A summary of the parameters used in NMOS and PMOS fabrication is shown in Table 1.

Table 1. Parameters of CMOS fabrication.

| Process step                                     | NMOS parameters                                                                                                                                                                                                                                                                                                                                                    | PMOS parameters                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Silicon                                          | • 7.0×10 <sup>14</sup> cm <sup>-3</sup> boron                                                                                                                                                                                                                                                                                                                      | • 7.0×10 <sup>14</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                           |

| substrate                                        | • \( \lambda \) orientation                                                                                                                                                                                                                                                                                                                                        | boron                                                                                                                                                                                                                                                                                             |

| substrate                                        | (100) orientation                                                                                                                                                                                                                                                                                                                                                  | • $\langle 100 \rangle$ orientation                                                                                                                                                                                                                                                               |

| Retrograde                                       | • 0.02 µm screen                                                                                                                                                                                                                                                                                                                                                   | • 0.02 µm screen                                                                                                                                                                                                                                                                                  |

| well                                             | oxide                                                                                                                                                                                                                                                                                                                                                              | oxide                                                                                                                                                                                                                                                                                             |

| implantation                                     | • $3.75 \times 10^{12} \text{ cm}^{-3}$                                                                                                                                                                                                                                                                                                                            | • $2.75 \times 10^{11} \text{ cm}^{-3}$                                                                                                                                                                                                                                                           |

| miplantation                                     | boron                                                                                                                                                                                                                                                                                                                                                              | boron                                                                                                                                                                                                                                                                                             |

|                                                  | • 100 keV implant                                                                                                                                                                                                                                                                                                                                                  | • 100 keV implant                                                                                                                                                                                                                                                                                 |

|                                                  | energy                                                                                                                                                                                                                                                                                                                                                             | energy                                                                                                                                                                                                                                                                                            |

|                                                  | • 7° tilt                                                                                                                                                                                                                                                                                                                                                          | • 7° tilt                                                                                                                                                                                                                                                                                         |

|                                                  | • 30 min, 900 °C                                                                                                                                                                                                                                                                                                                                                   | • 100 min, 950 °C                                                                                                                                                                                                                                                                                 |

|                                                  | annealing                                                                                                                                                                                                                                                                                                                                                          | annealing                                                                                                                                                                                                                                                                                         |

|                                                  | • 36 min, 970 °C                                                                                                                                                                                                                                                                                                                                                   | • 46 min, 970 °C                                                                                                                                                                                                                                                                                  |

|                                                  | drive-in                                                                                                                                                                                                                                                                                                                                                           | drive-in                                                                                                                                                                                                                                                                                          |

| STI isolation                                    | • 0.01 µm pad oxide                                                                                                                                                                                                                                                                                                                                                | • 0.01 µm pad oxide                                                                                                                                                                                                                                                                               |

| STITISOLATION                                    | <ul> <li>0.01 μm pad oxide</li> <li>0.15 μm Si<sub>3</sub>N<sub>4</sub></li> </ul>                                                                                                                                                                                                                                                                                 | <ul> <li>0.01 μm pad oxide</li> <li>0.15 μm Si<sub>3</sub>N<sub>4</sub></li> </ul>                                                                                                                                                                                                                |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>0.13 μm Si<sub>3</sub>N<sub>4</sub></li> <li>0.50 μm trench</li> </ul>                                                                                                                                                                                                                   |

|                                                  | • 0.50 µm trench depth                                                                                                                                                                                                                                                                                                                                             | depth                                                                                                                                                                                                                                                                                             |

|                                                  | • 15 min, 900 °C annealing                                                                                                                                                                                                                                                                                                                                         | • 15 min, 900 °C                                                                                                                                                                                                                                                                                  |

|                                                  | anneanng                                                                                                                                                                                                                                                                                                                                                           | annealing                                                                                                                                                                                                                                                                                         |

| Gate oxide                                       | • 0.024 um cata avida                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                   |

| Jaie Oxide                                       | • 0.034 µm gate oxide                                                                                                                                                                                                                                                                                                                                              | • 0.034 µm gate oxide                                                                                                                                                                                                                                                                             |

| V <sub>th</sub> adjust                           | • 12.45×10 <sup>11</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                                          | • 12.85×10 <sup>11</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                         |

| implantation                                     | boron                                                                                                                                                                                                                                                                                                                                                              | boron                                                                                                                                                                                                                                                                                             |

| inipiantation                                    | • 5 keV implant                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |

|                                                  | -                                                                                                                                                                                                                                                                                                                                                                  | • 5 keV implant                                                                                                                                                                                                                                                                                   |

| Polygate                                         | energy                                                                                                                                                                                                                                                                                                                                                             | energy                                                                                                                                                                                                                                                                                            |

| deposition                                       | • 0.25 µm polysilicon                                                                                                                                                                                                                                                                                                                                              | • 0.25 μm polysilicon                                                                                                                                                                                                                                                                             |

| deposition                                       | • 26 min, 850 °C                                                                                                                                                                                                                                                                                                                                                   | • 26 min, 850 °C                                                                                                                                                                                                                                                                                  |

|                                                  | annealing                                                                                                                                                                                                                                                                                                                                                          | annealing                                                                                                                                                                                                                                                                                         |

| LDD                                              | • 1×10 <sup>13</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                                              | • 1×10 <sup>13</sup> cm <sup>-3</sup> boron                                                                                                                                                                                                                                                       |

| implantation                                     | phosphorous                                                                                                                                                                                                                                                                                                                                                        | • 5 keV implant                                                                                                                                                                                                                                                                                   |

| miplantation                                     | • 23 keV implant                                                                                                                                                                                                                                                                                                                                                   | energy                                                                                                                                                                                                                                                                                            |

|                                                  | energy                                                                                                                                                                                                                                                                                                                                                             | • 0.15 min, 850 °C                                                                                                                                                                                                                                                                                |

|                                                  | • 20 min, 800 °C                                                                                                                                                                                                                                                                                                                                                   | drive-in                                                                                                                                                                                                                                                                                          |

|                                                  | drive-in                                                                                                                                                                                                                                                                                                                                                           | diive-iii                                                                                                                                                                                                                                                                                         |

| Sidewall                                         | • 0.12 µm Si <sub>3</sub> N <sub>4</sub>                                                                                                                                                                                                                                                                                                                           | • 0.12 μm Si <sub>3</sub> N <sub>4</sub>                                                                                                                                                                                                                                                          |

| spacer                                           | 0.12 μπ 513114                                                                                                                                                                                                                                                                                                                                                     | 0.12 μπ 513114                                                                                                                                                                                                                                                                                    |

| deposition                                       |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |

| Source/drain                                     | • 1×10 <sup>15</sup> cm <sup>-3</sup> arsenic                                                                                                                                                                                                                                                                                                                      | • 5×10 <sup>13</sup> cm <sup>-3</sup> boron                                                                                                                                                                                                                                                       |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |

| implantation                                     | • $2 \times 10^{13} \text{ cm}^{-3}$                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                   |

| implantation                                     | • $2 \times 10^{13} \text{ cm}^{-3}$                                                                                                                                                                                                                                                                                                                               | • 10 keV implant                                                                                                                                                                                                                                                                                  |

| implantation                                     | • 2×10 <sup>13</sup> cm <sup>-3</sup><br>phosphorous                                                                                                                                                                                                                                                                                                               | • 10 keV implant energy                                                                                                                                                                                                                                                                           |

| implantation                                     | • 2×10 <sup>13</sup> cm <sup>-3</sup><br>phosphorous<br>• 25 keV implant                                                                                                                                                                                                                                                                                           | <ul><li>10 keV implant<br/>energy</li><li>45 min, 800 °C</li></ul>                                                                                                                                                                                                                                |

| implantation                                     | • 2×10 <sup>13</sup> cm <sup>-3</sup><br>phosphorous<br>• 25 keV implant<br>energy                                                                                                                                                                                                                                                                                 | • 10 keV implant energy                                                                                                                                                                                                                                                                           |

| implantation                                     | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850,</li> </ul>                                                                                                                                                                                                                                        | <ul><li>10 keV implant<br/>energy</li><li>45 min, 800 °C</li></ul>                                                                                                                                                                                                                                |

|                                                  | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> </ul>                                                                                                                                                                                                                       | • 10 keV implant<br>energy<br>• 45 min, 800 °C<br>annealing                                                                                                                                                                                                                                       |

| implantation  Silicide formation                 | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> </ul>                                                                                                                                                                                             | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> </ul>                                                                                                                                                                                             |

| Silicide                                         | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C</li> </ul>                                                                                                                                                                  | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C</li> </ul>                                                                                                                                                                  |

| Silicide                                         | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C</li> <li>RTA</li> </ul>                                                                                                                                                     | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> </ul>                                                                                                                                                              |

| Silicide                                         | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C</li> </ul>                                                                                                                                     | • 10 keV implant energy • 45 min, 800 °C annealing  • 0.12 µm titanium • 0.02 min, 1100 °C RTA • 0.1 min, 910 °C                                                                                                                                                                                  |

| Silicide                                         | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> </ul>                                                                                                                           | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> </ul>                                                                                                                           |

| Silicide<br>formation                            | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> </ul>                                                                                                     | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> </ul>                                                                                                     |

| Silicide<br>formation                            | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C</li> </ul>                                                                             | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C</li> </ul>                                                                             |

| Silicide formation  PMD deposition               | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> </ul>                                                                   | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> </ul>                                                                   |

| Silicide formation  PMD deposition  Metal 1      | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm Al</li> </ul>                                               | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm Al</li> </ul>                                               |

| Silicide formation  PMD deposition  Metal 1  IMD | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm AI</li> <li>0.30 μm BPSG</li> </ul>                         | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm AI</li> <li>0.30 μm BPSG</li> </ul>                         |

| Silicide formation  PMD deposition  Metal 1      | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm Al</li> <li>0.30 μm BPSG</li> <li>15 min, 950 °C</li> </ul> | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm AI</li> <li>0.30 μm BPSG</li> <li>15 min, 950 °C</li> </ul> |

| Silicide formation  PMD deposition  Metal 1  IMD | <ul> <li>2×10<sup>13</sup> cm<sup>-3</sup> phosphorous</li> <li>25 keV implant energy</li> <li>55 min, 800, 850, 900 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm AI</li> <li>0.30 μm BPSG</li> </ul>                         | <ul> <li>10 keV implant energy</li> <li>45 min, 800 °C annealing</li> <li>0.12 μm titanium</li> <li>0.02 min, 1100 °C RTA</li> <li>0.1 min, 910 °C annealing</li> <li>0.30 μm BPSG</li> <li>20 min, 850 °C annealing</li> <li>0.10 μm AI</li> <li>0.30 μm BPSG</li> </ul>                         |

## 3. Simulation results and discussions

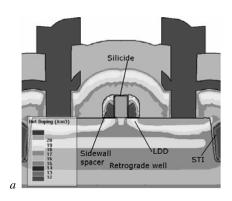

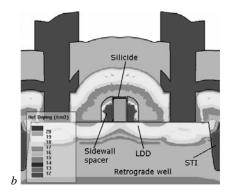

Fig. 1a and b shows the complete cross-sections of NMOS and PMOS, respectively. As clearly shown from the dopant density distributions, a high-energy well implantation has resulted in the highest dopant density concentrated at a certain depth below the substrate surface. As compared to conventional well implantation, in which the highest dopant density lies at the surface of the substrate, such retrograde wells are effective in minimizing punch through. With STI isolation technique implemented in this simulation design, the bird's beak effect, which is a commonly found problem in local oxidation of silicon (LOCOS) technique, has been successfully eliminated.

Two sidewall spacers deposited at the polysilicon gate allows LDD implantation to be performed. As can be seen in Figs 1a and b, the lightly doped phosphorous (for NMOS) and boron (for PMOS) right beneath the spacers allow a reduction in the doping gradient between drain/source and the channel. This, in turn, lowers the electric field at the channel in the vicinity of the drain.

A layer of titanium silicide is formed at the surface of the polygate. The layer of silicide, which has much lower resistivity than polysilicon is necessary to reduce power consumptions and RC time delay for submicron MOSFET local interconnection.

Some of the important parameters such as  $V_{\rm th}$ ,  $T_{\rm ox}$ , and  $L_{\rm g}$  are measured and extracted from the ATLAS

module. In order to validate the results, these parameters are compared with the standard parameters published by international technology roadmap for semiconductor (ITRS) and Berkeley predictive technology model (BPTM) [4]. Since only the standard parameters for 70 nm,  $0.10 \mu \text{m}$ ,  $0.13 \mu \text{m}$ , and  $0.18 \mu \text{m}$  CMOS can be found as published, the polynomial regression technique (using MATLAB tools) has been applied to achieve the required parameters for a 0.14 µm CMOS. Table 2 shows a comparison between the parameters derived from ATLAS and the standard ones obtained using the polynomial regression. All the simulated parameters for  $V_{\text{th}}$ ,  $T_{\text{ox}}$ , and  $L_g$  lie within the tolerance range of the parameters obtained through regression technique. Hence, it can be concluded that the results obtained from the simulation process are valid.

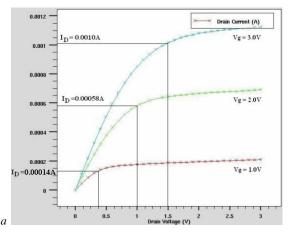

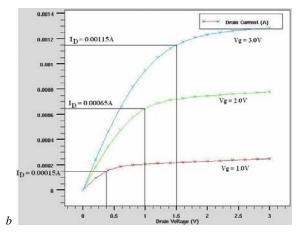

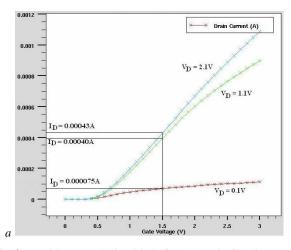

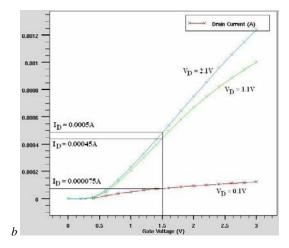

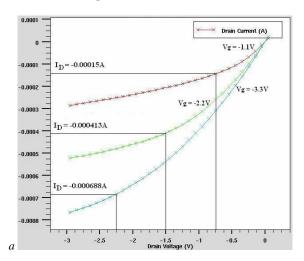

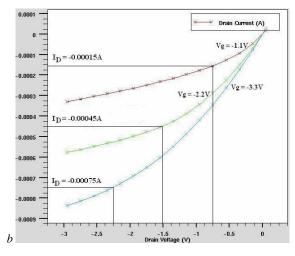

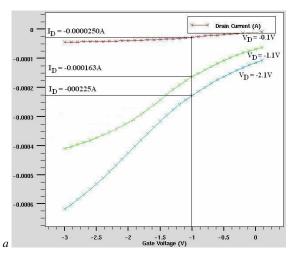

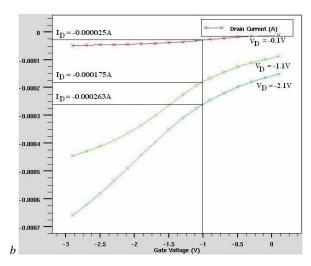

The  $I_D$ - $V_D$  and  $I_D$ - $V_g$  electrical characteristic curves are plotted using ATLAS simulator. Figs 2a and b show the NMOS  $I_D$ - $V_D$  relationships before and after metallization 2 is performed; whereas, Figs 3a and b show the NMOS  $I_D$ - $V_g$  relationships before and after metallization 2. Similarly, the  $I_D$ - $V_D$  relationships for PMOS are shown in Figs 4a and b, respectively; whereas, PMOS  $I_D$ - $V_g$  relationships are shown in Figs 5a and b, respectively. A comparison between before and after second level interconnection is made. The results are summarized in Tables 3 to 6.

Fig. 1. 0.14 µm NMOS (a), PMOS (b).

Fig. 2. NMOS  $I_D$ - $V_D$  relationship before (a) and after (b) metallization 2.

© 2006, V. Lashkaryov Institute of Semiconductor Physics, National Academy of Sciences of Ukraine

**Fig. 3.** NMOS  $I_D$ - $V_g$  relationship before (a) and after (b) metallization 2.

**Fig. 4.** PMOS  $I_D$ - $V_D$  relationship before (a) and after (b) metallization 2.

**Fig. 5.** PMOS  $I_D$ - $V_g$  relationship before (a) and after (b) metallization 2.

It can be observed that for both NMOS and PMOS the  $I_D$ - $V_D$  and  $I_D$ - $V_g$  relationships still retain after the second layer of metallization. This shows that the level of interconnection does not affect the electrical characteristics of the device. However, as

the level of interconnection increases, the drain current  $(I_D)$  increases. Since the power consumption is directly proportional to  $I_D$ , an increase in the level of interconnection will give rise to power consumption.

© 2006, V. Lashkaryov Institute of Semiconductor Physics, National Academy of Sciences of Ukraine

Table 2. Comparison between simulated results and standard parameters for a 0.14  $\mu m$  submicron CMOS.

| CMOS | Parameters      | ATLAS results | Standard parameters      |

|------|-----------------|---------------|--------------------------|

| NMOS | $V_{ m th}$     | 0.343138 V    | 0.3424 ± 12.7% V         |

|      | $T_{\text{ox}}$ | 3.46138 nm    | 3.2158 ± 4% nm           |

|      | $L_g$           | 0.133 µm      | 0.14 ± 15% µm            |

| PMOS | $V_{ m th}$     | -0.378108 V   | -0.3702 ± 12.7% V        |

|      | $T_{\rm ox}$    | 3.46167 nm    | 3.2158 ± 4% nm           |

|      | $L_{\sigma}$    | 0.133 µm      | $0.14 \pm 15\% \; \mu m$ |

Table 3. Comparison of  $I_D$  before and after metallization 2 in  $I_D$ - $V_D$  NMOS graph.

| $V_g, \mathbf{V}$ | $V_D$ , V | $I_D$ before level 2 interconnection, A | I <sub>D</sub> after level 2 interconnection, A | Rate of increase in $I_D$ , % |

|-------------------|-----------|-----------------------------------------|-------------------------------------------------|-------------------------------|

| 1.0               | 0.375     | 0.00014                                 | 0.00015                                         | 7.14                          |

| 2.0               | 1.0       | 0.00058                                 | 0.00065                                         | 12.07                         |

| 3.0               | 1.5       | 0.00100                                 | 0.00115                                         | 15.00                         |

Table 4. Comparison of  $I_D$  before and after metallization 2 in  $I_D$ - $V_g$  NMOS graph.

| $V_g, \ { m V}$ | $V_D,$ V | $I_D$ before level 2 interconnection, A | $I_D$ after level 2<br>Interconnection, | Rate of increase in $I_D$ , % |

|-----------------|----------|-----------------------------------------|-----------------------------------------|-------------------------------|

| 1.5             | 0.1      | 0.000075                                | 0.000075                                | 0                             |

| 1.5             | 1.1      | 0.000400                                | 0.000450                                | 12.50                         |

| 1.5             | 2.1      | 0.000430                                | 0.000500                                | 16.28                         |

Table 5. Comparison of  $I_D$  before and after metallization 2 in  $I_D$ - $V_D$  PMOS graph.

| $V_g$ , | $V_D, \  m V$ | $I_D$ before level 2 | $I_D$ after level 2 | Rate of     |

|---------|---------------|----------------------|---------------------|-------------|

|         |               | interconnection,     | interconnection,    | increase in |

| ·       |               | A                    | A                   | $I_D$ , %   |

| -1.1    | -0.75         | -0.000150            | -0.000150           | 0           |

| -2.2    | -1.5          | -0.000413            | -0.000450           | 8.96        |

| -3.3    | -2.25         | -0.000688            | -0.000750           | 9.01        |

Table 6. Comparison of  $I_D$  before and after metallization 2 in  $I_D$ - $V_g$  PMOS graph.

| $V_g, \ { m V}$ | $V_D,$ V | $I_D$ before level 2 interconnection, | $I_D$ after level 2 interconnection, A | Rate of increase in $I_D$ , % |

|-----------------|----------|---------------------------------------|----------------------------------------|-------------------------------|

| -1.0            | -0.1     | -0.000025                             | -0.000025                              | 0                             |

| -1.0            | -1.1     | -0.000163                             | -0.000175                              | 7.36                          |

| 1.0             | -2.1     | -0.000225                             | -0.000263                              | 16.89                         |

### 4. Conclusion

With the implement of retrograde well implantation, STI, sidewall spacer deposition, silicide formation, and LDD implantation to help to minimize high field effects, the design of a 0.14  $\mu$ m submicron CMOS has been successfully simulated and validated. The results show that power consumption tends to increase after the second metallization was performed.

### References

- 1. H. Xiao, *Introduction to semiconductor manufacturing technology*, Prentice Hall, 2004.

- 2. M. Quirk and J. Serda, *Semiconductor manufacturing technology*, Prentice Hall, 2001.

- 3. Rosfariza bt. Radzali, *Fabrication and characterization of a 0.13 micron device*, M.Sc. Thesis, University Kebangsaan, Malaysia, 2004.

- S. Xiong and J. Ding, *Impact of parameter variation* on future circuit performance, technical report. [Online] Available: http://mechatro2.me.berkeley.edu/~jgding/ee241/.

- C.K. Chen, C.L. Chen, P.M. Gouker, P.W. Wyatt, D.R. Yost, J.A. Burns, V. Suntharalingam, M. Fritze, and C.L. Keast, Fabrication of self-aligned 90 nm fully depleted SOI CMOS SLOTFETS // IEEE Electron Device Lett. 22 (7), p. 345-347 (2001).

- Y.V. Ponomarev, P.A. Stolk, C.J.J. Dachs, and A.H. Montree, A 0.13 μm poly-SiGe gate CMOS technology for low-voltage mixed signal applications // IEEE Trans. Electron Devices 47 (7), p. 1507-1513 (2000).

- 7. H. Koike, H. Ohtsuka, F. Matsuoka, M. Kakumu, and K. Maeguchi, Process simplification in deep submicron CMOS fabrication // IEEE/UCS/SEMI International Symposium Semiconductor Manufacturing, 24-27 (1995).

- 8. D. Parent, E. Basham, Y. Dessouky, S. Gleixner, G. Young, E. Allen, Improvements to a microelectronic design and fabrication course // *IEEE Trans. Education* **48** (3), p. 497-502 (2005).