# Failure of Switching Operation of SiC-MOSFETs and Effects of Stacking Faults on Safe Operation Area

Ryusei Fujita<sup>®</sup>, Kazuki Tani, Kumiko Konishi, and Akio Shima, *Member, IEEE*

Abstract-When developing silicon carbide (SiC) devices, the reliability of the internal body diode is an important issue. Stacking faults (SFs) are expanded from basal plane defects by using a body diode. Although it is well known that on-voltage degradation occurs due to SFs, their effects on dynamic reliability have not been studied well. Furthermore, including the effects of SFs, there are not many reports about the dynamic reliability of SiC-MOSFETs. In this paper, a double-pulse switching test using 3.3-kV SiC-MOSFETs was carried out to clarify the failure mechanism of the switching operation of SiC-MOSFETs and effects of SFs on the safe operation area (SOA). Before the switching test, current stress was applied to the body diode of the devices under test (DUTs) to expand the SFs. The circuit configuration was halfbridge type, and a double-pulse gate signal was applied to the lower arm DUT. The switching voltage was 1.8 kV, and the switching current increased at about 8-A steps to failure. As a result, reverse recovery SOA (RRSOA) reliability decreased depending on the amount of SFs in the SiC-MOSFET. Because RRSOA failure was caused by avalanche due to the hole concentration during reverse recovery and the SFs raised local current density, reverse bias SOA (RBSOA) hardly decreased even if SFs containing SiC-MOSFETs were used. This is because RBSOA failure was caused by degradation of the gate isolation layer due to overheating and the temperature coefficient of the SFs electric resistance indicated negative.

Index Terms—Body diode, safe operation area (SOA), SiC-MOSFET, stacking fault (SF).

### I. INTRODUCTION

**S** ILICON carbide (SiC) is an advanced material for power electronics applications [1]–[3]. In particular, SiC-MOSFETs are being developed actively. Power modules are required to be smaller, which can be achieved by using SiC-MOSFETs with an internal body diode [4]–[6]. However, the reliability of the body diode is an important issue in SiC-MOSFETs. It is well known that ON-voltage degradation

Manuscript received March 7, 2018; revised June 10, 2018 and July 25, 2018; accepted July 26, 2018. Date of publication August 24, 2018; date of current version September 20, 2018. The review of this paper was arranged by Editor B. Kaczer. (*Corresponding author: Ryusei Fujita.*)

The authors are with the Center for Technology Innovation— Electronics, Hitachi, Ltd., Tokyo 185-8601, Japan (e-mail: ryusei.fujita. kw@hitachi.com; kazuki.tani.ru@hitachi.com; kumiko.konishi.qo@ hitachi.com; akio.shima.yw@hitachi.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2018.2864305

occurs due to the expansion of stacking faults (SFs) from basal plane dislocations (BPDs) [7]-[10]. Although MOSFETs are unipolar devices, if a body diode is used and BPDs exist, SF expansion occurs. Since electrons are trapped in SFs that exist epitaxial layer, not only the forward voltage of body diodes but also the ON-voltage of MOSFETs degrade. On the other hand, the effects of SFs on dynamic reliability, such as a safe operation area (SOA), have not been studied well. SOA is an important characteristic of power module operation [11]–[15]. Power modules must be used in the range of voltage and current defined by the SOA, but there are not many reports about the SOA of SiC-MOSFETs including the effects of SFs. In this paper, a double-pulse switching test using SiC-MOSFETs was carried out to measure reverse bias SOA (RBSOA) and reverse recovery SOA (RRSOA) to clarify the failure mechanism and effects of SFs.

## **II. EXPERIMENTAL PROCEDURE**

## A. Samples for Switching Test

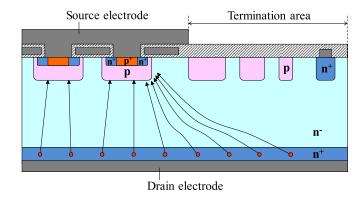

In this paper, the SiC-MOSFETs for the switching test were double-implanted MOSFETs fabricated on a Si-faced, 4° off-axis toward the <11–20> direction, and n-type 4H-SiC substrate. The nominal voltage was 3.3 kV, and the epitaxial layer was 30  $\mu$ m thick with an n-type doping concentration of  $3 \times 10^{15}$  cm<sup>-3</sup>. To expand the SFs before the switching test, we applied 55 A/cm<sup>2</sup>, 175 °C current stress to the body diode until degradation was saturated. The MOSFET ON-voltage was measured before and after the current stress was applied, and the degradation level was calculated using (1). If degradation did not occur, the degradation level was 1.0. The range of the degradation level of the devices under test (DUTs) was 1.0 through 8.0

Degradation level =

$$\frac{V_{\text{on\_after}}}{V_{\text{on\_before}}}$$

. (1)

## B. Switching Test Conditions

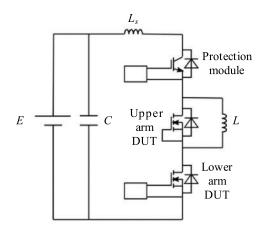

Fig. 1 shows the circuit configuration of the switching test, and Table I shows the circuit parameters. The circuit configuration was half-bridge, and the switching voltage was 1.8 kV. The Si-IGBT module was to protect the circuit from high current. It was turned OFF when the SiC-MOSFET failed to minimize influence of the failure and analyze the failure point. The gate and source terminals of the upper arm DUT

0018-9383 © 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 1. Circuit configuration of the switching test.

| TABLE I                   |

|---------------------------|

| <b>CIRCUIT PARAMETERS</b> |

| Name                                             | Symbol          | Value              |  |

|--------------------------------------------------|-----------------|--------------------|--|

| Input voltage                                    | Ε               | 1.8 kV             |  |

| Input capacitance                                | С               | 470 μF             |  |

| Stray inductance                                 | $L_s$           | 4 μΗ               |  |

| Load inductance                                  | L               | 1 mH               |  |

| Gate resistance                                  | $R_{g(on/off)}$ | $130/160 \ \Omega$ |  |

| Gate-drive voltage                               | $V_{g(on/off)}$ | +15/-8 V           |  |

| 1st pulse                                        |                 | 2nd pulse          |  |

| increase from 20 µs<br>to breakdown (5 µs steps) | 30 µ:           | s 10 µs            |  |

Fig. 2. Gate signal of the lower arm DUT.

were short connected to be used as a free-wheeling diode to analyze RRSOA. A double-pulse gate signal was applied to the lower arm DUT to analyze RBSOA. Fig. 2 shows the gate signal of the lower arm DUT. The width of the first pulse increased from 20  $\mu$ s to failure in 5- $\mu$ s steps, and the switching current ( $I_{sw}$ ) at failure was recorded. The failure of the upper arm DUT means that  $I_{sw}$  is beyond the limit of the RRSOA, and the failure of the lower arm DUT means that  $I_{sw}$  is beyond the limit of the RBSOA.

#### C. Current Flow Path Simulation

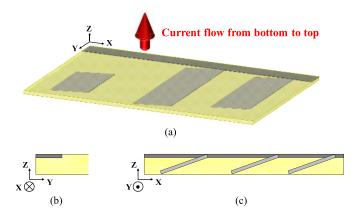

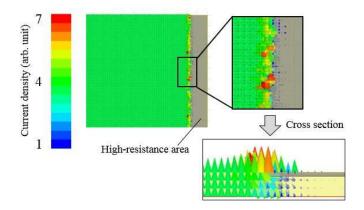

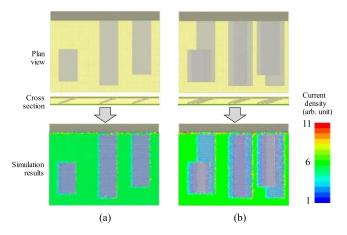

To estimate the carrier's route in SiC-MOSFETs containing SFs, current flow path simulation was carried out. The simulation software was ANSYS Q3D. Fig. 3 and Table II show the simulation conditions. The shape of the bulk was rectangular cuboid. Since the bulk material for the simulation has to be a conductor, copper was used. Pale gray area had  $10 \times$  larger resistivity compared to that of yellow bulk and was put in the bulk in a 4° tilted state assuming SFs. Deep gray area had  $1000 \times$  larger resistivity, assuming that there was a termination area. The current direction was from bottom to top, and the current density in the bulk was calculated.

Fig. 3. Simulation diagram. (a) 3-D view. (b) *yz* plane. (c) *xz* plane.

TABLE II SIMULATION CONDITIONS

| Color     | Resistivity<br>[Ω m]  | Width<br>[µm] | Depth<br>[µm] | Thickness<br>[µm] |

|-----------|-----------------------|---------------|---------------|-------------------|

| Yellow    | $1.68 \times 10^{-8}$ | 2000          | 1500          | 30                |

| Pale gray | $1.68 \times 10^{-7}$ | 340           | Respective    | 5                 |

| Deep gray | $1.68 \times 10^{-5}$ | 2000          | 170           | 5                 |

#### **III. RESULTS AND DISCUSSION**

## A. RRSOA and RBSOA Failure Model of SiC-MOSFET

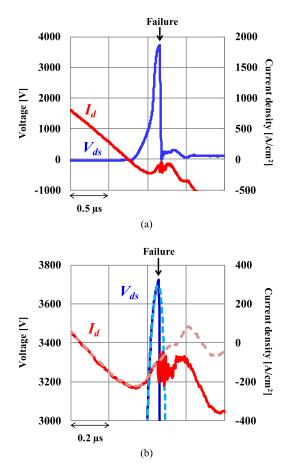

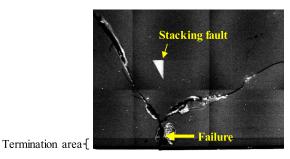

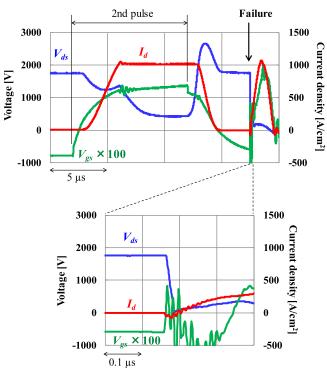

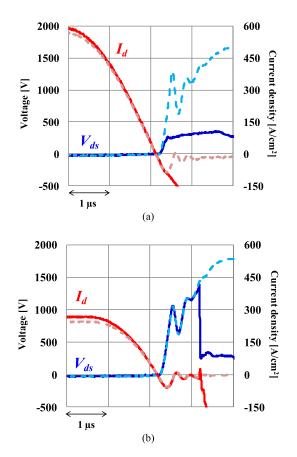

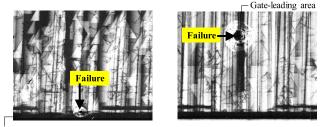

Fig. 4 shows the RRSOA failure waveforms at degradation level 1.0.  $I_{sw}$  was about 1500 A/cm<sup>2</sup>. The drain-to-source voltage (V<sub>ds</sub>) rose to 3.7 kV after the free-wheeling period, so it is inferred that the failure was caused by avalanche. Since  $V_{ds}$  at the previous step was barely lower than at failure, the failure occurred due to exceeding the limit of  $V_{ds}$ . The failure occurred during the reverse recovery period. Then, the holes left in the n – epitaxial layer and n + substrate went back to the source electrode, so the avalanche breakdown occurs at the point where more holes are concentrated. Fig. 5 shows a photoluminescence (PL) image of RRSOA failed DUT. The PL image was obtained at 420 nm using a long pass filter. Although the degradation level was 1.0, one SF existed. But the failure occurred near the termination area apart from the SF, so the holes were most concentrated and the local current density must be the highest at the failure point. Also, during Si bipolar device switching, there are reports that the current concentration and failure occur near the termination area [16], [17]. Fig. 6 shows a diagram of the hole concentration in a SiC-MOSFET. During reverse recovery, a high voltage is applied to the drain electrode, and holes left in the epitaxial layer and substrate are drawn to the source electrode, which is connected to the negative side of the power source. However, holes cannot pass through the termination area and concentrate near the MOSFET cell, which is located at the edge of the active area. Therefore, the avalanche breakdown occurs more easily at the edge of the active area. Fig. 7 shows the results of the current flow path simulation. The surface of the gray area was a high-resistance area assuming that there was a termination area. The current density was high at the edge of the high-resistance area.

Fig. 4. RRSOA failure waveforms (degradation level 1.0). (a) Enlarged view of the failure point. (b) Dotted lines: previous step of failure.

Fig. 5. PL image of RRSOA failed DUT (degradation level 1.0).

This result indicates that the current avoids the high-resistance area and is concentrated at the edge of this area. Also, in actual SiC-MOSFETs, it is inferred that holes avoid the termination area and concentrate at the edge. When the current density is beyond the limit, avalanche breakdown occurs.

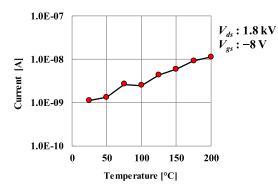

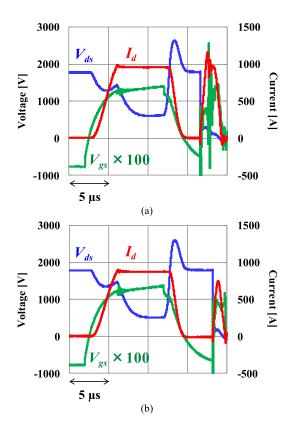

Fig. 8 shows the RBSOA failure waveforms at degradation level 1.0.  $I_{sw}$  was about 1000 A/cm<sup>2</sup>. At the second pulse, the ON-voltage was close to 500 V because of the high  $I_{sw}$ , so selfheating should have been very high, and the temperature of the DUT should have risen. Then, the failure occurred after turn-OFF. Therefore, it is inferred that the gate isolation layer was broken by applying a high voltage and by the rising temperature because the gate isolation layer generally degrades

Fig. 6. Diagram of holes concentration.

Fig. 7. Result of current flow path simulation (without SFs).

Fig. 8. RBSOA failure waveforms (degradation level 1.0).

under high temperature [18], [19]. Fig. 9 shows the temperature dependence of the gate leakage current. The gate leakage current increased depending on the temperature. The gate

Fig. 9. Temperature dependence of gate leakage current.

Fig. 10. Appearance image of RBSOA failed DUT (degradation level 1.0). Material of source electrode is aluminum.

leakage current was  $10 \times$  larger at 200 °C compared to that at 25 °C. Therefore, the gate isolation layer steadily degraded as the temperature rose, and the failure occurred when it could not stand at the electric field that was applied to the drain electrode by high voltage. Also, in a Si-IGBT, failure mode where failure occurred some microseconds after turn-OFFhas been reported [20], [21]. These reports show failure mode occurring in a short-circuit test due to overheating. Fig. 10 shows the appearance image of RBSOA failed DUT. The aluminum electrode was severely damaged, so the DUT had a very high temperature, which was equal to or higher than the melting point of aluminum. The failure occurred near the bonding wire, and this is appropriate because the current heads toward the bonding wire, and the temperature rises more easily there.

These failure mechanisms shown in this section have no relation of SFs and can occur in any SiC-MOSFET.

#### B. Effects of Stacking Faults to SOA

Fig. 11 shows the RRSOA failure waveforms at degradation level 4.1 and 8.0. Fig. 11(a) shows the waveforms of degradation level 4.1.  $I_{sw}$  was about 600 A/cm<sup>2</sup> and was less than half of the result of degradation level 1.0. Fig. 11(b) shows the waveforms of degradation level 8.0.  $I_{sw}$ was about 270 A/cm<sup>2</sup> and was less than a quarter of the result of degradation level 1.0. These results indicate that the RRSOA reliability decreased dependently on the degradation level. The increasing of local current density due to SFs is considered to be the factor that leads to the results because the failure is caused by avalanche due to the hole concentration. Since SFs electrically act as resistance, if expansion of SFs

Fig. 11. RRSOA failure waveforms of (a) degradation level 4.1 and (b) degradation level 8.0. Dotted lines: previous step of failure.

Fig. 12. Results of current flow path simulation with (a) three SFs and (b) eight SFs.

occurs, the effective active area decreases, and the local current density in the nonaffected areas increases. Therefore, the failure occurred at lower  $I_{sw}$  at large degradation level DUTs. Fig. 12 shows the results of the current flow path simulation assuming DUTs containing SFs. The pale gray areas have  $10 \times$  larger the resistivity and 1/6 the thickness compared to the yellow area assuming SFs. Fig. 12(a) and (b) contains three SFs and eight SFs, respectively. In Fig. 12(b), the current density is higher than in Fig. 12(a) wholly and near the dark gray area in which surface lets no current flow through. Also, in actual SiC-MOSFETs, it is inferred that

Termination area

Fig. 13. PL image of RRSOA failure DUTs of (a) degradation level 4.1 and (b) degradation level 8.0.

Fig. 14. RBSOA failure waveforms of (a) degradation level 4.1 and (b) degradation level 8.0.

similar phenomenon occurred and the SiC-MOSFETs broke down at lower  $I_{sw}$ . Fig. 13 shows a PL image of RRSOA failed DUTs. In Fig. 13(a), failure occurred near the termination area shown in Fig. 5 (degradation level 1.0). This is appropriate because failure is caused by avalanche, and the carriers are more concentrated near the termination area. On the other hand, in Fig. 13(b), failure occurred away from the termination area. But the point was near the gate-leading area that carriers could not flow through as with the termination area. Therefore, near the gate-leading area, the current density is higher than closer to the center.

Fig. 14 shows the RBSOA failure waveforms at degradation levels 4.1 and 8.0. Fig. 14(a) shows the waveforms of degradation level 4.1.  $I_{sw}$  was about 950 A/cm<sup>2</sup> and hardly decreased compared to degradation level 1.0. Fig. 14(b) shows the waveforms of degradation level 8.0.  $I_{sw}$  was

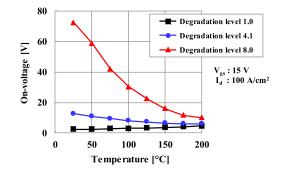

Fig. 15. Temperature dependence of the on-voltage.

Fig. 16. Energy losses during the second pulse at failure step.

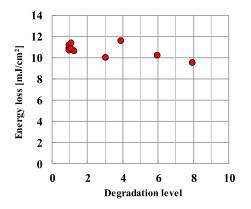

about 860 A/cm<sup>2</sup> and was about 10% less than the result of degradation level 4.1. Although self-heating during the second pulse was considered a factor of RBSOA failure,  $I_{sw}$ at failure did not decrease much. The cause of these results is considered to be the temperature dependence of the SF's electric resistance. Fig. 15 shows the temperature dependence of the ON-voltage. The ON-voltage decreased depending on the temperature. Although it was measured again at 25 °C after at 200 °C, the ON-voltage was almost the same as the first measurement. This means that the temperature coefficient of the SF's electric resistance indicates as negative. Thus, a model was proposed [22]. The model is that electron trapping decreases due to the reduction of the energy bandgap between the quasi-electron Fermi energy and the highest occupied state in the SF quantum well due to the Fermi energy reduction caused by the temperature rising. As shown in Fig. 14, the failure occurred after turn-OFF, which is the same as at degradation level 1.0. Therefore, it is inferred that the failure model is the same as that of degradation level 1.0 although more SFs exist. Since the RBSOA failure was caused by overheating, energy loss due to failure should not decrease dependently on degradation level. Fig. 16 shows the energy losses during the second pulse at the failure step. Except for degradation level 8.0, energy losses did not depend on degradation level. At degradation level 8.0, the ON-voltage might not decrease to the same level as that of low degradation level.

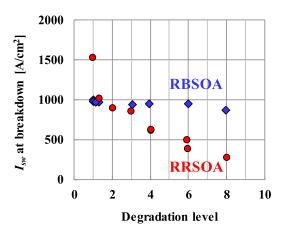

Fig. 17 shows  $I_{sw}$  at failure at each degradation level. RRSOA reliability decreased dependently on degradation

Fig. 17. Switching current at failure.

level. On the other hand, RBSOA reliability hardly decreased even if SFs containing SiC-MOSFETs were used.

#### **IV. CONCLUSION**

We carried out double-pulse switching tests using SiC-MOSFETs and analyzed the failure mode. RRSOA failure occurred near the termination or gate-wiring area, and we concluded that the failure was caused by avalanche due to hole concentration during reverse recovery. RRSOA reliability decreased when SFs expanded because the SFs reduced the effective active area and the current density increased. RBSOA failure occurred after turn-OFF, and the ON-voltage during the second pulse was very high. Therefore, we concluded that RBSOA failure was caused by degradation of the gate isolation layer due to overheating. Since the temperature coefficient of SF's electric resistance indicates as negative, RBSOA reliability hardly decreased even if SFs containing SiC-MOSFETs were used.

#### REFERENCES

- M. Bhatnagar and B. J. Baliga, "Comparison of 6H-SiC, 3C-SiC, and Si for power devices," *IEEE Trans. Electron Devices*, vol. 40, no. 3, pp. 645–655, Mar. 1997, doi: 10.1109/16.199372.

- [2] G. Y. Chung *et al.*, "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 176–178, Apr. 2001, doi: 10.1109/55.915604.

- [3] J. A. Cooper and A. Agarwal, "SiC power-switching devices-the second electronics revolution?" *Proc. IEEE*, vol. 90, no. 6, pp. 956–968, Jun. 2002, doi: 10.1109/JPROC.2002.1021561.

- [4] J. Jordán *et al.*, "A comparative performance study of a 1200 V Si and SiC MOSFET intrinsic diode on an induction heating inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2550–2562, May 2014, doi: 10.1109/TPEL.2013.2282658.

- [5] S. Jahdi *et al.*, "An analysis of the switching performance and robustness of power MOSFETs body diodes: A technology evaluation," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2383–2394, May 2015, doi: 10.1109/TPEL.2014.2338792.

- [6] D. Martin, W. A. Curbow, B. Sparkman, L. E. Kegley, and T. McNutt, "Switching performance comparison of 1200 V and 1700 V SiC optimized half bridge power modules with SiC antiparallel Schottky diodes versus MOSFET intrinsic body diodes," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2017, pp. 2297–2304, doi: 10.1109/APEC.2017.7931020.

- [7] M. Skowronski and S. Ha, "Degradation of hexagonal silicon-carbidebased bipolar devices," J. Appl. Phys., vol. 99, no. 1, p. 01101, Jan. 2006, doi: 10.1063/1.2159578.

- [8] T. Kimoto *et al.*, "Understanding and reduction of degradation phenomena in SiC power devices," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2017, pp. 2A-1.1–2A-1.7, doi: 10.1109/IRPS.2017.7936253.

- [9] S. Yamamoto, Y. Nakao, N. Tomita, S. Nakata, and S. Yamakawa, "Development of 3.3 kV SiC-MOSFET: Suppression of forward voltage degradation of the body diode," *Mater. Sci. Forum*, vols. 778–780, pp. 951–954, Feb. 2014, doi: 10.4028/www.scientific.net/MSF.778-780.951.

- [10] K. Konishi, S. Yamamoto, S. Nakata, Y. Toyoda, and S. Yamakawa, "Driving force of stacking fault expansion in 4H-SiC PN diode by *in situ* electroluminescence imaging," *Mater. Sci. Forum*, vols. 778–780, pp. 342–345 Feb. 2014, doi: 10.4028/www.scientific.net/MSF.778-780.342.

- [11] H. Yilmaz, K. Owyang, P. O. Shafer, and C. C. Borman, "Optimization of power MOSFET body diode for speed and ruggedness," *IEEE Trans. Ind. Appl.*, vol. 26, no. 4, pp. 793–797, Jul. 1990, doi: 10.1109/28.56007.

- [12] N. Thaper and B. J. Baliga, "A new IGBT structure with a wider safe operating area (SOA)," in *Proc. 6th Int. Symp. Power Semiconductor Devices and ICs*, Jun. 1994, pp. 177–182, doi: 10.1109/ISPSD.1994. 583697.

- [13] M. Domeij, J. Lutz, and D. Silber, "On the destruction limit of Si power diodes during reverse recovery with dynamic avalanche," *IEEE Trans. Electron Devices*, vol. 50, no. 2, pp. 486–493, Feb. 2003, doi: 10.1109/TED.2002.808423.

- [14] X. Gong, "A 3.3kV IGBT module and application in modular multilevel converter for HVDC," in *Proc. IEEE Int. Symp. Ind. Electron. (ISIE)*, May 2012, pp. 1944–1949, doi: 10.1109/ISIE.2012.6237390.

- [15] A. Castellazzi et al., "Transient out-of-SOA robustness of SiC power MOSFETs," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2017, pp. 2A-3.1–2A-3.8, doi: 10.1109/IRPS.2017.7936255.

- [16] Y. Tomomatsu *et al.*, "An analysis and improvement of destruction immunity during reverse recovery for high voltage planar diodes under high dIrr/dt condition," in *Proc. 8th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, May 1996, pp. 353–356, doi: 10.1109/ISPSD. 1996.509514.

- [17] Z. Chen, K. Nakamura, and T. Terashima, "LPT(II)-CSTBT (III) for High Voltage application with ultra robust turn-off capability utilizing novel edge termination design," in *Proc. 24th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Jun. 2012, pp. 25–28, doi: 10. 1109/ISPSD.2012.6229014.

- [18] J. S. Suehle, "Ultrathin gate oxide reliability: Physical models, statistics, and characterization," *IEEE Trans. Electron Devices*, vol. 49, no. 6, pp. 958–971, Jun. 2002, doi: 10.1109/TED.2002.1003712.

- [19] P. Fiorenza, A. La Magna, M. Vivona, and F. Roccaforte, "Near interface traps in SiO<sub>2</sub>/4H-SiC metal-oxide-semiconductor field effect transistors monitored by temperature dependent gate current transient measurements," *Appl. Phys. Lett.*, vol. 109, no. 1, p. 012102, Jul. 2016, doi: 10.1063/1.4955465.

- [20] T. Laska et al., "Short circuit properties of trench-/field-stop-IGBTsdesign aspects for a superior robustness," in Proc. IEEE 15th Int. Symp. Power Semiconductor Devices ICs (ISPSD), Apr. 2003, pp. 152–155, doi: 10.1109/ISPSD.2003.1225252.

- [21] A. Benmansour, S. Azzopardi, J. C. Martin, and E. Woirgard, "Failure mechanisms of Trench IGBT under various short-circuit conditions," in *Proc. IEEE Power Electron. Spec. Conf. (PESC)*, Jun. 2007, pp. 1923–1929, doi: 10.1109/PESC.2007.4342297.

- [22] J. D. Caldwell, R. E. Stahlbush, M. G. Ancona, O. J. Glembocki, and K. D. Hobart, "On the driving force for recombination-induced stacking fault motion in 4H–SiC," *J. Appl. Phys.*, vol. 108, no. 4, p. 044503, Aug. 2010, doi: 10.1063/1.3467793.

**Ryusei Fujita** received the Degree from the Omura Technical High School, Nagasaki, Japan, in 2009.

Since 2009, he has been with the Central Research Laboratory, Hitachi, Ltd., Tokyo, Japan, where he is currently focusing on the research of SiC power device from the view point of the circuit reliability in power module.

Kazuki Tani received the B.S. and M.S. degrees in material engineering from the University of Tokyo, Tokyo, Japan, in 2007 and 2009, respectively.

Since 2009, he has been with the Central Research Laboratory, Hitachi, Ltd., Tokyo, where he has been involving in the research and development of Ge light-emitting diode for Si photonics. His current research interests include power device reliability and device physics.

Akio Shima (M'04) received the B.S. and M.S. degrees in applied physics from the University of Tokyo, Tokyo, Japan, in 1993 and 1995, respectively, and the Ph.D. degree in electrical engineering from Waseda University, Tokyo, in 2007.

He is currently the Department Manager in charge of energy conversion electronics with the Center of Technology Innovation, Electronics, Hitachi Ltd., Tokyo.

Kumiko Konishi received the B.S. and M.S. degrees in electrical and electronics engineering from Chiba University, Chiba, Japan, in 2007 and 2009, respectively.

Since 2009, she has been with the Central Research Laboratory, Hitachi, Ltd., Tokoyo, Japan. Her current research interests include defect physics in SiC by optical and electrical characterization, and its effect on the reliability of SiC power devices.