# PAPER Fast Simulation Technique of Plane Circuits via Two-Layer CNN-Based Modeling

Yuichi TANJI<sup>†a)</sup>, Hideki ASAI<sup>††</sup>, *Members*, Masayoshi ODA<sup>†††</sup>, *Nonmember*, Yoshifumi NISHIO<sup>†††</sup>, and Akio USHIDA<sup>††††</sup>, *Members*

**SUMMARY** A fast time-domain simulation technique of plane circuits via two-layer Cellular Neural Network (CNN) -based modeling, which is necessary for power/signal integrity evaluation in VLSIs, printed circuit boards, and packages, is presented. Using the new notation expressed by the two-layer CNN, 1,553 times faster simulation is achieved, compared with Berkeley SPICE (*ngspice*). In CNN community, CNNs are generally simulated by explicit numerical integration such as the forward Euler and Runge-Kutta methods. However, since the two-layer CNN is a stiff circuit, we cannot analyze it by using an explicit numerical integration method. Hence, to analyze the two-layer CNN and reduce the computational cost, the leapfrog method is introduced. This procedure would open an application of CNN to electronic design automation area.

*key words: cellular neural networks, plane circuits, signal/power integrity, leapfrog method*

#### 1. Introduction

VLSI implementations, potential applications for image processing, and nonlinear wave phenomena of Cellular Neural Networks (CNNs) have attracted many interests in the last two decades. As one of the studies, the nonlinear wave phenomena have been analyzed via CNNs [1], [2], [8], where the partial differential equations are expressed into CNNs, and the nonlinear phenomena are efficiently analyzed by the CNN universal machine [6]. On an engineering application, the ability of solving partial differential equations applications.

In this paper, we analyze the plane circuits using a CNN for power/signal integrity evaluation in VLSIs, packages, and printed circuit boards in the high-speed electronic systems [3], [4]. The high-speed electronic systems suffer from the inductance effects. We introduce the two-layer CNN [5] to model the inductance effects using the coupling templates.

<sup>++++</sup>The author is with the Department of Mechanical and Electronic Engineering, Tokushima Bunri University, Sanuki-shi, 769-2193 Japan.

a) E-mail: tanji@eng.kagawa-u.ac.jp

DOI: 10.1093/ietfec/e91-a.12.3757

3757

The CNN universal machine simulates CNNs using the forward Euler method. However, the linear RLC models of VLSIs, packages, and printed circuit boards are stiff circuits, which prohibit use of explicit numerical integration such as forward Euler method for transient simulation. Alternatively, implicit numerical integration such as backward Euler, backward difference, and Gear methods [7], which are used in SPICE-like simulators, are applicable, but these methods are computationally inefficient since they need to solve a set of linear equations. To reduce the computational costs, we introduce the leapfrog method [9], [11], where the state vectors in the first and second layers of the CNN are decoupled and updated alternately in the same manner as the forward Euler method. This method is a variety of FDTD methods [10] which are known as a Maxwell's solver. In an illustrative example, it is shown that the proposed procedure via the two-layer CNN-based modeling is 1,553 times faster than Berkeley SPICE (ngspice). This means that we can expect further speed up if these computations are carried out on a hardware accelerator as the CNN universal machine.

## 2. Two-Layer CNN-Based Modeling of Plane Circuits

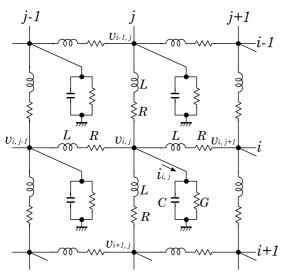

In signal/power integrity evaluation in VLSIs, packages, and printed circuit boards of high-speed electronic systems, analysis of a plane circuit is required. The physical phenomena on a plane circuit are governed by the Helmholtz's equations which are obtained from the Maxwell's equations on Lorentz or Coulomb gauge. However, since solving the Helmholtz's equations requires a huge CPU cost, the plane circuit is approximated by the linear passive R, L, C, and G elements shown in Fig. 1 [15]. The circuit shown in Fig. 1 is governed by the following two equations:

$$\frac{dv_{i,j}(t)}{dt} = -G\sqrt{\frac{L}{C}}v_{i,j}(t) + \sqrt{\frac{L}{C}}i_{i,j}(t),$$

(1)

$$\frac{di_{i,j}(t)}{dt} = -R\sqrt{\frac{C}{L}}i_{i,j}(t) + \sqrt{\frac{C}{L}}\left(v_{i-1,j}(t) + v_{i+1,j}(t) + v_{i,j-1}(t) + v_{i,j+1}(t) - 4v_{i,j}(t)\right),$$

(2)

where

$$t = \frac{1}{\sqrt{LC}}\tau,\tag{3}$$

and  $\tau$  and t show the actual and normalized times, respectively. Equation (1) is KCL at the node (i, j) and (2) is

Manuscript received December 10, 2007.

Manuscript revised April 27, 2008.

<sup>&</sup>lt;sup>†</sup>The author is with the Department of Reliability-based Information Systems Engineering, Kagawa University, Takamatsu-shi, 761-0396 Japan.

<sup>&</sup>lt;sup>††</sup>The author is with the Department of Systems Engineering, Shizuoka University, Hamamatsu-shi, 432-8561 Japan.

<sup>&</sup>lt;sup>†††</sup>The authors are with the Department of Electrical and Electronic Engineering, Tokushima University, Tokushima-shi, 770-8506 Japan.

Fig. 1 Circuit model of plane circuit.

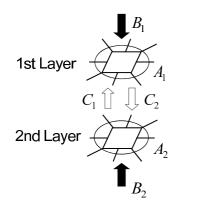

Fig. 2 Cells of two-layer CNN.

obtained from the characteristics of the four RL branches which are connected to the node (i, j).

Consider expressing (1) and (2) by a two-layer CNN. Cells of two-layer CNN interact each other through  $A_m$ ,  $B_m$ , and  $C_m$  templates as shown in Fig. 2. The state equations of the two-layer CNN are written by

$$\begin{aligned} \frac{dv_{x1ij}(t)}{dt} &= -v_{x1ij}(t) \\ &+ \sum_{C(k,l) \in N_r(i,j)} A_1(i, j; k, l) v_{y1kl}(t) \\ &+ \sum_{C(k,l) \in N_r(i,j)} B_1(i, j; k, l) v_{u1kl}(t) \\ &+ \sum_{C(k,l) \in N_r(i,j)} C_1(i, j; k, l) v_{y2kl}(t) + I_1, \end{aligned}$$

(4)

$$\begin{aligned} \frac{dv_{x2ij}(t)}{dt} &= -v_{x2ij}(t) \\ &+ \sum_{C(k,l) \in N_r(i,j)} A_2(i, j; k, l) v_{y2kl}(t) \\ &+ \sum_{C(k,l) \in N_r(i,j)} B_2(i, j; k, l) v_{u2kl}(t) \end{aligned}$$

$C(k, \overline{l}) \in N_r(i, j)$

$$+\sum_{C(k,l)\in N_{c}(i,j)}C_{2}(i,j;k,l)v_{y1kl}(t)+I_{2},$$

(5)

where  $N_r(i, j)$  is the *r*-neighborhood of a cell C(i, j) as  $N_r(i, j) = \{C(k, l) | \max\{|k - i|, |l - j|\} \le r. v_{x1ij}(t), v_{y1ij}(t)$ , and  $v_{u1ij}(t)$  are the internal state, output, input of a cell C(i, j) in the first layer, respectively.  $v_{x2ij}(t), v_{y2ij}(t)$ , and  $v_{u2ij}(t)$  are the internal state, output, input of a cell C(i, j) in the second layer.  $A_m(i, j; k, l), B_m(i, j; k, l)$ , and  $C_m(i, j; k, l)$  are the feedback, control, and coupling templates in the *m*-th layer, respectively [5]. The output functions of the two-layer CNN are described by

$$v_{y1ij}(t) = \frac{1}{2} \left( |v_{x1ij}(t) + 1| - |v_{x1ij}(t) - 1| \right), \tag{6}$$

$$v_{y2ij}(t) = \frac{1}{2} \left( |v_{x2ij}(t) + 1| - |v_{x2ij}(t) - 1| \right).$$

(7)

Comparing the circuit Eqs. (1) and (2) with (4) and (5), we can describe the cloning templates for the plane circuit as

$$A_{1} = \begin{pmatrix} 0 & 0 & 0 \\ 0 & 1 - G \sqrt{\frac{L}{C}} & 0 \\ 0 & 0 & 0 \end{pmatrix}, B_{1} = \mathbf{0},$$

$$C_{1} = \begin{pmatrix} 0 & 0 & 0 \\ 0 & \sqrt{\frac{L}{C}} & 0 \\ 0 & 0 & 0 \end{pmatrix}, I_{1} = 0,$$

$$A_{2} = \begin{pmatrix} 0 & 0 & 0 \\ 0 & 1 - R \sqrt{\frac{C}{L}} & 0 \\ 0 & 0 & 0 \end{pmatrix}, B_{2} = \mathbf{0},$$

$$C_{2} = \begin{pmatrix} 0 & \sqrt{\frac{C}{L}} & 0 \\ \sqrt{\frac{C}{L}} & -4 \sqrt{\frac{C}{L}} & \sqrt{\frac{C}{L}} \\ 0 & \sqrt{\frac{C}{L}} & 0 \end{pmatrix}, I_{2} = 0,$$

(9)

where the matrices  $A_m$ ,  $B_m$ , and  $C_m$  are the matrix representations of  $A_m(i, j; k, l)$ ,  $B_m(i, j; k, l)$ , and  $C_m(i, j; k, l)$ , respectively. Since the plane circuit shown in Fig. 1 is linear, the output functions (6) and (7) are redefined by

$$v_{y1ij}(t) = v_{x1ij}(t),$$

(10)

$$v_{y2ij}(t) = v_{x2ij}(t).$$

(11)

Although CNN has a periodical boundary condition in general, the circuit model of the plane circuit does not have such a condition. The nodes on the edge connects three or two RL branches. Therefore, we should rewrite  $C_2$  appropriately for these nodes. If the node connects with three RL branches,  $C_2$  is written by

$$\boldsymbol{C}_2 = \begin{pmatrix} 0 & \sqrt{\frac{C}{L}} & 0 \\ 0 & -3\sqrt{\frac{C}{L}} & \sqrt{\frac{C}{L}} \\ 0 & \sqrt{\frac{C}{L}} & 0 \end{pmatrix}.$$

If the node connects two RL branches,  $C_2$  is written by

$$C_{2} = \begin{pmatrix} 0 & \sqrt{\frac{C}{L}} & 0 \\ 0 & -2\sqrt{\frac{C}{L}} & 0 \\ 0 & \sqrt{\frac{C}{L}} & 0 \end{pmatrix}.$$

It should be noted that position of the nonzero off-diagonal elements depends on the node.

### 3. Leapfrog Method

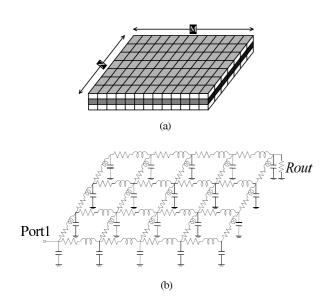

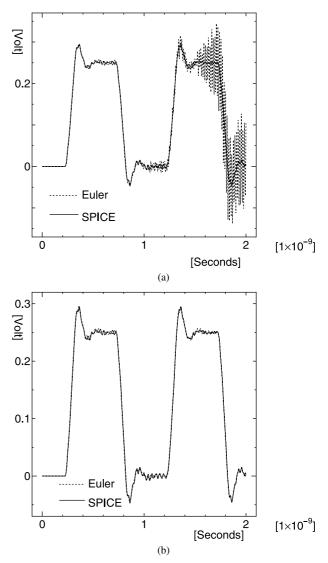

In the CNN universal machine [6], the dynamics of CNN is simulated by using the forward Euler method. However, if the circuit is stiff, the forward Euler method may break down. For example, we simulated the two-layer CNN corresponding to the plane circuit shown in Fig. 3(a), where the plane circuit with  $3 \times 4$  cells is approximated by the RLC circuit as shown in Fig. 3(b). Figure 4(a) shows the transient voltage waveform at the output resister  $R_{out}$  in Fig. 3(b) when a pulse is given at 'Port1,' where the waveform was calculated by the forward Euler method. The result is compared with Berkeley SPICE. The response obtained from the forward Euler method is violently vibrated and the simulation would break down for a long duration. In this example, the ratio of the maximum absolute eigenvalue to the minimum is  $2.83 \times 10^6$  so that the circuit is stiff. This is the reason why the simulation would break down. Fortunately, with 10 times smaller time-step size than the case of Fig. 4(a), we can obtain the reliable result as shown in Fig. 4(b). However, since it is not easy to know the appropriate time-step size, the conventional forward Euler or Runge Kutta method is not suitable for all the CNNs. Instead of such explicit methods, we can use implicit numerical integration such as backward Euler, backward difference, and Gear methods [7]. However, these methods need to solve a set of linear equations, which prohibits the application of these methods to large-scale problems. To analyze large-scale and stiff cir-

Fig. 3 Modeling of plane circuit. (a) Plane circuit. (b) The equivalent circuit.

cuits, we use the leapfrog method [11] which is a variety of FDTD methods [10] for circuit simulation [9].

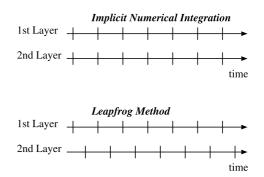

Since the center values of  $A_1$  in (8) and  $A_2$  in (9) are only non-zero, the first and second layers interact each other through the coupling templates  $C_1(i, j; k, l)$  of (4) and  $C_2(i, j; k, l)$  of (5). If implicit numerical integration is used for solving (4) and (5), we have to solve a set of linear equations due to these couplings. In the leapfrog method, the two coupled state vectors are alternately updated. Hence, the simulation points of the first layer is shifted with half a time step to the second layer as shown in Fig. 6, whereas the state vectors in both layers are simultaneously updated when implicit integration is used. Since the state vectors are alternately updated in the leapfrog method, we do not have to solve a set of linear equations, differently from the case of

**Fig. 4** Transient waveforms calculated by the forward Euler methods. The 10 times smaller time-step size than the case of Fig. 4(a) is used for the forward method to obtain the result of the Fig. 4(b). In Fig. 4(b), the waveform (Euler) obtained by the forward Euler method almost overlaps that obtained by SPICE.

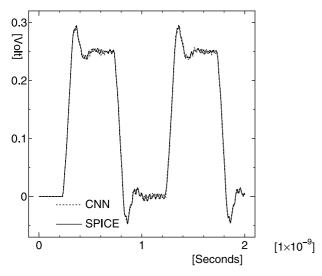

**Fig.5** Transient waveforms calculated by the leapfrog method. The waveform (CNN) obtained by the leapfrog method almost overlaps that obtained by SPICE.

the implicit integration. As a result, the leapfrog method is much faster than the SPICE simulation which uses implicit numerical integration for transient analysis.

The update rules of the leapfrog method for the twolayer CNN are described by

$$\frac{v_{x1ij}(t_{i+1}) - v_{x1ij}(t_i)}{t_{i+1} - t_i} = -v_{x1ij}(t_{i+1}) \\

+ \sum_{C(k,l) \in N_r(i,j)} A_1(i, j; k, l) v_{y1kl}(t_{i+1}) \\

+ \sum_{C(k,l) \in N_r(i,j)} B_1(i, j; k, l) v_{u1kl}(t_{i+1/2}) \\

+ \sum_{C(k,l) \in N_r(i,j)} C_1(i, j; k, l) v_{y2kl}(t_{i+1/2}) + I_1, \quad (12)$$

$$\frac{v_{x2ij}(t_{i+1/2}) - v_{x2ij}(t_{i-1/2})}{t_{i+1/2} - t_{i-1/2}} = -v_{x2ij}(t_{i+1/2}) \\

+ \sum_{C(k,l)\in N_r(i,j)} A_2(i, j; k, l)v_{y2kl}(t_{i+1/2}) \\

+ \sum_{C(k,l)\in N_r(i,j)} B_2(i, j; k, l)v_{u2kl}(t_i) \\

+ \sum_{C(k,l)\in N_r(i,j)} C_2(i, j; k, l)v_{y1kl}(t_i) + I_2.$$

(13)

In (12) and (13), since  $A_1(i, j; i, j)$  and  $A_2(i, j; i, j)$  are nonzero and the other values of A templates are zero, it is not necessary to solve a set of linear equations for updating the state vectors.

We simulated the example of  $3 \times 4$  cells using the leapfrog method. Figure 5 shows the transient voltage waveform at the output resister  $R_{out}$  shown in Fig. 3(b). To obtain the result, the time step size was taken as 100 times larger than the forward Euler method in the case of Fig. 4(a), which means that the leapfrog method is robust for a stiff problem, though implicit integration is not used.

**Fig. 6** Updated points of the state vectors in implicit numerical integration and the leapfrog methods.

It should be noted that the leapfrog method is restricted by the Courant condition which gives the allowable largest time step size h in order to ensure the stability. The Courant condition is obtained as

$$h \le \sqrt{L_{min}C_{min}},\tag{14}$$

where  $L_{min}$  and  $C_{min}$  are minimum inductance and capacitance, respectively [9]. If the normalized time of (3) is  $\tau = 1/\sqrt{L_{min}C_{min}}$ , the Courant condition becomes  $t_{i+1} - t_i \leq 1$ . Putting the time step size as  $t_{i+1} - t_i = 1$ , we can obtain the discrete time model, which is a Discrete Time CNN (DT-CNN) [12], [13].

### 4. Examples

To show the performance of the proposed method via twolayer CNN-based modeling, the plane circuit shown in Fig. 3(a) was analyzed. The plane circuit is divided into identical cells which are modeled by an RLC  $\pi$ -model [4], and the equivalent circuit is obtained as Fig. 3(b). Based on the electromagnetic theory, the parameters of the RLC  $\pi$ -model corresponding to a package are determined as R = $1.73 \times 10^{-3}$  [ $\Omega$ ],  $L = 2.26 \times 10^{-9}$  [H], and  $C = 9.15 \times 10^{-15}$  [F] [4].

We calculated the transient responses of the CNN by the leapfrog method and compared with Berkeley SPICE (*ngspice*) [14]. The CNN simulations were carried out by Matlab 7 on Federa Core 3. The CPU times of CNN and SPICE simulations were measured on Pentium 4 with 3 GHz clock and 1 GByte memory.

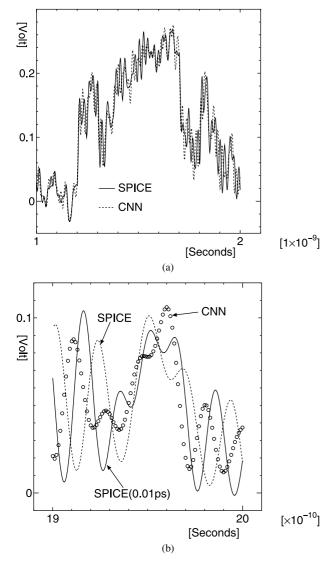

The linear circuit shown in Fig. 3(b) was driven by a current source of 0.1 [ns] fall/rise time, 0.4 [ns] pulse width, 0.2 [ns] delay time, 1.0 [ns] period, and 5 [mA] amplitude at 'Port1.' The transient analysis was carried out for the time interval from 0 [ns] to 2.0 [ns] using 1 [ps] time step size. Table 1 shows the comparison of CPU times. For  $320 \times 320$  cells, the proposed method via the two-layer CNN-based modeling is 1,553 times faster than *ngspice*. To investigate accuracy of the proposed method, we calculated the transient waveforms for  $10 \times 10$  cells. Figure 7(a) shows the transient voltage waveforms at 'Port1.' The result obtained via the SPICE.

| •                |          |        | *         |          |  |

|------------------|----------|--------|-----------|----------|--|

| cells            | elements | CNN    | ngspice   | Speed-up |  |

| $10 \times 10$   | 341      | 0.53   | 2.33      | 4.4      |  |

| $20 \times 20$   | 1281     | 0.74   | 19.567    | 26.44    |  |

| $40 \times 40$   | 4961     | 1.79   | 155.56    | 86.90    |  |

| $80 \times 80$   | 19521    | 6.25   | 1400.10   | 224.02   |  |

| $160 \times 160$ | 77441    | 32.68  | 16535.75  | 505.99   |  |

| $320 \times 320$ | 308481   | 152.09 | 236199.93 | 1553.03  |  |

Table 1

Comparison of CPU times for transient simulation of a plane circuit.

**Fig.7** Transient responses calculated by the proposed method and SPICE. (a) The responses are calculated by h = 1 [ps]. (b) The enlarged responses of (a) and the SPICE simulation result obtained by using h = 0.01 [ps].

Enlarging the waveforms from 1.9 [ns] to 2.0 [ns], there exist differences between the proposed method ('CNN') and SPICE in Fig. 7(b), where 1 [ps] time step size was used in both the proposed method and SPICE simulation. Using 0.01 [ps] time step, we carry out the SPICE simulation, the result of which is shown as 'SPICE(0.01ps)' in Fig. 7(b). Since a small time step is taken, 'SPICE(0.01ps)' would be more accurate than 'CNN' and 'SPICE.' However, comparing 'SPICE(0.01ps)' with 'CNN' and 'SPICE,' we cannot judge which is more accurate, 'CNN' or 'SPICE.' Therefore, both methods are of the same accuracy. Since efficiency of the proposed method is remarkable as listed in Table 1, the leapfrog method via the CNN-based modeling for analyzing plane circuit is better than implicit/explicit numerical integration. We do not consider any parallelism of CNN. If a hardware accelerator for simulating the two-layer CNN is realized, further speed-up can be expected.

## 5. Conclusions

In this paper, a fast simulation of the plane circuits using the CNN-based modeling has been presented, where the Maxwell's equations of plane circuits are expressed by the two-layer CNN and the dynamics of the two-layer CNN is calculated by the leapfrog method. Since the proposed method is very fast on a single processor, it might be extremely fast using any hardware accelerators. The leapfrog method is based on the FDTD methods [10]. Therefore, the hardware accelerators would be extended to full wave analysis of electromagnetic field.

#### References

- T. Roska, L.O. Chua, D. Wolf, T. Kozek, R. Tetzlaff, and F. Puffer, "Simulating nonlinear waves and partial differential equations via CNN—Part I," IEEE Trans. Circuits Syst., vol.42, no.10, pp.807– 815, 1995.

- [2] T. Roska, L.O. Chua, D. Wolf, T. Kozek, R. Tetzlaff, and F. Puffer, "Simulating nonlinear waves and partial differential equations via CNN—Part II," IEEE Trans. Circuits Syst., vol.42, no.10, pp.816– 820, 1995.

- [3] M.W. Beattie and L.T. Pileggi, "Modeling magnetic coupling for on-chip interconnect," Proc. 38th Design Automation Conference, 2001.

- [4] T. Watanabe, K. Srinivasan, H. Asai, and M. Swaminathan, "Modeling of power distribution networks with retardation using the transmission matrix method," Proc. EPEP'04, 2004.

- [5] Z. Yang, Y. Nishio, and A. Ushida, "Generation of various types of spatio-temporal phenomena in two-layer cellular neural networks," IEICE Trans. Fundamentals, vol.E87-A, no.4, pp.864–871, April 2004.

- [6] L.O. Chua and T. Roska, "The CNN universal machine," IEEE Trans. Circuits Syst. II, vol.40, no.3, pp.163–173, 1993.

- [7] L.O. Chua and P.-M. Lin, Computer-aided analysis of Electrical Circuits: Algorithms and Computational Techniques, Prentice-Hall, Englewood Cliffs, 1975.

- [8] L.O. Chua, "Passivity and complexity," IEEE Trans. Circuits Syst. I, vol.46, no.1, pp.71–82, 1999.

- [9] J.E. Schutt-Aine, "Latency insertion method (LIM) for the fast transient simulation of large networks," IEEE Trans. Circuits Syst. I, vol.48, no.1, pp.81–89, 2001.

- [10] K.S. Yee, "Numerical solution of initial boundary value problems involving maxwell's equations in isotropic media," IEEE Trans. Antennas Propag., vol.14, no.4, pp.302–307, 1966.

- [11] H. Kubota, Y. Tanji, T. Watanabe, and H. Asai, "Generalized method of the time-domain circuit simulation based on LIM with mna formulation," Proc. 2005 IEEE Custom Integrated Circuits Conference, 2005.

- [12] H. Harrer and J.T. Nossek, "Discrete-time cellular neural networks," Int. J. Circuit Theory Appl., vol.20, pp.453–467, 1992.

- [13] M. Ikegami and M. Tanaka, "Image coding and decoding by discrete time cellular neural networks," IEICE Trans. Fundamentals (Japanese Edition), vol.J77-A, no.7, pp.954–964, July 1994.

- [14] http://ngspice.sourceforge.net/

- [15] N. Na, J. Choi, S. Chun, and M. Swaminathan, "Modeling and transient simulation of planes in electromagnetic packages," IEEE Trans. Comp., Packag., Manufact. Technol. B, vol.23, no.3, pp.340– 352, Aug. 2000.

Masayoshi Oda received the B.E. and the M.E. degrees from Electrical and Electronic Engineering from Tokushima University, Tokushima Japan, in 2005 and 2007. His research interests include the computer-aided design technology.

Yoshifumi Nishio received B.E., M.E., and Ph.D. degrees in electrical engineering from Keio University, Yokohama Japan, in 1988, 1990, and 1993, respectively. In 1993, he joined the Department of Electrical and Electronic Engineering at Tokushima University, Tokushima Japan, where he is currently an Associate Professor. From May 2000 he spent a year in the Laboratory of Nonlinear Systems (LANOS) at the Swiss Federal Institute of Technology Lausanne (EPFL) as a Visiting Professor. His re-

search interests include analysis and application of chaos in electrical circuits, analysis of synchronization in coupled oscillatory circuits, development of analyzing methods for nonlinear circuits, theory and application of cellular neural networks, and neural network architecture. He was the Chair of the IEEE CAS Society Technical Committee on Nonlinear Circuits and Systems (NCAS) during 2004-2005, the Steering Committee Secretary of the IEICE Research Society of Nonlinear Theory and its Applications (NOLTA) during 2004-2007, and is currently the Secretary/Treasurer of the IEEE CAS Society Shikoku Chapter. He was an Associate Editor of the IEEE Transactions on Circuits and Systems-I: Regular Papers during 2004-2005, and is currently serving as an Associate Editor for the IEEE CAS Magazine, the IEEE CAS Society Newsletter, and the RISP Journal of Signal Processing. He is also the Editor of the IEICE Fundamentals Review and is a member of the Editorial Board of International Journal of Circuit Theory and Applications. He is a senior member of the IEEE, and a member the RISP.

Akio Ushida received the B.E. and M.E. degree in Electrical Engineering from Tokushima University in 1961 and 1966, respectively, and the Dr. degree in Electrical Engineering from University of Osaka Prefecture in 1974. From 1980 to 2003, he was a Professor in Department of Electrical and Electronic Engineering at Tokushima University. Since 2003, he has been with the Department of Mechanical-Electronic Engineering, Tokushima Bunri University. From 1974 to 1975, he spent one year

as a visiting scholar at the Department of Electrical Engineering and Computer Sciences at the University of California, Berkeley. His current research interests include numerical methods and computer-aided analysis of nonlinear circuits. Dr. Ushida is Senior member of the IEEE.

Yuichi Tanji received the B.E., M.E., and Ph.D. degrees from Tokushima University, Tokushima, Japan, in 1993, 1995 and 1998, respectively. After graduation, he held Research Associate positions at Sophia University and Kagawa Univesity, and is currently an Associste Professor of the Department of Reliabilitybased Information Systems Engineering at Kagawa University. His research interests are in circuit simulation, artificial neural networks, and image and signal processing. Dr. Tanji is a

member of the IEEE.

Hideki Asai received the B.E., M.E., and Ph.D. degrees in electrical engineering from Keio University, Yokohama, Japan, in 1980, 1982, and 1985, respectively. In 1985, he was with the Department of Electrical and Electronics Engineering, Sophia University, Tokyo, Japan. He was a Visiting Professor at Carleton University, Ottawa, ON, Canada, and Santa Clara University, Santa Clara, CA (1999–2000). Since 1986, he has been with Shizuoka University, Hamamatsu, Japan, where he is currently

a Professor involved with VLSI-CAD and electrical design automation (EDA), analog circuit design, and neural networks. He is an author of the books, "Exercise Notes of Digital Circuits, CORONA PUBLISHING. CO., LTD., 2001" and "Electronic Circuit Simulation Techniques, SCI TECHS PRESS, 2003." Dr. Asai is a member of the IEEE Nonlinear Circuits and Systems Technical Committee. He was a secretary for the IEEE Circuits and Systems Society Tokyo Chapter (1994–1995), and a chairman of the Technical Group on Nonlinear Problems of the Institute of Electronics, Information and Communication Engineers (IEICE) (2007–2008). He is now a chairman of the Technical Group on System Packaging CAE of JIEP. He was the recipient of the Research Encouragement Awards on the occasion of the Takayanagi anniversary, the 50th anniversary of the founding of the IEICE Tokai branch, and on the occasion of the Saitoh anniversary in 1988, 1989, and 1993, respectively.