# A Fast Voltage Detection Method for Grid-tied Renewable Energy Generation Systems under Distorted Grid Voltage Conditions

Furong Xiao<sup>1</sup>, Lei Dong<sup>1</sup>, Li Li<sup>2</sup>, Xiaozhong Liao<sup>1</sup>

<sup>1</sup> School of Automation, Beijing Institute of Technology, Beijing, China

<sup>2</sup> Faculty of Engineering and Information Technology, University of Technology, Sydney, Australia

## Corresponding Author: Lei Dong, Associate Professor, School of Automation in Beijing Institute of Technology Email: correspondent dong@163.com

*Abstract-* A fast voltage detection method to assist with the low voltage ride-through (LVRT) operation of gridtied renewable energy generation systems is proposed in this paper. It is designed to detect every phase voltage so that it can be applied in both three-phase and single-phase applications. The whole voltage detection approach consists of two stages, the pre-filtering stage and the voltage detection stage. In the pre-filtering stage, a cascaded delayed signal cancellation (CDSC) module and a low-pass filter are connected in series to filter low-order harmonics and high-frequency noises. For eliminating the low-order harmonics of interest, different types of CDSC methods are studied in detail. Subsequently, a new orthogonal signal generator (OSG) is built to calculate the voltage amplitude in the voltage detection stage. Finally, the proposed voltage detection method is verified by experimental results.

*Index Terms*—voltage detection, cascaded delayed signal cancellation, orthogonal signal generator, harmonic cancellation.

Along with the increasing penetration of distributed renewable energy generation systems, the grid stability and reliability are now facing significant challenges [1]. Especially, during the grid fault period, the behaviors of grid-tied converters have a significant impact on the grid stability. For instance, sudden disconnection of massive renewable power plants from the grid during voltage sag faults may trigger more severe problems than the initial event such as power outage and voltage flicker [2] [3]. Hence, many countries have enacted their grid codes to guide the operation of grid-tied renewable power systems [4] [5]. These new grid codes require grid-tied converters be capable of low voltage ride-through (LVRT) when suffering grid voltage sag.

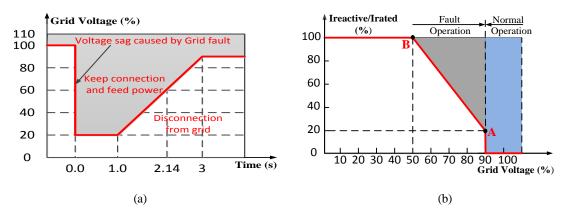

Fig. 1. LVRT requirements (a) China: Q/GDW 617-2011. (b) The E.ON code for LVRT.

Fig. 1(a) shows the Chinese LVRT standard for large-capacity grid-tied photovoltaic (PV) inverters. As shown, PV inverters should stay connected to the grid in the shaded area. Besides, they are also required to provide reactive power for dynamic network support during the fault period and in the recovery process [6]. The E.ON code shown in Fig. 1(b) defines the amount of injected reactive current during LVRT. The injection of reactive power should be sufficiently fast, e.g., the PV system should deliver the required reactive power within 30 ms [7]. Moreover, faster detection of the voltage sag means that the grid-tied converter has more respond time, which is beneficial for the converter safety. Therefore, the voltage variation ratio should be detected as fast as possible.

Since the grid-tied converter is required to respond according to the variation of either line voltage or phase

voltage [7], the adopted voltage detection method should have the capability of detecting each phase voltage. Consequently, conventional voltage detection approaches based on three-phase phase locked loop (PLL) such as DQ transformation method [8], cannot satisfy the new requirements. Several other voltage detection methods have been proposed in the literature, e.g., the RMS voltage detection [9], the peak voltage detection [10], and the discrete Fourier transform (DFT) [11] [12] [13], whose detection speed is too slow for LVRT operation. The peak voltage detection method maximally introduces half grid cycle delay, while both the RMS and FFT related methods induce one grid cycle delay [14]. Furthermore, for ensuring an accurate detection of the grid voltage under distorted conditions, the low-order harmonics and unbalanced variations of the grid voltage should be considered during the design. The current solutions are to either insert a digital filter into the PLLs [15] [16] [17], or use the positive and negative component separation methods [18] [19] to extract the fundamental voltage component for calculating the grid voltage. Note that, detecting each phase voltage separately with three independent single-phase PLLs is also valid for unbalanced voltage variations. However, as a matter of fact, the settling time of PLL related methods generally cannot be less than one grid cycle so that PLLs are not suitable for detecting the grid voltage variation ratio during LVRT operation. [14] presents a new detection method which is to detect both the maximum and zero voltage points. Its response time is affected by the position at which the voltage variation occurs, and the largest time delay is 10.1 ms.

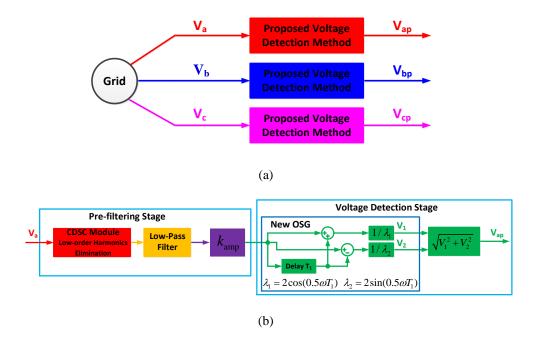

To meet the requirement of LVRT operation, a new voltage detection scheme is designed for detecting the grid voltage variation ratio as fast as possible, while providing high detection accuracy under generally distorted conditions. In this work, every phase voltage is detected separately as shown in Fig. 2. Since the delayed signal cancellation (DSC) technique has the advantages of easy implementation and less computational burden [20] [21] [22], a cascaded DSC (CDSC) module is used to eliminate the low-order odd harmonics of the sampled grid voltage signal in the pre-filtering stage. In addition, a low-pass filter is employed to filter possible high-

frequency noises. Next, a new orthogonal signal generator (OSG) is built to calculate the voltage amplitude in the voltage detection stage. The main contribution of this paper is developing a new OSG with fast dynamic speed. Also, a new harmonic cancellation method is introduced. Finally, a fast and accurate detection of the grid voltage can be achieved with the proposed method.

Fig. 2. (a) The voltage detection approach for three-phase systems. (b) The proposed voltage detection method for each phase.

## II Proposed Orthogonal Signal Generator (OSG) for Voltage Detection

Given the same detection principle of each phase voltage in Fig. 2, only the phase a  $V_a(t) = V_{ap} \sin(\omega t)$ , where  $V_{ap}$  is the voltage amplitude and  $\omega$  is the angular frequency, is analyzed in this paper. Generally, an orthogonal signal  $V_{\beta}$  with respect to  $V_a$  can be generated with the OSG technique so that the voltage amplitude can be given by  $V_{ap} = \sqrt{V_a^2 + V_{\beta}^2}$ . The second order generalized integrator (SOGI) [23], the quartercycle delay [24], and the first-order differential method [25] [26], are three typical OSG methods. SOGI provides low computation burden and strong filtering capability. However, it gives a settling time of more than half of the fundamental period [27]. The quarter-cycle delay introduces a time delay of one fourth of the fundamental period. Comparatively, the first-order differential method, which can derive the orthogonal signal in one sampling period, is the fastest OSG. As well known, higher accuracy of the first-order differential method requires higher sampling frequency, yet the high-frequency noise in the sampling process will be further amplified inevitably. To deal with these issues, a fast OSG algorithm, which is characterized by noise immunity and high accuracy in a wide range of sampling frequencies, is hereby proposed as

$$V_{1}(t) = \frac{V_{a}(t) + V_{a}(t - T_{1})}{\lambda_{1}} = \frac{V_{ap} \sin(\omega t) + V_{ap} \sin(\omega t - \omega T_{1})}{2\cos(0.5\omega T_{1})} = V_{ap} \sin(\omega t - 0.5\omega T_{1})$$

$$V_{2}(t) = \frac{V_{a}(t) - V_{a}(t - T_{1})}{\lambda_{2}} = \frac{V_{ap} \sin(\omega t) - V_{ap} \sin(\omega t - \omega T_{1})}{2\sin(0.5\omega T_{1})} = V_{ap} \cos(\omega t - 0.5\omega T_{1})$$

(1)

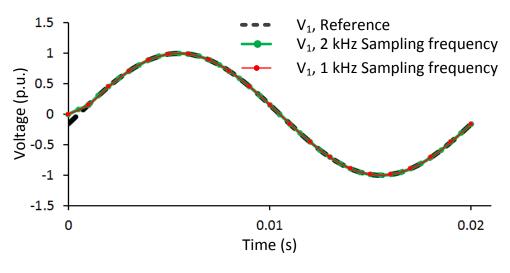

in which,  $T_1$  is a predetermined delay time, and  $\lambda_1$  and  $\lambda_2$  are functions of  $T_1$  and the grid frequency  $\omega$ . Different from previous OSGs, the developed OSG creates an orthogonal frame of  $V_{ap} \sin(\omega t - 0.5\omega T_1)$  and  $V_{ap} \cos(\omega t - 0.5\omega T_1)$  instead of  $V_{ap} \sin(\omega t)$  and  $V_{ap} \cos(\omega t)$ . It is worth noting that (1) is obtained by rigorous mathematical deduction without any approximation so that the accuracy of the proposed OSG is independent of the sampling frequency (see Fig. 3). From (1), the voltage amplitude can be achieved as  $V_{ap} = \sqrt{V_1^2 + V_2^2}$ .

Note that  $T_1$  is the only parameter which needs to be tuned in the proposed OSG. In what follows, the design considerations of  $T_1$  are derived. Considering the high-frequency random noise  $V_x$  in the sampling process as  $\tilde{V}_a(t) = V_a(t) + V_x(t)$ , (1) can be rewritten as

$$\begin{split} \tilde{V}_{1}(t) &= \frac{\tilde{V}_{a}(t) + \tilde{V}_{a}(t - T_{1})}{2\cos(0.5\omega T_{1})} = \frac{[V_{ap}\sin(\omega t) + V_{x}(t)] + [V_{ap}\sin(\omega t - \omega T_{1}) + V_{x}(t - T_{1})]}{2\cos(0.5\omega T_{1})} \\ &= V_{ap}\sin(\omega t - 0.5\omega T_{1}) + \frac{V_{x}(t) + V_{x}(t - T_{1})}{2\cos(0.5\omega T_{1})} \\ &= V_{ap}\sin(\omega t - 0.5\omega T_{1}) + V_{1n} \\ \tilde{V}_{2}(t) &= \frac{\tilde{V}_{a}(t) - \tilde{V}_{a}(t - T_{1})}{2\sin(0.5\omega T_{1})} = \frac{[V_{ap}\sin(\omega t) + V_{x}(t)] - [V_{ap}\sin(\omega t - \omega T_{1}) + V_{x}(t - T_{1})]}{2\sin(0.5\omega T_{1})} \\ &= V_{ap}\cos(\omega t - 0.5\omega T_{1}) + \frac{V_{x}(t) - V_{x}(t - T_{1})}{2\sin(0.5\omega T_{1})} \\ &= V_{ap}\cos(\omega t - 0.5\omega T_{1}) + \frac{V_{x}(t) - V_{x}(t - T_{1})}{2\sin(0.5\omega T_{1})} \end{split}$$

(2)

The physical quantities with superscript  $\sim$  in this paper indicate the existence of random noise. In (2)

$$|V_{1n}| = \frac{|V_x(t) + V_x(t - T_1)|}{|2\cos(0.5\omega T_1)|} \le \frac{|V_x(t)| + |V_x(t - T_1)|}{|2\cos(0.5\omega T_1)|} \le \frac{|V_x|}{|\cos(0.5\omega T_1)|} = k_1 |V_x|$$

$$|V_{2n}| = \frac{|V_x(t) - V_x(t - T_1)|}{|2\sin(0.5\omega T_1)|} \le \frac{|V_x(t)| + |V_x(t - T_1)|}{|2\sin(0.5\omega T_1)|} \le \frac{|V_x|}{|\sin(0.5\omega T_1)|} = k_2 |V_x|$$

(3)

(a) Generated Signal  $V_1$ .

(b) Generated signal  $V_2$ .

Fig. 3. Orthogonal signals constructed by the proposed OSG under different sampling frequencies.

where,  $k_1$  and  $k_2$  are the possible maximal noise amplification factors of the developed OSG in the worst condition. Since  $T_1$  is designed below 0.25 grid periods for the sake of fast response,  $k_1$  is smaller than  $k_2$ so that  $k_2$  is mainly considered during the tuning of  $T_1$ . Obviously,  $k_2$  decreases remarkably and the response time increases linearly with the increased  $T_1$ . Consequently, it is necessary to find a good compromise between noise reduction and response speed. Industrial experience suggests that a noise amplification factor of 10 can fully meet the precision requirement in most cases [28]. Considering the required fast detection of voltage sags during LVRT applications,  $T_1$  is set as 1 ms so that  $k_1 = 1.01$  and  $k_2 = 6.4$ . Namely, the response time of the designed OSG is 1 ms in this work. The possible high-frequency noises can be rejected by a low-pass filter with 1 kHz cutoff frequency in the pre-filtering stage as shown in Fig. 2 (b).

Note that, (1) is derived on the premise of known grid frequency  $\omega$ . Generally, the grid frequency is often measured with a PLL in grid-tied converters. Therefore, it is reasonable to assume the grid frequency is known for implementing the proposed OSG. The frequency  $\omega$  for calculating  $\lambda_1$  and  $\lambda_2$  should only update after the PLL settles to a new steady state. Consequently, the dynamic process of the PLL in response to voltage variations (amplitude or phase angle jump) does not affect the performance of voltage detection. In practice,

the allowable variation range of the grid frequency is generally small in normal operation mode such as 0.2 Hz in China, which has negligible influence on the accuracy of the developed voltage detection method. Hence, this paper mainly focuses on the grid voltage variation cases.

## III Proposed Voltage Detection Method under Distorted Conditions

To accurately detect the grid voltage under distorted conditions, a CDSC module is used to filter the sampled grid voltage signal before sending it to the voltage detection stage. The 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonics are considered in this work because these harmonics are dominant low-order harmonics in the grid [14], [29]. It should be mentioned that this method is not restrictive, and can be extended to more harmonics.

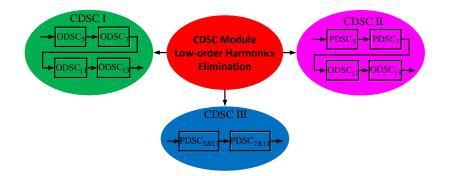

Fig. 4. Three types of CDSC methods for eliminating the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonics.

## A. CDSC Method I

The CDSC method I (see Fig. 4) based on the original delayed signal cancellation (ODSC) [20] [21] [22] is used for cancelling the concerned harmonics. For the sake of simplicity, the grid voltage with only the n<sup>th</sup> odd harmonic as  $V_a(t) = V_{ap} \sin(\omega t + \theta_1) + V_n \sin(n\omega t + \theta_n)$  is assumed for illustrating the operator ODSC<sub>n</sub>. The output ODSC<sub>no</sub> of ODSC<sub>n</sub> is given by

$$ODSC_{no}(t) = V_a(t) + V_a(t - t_d) = V_a(t) + V_a(t - \frac{T_f}{2n})$$

=  $V_{ap} \sin(\omega t + \theta_1) + V_n \sin(n\omega t + \theta_n) + V_{ap} \sin(\omega t + \theta_1 - \frac{\pi}{n}) + V_n \sin(n\omega t + \theta_n - \pi)$  (4)

=  $2V_{ap} \cos(\frac{\pi}{2n}) \sin(\omega t + \theta_1 - \frac{\pi}{2n})$

in which,  $T_f$  is the fundamental period and  $t_d$  is the delay time. It is clear that the output does not contain the n<sup>th</sup> odd harmonic, while the fundamental component suffers from fixed amplitude and phase angle shift. Note that, the n<sup>th</sup> odd harmonic can be removed by ODSC<sub>n</sub> only when  $t_d = T_f / (2n)$ . The total delay time of the CDSC Method I is  $0.255T_f$ , i.e., 5.1 ms for a 50 Hz power system (the grid frequency is assumed to be always 50 Hz in the following discussions).

#### B. CDSC Method II

We firstly introduce a proposed delayed signal cancellation (PDSC) operator PDSC<sub>n</sub> for cancelling the n<sup>th</sup> odd harmonic. Similarly, the input  $V_a(t) = V_{ap} \sin(\omega t + \theta_1) + V_n \sin(n\omega t + \theta_n)$  is used to illustrate the PDSC<sub>n</sub> as

$$PDSC_{no}(t) = V_{a}(t) + V_{a}(t - t_{d}) - 2\cos(0.5n\omega t_{d})V_{a}(t - 0.5t_{d})$$

$$= V_{ap}\sin(\omega t + \theta_{1}) + V_{n}\sin(n\omega t + \theta_{n}) + V_{ap}\sin(\omega t + \theta_{1} - \omega t_{d}) + V_{n}\sin(n\omega t + \theta_{n} - n\omega t_{d})$$

$$- 2\cos(0.5n\omega t_{d})[V_{ap}\sin(\omega t + \theta_{1} - 0.5\omega t_{d}) + V_{n}\sin(n\omega t + \theta_{n} - 0.5n\omega t_{d})]$$

$$= 2[\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})]V_{ap}\sin(\omega t + \theta_{1} - 0.5\omega t_{d})$$

(5)

It is obvious that the n<sup>th</sup> odd harmonic is eliminated for any given  $t_d > 0$ . A close observation of (4) and (5) reveals that ODSC<sub>n</sub> is a special case of PDSC<sub>n</sub> with  $t_d = T_f / (2n)$ . Next, how to design PDSC<sub>n</sub> for eliminating the n<sup>th</sup> odd harmonic with less time delay is given. Considering the high-frequency random noise  $V_x$  in the sampling process as  $\tilde{V}_a(t) = V_a(t) + V_x(t)$ , (5) can be rewritten as

$$PDS\tilde{C}_{no}(t) = \tilde{V}_{a}(t) + \tilde{V}_{a}(t - t_{d}) - 2\cos(0.5n\omega t_{d})\tilde{V}_{a}(t - 0.5t_{d})$$

$$= 2[\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})]V_{ap}\sin(\omega t + \theta_{1} - 0.5\omega t_{d})$$

$$+ [V_{x}(t) + V_{x}(t - t_{d}) - 2\cos(0.5n\omega t_{d})V_{x}(t - 0.5t_{d})]$$

(6)

The ratio of the random noise to the amplitude of the fundamental component in (6) is defined as

$$F(t_{d},n) = \frac{|V_{x}(t) + V_{x}(t - t_{d}) - 2\cos(0.5n\omega t_{d})V_{x}(t - 0.5t_{d})|}{|2[\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})]V_{ap}|}$$

$$\leq \frac{|V_{x}| + |V_{x}| + |2\cos(0.5n\omega t_{d})||V_{x}|}{|2[\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})]V_{ap}|} = k_{3}(t_{d},n)\frac{|V_{x}|}{V_{ap}}$$

(7)

where  $k_3(t_d, n)$  is termed as the possible maximal noise amplification factor of PDSC<sub>n</sub> in the worst case. While in ODSC<sub>n</sub>

$$ODS\tilde{C}_{no}(t) = [\tilde{V}_{a}(t) + \tilde{V}_{a}(t - \frac{T_{f}}{2n})] = 2V_{ap}\cos(\frac{\pi}{2n})\sin(\omega t + \theta_{1} - \frac{\pi}{2n}) + [V_{x} + V_{x}(t - \frac{T_{f}}{2n})]$$

$$F(\frac{T_{f}}{2n}, n) = \frac{|V_{x} + V_{x}(t - \frac{T_{f}}{2n})|}{|2\cos(\frac{\pi}{2n})V_{ap}|} \le \frac{|V_{x}|}{|\cos(\frac{\pi}{2n})|V_{ap}} = k_{3}(\frac{T_{f}}{2n}, n)\frac{|V_{x}|}{|V_{ap}|}$$

(8)

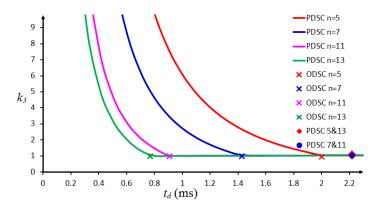

Fig. 5 shows the relationship of the noise amplification factor versus the delay time. It is obvious that the noise amplification factor  $k_3(t_d, n)$  of PDSC<sub>n</sub> decreases with the increased  $t_d$  in the shown range. In terms of LVRT operation, a faster detection of the grid voltage variation ratio is preferred. Therefore,  $k_3$  is set to around 3 so that the total delay time of four cascaded PDSC<sub>n</sub> (n= 5, 7, 11, 13) operators is 3.43 ms, which is 1.67 ms less than that (5.1 ms) of the CDSC method I. However, the possible maximal noise amplification factor of such four PDSC blocks is 81, which may be not preferred in practice. Alternatively, the 5<sup>th</sup> and 7<sup>th</sup> harmonics are eliminated with PDSC<sub>5</sub> and PDSC<sub>7</sub>, respectively, and the 11<sup>th</sup> and 13<sup>th</sup> harmonics are removed with ODSC<sub>11</sub> and ODSC<sub>13</sub>, respectively, as shown in Fig. 4. This method provides 4 ms time delay with the total noise amplification factor of 9, and is called the CDSC method II.

Fig. 5. The noise amplification factor versus the delay time.

#### C. CDSC Method III

In previous discussions, either ODSC<sub>n</sub> or PDSC<sub>n</sub> is designed to eliminate only the n<sup>th</sup> odd harmonic so that four DSC blocks are needed for cancelling the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonics. In this section, a new operator PDSC<sub>n&m</sub> with  $t_d = 2T_f / (n+m)$  is used to remove the n<sup>th</sup> and m<sup>th</sup> odd harmonics (m>n) simultaneously, so that the number of cascaded blocks can be reduced by half, with the resulting reduced computation and delay time. The principle of PDSC<sub>n&m</sub> is illustrated as follows:

$$V_{a}(t) = V_{ap} \sin(\omega t + \theta_{1}) + V_{n} \sin(n\omega t + \theta_{n}) + V_{m} \sin(m\omega t + \theta_{m})$$

$$PDSC_{n\&mo}(t) = V_{a}(t) + V_{a}(t - t_{d}) - 2\cos(0.5n\omega t_{d})V_{a}(t - 0.5t_{d})$$

$$= 2[\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})]V_{ap} \sin(\omega t + \theta_{1} - 0.5\omega t_{d})$$

(9)

To eliminate the 5<sup>th</sup> and 13<sup>th</sup> harmonics,  $t_d$  of PDSC<sub>5&13</sub> should be  $T_f/9$ . Similarly, PDSC<sub>7&11</sub> with  $t_d = T_f/9$  can remove both the 7<sup>th</sup> and 11<sup>th</sup> harmonics. Therefore, only two cascaded blocks, PDSC<sub>5&13</sub> and PDSC<sub>7&11</sub>, are needed for eliminating the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> harmonics, and this method is named as the CDSC method III. With half number of the cascaded blocks, this approach can reduce the computational load compared with the CDSC I and II methods. In addition, the total delay time of the CDSC method III is 4.4 ms which is 0.7 ms less than that of the CDSC method I. From (7), the noise amplication factors of PDSC<sub>5&13</sub> and PDSC<sub>7&11</sub> can be derived as

$$k_{3}(\frac{T_{f}}{9},5) = \frac{(1+|\cos(0.5n\omega t_{d})|)}{|\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})|} = \frac{(1+|\cos(\frac{5\pi}{9})|)}{|\cos(\frac{\pi}{9}) - \cos(\frac{5\pi}{9})|} = 1.054, \text{ PDSC}_{5\&13}$$

$$k_{3}(\frac{T_{f}}{9},7) = \frac{(1+|\cos(0.5n\omega t_{d})|)}{|\cos(0.5\omega t_{d}) - \cos(0.5n\omega t_{d})|} = \frac{(1+|\cos(\frac{7\pi}{9})|)}{|\cos(\frac{\pi}{9}) - \cos(\frac{7\pi}{9})|} = 1.035, \text{ PDSC}_{7\&11}$$

(10)

The noise amplification factors of the designed  $PDSC_{5\&13}$  and  $PDSC_{7\&11}$  are close to one, which means the CDSC method III has nearly the same noise rejection capability as the CDSC method I according to Fig. 5. As analyzed above, due to the CDSC module, the fundamental component suffers from a fixed amplitude shift, which is compensated by using a factor  $k_{amp}$  as shown in Fig. 2(b). The compensating factors of different

CDSC methods are shown as

$$k_{amp} = \frac{1}{16\cos(\frac{\pi}{10})\cos(\frac{\pi}{14})\cos(\frac{\pi}{22})\cos(\frac{\pi}{26})} = 0.0686, \text{ CDSC I}$$

$$k_{amp} = \frac{1}{4[\cos(\frac{\pi}{100}) - \cos(\frac{\pi}{20})][\cos(\frac{9\pi}{200}) - \cos(\frac{63\pi}{200})]} \times \frac{1}{4\cos(\frac{\pi}{22})\cos(\frac{\pi}{26})} = 0.2021, \text{ CDSC II}$$

(11)

$$k_{amp} = \frac{1}{4[\cos(\frac{\pi}{9}) - \cos(\frac{5\pi}{9})][\cos(\frac{\pi}{9}) - \cos(\frac{\pi}{9})]} = 0.1316, \text{ CDSC III}$$

$$TABLE I$$

Detection time comparison of different methods considering low-order harmonic distortion

| Detection Method | FFT-based Methods | PLL-based Methods | RMS Method | Method        | Proposed method |         |          |

|------------------|-------------------|-------------------|------------|---------------|-----------------|---------|----------|

|                  | [11]-[13]         | [30] [31]         | [9]        | [Error!       | CDSC I          | CDSC II | CDSC III |

|                  |                   |                   |            | Bookmark      |                 |         |          |

|                  |                   |                   |            | not defined.] |                 |         |          |

| Detection Time   | 20 ms             | > 20 ms           | 20 ms      | 5 - 10.1 ms   | 6.6 ms          | 5.5 ms  | 5.9 ms   |

### D. Comparison with Previous Voltage Detection Methods

The detection time comparison between previous voltage detection methods, and the proposed ones with different harmonic cancellation methods is listed in Table I for the condition of three-phase unbalanced voltage drop with low-order harmonic distortion. The developed method can detect the voltage amplitude within 6.6 ms (CDSC I) or 5.5 ms (CDSC II) or 5.9 ms (CDSC III) when considering the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> harmonics. The detection time mentioned here is obtained considering both the pre-filtering stage and the voltage detection stage. It is worth mentioning that the detection time would increase slightly if more odd harmonics are considered. In terms of the detection time, the proposed methods are better than most of the previous methods

which can provide accurate voltage measurement under distorted conditions.

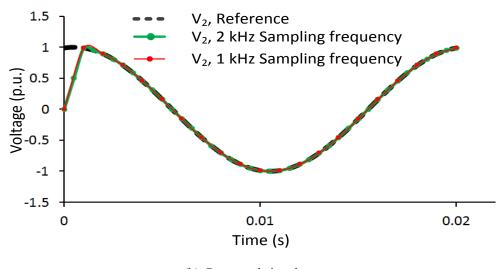

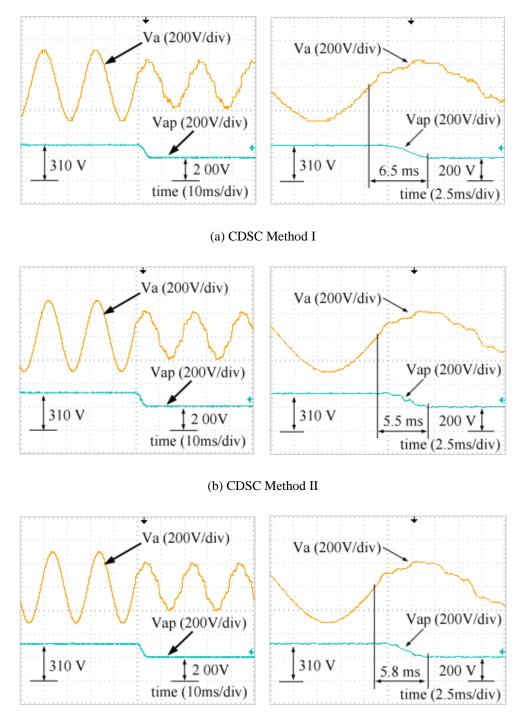

## IV Experimental Results

The proposed voltage detection method is verified experimentally on a DSP chip TMS30F28335-based platform. All the operations are conducted with 10 kHz sampling frequency. The normal voltage amplitude is 310 V and the dropped voltage amplitude is set to 200 V. Along with the voltage amplitude drop, the 5<sup>th</sup> (6%), 7<sup>th</sup> (4.8%), 11<sup>th</sup> (4%) and 13<sup>th</sup> (3.2%) voltage harmonics are added for testing the harmonic rejection performance of the developed voltage detection method. The corresponding experimental results are shown in Fig. 5. It can be observed that the detection method with CDSC I, CDSC II or CDSC III, can fast detect the voltage amplitude even under distorted grid voltages. The response time of the approach with PDSC (CDSC II or CDSC III) is less compared to the one (CDSC I) based on ODSC. The achieved reduction of the delay time by using PDSC is limited in this paper, however, the freedom to design the time delay as well as the possibility to reduce the number of cascaded modules makes PDSC interesting for applications related to harmonics cancellation.

## V Conclusions

This paper presents a fast voltage detection method to assist with the LVRT operation of grid-tied renewable energy generation systems. With the proposed approach, the amplitude of each phase voltage can be measured in a fast and accurate way under generally distorted conditions. Firstly, a new OSG with fast response speed is analyzed in detail. The benefit of adopting the new OSG is that the detection time of the grid voltage is significantly reduced. Secondly, based on DSC, a novel harmonic cancellation block is developed such that both the delay time and number of the cascaded DSC blocks for eliminating the low-order harmonics of interest

can be reduced. Finally, the presented voltage detection method is verified by experimental results.

(c) CDSC Method III

Fig. 5. Experimental results of the proposed voltage detection method.

References

[1] S. Yang, Q. Lei, F. Z. Peng, and Z. Qian, "A robust control scheme for grid-connected voltage-source inverters," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 202–212, Jan. 2011.

[2] K. O. Kovanen, "Photovoltaics and power distribution," Renewable Energy Focus, vol. 14, no. 3, pp. 20-21, 2013.

[3] Y. Bae, T. K. Vu and R. Y. Kim, "Implemental control strategy for grid stabilization of grid-connected PV system based on German

grid code in symmetrical low-to-medium voltage network," IEEE Trans. Energy Convers., vol. 28, no. 3, pp. 619-631, Sep. 2013.

[4] E.ON Netz GmbH, Grid code high and extra high voltage Bayreuth, Germany: E.ON Netz GmbH, Apr. 2006.

[5] Energinet, "Regulation TF 3.2.5 wind turbines connected to grids with voltages above 100 kV," Denmark, Dec. 2010.

[6] A. Marinopoulos, F. Papandrea, M. Reza, S. Norrga, F. Spertino and R. Napoli, "Grid integration aspects of large solar PV installations: LVRT capability and reactive power/voltage support requirements," IEEE PowerTech Conference, Trondheim, pp. 1-8, 2011.

[7] Technical requirements for connecting photovoltaic power station to power system, Tech. Rep. GB/T 19964-2012, China, Dec. 2012.

[8] Y. Kumsuwan and Y. Sillapawicharn, "A fast synchronously rotating reference frame-based voltage sag detection under practical grid voltages for voltage sag compensation systems," in Proc. 6th IET Int. Conf. Power Electron. Mach. Drives, 2012, pp. 1–5.

[9] E. Styvaktakis, M. H. J. Bollen Seniorand, and I. Y. H. Gu, "Automatic classification of power system events using rms voltage measurements," in Proc. Power Eng. Soc. Summer Meet., 2002, pp. 824–829.

[10] R. Naidoo and P. Pillay, "A new method of voltage sag and swell detection," IEEE Trans. Power Del., vol. 22, no. 2, pp. 1056– 1063, Apr. 2007.

[11] W. H. Zou and S. P. Su, "Voltage flicker detection based on wavelet Fourier transform," in Proc. Int. Conf. Elect. Control Eng., 2011, pp. 4218–4220.

[12] E. Jacobsen and R. Lyons, "The sliding DFT," IEEE Signal Process.Mag., vol. 20, no. 2, pp. 74-80, Mar. 2003.

[13] E. Jacobsen and R. Lyons, "An update to the sliding DFT," IEEE Signal Process. Mag., vol. 21, no. 1, pp. 110–111, Jan. 2004.

[14] C. Ma, F. Gao, G. He, and G. Li, "A voltage detection method for the voltage ride-through operation of renewable energy generation systems under grid voltage distortion conditions," IEEE Trans. Sustainable Energy, vol. 6, no. 3, pp. 1131-1139, July 2015.

[15] Y. F. Wang and Y. W. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," IEEE Trans. Power Electron., vol. 26, no. 4, pp. 1067–1080, Apr. 2011.

[16] K. J. Lee, J. P. Lee, D. Shin, D. W. Yoo, and H. J. Kim, "A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS," IEEE Trans. Ind. Electron., vol. 61, no. 1, pp. 292-301, Jan. 2014.

[17] S. Golestan, M. Ramezani, J. M. Guerrero, et al., "Moving average filter based phase-locked loops: performance analysis and

design guidelines," IEEE Trans. Power Electron., vol. 29, no. 6, pp. 2750-2763, June 2014.

- [18] P. Rodr'iguez, J. Pou, and J. Bergas, "Decoupled double synchronous reference frame PLL for power converters control," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 584–592, Mar. 2007.

- [19] P. Rodr'uez et al., "A fast and accurate synchronization technique for extraction of symmetrical components," IEEE Trans.Power Electron., vol. 24, no. 3, pp. 674–684, Mar. 2009.

- [20] F. A. S. Neves et al., "A generalized delayed signal cancellation method for detecting fundamental-frequency positive-sequence three-phase signals," IEEE Trans. Power Del., vol. 25, no. 3, pp. 1816–1825, Jul. 2010.

- [21] J. Svensson, M. Bongiorno, and A. Sannino, "Practical implementation of delayed signal cancellation method for phase-sequence separation," IEEE Trans. Power Del., vol. 22, no. 1, pp. 18–26, Jan. 2007.

- [22] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," IEEE Trans. Power Electron., vol. 26, no. 7, pp. 1987–1997, Jul. 2011.

- [23] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in Proc. 37th IEEE PESC, pp. 1511–1516, 2006.

- [24] R. Zhang, M. Cardinal, P. Szczesny and M. Dame, "A grid simulator with control of single-phase power converters in D–Q rotating frame," in Proc. IEEE Power Electron. Spec. Conf., pp. 1431–1436, 2002.

- [25] A. Luo, Y. D. Chen, Z. K. Shuai, and C. M. Tu, "An improved reactive current detection and power control method for single-phase photovoltaic grid-connected DG system," IEEE Trans. Energy Convers., vol. 28, no. 4, pp. 823–831, Dec. 2013.

- [26] A. Roshan, R. Burgos, A. C. Baisden, F. Wang, and D. Boroyevich, "A D-Q frame controller for a full-bridge single phase inverter used in small distributed power generation systems," in Proc. IEEE Appl. Power Electron. Conf., pp. 641–647, 2007.

- [27] A. Kulkarni and V. John, "A novel design method for SOGI-PLL for minimum settling time and low unit vector distortion," In Industrial Electronics Society, IECON 2013-39th Annual Conference of the IEEE, pp. 274-279, November 2013.

- [28] L. Xiong, F. Zhuo, F. Wang, X. Liu, and M. Zhu, "A Fast Orthogonal Signal-Generation Algorithm Characterized by Noise Immunity and High Accuracy for Single-Phase Grid," IEEE Power Electron., vol. 31, no. 3, pp. 1847-1851, March 2016.

- [29] Y. F. Wang and Y. W. Li, "Three-phase cascaded delayed signal cancellation PLL for fast selective harmonic detection," IEEE Trans. Ind. Electron., vol. 60, no. 4, pp. 1452-1463, April 2013.

- [30] Y. Park, S. K. Sul, W. C. Kim, and H. Y. Lee, "Phase locked loop based on an observer for grid synchronization," IEEE Trans. Ind. Appl., vol. 50, no. 2, pp. 1256–1265, Mar./Apr. 2014.

- [31] L. Wang, Q. Jiang, L. Hong, C. Zhang, and Y. Wei, "A novel phase-locked loop based on frequency detector and initial phase angle detector," IEEE Trans. Power Electron., vol. 28, no. 10, pp. 4538–4549, Oct. 2013.