# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

1970

# Fault detection on sequential machines

Chung-Tao David Wang

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

### **Recommended Citation**

Wang, Chung-Tao David, "Fault detection on sequential machines" (1970). Masters Theses. 7063. https://scholarsmine.mst.edu/masters\_theses/7063

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# FAULT DETECTION ON SEQUENTIAL MACHINES

By

CHUNG-TAO DAVID WANG, 1943-

A

THESIS

submitted to the faculty of

UNIVERSITY OF MISSOURI-ROLLA

in partial fulfillment of the requirements for the

Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

Rolla, Missouri

1970

T2325

c.I

70 pages

Approved by

(advisor)

183316

#### ABSTRACT

This paper presents an algorithm for deriving an optimum test sequence for detecting faults in a synchronous machine. In this study, the flow table is used as a tool to generate the fault detection tests. The fault stuck-at-1 (or stuck-at-0) is said to be present when a permanent signal valued 1 (or 0) appears on a component of the machine. Only single faults are treated. The result of the procedure is one or more test sequences guaranteed to detect a set of faults  $(F_p)$ .

First, sequential machines with feedback lines as memory elements are considered. Then the memory elements are changed to R-S flip-flops. Finally, several suggestions for further work are made.

## ACKNOWLEDGEMENT

The author wishes to take this opportunity to express his deep appreciation to his advisor, Dr. Stephen A. Szygenda, for his guidance and helpful advice.

# TABLE OF CONTENTS

|        |      |                    |            |     |         |         |         |         |     |     |     |     |        |          |         |         |         |   |   | Page |

|--------|------|--------------------|------------|-----|---------|---------|---------|---------|-----|-----|-----|-----|--------|----------|---------|---------|---------|---|---|------|

| ABSTRA | CT . |                    |            | •   | •       | •       | •       |         |     |     | •   |     | •      | •        | •       |         | •       |   |   | ii   |

| ACKNOW | LEDG | EMENT              |            | •   | •       | •       |         | •       |     |     |     | •   |        | •        | •       |         |         |   |   | iii  |

| LIST O | F FI | GURES              |            | •   | •       | •       |         |         |     |     | •   | •   |        | •        |         | •       |         |   |   | vi   |

| LIST O | F TA | BLES .             |            | •   | •       | •       | •       | •       |     |     | •   | •   |        |          | •       | •       |         | • | • | vii  |

| Chapte | r    |                    |            |     |         |         |         |         |     |     |     |     |        |          |         |         |         |   |   |      |

| I.     |      | RODUCTI            | ON         |     |         |         |         |         |     |     |     |     |        |          |         |         |         |   |   | -    |

|        |      |                    | ON         | •   | •       | •       | •       | •       | •   | •   | •   | •   | •      | •        | •       | •       | •       | • | • | Ĺ    |

| II.    | BAC  | KGROUND            | •          | •   | •       | •       | •       | •       | •   | •   | •   | •   | •      | •        | •       | •       | •       | • | • | 6    |

|        | Α.   | Sequen             | tia        | LS  | Swi     | tc      | hi      | nç      | j S | ЗУЗ | ste | ∍m  | •      | •        | •       | •       | •       | • | • | 6    |

|        | В.   | Synchr             | onoi       | ıs  | Sw      | /it     | ch      | ir      | ıg  | Ci  | r   | cui | .t     | •        | •       | •       | •       | • | • | 7    |

|        | С.   | Fault              |            |     | •       | •       | •       |         | •   |     | •   | •   |        | •        |         |         |         |   | • | 7    |

|        | D.   | Test               |            |     |         | •       |         |         |     |     | •   | •   |        |          |         | •       |         |   |   | 8    |

|        | Ε.   | Summar             | y ar       | nd  | Ex      | am      | p1      | .e      |     |     |     | •   |        |          |         |         |         |   | • | 9    |

| III.   | DER  | IVATION            | OF         | OF  | TT      | MU      | Μ       | TE      | SI  | ' S | Ές  | )UE | NC     | ES       | ;       |         |         |   |   | 11   |

|        | Α.   | Networ             | с Ar       | nal | ys      | is      |         | •       |     |     |     |     | •      |          |         |         |         |   |   | 11   |

|        | В.   | Deriva<br>Sequenc  |            |     | of<br>• | Fa<br>• |         |         |     |     |     |     | n<br>• | Те<br>•  | st<br>• | •       | •       | • | • | 19   |

|        | С.   | Limitat            |            |     |         | •       | os<br>• | si<br>• |     |     | In  | -   | · 0    | rem<br>• | er.     | ıt<br>• | of<br>• | • |   | 28   |

| IV.    |      | IVATION<br>M A SET |            |     |         |         |         |         |     |     |     |     |        |          |         | `AL     | lrı     |   | • | 31   |

|        | Α.   | Introdu            | ıcti       | on  | 1       |         |         |         |     |     |     |     |        | •        |         |         |         | • | • | 31   |

|        | В.   | Change<br>Optimum  |            |     |         |         |         |         |     |     |     |     |        | rin<br>• | g<br>•  | th<br>• | ne<br>• |   | • | 34   |

|        | c.   | Results            | 5 <b>.</b> |     |         |         |         |         |     |     |     |     | •      |          |         |         |         |   |   | 38   |

| V.   | FAULT DETECTION IN SEQUENTIAL LOGIC                                                               |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | 등 1의 경영화 등 대한 기계 등 기계 등 1일 등 1일 하지 않는 지역 회원 등 기계 원리를 보고 있다. 기계 등 기계 | 39 |

|      | A. Introduction                                                                                   | 39 |

|      | B. Modified Sequential Model                                                                      | 41 |

|      | C. Change of Procedure for Deriving Optimum                                                       |    |

|      |                                                                                                   | 43 |

|      | D. An Example                                                                                     | 46 |

|      | E. Discussion                                                                                     | 54 |

|      | F. Summary                                                                                        | 55 |

| VI.  | CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK .                                                    | 56 |

|      | A. Conclusions                                                                                    | 56 |

|      | B. Suggestions for Further Work                                                                   | 57 |

| VII. | BIBLIOGRAPHY                                                                                      | 60 |

| III. | VITA                                                                                              | 62 |

# LIST OF FIGURES

| Figure |                                                                  | 3 | Page |

|--------|------------------------------------------------------------------|---|------|

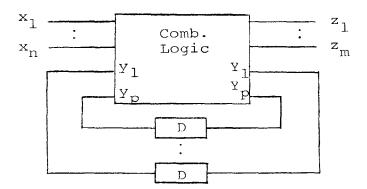

| 2.1    | Huffman Model of Sequential Circuit                              |   | 6    |

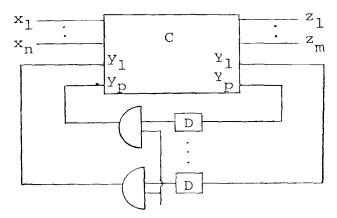

| 2.2    | Synchronous Sequential Circuit                                   | • | 7    |

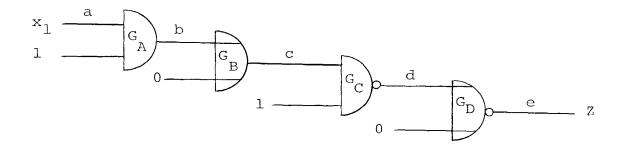

| 3.1    | A Path                                                           |   | 12   |

| 3.2    | An Illustrative Network for enf                                  | • | 13   |

| 3.3    | A Sequential Circuit with Two Feedbacks                          |   | 17   |

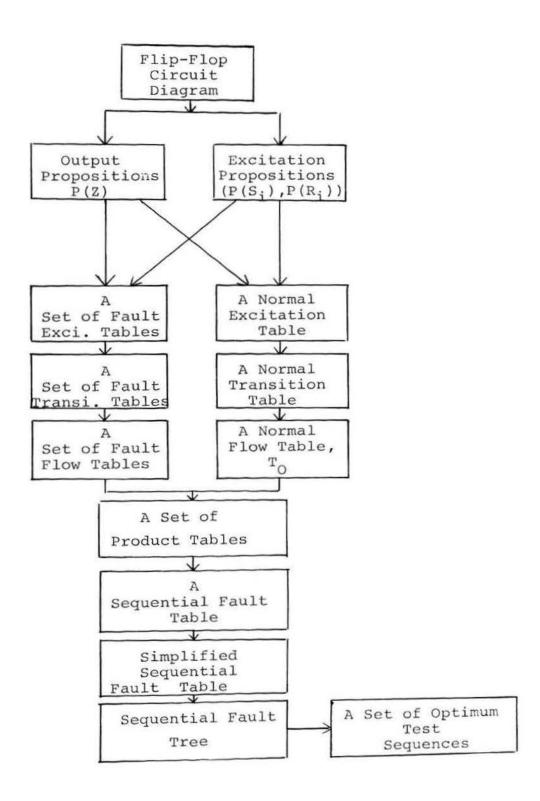

| 3.4    | Flow Chart of Overall Procedure                                  |   | 20   |

| 3.5    | A Sequential Network with Two Feedbacks                          | • | 21   |

| 3.6    | Sequential Fault Tree and Results                                | • | 28   |

| 5.1    | R-S Flip-Flop Symbol                                             | • | 39   |

| 5.2    | R-S Flip-Flop Logic Circuit                                      | • | 40   |

| 5.3    | A Synchronous Sequential Model with Flip-Flops                   | • | 42   |

| 5.4    | A Modified Flow Chart for Fault Detection of A Flip-Flop Circuit |   | 45   |

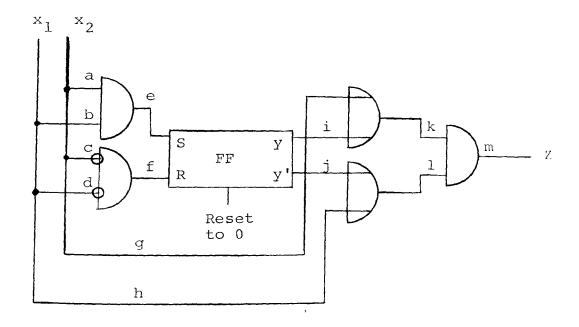

| 5.5    | A Sequential Net with One R-S Flip-Flop                          | • | 46   |

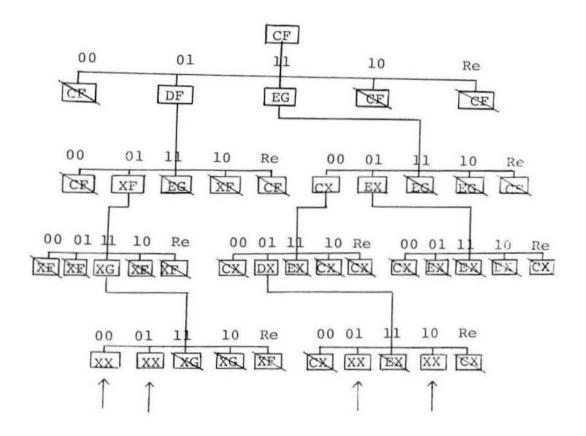

| 5.6    | Sequential Fault Tree                                            | • | 53   |

| 6.1    | A Typical Sequential Circuit                                     |   | 58   |

# LIST OF TABLES

| Table |                                                   | Page |

|-------|---------------------------------------------------|------|

| 2.1   | (a) A Fault-Free Truth Table                      | 10   |

|       | (b) A Fault Truth Table with s-a-l Fault on $x_1$ | 10   |

| 3.1   | A Fault-Free Flow Table, T <sub>0</sub>           | 22   |

| 3.2   | A Set of Fault Flow Tables, (Ta, Td, Te,          |      |

| 3.3   | T <sub>q<sub>1</sub></sub>                        | 23   |

|       | $\operatorname{PT}_{\operatorname{q}_1}$ )        | 24   |

| 3.4   | Yl Sequential Fault Table                         | 25   |

| 3.5   | Simplification Process Table                      | 26   |

| 4.1   | A Normal Flow Table with Reset Column             | 32   |

| 4.2   | A Reset Fault Flow Table with Reset Column .      | 33   |

| 4.3   | Another Reset Fault Flow Table                    | 33   |

| 4.4   | A Set of Flow Tables                              | 35   |

| 4.5   | A Set of Product Tables                           | 36   |

| 4.6   | A Set of Product Tables for $(R_0)$               | 37   |

| 5.1   | Truth Table of R-S Flip-Flop                      | 40   |

| 5.2   | The Normal Case                                   | 47   |

| 5.3   | The Fault Flow Table $T_{a_1}$                    | 48   |

| 5.4   | 1                                                 | 49   |

| 5.5   | <del>-</del>                                      | 50   |

| 5.6   | Product Table PT                                  | 50   |

| Table |                                                                     | Page |

|-------|---------------------------------------------------------------------|------|

| 5.7   | Product Table PT <sub>g1</sub>                                      | 51   |

| 5.8   | Product Table PT1,                                                  | 51   |

| 5.9   | Sequential Fault Table and Simplification of Sequential Fault Table | 52   |

| 5.10  | Don't Care Entries Caused by Fault d <sub>1</sub>                   | 55   |

#### CHAPTER I

#### INTRODUCTION

The diagnosis of equipment failures is of great importance in the field of digital system maintenance. In order to maintain digital systems, first it is necessary to detect any possible failure in the equipment and then, to isolate the failure to a repairable subsystem. The goal of this paper is to generate test sequences to detect faults, if any exist, in a sequential machine. The synchronous sequential machine is considered. Machines with different memory elements, such as feedback loops and flip-flops, are investigated separately.

For fault location in combinational logic, Eldred<sup>4</sup> and Armstrong<sup>5</sup> have developed a technique to derive tests by the use of logical diagrams of the system.

These techniques are called path sensitizing and equivalent normal form, respectively. Details of these techniques will be given in Chapter III. Roth<sup>8,9</sup> expanded this work with the "Calculus of D-Cubes" to find tests for combinational logic nets. Poage<sup>1</sup> constructed fault tables as a means of performing a special kind of network analysis which is ideally suited for fault detection purposes. Using this technique, tests with minimal length can be found as the solution of the fault table. He also

developed a method to detect multiple faults by adding extra columns to the single fault table.

Poage's later work<sup>2,3</sup> treats the problem of sequential machines in a manner analogous to that devised for combinational logic nets. The procedure for combinational and sequential nets can be briefly described as follows:

- (A) For the generation of fault detection tests for a combinational logic net, the following procedure is followed.

- (1) Perform network analysis; generate output proposition in terms of input propositions and element propositions.

- (2) Compute network functions in the presence of faults; find each faulty output proposition.

- (3) Construct the single fault table column by column. The fault table is formed by assigning each possible fault in  $(F_p)$  as an element in a column, each input combination of (X) as an element in a row, and a cross in row i and column j indicates that the input combination of row i will detect the single fault of column j. Where  $(F_p)$  and (X) are defined as a set of faults to be

- detected, and a set of fault-detection tests, respectively.

- (4) Use column dominance technique to simplify the single fault table.

- (5) Add additional columns to the single fault table in order to construct the multiple fault table.

- (6) Find the optimum test by performing the row dominance technique.

- (B) For a fault detection test sequence of a <u>sequential</u> machine, the procedure is as follows:

- (1) Perform network analysis; generate excitation propositions and output propositions in terms of input propositions and element propositions.

- (2) Tabulate each fault flow table and one fault-free flow table; label these  $T_1$ ,  $T_2$ ,...,  $T_m$  and  $T_0$ .

- (3) In construction of the sequential fault table, sets of sequences which detect each fault are found by forming the product of each fault table with T<sub>0</sub>. Then combine all the m product tables into one final sequential fault table. Here the individual product is analogous to the single column of the combinational fault table.

- (4) Use column dominance techniques to simplify the sequential fault table.

- (5) Expand the table into a sequential fault tree where the optimum test sequence for the set (F<sub>p</sub>) is found.

Several other approaches to the test generation for sequential machines have appeared. Galey, Norby and Roth derived tests by logically cutting all the feedback loops so that the circuit would have no cycles. This method, for diagnosis, proceeds as if these cuts were actually made. Seshu<sup>6</sup>, determined first how a machine could be transformed by a fault. Then he developed four strategies for finding a next test sequence which will provide the maximum amount of information. The information serves the purpose of further partitioning of the faulty machines. In other words, an attempt is made to find a test which would be able to detect or diagnose the greatest number of faults.

This study is an extension of Poage's work. Basically, the author tries to treat the problem of finding faults which may exist in the reset circuitary. Extensions of Poage's techniques to find faults in R-S flipflop circuits are also considered. Chapter II will present the required background of sequential machines,

faults, tests, and the basic concept of how faults can be detected by tests. In the last section, an example is given to demonstrate the above concepts.

#### CHAPTER II

#### BACKGROUND

### A. Sequential Switching System

A sequential switching circuit is one whose output values, at a given time, depend not only on the present inputs, but also on inputs applied previously. A general model was first introduced by Huffman<sup>12</sup>. Huffman's system is defined as a combinational network C with some of the outputs being fed back to some of the inputs through unit delays. It can be depicted as shown in Figure 2.1.

Figure 2.1. Huffman Model of Sequential Circuit

The symbols x and y are used for primary inputs and feedback inputs to the combinational logic C; Y and z are used for feedback outputs and primary outputs, respectively. The history of previous inputs is summarized in the states of the circuit.

# B. Synchronous Switching Circuit

A model of a synchronous switching circuit was introduced by Mealy, and is shown in Figure 2.2. The clock pulses occuring at certain times govern the performance of the system. The primary outputs and feedback outputs at time t are determined by the primary and feedback inputs at t. Then the present feedback output,  $y_{t+1}$ , will in turn become the feedback input vector y for the next time instant t+1. This model is used throughout the study.

Clock pulses governing the circuit

Figure 2.2. Synchronous Sequential Circuit

#### C. Fault

A fault, in general, is a physical defect of one or more components which can cause the circuit to malfunction. The faults considered in this study are restricted by the following assumptions:

- (1) Only one fault can occur at a time, i.e., single fault assumption. This implies that a malfunction is detected, located and repaired before the next fault occurs.

- (2) Only logical faults are investigated, and the types of faults are known. The fault may be defined as a transformation of a good (or fault-free) machine into one of the different possible, known faulty machines. If there are m possible faulty machines, there are m + 1 machines which should be taken into consideration in finding tests to detect all faults.

- (3) It is possible to momentarily reset the feedback lines to a known initial state even under failure conditions.

#### D. Test

When a particular input is applied to a faulty machine, the resulting output may differ from that of the good machine. If this occurs, it is said that this input or test can detect the fault. For a sequential machine, a sequence of input vectors should be applied in order to detect the fault.

Moreover, the different possible outputs of a machine for a particular input can partition the machines into various groups. Hence, successive inputs, applied to the

system, may identify the individual fault, or isolate the fault to the lowest degree. At that stage, the fault is said to be diagnosed.

## E. Summary and Example

The purpose of this study is to derive a set of optimum test sequences  $(X_{\operatorname{op}})$  to detect a set of faults  $(F_{\operatorname{p}})$  in a given synchronous sequential machine. The optimum test sequence is defined as the shortest sequence of symbols guaranteed to detect a set of m faults in  $(F_{\operatorname{p}})$ .

The following notation will be used in this paper:

- (F): the set of all possible faults

- $(F_p)$ : a subset of (F) selected for particular reasons

- (X): the set of all possible input combinations

- $(X_{op})$ : the set of optimum test sequences

The reasons for choosing subsets of (F) is primarily for the purpose of simplifying the procedure of deriving the test sequences. In general, Poage's technique becomes cumbersome and requires a columinous table to find the solution, when all the possible faults are considered at one time.

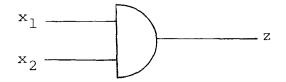

An example is given to show the concept of test for a combinational circuit.

Example 2.1. Find the test for a s-a-l fault on an input of an AND gate.

|     | × <sub>1</sub> | × <sub>2</sub> | Z |

|-----|----------------|----------------|---|

| (a) | 0              | 0              | 0 |

|     | 0              | 1              | 0 |

|     | 1              | 0              | 0 |

|     | 1              | 1              | 1 |

|      | ^1 | ^2 |     |

|------|----|----|-----|

|      | 1. | 0  | 0   |

| /h \ | 1  | 1  | 1   |

| (b)  | 1  | 0  | 0   |

|      | 1  | 1  | 1   |

|      |    |    | l . |

Table 2.1 (a) A Fault-Free Truth Table

(b) A Fault Truth Table with s-a-l Fault on  $x_1$

The input combination  $\overline{x}=(0,1)$  can detect the fault  $(x_1, s-a-1)$ , since the outputs are different in the two truth tables.

Chapter III of this study is devoted to the derivation of the optimum test sequences for synchronous sequential machine together with more extensive examples.

#### CHAPTER III

## DERIVATION OF OPTIMUM TEST SEQUENCES

## A. Network Analysis

The reason for performing network analysis before deriving test sequences is primarily to show how the fault may affect the operation of the machine. Unfortunately, ordinary Boolean algebra can only describe the normal operation of the switching circuits, but not the operation in the presence of the faults. The result of the network analysis is an expression showing the network function as well as indicating all possible faults. After a simplification procedure, the required tests can be found.

The general strategy for finding a set of fault detection tests, for a class of faults, has been found to start with network analysis. For comparison, Armstrong's Path Sensitizing\* and Equivalent Normal Form (enf) techniques are introduced here.

### Definition of a Path

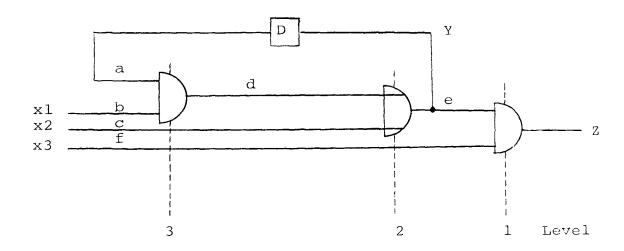

A path from  $G_0$  to  $G_n$  is defined as a physical connection traced from one primary input to a possible output as shown in Figure 3.1. For example, 'abcde' is considered as a path from input  $x_1$  to output z.

<sup>\*</sup>The Path Sensitizing concept was suggested at Conference on Diagnosis of Failure in Switching Circuit; May 1961.

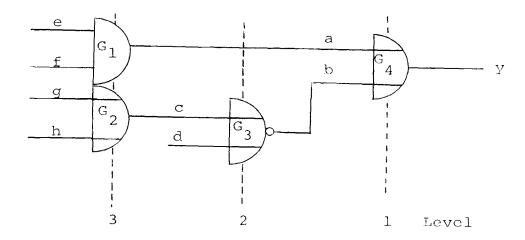

Figure 3.1. A Path

In order to detect a s-a-l fault on wire a (short for  $a_1$ ), several initial values should be assigned as This is called the normal condition. Now the change to 1 on wire "a" propagates the faulty signal all the way to z. Under this condition, the path 'abcde' is said to be sensitized, and the fault a, is said to be detected. Note that not only a can be detected, but s-a-1's on b, c, and e, as well as, s-a-0 on d can also be detected. By applying the path sensitizing technique, an enf for the net is formed. This is demonstrated by the following example. First, associate with each wire a name, a, b, c, etc., and with each gate a G1, G2, G3, Then level the gates with numbers as shown in Figure 3.2. The enf is found starting with level number 1. The resulting enf is a "sum of products" expression. Each literal consists of an input variable subscripted by a

sequence of gate numbers. The variable and its subscript sequence identifies a path from an input to an output.

Figure 3.2. An Illustrative Network for enf

$$y = (a + b)_{4}$$

$$= ((ef)_{1} + (c'd')_{3})_{4}$$

$$= e_{14}f_{14} + (g'_{234} h'_{234}) d'_{34}$$

$$= e_{14}f_{14} + g'_{234}h'_{234}d'_{34} . . . . . . . . . . . (3.1)$$

It has been shown that the enf provides a tool to construct fault tables<sup>5</sup>. Systematically finding the most desirable test could be accomplished from the fault tables. Desirable tests are those which can sensitize many paths so as to detect many faults.

The network analysis performed in this study is introduced as follows.

# Definition of Propositions

### 1. Input propositions

Associate with each input line,  $X_{i}$ , two input propositions:

- $x_i$ : For the signal applied to input line  $X_i$  as a value of 1.

- $\mathbf{x_{i}^{!}}$ : For the signal applied to input line  $\mathbf{X}_{i}$  as a value of 0.

# 2. Element propositions

The elements of the gate network are the wires connecting two gates, primary inputs, outputs, or feedback lines. Elements of the system have the property that they are binary in nature. Hence, any element, a, may appear in any of following states:

- (a) The wire a is normal; i.e., its signal may be switched to either value 1 or 0. The element proposition associated with it is  $a_n$ .

- (b) The wire a is stuck-at-one; i.e., a signal of constant value 1 appears on the wire. The element proposition is a<sub>1</sub>.

- (c) The wire is stuck-at-zero; i.e., a signal of constant value 0 appears on the wire. The element proposition in this case is a<sub>0</sub>.

In summary, any element, a, can have three propositions, namely,  $a_n$ ,  $a_1$ , and  $a_0$ .

## 3. The output propositions

The output propositions are expressed in terms of input and element propositions. The output proposition can describe the signal on the wire and the circuit performance of the machine. For example, consider a single AND gate.

The proposition for wires a, b, and c are x, y, and xy, respectively. Further, the proposition which can describe the logic operation in the presence of faults are given as follows:

For convenience, the general propositions will be defined first.

$P_a = x a_n + a_1$  to express a signal of value 1 appearing on wire a.

$P'_a = x'a_n + a_0$  to express a signal of value 0 appearing on wire a.

The output propositions of the gate are,

$$P_{c} = (P_{a}P_{b})c_{n} + c_{1}$$

$$= (P_{a}c_{n} + c_{1}) (P_{b}c_{n} + c_{1})$$

A compressed form of notation for the proposition is, for convenience, to drop  $\boldsymbol{c}_n$  and have P written as follows.

$$P_{c} = P_{a}(c_{1}) \cdot P_{b}(c_{1}) \cdot \dots \cdot (3.2)$$

Similarly,

Note that several theorems such as

$$(X + Y)^{-} = XZ + YZ,$$

$XY + Z = (X + Z) (Y + Z),$

$X = X + X,$

XX = X, etc. have been applied to obtain a standard sum of products form. Further, for convenience, the final results are condensed into their compressed notation form. For a more complicated circuit, the analysis procedure is done backwards, from the output level to the primary input level. At each level, the above theorem and compressed notation technique must be applied to avoid a very combersome standard form. The above definitions and techniques are demonstrated by Example 3.1.

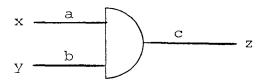

Example 3.1. Find the excitation propositions and output propositions for the following sequential circuit.

Figure 3.3. A Sequential Circuit With Two Feedbacks

(1) Start from the output, Z. The excitation proposition for  $Y_{l}$  is

$$P(Y_1) = (P_e + P_f) m_n + m_1 \dots (3.4)$$

(2) Apply theorem (X + Y)Z = XZ + YZ and X + X = X:  $P(Y_1) = (P_e^m + m_1) + (P_f^i + m_1) + \dots$  (3.5)

(3) Reduce it into compressed notation form:

$$P(Y_1) = P_e(m_1) + P_f(m_1) \dots \dots (3.6)$$

Again using the same techniques, one can find the final standard form systematically.

$$P(Y_{1}) = ((P_{a}P_{b})e_{n} + e_{1})(m_{1}) + ((P_{c}P_{d})'f_{n} + f_{0})(m_{1})$$

$$= P_{a}P_{b}(e_{1}m_{1}) + (P_{c}' + P_{d}')(f_{0}m_{1})$$

$$= P_{a}(e_{1}m_{1}) \cdot P_{b}(e_{1}m_{1}) + P_{c}'(f_{0}m_{1}) + P_{d}'(f_{0}m_{1})$$

To sum up, the excitation proposition and output proposition could be found by applying three steps:

- (1) Regard each term as an individual output. Find the output proposition in terms of its input propositions and element propositions.

- (2) Use proper theorems to expand the expression into a sum of products form.

- (3) Reduce the form to its compressed notation form.

The three steps are used level by level until the primary inputs have been reached.

Hence,  $P(Y_2)$  and P(Z) are found as follows:

$$P(Z) = (y_{1}(a_{1}e_{1}j_{1}l_{1}) \cdot x_{1}(b_{1}e_{1}j_{1}l_{1}) + x_{2}'(g_{0}f_{0}j_{1}l_{1})$$

$$+ y_{2}'(d_{0}f_{0}j_{1}l_{1}) \cdot (y_{1}'(a_{0}g_{0}k_{1}l_{1}) + x_{1}'(b_{0}g_{0}k_{1}l_{1})$$

$$+ x_{2}(c_{1}h_{1}k_{1}l_{1}) \cdot y_{2}(d_{1}h_{1}k_{1}l_{1}) \cdot \dots (3.9)$$

# Output functions in the presence of faults

If the wire b is now stuck-at-1, in the previous example, the element propositions  $b_1, a_n, \ldots, l_n$  are assigned

to be true, and the others to be false. The excitation functions are formed as follows:

Take the first terms of Equation (3.7),  $y_1(a_1e_1m_1) \cdot x_1(b_1e_1m_1)$ , to demonstrate the technique. Originally this terms is in the form

$(((y_1a_n + a_1)e_n + e_1)m_n + m_1)(((x_1b_n + b_1)e_n + e_1)m_n + m_1).$ Under the fault b<sub>1</sub>,

$$b_1 = a_n = e_n = m_n = 1$$

, and  $b_n = a_1 = e_1 = m_1 = 0$ .

Substitute those values into the above term:

$$y_1(a_1e_1m_1) \cdot x_1(b_1e_1m_1)|_{b_1}$$

=  $(((y_1 \cdot 1 + 0)1 + 0) 1 + 0)(((x_1 \cdot 0 + 1) 1 + 0)1 + 0)$

=  $y_1 \cdot 1 = y_1$ .

Therefore,

$$P(Y_1)|_{b_1} = y_1 + x_2' + y_2' \cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot (3.10)$$

$P(Y_2)|_{b_3} = y_1' + x_2y_2 \cdot (3.11)$

Similiarly,

$$P(Z)|_{b_1} = (y_1 + x_2 + y_2)(y_1 + x_2y_2) \dots (3.12)$$

The above expression is equivalent to a permanent signal of value 1 at wire b, when deriving the output function using ordinary Boolean Algebra.

# B. Derivation of Fault Detection Test Sequences

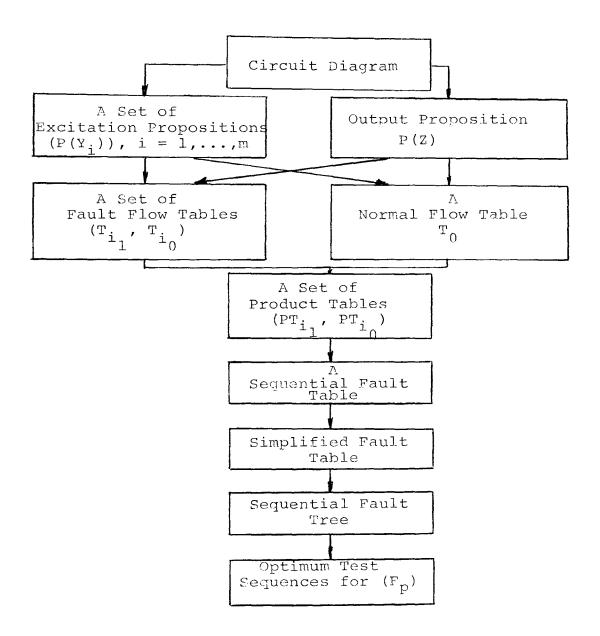

The procedure has been stated in Chapter I. A more detailed description of the overall concept is given in Figure 3.4.

Figure 3.4. Flow Chart of Overall Procedure

The following example is used to illustrate the procedure. The machine is said to be able to reset to a particular initial state (00), even in the presence of fault.

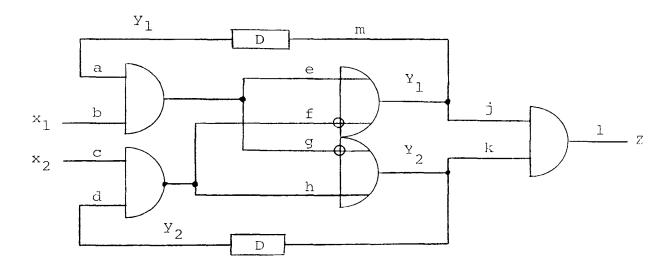

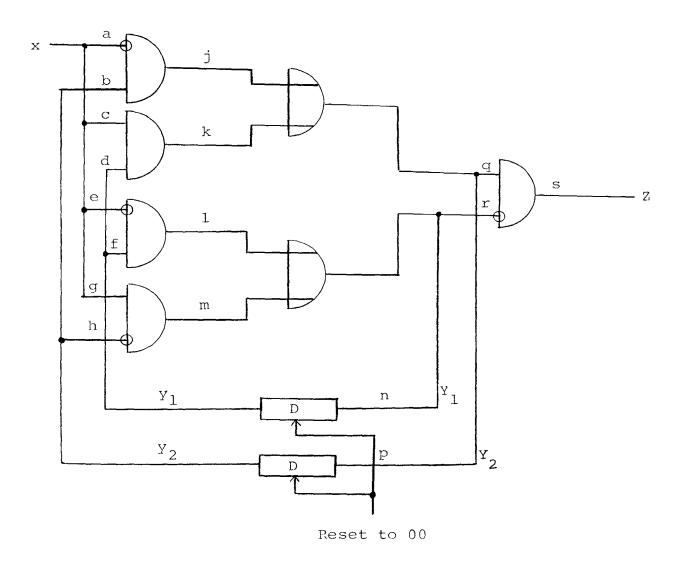

Example 3.2. Find the set of fault detection test sequences for  $(F_p) = (a_1, d_1, e_1, q_1)$  in the following sequential logic. Note that not all possible faults are considered.

# (1) Circuit diagram

Figure 3.5. A Sequential Network With Two Feedbacks

(2) Excitation propositions and output proposition:

$$\begin{split} & P(Y_1) = x'(a_0 j_1 p_1) \cdot y_1(b_1 j_1 p_1) + x(c_1 k_1 p_1) \cdot y_2(d_1 k_1 p_1) \dots (3.13) \\ & P(Y_2) = x'(e_0 l_1 n_1) \cdot y_2(f_1 l_1 n_1) + x(g_1 m_1 n_1) \cdot y_1'(h_0 m_1 n_1) \dots (3.14) \\ & P(Z) = ((x'(a_0 j_1 q_1 s_1) \cdot y_1(b_1 j_1 q_1 s_1) + x(c_1 k_1 q_1 s_1) \cdot y_2(d_1 k_1 q_1 s_1)) \\ & (x(e_1 l_0 r_0 s_1) + y_2'(f_0 l_0 r_0 s_1)) (x'(g_0 m_0 r_0 s_1) + y_1(h_1 m_0 r_0 s_1)). \end{split}$$

(3) Construction of the fault-free flow table,  $T_0$ , and a set of fault flow tables for  $(F_p)$ , which are:

$$(T_{i_1}, T_{i_0}) = (T_{a_1}, T_{d_1}, T_{e_1}, T_{q_1}).$$

Table 3.1. A Fault-Free Flow Table, To

In the presence of fault a<sub>1</sub>, the propositions reduce to the following form:

$$P(Y_2)|_{a_1} = x'y_2 + xy_1' \dots \dots \dots (3.17)$$

$$P(Z)|_{a_1} = xy_2(x + y_2)(x' + y_1) = xy_1y_2 ... (3.18)$$

Hence the set of fault flow tables are found as shown in Table 3.2.

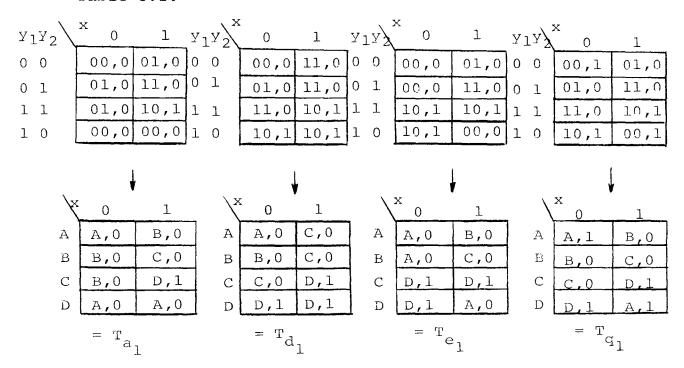

Table 3.2. A Set of Fault Flow Tables,  $(T_{a_1}, T_{d_1}, T_{e_1}, T_{q_1})$

(4) Construct the set of product tables  $(PT_{i_1}, PT_{i_0}) = (PT_{a_1}, PT_{d_1}, PT_{e_1}, PT_{q_1}).$

To start with the same initial state A, the entries of each product table are found as the product of corresponding states in T<sub>0</sub> and each fault flow table. If a new entry occurs, such as (CB,00), with the same output value, a new row should be added since a new state in the product table has occured. However, the output value cannot indicate the fault yet. Therefore, if an entry like

(DC,10) or (DA,10) occurs, this entry is marked with a cross "X". There is no need to add a new row since the fault is already detected.

The major purpose of a product table is to denote a set of sequences. The internal states of the component machines and their outputs are of secondary importance. Hence, the product table, PT , can be trimmed down to a form shown in Table 3.3.

Flow tables for the remaining faults of  $(F_p)$  are derived in a similar manner.

Table 3.3. A Set of Product Tables,  $(PT_{a_1}, PT_{d_1}, PT_{e_1})$

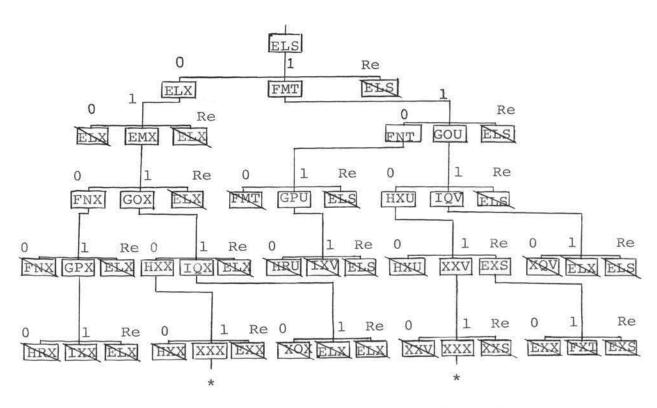

(5) Construct a sequential fault table. It is started with an initial product state (EJLS), where each literal corresponds to the initial state of each product table. New rows are added when new states occur. The table is completed when there is a row containing all entries which have occured as previous entries.

|                |                |       | /x             |         |         |

|----------------|----------------|-------|----------------|---------|---------|

| a <sub>1</sub> | $^{\rm d}_{1}$ | $e_1$ | q <sub>1</sub> | 0       | 1       |

| E              | J              | L     | S              | ЕЈЬХ    | F K M T |

| F              | K              | M     | Т              | F K N T | GXOU    |

| F              | K              | N     | T              | F K N T | G X P U |

| G              | Χ              | 0     | U              | нххи    | IXQV    |

| G              | X              | P     | U              | H X R U | IXXV    |

| H              | X              | R     | U              | H X R U | XXXV    |

| I              | X              | Q     | V              | X X Q V | EXLX    |

Table 3.4. Sequential Fault Table

(6) Simplify the sequential fault table by column dominance technique. First remove all the letters and leave only crosses in the table. Fault d<sub>1</sub> need not be considered since its column dominates columns

for faults  $a_1$  and  $e_1$ . Any sequence detecting fault  $a_1$  must use entry (XXQV) or entry (XXXV). Fault  $d_1$  can also be detected by these entries and thus contributes nothing to the derivation of the test.

|        |                                                                           | a <sub>1</sub> | d <sub>1</sub>        | e <sub>1</sub> | $q_1$ |

|--------|---------------------------------------------------------------------------|----------------|-----------------------|----------------|-------|

| x<br>0 | E J L S<br>F K M T<br>F K N T<br>G X O U<br>G X P U                       |                | X<br>X<br>X           | X              | Х     |

|        | H X R U<br>I X Q V                                                        | Х              | X                     |                |       |

| 1      | E J L S<br>F K M T<br>F K N T<br>G X O U<br>G X P U<br>H X R U<br>I X Q V | X              | X<br>X<br>X<br>X<br>X | X<br>X         | Х     |

Table 3.5. Simplification Process Table

(7) Expand the simplified sequential fault table into a sequential fault tree. In terms of the sequential fault table, an optimum test is the shortest sequence of input symbols using a set of entries having at least one cross in every position. Figure 3.6 illustrates the process of finding a sequential fault tree. The process is as follows.

- (a) Start with the initial state, (ELS). Input variable x (valued 0 or 1) or a reset value is applied to the system. The three product states result as the next level of the tree. It is assumed, in this example, that a reset signal and input signal cannot be applied simultaneously. If a reset signal can be applied simultaneously with an input symbol, it must be regarded as an additial input variable. In this event, the number of branches leaving a product state will be twice the number of input symbols; four in the example.

- (b) If a cross appears in a product state, all subsequent branches must contain a cross in the same position. If a product state has appeared previously, it is checked out and can no longer be considered as another initial state at this level. Further extension of this branch will result in an idential path and hence is fruitless.

- (c) The branch is terminated if all three product states have appeared previously and are to be checked out, or, if a product state with all crosses has occured.

(d) Then, the optimum tests are those input sequences along the branches from the initial state (ELS) to the terminating states with all crosses, (XXX).

Therefore, the set of optimum test sequences is  $(X_{op}) = (01101, 11011) \dots \dots \dots \dots \dots (3.13)$

Figure 3.6. Sequential Fault Tree and Results

C. Limitations and Possible Improvements of the Procedure

The procedure presented in the previous sections has

several limitations. First, the resulting test sequence

can only detect a specific set of faults, (F<sub>p</sub>). Practically, if (F<sub>p</sub>) contains all the possible m faults, the flow tables will be too large. Hence, it is quite reasonable to consider applying path sensitizing concepts, to determine which faults should be chosen as a set, in order to save unnecessary work. Note that feedback loops should be considered as a part of the path. A suggestion on path sensitizing techniques for sequential machines is presented in Chapter VI.

Secondly, one of the assumptions stated that a machine, even in the presence of faults, may be reset to a particular initial state. What happens when the reset cannot force a defective machine to the initial state,  $q_{\lambda}?$  The modified system was investigated by Poage and is introduced in the next chapter.

The last limitation is due to the memory consuming nature of the procedure; therefore, it can only be applied to relatively small machines. As a result, practical applications are restricted to small modules or special units. However, many circuits to be checked frequently are comparatively small, and larger networks usually consist of repeated or iterative structures. This procedure can first be applied to small basic modules individually. Then, the results can possibly be combined to obtain an overall and complete test set.

In Chapter IV, detection of faults from a set containing reset failures is considered. The modified system will become more memory consuming since more flow tables should be taken into consideration.

### CHAPTER IV

DERIVATION OF OPTIMUM TEST TO DETECT FAULTS FROM A SET

CONTAINING RESET FAILURES

### A. Introduction

The assumption made for the approach described in the previous chapters states that a reset signal can always force the set of all m+l machines,  $^{\rm M}_0$ ,  $^{\rm M}_1$ ,...,  $^{\rm M}_m$  into some initial or starting state,  $^{\rm Q}_\lambda$ . What happens when the reset does not guarantee this condition? Two undesirable consequences of this condition will be considered in this chapter:

- (1) Certain feedback lines, under fault conditions, can not possibly be reset to a particular initial state  $\mathbf{q}_{\lambda}.$

- (2) Some feedback lines are permanently reset to a particular state  $\mathbf{q}_{\lambda}$ . One may say that the feedback input is stuck at the reset value. It is determined that this reset signal can be found to be equivalent to an input signal, when the reset fault is present.

In both cases, the previous flow tables would have to be modified for deriving fault detection tests. This is done by adding an extra column, called the reset column, to the excitation table, to show the effect of reset

failures. The other parts of the procedure are similar to the previous system. The result, however, will consist of test inputs as well as the reset inputs. This is demonstrated in the following example.

- Example 4.1. To show the addition of reset columns to the normal flow table and flow tables with reset faults, respectively. The sequential network is shown in Figure 3.5.

- (1) The normal excitation table is modified to the following form:

| y <sub>1</sub> y <sub>2</sub> ×, | Re<br>0 | 1    | Re |

|----------------------------------|---------|------|----|

| 0 0                              | 00,0    | 01,0 | 00 |

| 0 1                              | 01,0    | 11,0 | 00 |

| 1 1                              | 11,0    | 10,1 | 00 |

| 1 0                              | 10,1    | 00,0 | 00 |

Hence the normal flow table turns out to be

| х, | Re  |     |    |

|----|-----|-----|----|

|    | 0   | 1   | Re |

| Α  | A,0 | в,0 | A  |

| В  | В,0 | C,0 | Α  |

| С  | C,0 | D,0 | A  |

| D  | D,1 | A,1 | A  |

Table 4.1. A Normal Flow Table with Reset Column

O state; i.e., the reset signal cannot change the present state of y. To show this effect in the excitation table, the Y<sub>1</sub> portion of the reset column is replaced by the y<sub>1</sub> column, but leaves the column for input x unchanged.

| ×,                            | Re   |                 |     |

|-------------------------------|------|-----------------|-----|

| У <sub>1</sub> У <sub>2</sub> | 0    | 1               | Re  |

| 0 0                           | 00,0 | 01,0            | 00  |

| 0 1                           | 01,0 | 11,0            | 0.0 |

| 1 1                           | 11,0 | 10,1            | 00  |

| 1 0                           | 10,1 | 00,1            | 00  |

|                               | У1У  | 2, <sup>Z</sup> |     |

| < ×, | Re  |     |    |

|------|-----|-----|----|

|      | 0   | 1   | Re |

| А    | A,0 | В,0 | А  |

| В    | В,0 | C,0 | A  |

| С    | C,0 | D,1 | D  |

| D    | D,1 | A,0 | D  |

|      |     | S,Z |    |

Table 4.2. A Reset Fault Flow Table with Reset Column

(3) Consider now that the memory element  $y_1$  is permanently reset; i.e., the reset column is not changed, but the  $Y_1$  portions of columns x=0 and x=1 are replaced by the  $y_1$  portion of the reset column.

| Y <sub>1</sub> Y <sub>2</sub> × , R | e<br>0 | 11   | Re  |

|-------------------------------------|--------|------|-----|

| 0 0                                 | 00,0   | 01,0 | 00  |

| 0 1                                 | 01,0   | 01,0 | 0.0 |

| 1 1                                 | 01,9   | 00,1 | 00  |

| 1 0                                 | 00,1   | 00,0 | 00  |

| ×, | Re  |     |    |

|----|-----|-----|----|

|    | 0   | 1   | Re |

| Α  | A,0 | В,0 | А  |

| В  | В,0 | В,0 | А  |

| С  | в,0 | A,1 | А  |

| D  | A,1 | A,0 | Α  |

Table 4.3. Another Reset Fault Flow Table

B. Change in Procedure When Deriving the Optimum Tests

Since a reset does not always return a defective machine to the initial state, more than one product table is required to describe one machine, under fault conditions.

Let the set of faults containing reset faults be  $(\mathbf{F}_{\mathrm{D}}) \ = \ (\mathbf{a}_{1}, \ \mathbf{e}_{1}, \ \mathbf{q}_{1}, \ \mathbf{R}_{0}, \ \mathbf{R}_{1})$

- (R $_0$ ) denoting that both  $\mathbf{y}_1$  and  $\mathbf{y}_2$  cannot be reset to the initial state (00), and

- (R<sub>1</sub>) denoting that both  $y_1$  and  $y_2$  are permanently reset to the initial state (00).

Product tables PT , PT , PT , and PT can be easily found as done previously.

For the fault  $R_0$ , one does not know which of the initial states to start with. Hence, all the four starting values, A, B, C, and D have to be considered individually to avoid the possibility of a test which fails to detect a fault under certain initial conditions. The set of product tables for fault  $R_0$  is

$$(PT_{R_0}^{-A}, PT_{R_0}^{-B}, PT_{R_0}^{-C}, PT_{R_0}^{-D}).$$

The final product, of the four product tables, can be formed in a list sequence which detects fault  ${\bf R_0}$ , regardless of the initial states.

(1) Forming the set of flow tables for  $(F_p)$

Table 4.4. A Set of Flow Tables

(2) Forming the set of product tables

Table 4.5. A Set of Product Tables

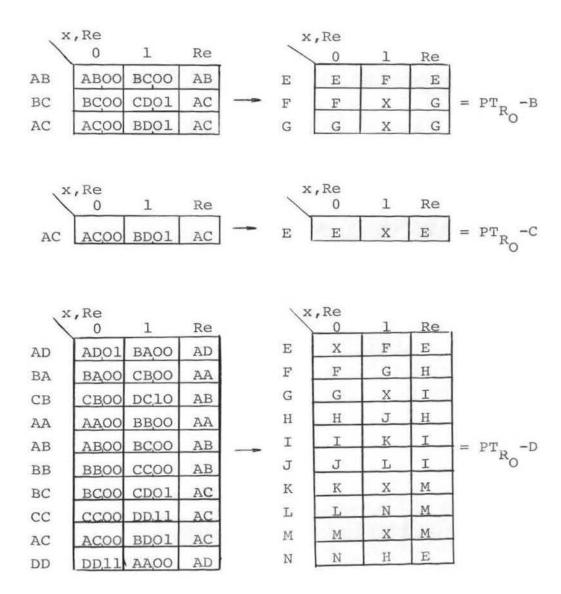

b) The set of product tables for  $R_0$ ,  $(PT_R^{-A}, PT_R^{-B}, PT_R^{-C}, PT_R^{-D})$

| X, | Re   |      |    |    | X | ,Re |   |    |                       |

|----|------|------|----|----|---|-----|---|----|-----------------------|

| 1  | 0    | 1    | Re | 1  |   | 0   | 1 | Re | i                     |

| AA | AAOO | ввоо | AA |    | E | E   | F | E  |                       |

| BB | ввоо | ccoo | AB |    | F | F   | G | Н  |                       |

| CC | CCOO | DD11 | AC |    | G | G   | I | Н  |                       |

| AB | ABOO | всоо | AB |    | H | Н   | K | Н  |                       |

| DD | DD11 | AAOO | AD | -> | I | I   | E | L  | = PT <sub>RO</sub> -A |

| AC | ACOO | BD01 | AC |    | J | J   | Х | J  | 0                     |

| BC | всоо | CDO1 | AC |    | K | K   | X | J  |                       |

| AD | ADO1 | BAOO | AD |    | L | X   | M | L  |                       |

| BA | BAOO | СВОО | AA |    | M | M   | N | E  |                       |

| CB | СВОО | DC10 | AB |    | N | N   | Х | Н  |                       |

Table 4.6. A Set of Product Tables for  $(R_0)$

### C. Results

Once the product tables have been formed for all faults of  $(F_p)$ , the derivation of an optimum detection test proceeds exactly as in the previous chapter. In other words, the product of eight product tables for the fault set,  $(F_p) = (a_1, e_1, q_1, R_0, R_1)$  is formed to obtain a sequential fault table. Dominance simplification is used, and the resulting test sequence is found to be

$$x_{op} = (1101 \text{ Re } 0).$$

Note that the reset value is treated as a part of the test sequence. It implies that Re = 0 at the beginning.

Compare the results with test derived for the same network in Chapter III:

(a)

$$(F_p) = (a_1, e_1, q_1); (X_{op}) = (01101; 11011).$$

(b)

$$(F_p) = (a_1, e_1, q_1, R_0, R_1); (X_{op}) = 1101 Re 0.$$

The result has the same length, five test inputs, but detects more faults.

The next chapter will describe the derivation of optimum tests for flip-flop circuits. The procedure will be modified to sequential networks containing R-S flip-flops. An example is investigated in detail to demonstrate the proposed technique.

### CHAPTER V

# FAULT DETECTION IN SEQUENTIAL LOGIC CONTAINING FLIP-FLOPS

### A. Introduction

In Chapter III and IV, the memory elements for the sequential machine were represented by the presence of feedback loops. Practically, the flip-flop (bistable multivibrator) is a more useful memory device for binary digit storage and switching functions, because of its speed and bistable characteristics. This chapter is devoted to the derivation of fault detection tests for sequential machines having only R-S flip-flops as memory elements.

Some characteristics of R-S flip-flops are stated as follows:

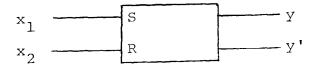

(1) The Reset-Set flip-flop circuit can be represented by either the symbol shown in Figure 5.1 or by two NOR gates as in Figure 5.2.

Figure 5.1. R-S Flip-Flop Symbol

Figure 5.2. R-S Flip-Flop Logic Circuit

where y: Flip-flop output

x: input variable

When x = S, it is called the set input; i.e., S = 1 can set y to one, and when x = R, it is called the reset input; i.e., R = 1 can set y to zero.

(2) The truth table and characteristic function of an R-S flip-flop are shown as follows:

| S R y | Y |                                                                                                                                                                         |

|-------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0 | 0 |                                                                                                                                                                         |

| 0 0 1 | 1 |                                                                                                                                                                         |

| 0 1 0 | 0 | $\mathbf{v} = \mathbf{S} + \mathbf{R}^{T} \mathbf{v} \dots \dots$ |

| 0 1 1 | 0 |                                                                                                                                                                         |

| 1 1 0 | d |                                                                                                                                                                         |

| 1111  | d |                                                                                                                                                                         |

| 1 0 0 | 1 |                                                                                                                                                                         |

| 1 0 1 | 1 |                                                                                                                                                                         |

Table 5.1. Truth Table of R-S Flip-flop

Note that the situation where S=R=1 is assumed not to occur. It can only happen when certain faults cause this state to occur. This is discussed in a later section.

(3) Therefore, the state transition function is Y = f(x,y)

where x = R, S and Y is the result state.

### B. Modified Sequential Model

The flip-flop is called an internal memory device. The feedback nature of the flip-flop is not as clearly presented as before. Hence, the general model for a sequential machine described in Chapter II seems to be inaccurate. However, feedback lines are actually contained within the flip-flop circuitry. In this chapter, the faults within the block of flip-flops are not considered.

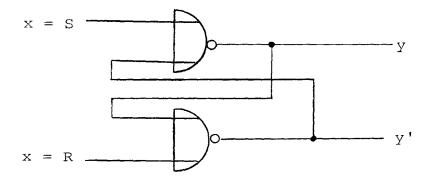

To express the presence of R-S flip-flops, the synchronous sequential model is modified to the form shown in Figure 5.3.

Figure 5.3. A Synchronous Sequential Model with Flip-Flops

where,  $x_i$ : primary input, i = 1, 2, ..., n.

$z_j$ : primary output, j = 1,2,3,...,m.

Sk: set input for kth flip-flop.

Rk: reset input for kth flip-flop.

yk: flip-flop output for kth flip-flop

k = 1, 2, ..., p.

C: clock pulse governing the operation of the circuit.

The reset assumption is again used to force all m + 1 machines into a particular initial state  $q_{\lambda}$ .

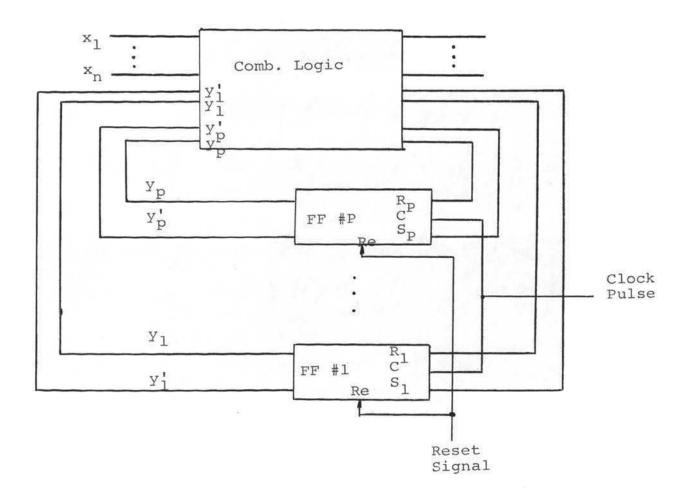

- C. Change of Procedure for Deriving Optimum Tests

- (1) Network Analysis

The output proposition remains unchanged. For the excitation proposition, let

- P(S) be the excitation proposition for set inputs.

- P(R) be the excitation proposition for reset inputs.

- Again, a given machine is analyzed to obtain a set of m + 1 flow tables (T<sub>0</sub>, T<sub>1</sub>,...,T<sub>m</sub>) for machines (M<sub>0</sub>, M<sub>1</sub>,...,M<sub>m</sub>). Here m + 1 transition tables are required in order to find the fault flow tables.

- (3) Forming the Product Tables

A sequence which detects each fault is found by comparing tables  $T_1, T_2, \dots, T_m$  with  $T_0$ , individually. The results are called a set of product tables,

(4) The Sequential Fault Table Combine all the m product tables, resulting in a sequential fault table. The column dominance simplification process is performed, then, to wipe out those sets of sequences which contain (or dominate) other sets. The result is called a simplified sequential fault table.

(5) Sequential Fault Tree and Result

Optimum test sequences are found by expanding the simplified sequential fault table into a sequential fault tree.

A flow chart for the derivation of optimum tests for fault detection in sequential machines containing R-S flip-flops is shown in Figure 5.4. An example is given in the next section to illustrate this procedure.

Figure 5.4. A Modified Flow Chart for Fault Detection of A Flip-Flop Circuit

# D. An Example

Find optimum tests for the set of faults

$$(F_p) = (a_1, g_1, l_1).$$

Figure 5.5. A Sequential Net with One R-S Flip-Flop

# (1) Network Analysis

$$P(S) = P_a P_b e_n + e_1$$

=  $x_1 (a_1 e_1) \cdot x_2 (b_1 e_1) \cdot \cdot \cdot \cdot \cdot (5.2)$

$$P(R) = P_{cdn}^{'} + f_{1}$$

$$= x_{1}^{'} (c_{0}f_{1}) \cdot x_{2}^{'} (d_{0}f_{1}) \cdot \cdot \cdot \cdot \cdot (5.3)$$

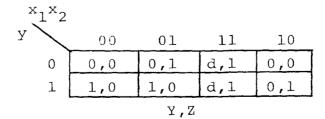

# (2) Forming Flow Tables

a) If no faults occur, the propositions reduce to

$$P(S) = x_1 x_2 \dots \dots (5.5)$$

$$P(Z) = yx_1 + y'x_2 \dots \dots (5.7)$$

The excitation table, transition table and flow table are

| 1^2 | 00  | 01  | 11  | 10  |

|-----|-----|-----|-----|-----|

| A   | A,0 | A,1 | В,1 | A,0 |

| В   | A,0 | В,0 | В,1 | В,1 |

Table 5.2. The Normal Case

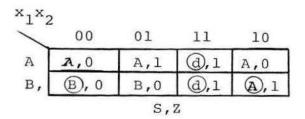

In the presence of fault  $a_1$ , b)

$$P(z)|_{a_1} = yx_1 + y'x_2 \dots \dots (5.10)$$

The circled entries indicate the malfunction caused by fault a,.

| 1 | 2 00 | 01   | 11   | 10   |

|---|------|------|------|------|

| 0 | 01,0 | 10,1 | 10,1 | 00,0 |

| 1 | 01,0 | 10,0 | 10,1 | 00,1 |

$$T_{a_1} = \begin{bmatrix} x_1^{x_2} \\ 00 & 01 & 11 & 10 \\ A & A, 0 & B, 1 & B, 1 & A, 0 \\ B & A, 0 & B, 0 & B, 1 & B, 1 \end{bmatrix}$$

Table 5.3. The Fault Flow Table  $T_{a_1}$

In the presence of fault g, C)

$$P(S)|_{g_1} = x_1 x_2 \dots \dots (5.11)$$

$$P(R) |_{g_1} = x_1' x_2' \dots \dots \dots (5.12)$$

$$P(z)|_{g_1} = y + y'x_2 \dots \dots (5.13)$$

SR,Z

| 1, | 00  | 01  | 11  | 10  |

|----|-----|-----|-----|-----|

| 0  | 0,0 | 0,1 | 1,1 | 0,0 |

| 1  | 0,1 | 1,1 | 1,1 | 1,1 |

$$T_{g_1} = \begin{bmatrix} X_1 X_2 \\ A & A, 0 & A, 1 & B, 1 & A, 0 \\ A & A, 0 & B, 0 & B, 1 & B, 1 \end{bmatrix}$$

Table 5.4. Fault Flow Table Tg1

In the presence of fault 1, d)

$$P(S)|_{1} = x_{1}x_{2} \dots \dots \dots \dots (5.14)$$

$$P(S)|_{1_1} = x_1 x_2 \dots \dots \dots \dots (5.14)$$

$P(R)|_{1_1} = x_1' x_2' \dots \dots \dots \dots (5.15)$

$P(Z)|_{1_1} = x_1 y \dots \dots \dots \dots (5.16)$

| Y | 00   | 01   | 11   | 10   |

|---|------|------|------|------|

| 0 | 01,0 | 00,0 | 10,0 | 00,0 |

| 1 | 01,0 | 00,0 | 10,1 | 00,1 |

| 1 2 00 | 01  | 11  | 10  |

|--------|-----|-----|-----|

| 0 0,0  | 0,0 | 1,0 | 0,0 |

| 1 0,0  | 1,0 | 1,1 | 1.1 |

| 1 | 2 00 | 01  | 11   | 10  |

|---|------|-----|------|-----|

| A | A,0  | A,0 | в, 🔘 | A,0 |

| В | A,0  | В,0 | В,1  | В,1 |

Table 5.5. Fault Flow Table T

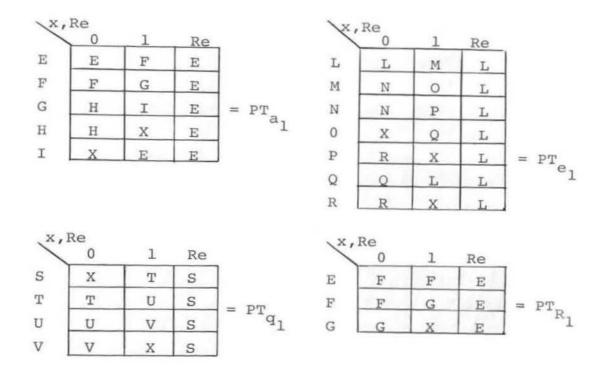

### (3) Forming Product Tables

The set of product tables is formed by the product of  $T_0$  with  $T_1$ ,  $T_2$ ,..., $T_m$  individually. When a new state occurs with the same output value, a new row is to be added. If an entry occurs with different output values a cross is then placed in that entry.

Table 5.6. Product Table PTal

Table 5.7. Product Table PT g1

c)

$$PT_{1_1} = T_0 \cdot T_{1_1}$$

Table 5.8. Product Table PT11

# (4) Forming Sequential Fault Table

Combining all the flow tables and starting at the initial state CFI, the sequential fault table is formed by adding a new row to the table when a new state occurs. The table is complete when there is a row for every entry that has appeared previously.

| X                                            | 1X | 2   |     |     |     |

|----------------------------------------------|----|-----|-----|-----|-----|

| a <sub>1</sub> g <sub>1</sub> l <sub>1</sub> | /  | 00  | 01  | 11  | 10  |

| C F                                          | I  | CFI | DFX | EGX | CFI |

| D F                                          | Х  | CFX | XFX | EGX | XFX |

| E G                                          | Х  | CXX | EXX | EGX | EGX |

| ×1 | ×2 |                   | a<br>1 | g <sub>1</sub> | 11          |

|----|----|-------------------|--------|----------------|-------------|

| 0  | 0  | CFI<br>DFX<br>EGX |        | Х              | x           |

| 0  | 1  | CFI<br>DFX<br>EGX | х      | Х              | X<br>X<br>X |

| 1  | 1. | CFI<br>DFX<br>EGX |        |                | X<br>X<br>X |

| 1  | 0  | CFI<br>DFX<br>EGX | Х      |                | X<br>X      |

Table 5.9. Sequential Fault Table and Simplification of Sequential Fault Table

# (5) Sequential Fault Tree and Result

Figure 5.6. Sequential Fault Tree

From Figure 5.6, it can be determined that the resulting set of optimum test sequences are (X op) = ((00,11,01,01); (01,11,01,01); (01,01,00,11); (10,01,00,11))

#### Ε. Discussion

A fault can sometimes cause R = S = 1 to occur in the transition table. The (11) entry of the table will then provide no information concerning fault detection since the value in the corresponding flow table is a 'don't care' entry. This situation is illustrated by the following example.

### Example 5.2.

If the fault  $d_{1}$  occurs, in the previous network, the excitation and output propositions are reduced to

The excitation, transition, and flow tables are formed as follows:

| $x_1x_2$ |        |      |      |      |  |

|----------|--------|------|------|------|--|

| У        | 00     | 01   | 11   | 10   |  |

| 0        | 00,0   | 00,1 | 11,1 | 01,0 |  |

| 1        | 00,0   | 00,0 | 11,1 | 01,1 |  |

|          | SR - 7 |      |      |      |  |

Table 5.10. Don't Care Entries Caused by Fault d

The entries, which are different from the normal flow table, are marked by circles as shown in Table 5.10. Fortunately, the test sequence for d<sub>1</sub> can be found by the other two circles, (A) and (B), when forming the product table. The 'don't care' conditions are regarded as normal, since they contribute no information for the test sequence. However, if only circles portions of the flow table are don't cares, one cannot detect this particular fault.

### F. Summary

The object of this chapter was to describe a technique for deriving optimum test sequences for synchronous

sequential machines with R-S flip-flops. It is seen that

the reset constraint must be used in the system. Faults

in the reset circuitry were not considered.

The R-S flip-flops are represented by blocks. The technique can be applied to the outside of the blocks. The next chapter will present a conclusion to the study, and some suggestions for further work.

### CHAPTER VI

# CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK

### A. Conclusions

The purpose of this study was to derive fault detection tests for sequential machines. The procedure starts with network analysis. That is, the machines are characterized by input symbols, internal elements and internal states, which are suitable to form a set fault flow tables. An algorithm is then presented to generate the set of optimum test sequences that is guaranteed to produce an output sequence different from the normal output sequence. Then, the set of fault  $(F_p)$  is guaranteed to be detected by the test, if one of the faults in the set occurs.

The sequential machine considered in this study must be in pulse mode operations, since errors caused by timing are not included. Hence the occurance of races, critical or noncritical are automatically avoided.

Besides, oscillations are not allowed to occur in the system; otherwise the technique will not work. Consequently, if no ultimate stable state is entered, the fault cannot be detected.

The possible size of the sequential machine which can be analyzed using flow tables as an approach, is comparatively

small. This is because the size of the flow table and the sequential fault tree will become too large to handle when the network has a large number of primary inputs and gates. However, the procedure may provide the beginning of a clear approach to fault detection in sequential logic.

### B. Suggestions for Further Work

The objective of this section is to present some ideas for more practical approaches to fault detection is sequential logic.

As stated in section 3.3, the path sensitizing concept is fruitful for defining the fault set (F). If a proper set of faults is chosen such that the resulting test can sensitize all the paths within the network, all faults in the network will be detected. So far, the technique for sensitizing the path consisting of feedback loops is still unexplored. An immediate approach to the problem is to break those feedback loops and treat the network as if it were combination logic. However, it is hoped that it would not be necessary to break the feedback loops. Instead, it may be possible to use flow tables as an approach to develop a system which is able to consider feedback loops as a section of the path.

Consider the network in Figure 6.1 as an example: The feedback output Y and network output Z, in terms of

primary inputs and internal connecting lines, with subscription of the gate numbers are found as follows.

$$Z = (e.f)_3$$

=  $((d + c)_{23}f_3)$

Figure 6.1. A Typical Sequential Circuit

$$Z = ((a \cdot b)_{123}) f_3 + c_{23} f_3$$

=  $a_{123} b_{123} f_3 + c_{23} f_3$ , (6.1)

$$Y = (d + c)_2$$

=  $(a \cdot b)_{12} + c_2$

=  $a_{12} b_{12} + c_2$ . (6.2)

The resulting expressions can be called the equivalent normal forms for sequential logic, which is analogous to the enf in combinational logic.

The problem arises when one wishes to generate a set of fault flow tables from the result of the sequential enf.

More work on this technique could be fruitful for fault detection procedures.

The procedures which have been described are limited to pulse mode operation. The extension of the system to machines with fundamental mode operations needs to have some kind of timing analysis for the network, such as associating a fix time delay to each gate. Hence, race conditions and oscillations could be considered. The rest of the procedure is found to have no significant difference for machines with level inputs (fundamental mode operation).

### VII. BIBLIOGRAPHY

- Poage, J.F., "Derivation of Optimum Tests to

Detect Faults in Combinational Circuits", Proc.

1963 Symp. on Math Theory of Automata, Brooklyn,

New York, Polytechniques Press, pp. 483-528.

- Poage, J.F., "Derivation of Optimum Test Procedures for Switching Circuits", Ph.D. Thesis, Department of Electrical Engineering, Princeton University, January, 1963.

- 3. Poage, J.F., "Derivation of Optimum Test Sequences for Sequential Machines", <a href="Proc. 5th Annual Symposium">Proc. 5th Annual Symposium</a> on Switching Circuits, Theory and Logical Design, October, 1964.

- 4. Eldred, R.D., "Test Routines Based on Symbolic Logical Statements", ACM Journal, Vol. 6, pp. 33-36, January, 1959.

- 5. Armstrong, D.B., "On Finding a Near Minimal Set of Fault Detection Tests for Combinational Logic Nets",

IEEE Trans. on Electronic Computers, Vol. EC-15,

pp. 66-73, February, 1966.

- 6. Seshu, S., and Freeman, P.H., "The Diagnosis of Asynchronous Sequential Switching System", IRE

Trans. on Electronic Computers, Vol. EC-11, No. 4,

pp. 459-465, August, 1962.

- 7. Seshu, S., "On an Improved Diagnosis Program",

IEEE Trans. on Electronic Computers (Short Notes),

Vol. EC-14, pp. 76-79, February, 1965.

- Roth, J.P., "A Calculus for Failure Diagnosis",

IBM Watson Research Center, Symposium on the

Organization of Reliable Automata, February, 1966.

- Roth, J.P., "Diagnosis of Automata Failures A Calculus and a Method", IBM Journal, July, 1966.

- 10. McCluskey, E.J., "Introduction to the Theory of Switching Circuits", McGraw-Hill Book Company, Princeton University Series, 1965.

- 11. Hellerman, H., "Digital Computer System Principles",

McGraw-Hill Book Company, 1967.

### VIII. VITA

Chung-tao David Wang was born on December 3, 1943 in China. He received his primary and secondary education in Taipei, Taiwan, China, and attended his undergraduate training at Cheng Kung University in Tainan, Taiwan, China. After his graduation in 1966, he served in the Chinese Army for one year. Then he worked in Thunghi University, Tai-chung, Taiwan, China as a Teaching Assistant of Electrical Engineering until June of 1968.

He has been enrolled in graduate school at the University of Missouri-Rolla and has been a Graduate Assistant in Electrical Engineering since September of 1968.