# FDS0I Process Technology for Subthreshold-Operation Ultralow-Power Electronics

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation     | Vitale, S.A. et al. "FDS0I Process Technology for Subthreshold-<br>Operation Ultralow-Power Electronics." Proceedings of the IEEE<br>98.2 (2010): 333–342. © 2010 IEEE |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| As Published | http://dx.doi.org/10.1109/jproc.2009.2034476                                                                                                                           |  |  |  |

| Publisher    | Institute of Electrical and Electronics Engineers (IEEE)                                                                                                               |  |  |  |

| Version      | Final published version                                                                                                                                                |  |  |  |

|              | i mat published version                                                                                                                                                |  |  |  |

| Citable link | http://hdl.handle.net/1721.1/74123                                                                                                                                     |  |  |  |

# **FDSOI Process Technology for Subthreshold-Operation Ultralow-Power Electronics**

Silicon-on-insulator devices designed for optimum operation at 0.3 V promise longer operational life than conventional application-specific integrated circuits.

By STEVEN A. VITALE, PETER W. WYATT, Member IEEE, NISHA CHECKA, JAKUB KEDZIERSKI, AND CRAIG L. KEAST

ABSTRACT | Ultralow-power electronics will expand the technological capability of handheld and wireless devices by dramatically improving battery life and portability. In addition to innovative low-power design techniques, a complementary process technology is required to enable the highest performance devices possible while maintaining extremely low power consumption. Transistors optimized for subthreshold operation at 0.3 V may achieve a 97% reduction in switching energy compared to conventional transistors. The process technology described in this article takes advantage of the capacitance and performance benefits of thin-body silicon-oninsulator devices, combined with a workfunction engineered mid-gap metal gate.

**KEYWORDS** | Low power; metal gate; silicon-on-insulator (SOI); subthreshold

## I. INTRODUCTION

Ultralow-power (ULP) transistors are an enabling technology for many proposed applications. Ubiquitous sensor networks, RFID tags, implanted medical devices, portable biosensors, handheld devices, and space-based applications are among those which would benefit from extremely low power circuits [1]-[3]. ULP circuits could take advantage

Manuscript received June 4, 2009; revised August 26, 2009. Current version published January 20, 2010. This work was sponsored by the Air Force under contract #FA8721-05-C-0002. Opinions, interpretations, conclusions, and recommendations are those of the author and are not necessarily endorsed by the United States Government.

The authors are with the Solid State Technology Division of Lincoln Laboratory, Massachusetts Institute of Technology, Lexington, MA 02420 USA (e-mail: steven.vitale@ll.mit.edu; wyatt@ll.mit.edu; nchecka@ll.mit.edu; jakub@ll.mit.edu; keast@ll.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2034476

of new energy-harvesting devices which recharge batteries by scavenging power from motion or solar cells, such as a recently demonstrated wristwatch design requiring 50 nA of on-current at 0.42 V operation [4], [5]. In general, low standby power (LSTP) applications require less than 100 pA/ $\mu$ m leakage current, [5] while maximizing the on-current at a modest power supply voltage.

A recent study examined the impact of ULP techniques on a typical sensor system [6]. The analysis assumed ultralow-power digital electronics which consume  $15-20\times$ less energy per operation than conventional ASIC technology. With this assumption, the study showed it would be practical to build a sensor system that would have the same performance characteristics, but operate 4 times as long as would be possible using conventional ASIC digital logic. This paper will explore some of the methods that enable this longer operational lifetime without compromise to system performance.

Subthreshold operation transistors hold great promise for integration into ultralow-power designs, since the most efficient way to reduce power is to reduce the operating voltage [7]. With an operating voltage of 0.3 V, and an oncurrent of less than 1  $\mu$ A/ $\mu$ m, subthreshold transistors use orders of magnitude less power than transistors operated in strong inversion. Subthreshold operation also provides the highest transconductance  $(g_m)$  for a given drain current [8]. In subthreshold, conduction is by diffusion rather than drift, which implies that the on-current is determined by subthreshold swing rather than mobility. Given similar subthreshold swing, it is possible to have equal NMOS and PMOS drive currents per unit of transistor width. This allows equal sizing of NMOS and PMOS transistors in contrast to the typical 2× wider PMOS transistor size for conventional devices, resulting in reduced circuit area and capacitance.

Simply lowering the operating voltage of a conventional high-performance transistor will not produce very good device performance in subthreshold operation. Conventional transistors will have comparatively high off-state leakage and overlap capacitance, as well as poorer subthreshold slope and unequal NMOS and PMOS on-current. By designing a fabrication process from the substrate material through the interconnect metal, optimized for subthreshold transistor performance, it is possible to realize a device with the minimum switching energy and off-state current without significant impact to the energy-delay product. This paper will explore the advantages of SOI technology in ultralowpower applications, and detail the processing techniques which have been employed to optimize the devices for subthreshold operation.

#### II. BULK SILICON VERSUS SOI

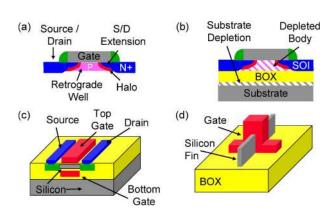

Fig. 1(a) and (b) illustrates a schematic comparison of bulk silicon and SOI transistors. The benefits and disadvantages of SOI vs. bulk silicon technology have been discussed many times [2], [4], [9], [10]. Compared to bulk silicon, SOI provides up to 90% lower junction capacitance, nearideal subthreshold swing, reduced device cross-talk, lower junction leakage, no latch-up, increased radiation hardness, and full dielectric isolation of the transistor. The low junction capacitance is extremely valuable to ultralowpower devices, as it allows reduction of the CV<sup>2</sup> switching energy of the transistor. Another significant advantage for low-power operation is that SOI devices do not suffer from substrate reverse bias effects, in that the depletion charge does not increase when a source potential is applied. Thinbody SOI also provides better electrostatic channel control, leading to reduced source-to-drain leakage and reduced short channel effects (SCE) [11]. In contrast, it has been suggested that bulk silicon is now facing GIDL limits with device scaling, making it inappropriate for ultralowpower applications [5].

Fig. 1. Transistor architectures: (a) bulk silicon, (b) partially depleted SOI, (c) double gate SOI, (d) FinFET. Adapted from Roy [11].

SOI also provides significant advantages for extreme environment operation. At cryogenic temperatures, bulk silicon devices isolated by reverse-biased diodes can suffer from carrier freeze-out and increased crosstalk, to which SOI devices are not susceptible due to the full dielectric isolation. At high temperatures, thermally induced diode leakage is much smaller in SOI devices, due to the reduced junction area. In addition, impact ionization is more strongly balanced by thermal recombination [9]. Functional SOI transistor operation has been demonstrated at 4 K and 573 K [12], [13].

Perhaps the strongest drawbacks of SOI technology are the floating body effects. The body potential can shift over time based on the history of the transistor operation and the generation or recombination of carriers. This can cause shifts in threshold voltage, subthreshold swing, and kinkeffect. Floating body effects can be minimized, though not eliminated, by using thinner silicon.

SOI technology can be fully depleted (FDSOI) or partially depleted (PDSOI). The depletion depth is given by

$$T_{

m dep} = \sqrt{rac{4arepsilon\Phi_f}{qN_{

m ch}}}$$

(1)

where  $\Phi_f = kT \cdot \ln(N_{

m ch}/N_{

m i})/q$  is the Fermi potential,  $N_{

m ch}$ is the channel doping concentration, and  $N_i$  is the intrinsic carrier concentration [7]. When the depletion depth is larger than the physical silicon thickness, a neutral region no longer exists between the source and drain, and the silicon becomes fully depleted [4]. For a highly doped channel where  $N_{\rm ch} = 1 \times 10^{18} \, {\rm cm}^{-3}$ ,  $T_{\rm dep} = 32 \, {\rm nm}$  by (1).

FDSOI is more difficult to fabricate than PDSOI, as the silicon channel must be reduced to a very small and wellcontrolled thickness. Another disadvantage is that series resistance in thin FDSOI can be quite high [14]. Further, unlike a PDSOI device, the FDSOI device is very susceptible to charge in the buried oxide (BOX) layer, which can capacitively couple through the depleted silicon of the body, changing the front channel threshold voltage. However, FDSOI also has important advantages over PDSOI, such as higher  $g_m$  and reduction of floating body effects [4], [7], [14]. A comparison of PDSOI, FDSOI, and bulk silicon technologies is given in Table 1.

For subthreshold transistors, one of the most important FDSOI advantages is the near-ideal subthreshold swing. The drive current in the subthreshold regime is given by:

$$I_{\rm sub} = I_{\rm o} \cdot 10^{\left([V_{\rm gs} + \eta V_{\rm ds}]/S\right)} \cdot \left(1 - e^{-V_{\rm ds}/U_{\rm th}}\right)$$

(2)

where  $I_o$  is a function of the transistor L and W,  $\eta$  is the DIBL factor, S is the subthreshold swing, and  $U_{\rm th}$  is the thermal voltage [1]. Note that subthreshold transistor

Table 1 Comparison of Bulk, PDSOI, and FDSOI Transistors

| Transistor Type                                        | Bulk  | PDSOI  | FDSOI  |  |

|--------------------------------------------------------|-------|--------|--------|--|

| Approximate Substrate<br>Cost (300mm)                  | \$300 | \$1000 | \$1000 |  |

| Active Silicon<br>Thickness (nm)                       | >1000 | ~100   | <40    |  |

| Subthreshold Swing (mV/dec)                            | >120  | 80-120 | 65-80  |  |

| Junction Capacitance                                   | High  | Low    | Low    |  |

| Diode Leakage                                          | High  | Low    | Low    |  |

| V <sub>t</sub> Sensitivity to Si<br>Thickness          | None  | Medium | High   |  |

| Extreme Environment<br>Performance, (<4K or<br>>300°C) | Poor  | Good   | Good   |  |

| Series Resistance                                      | Low   | Medium | High   |  |

| V <sub>t</sub> Sensitivity to BOX<br>Charge            | None  | Low    | High   |  |

| Transconductance                                       | High  | Medium | High   |  |

| Kink Effect                                            | None  | High   | Medium |  |

performance is a strong function of  $\eta$  and S in (2), and will be very sensitive to short channel effects since both  $\eta$  and S increase as gate length decreases. BOX thickness can be varied to achieve a tradeoff between on-current and offcurrent; thinner BOX improves DIBL but degrades S [1].

The subthreshold  $I_{\rm on}/I_{\rm off}$  ratio is derived from (2) to be simply

$$I_{\rm on}/I_{\rm off} = 10^{\rm V_{\rm gs}/S} \tag{3}$$

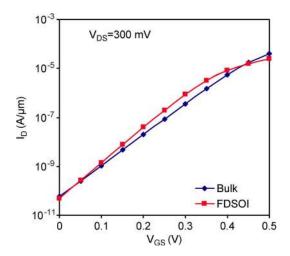

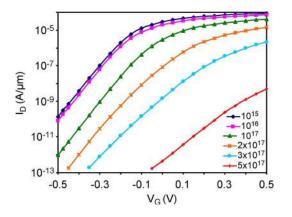

thus *S* is a critical parameter for subthreshold operation. Simulations using the ATLAS device simulator predict that at low operating voltages ( $V_{dd} = 0.3 \text{ V}$ ), FDSOI devices still provide a superior subthreshold slope to bulk silicon devices, as shown in Fig. 2. Therefore an optimized ultralow-power process technology will benefit from the lower subthreshold swing and capacitance provided by FDSOI.

## III. CHANNEL DOPING

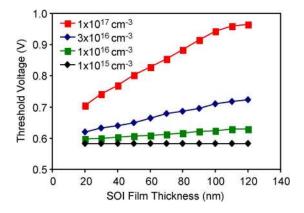

The threshold voltage is a strong function of silicon film thickness when using FDSOI with highly doped channels.

Fig. 2. Simulation of ultralow-power transistors, for 65 nm gate length. FDSOI exhibits improved subthreshold slope and thus a 2.5 $\times$  improvement in  $I_{on}/I_{off}$  ratio at 0.3 V operating voltage compared to bulk silicon.

$V_t$  changes by approximately 4 mV per 1 nm silicon thickness when the doping level is  $1 \times 10^{17}$  cm<sup>-3</sup>, according to the data reproduced in Fig. 3 from Hsiao [15]. By comparison, when the channel doping is extremely low, below  $5 \times 10^{15}$  cm<sup>-3</sup>,  $V_t$  is effectively independent of silicon film thickness. Since  $V_t$  control is critical for subthreshold transistors, it is highly desirable to use undoped (or more precisely, lightly doped) FDSOI, particularly for deeply scaled designs [14].

An undoped channel has additional benefits, including no  $V_t$  variation due to random dopant fluctuations, as well as higher carrier mobility. In addition, the depletion thickness given by (1) is large when the channel is undoped, which allows a more manufacturable silicon thickness to be used while maintaining the benefits of a FDSOI as opposed to a PDSOI device. Furthermore, low channel

Fig. 3. Threshold voltage as a function of silicon thickness and channel doping. Adapted from Hsiao [15].

doping will reduce band-to-band tunneling and increase the S/D breakdown voltage, which could be important when integrating 3.3 V I/O transistors on the same chip as the subthreshold transistors [2], [14].

There are disadvantages to using an undoped channel as well. SCEs are more difficult to control without channel doping, though thin-body FDSOI is less sensitive to SCEs than bulk silicon devices [11]. Additionally, threshold voltage adjustments are more difficult without channel doping; this issue is discussed further in Section IV. Thus there are trade-offs involved with using undoped silicon channels, and it is likely that highly doped SOI will remain the standard for high-performance devices, whereas for ultralow-power devices the undoped channel advantages are compelling.

#### IV. GATE FABRICATION

When simplified to ignore back-channel effects, the threshold voltage of an SOI transistor is given by:

$$V_{t} = \Phi_{\rm ms} + 2\Phi_{f} - \frac{1}{C_{\rm ox}} \left( Q_{\rm it} + q \int_{0}^{t} \rho(x) dx - q N_{\rm ch} t_{\rm soi} \right)$$

(4)

where  $\Phi_{ms}$  is the gate-to-semiconductor workfunction difference, Cox is the gate dielectric capacitance, Qit is the dielectric interface charge,  $\rho(x)$  is the charge density in the dielectric, and  $t_{\rm soi}$  is the silicon thickness. When  $N_{\rm ch}$  is high,  $V_t$  is a sensitive function of  $t_{soi}$ , which is a drawback for thin FDSOI. However, when the channel is undoped, the Fermi potential and the depletion charge are approximately zero, and the expression for the threshold voltage becomes:

$$V_t = \Phi_{\rm ms} - \frac{Q_f}{C_{\rm ox}} \tag{5}$$

where  $Q_f$  is the total charge in the gate dielectric. Thus the threshold voltage of the transistor is essentially set by the gate workfunction.

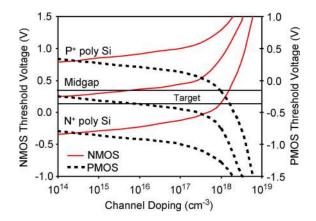

Fig. 4 shows a graphical representation of (4), illustrating  $V_t$  as a function of  $N_{ch}$  for  $N^+$  poly,  $P^+$  poly, and mid-gap gates [10]. There are two solutions for achieving a threshold voltage of  $\sim$ 0.35 V, band-edge gate materials with high channel doping  $(1 \times 10^{18} \text{ cm}^{-3})$ , or a mid-gap gate material with very low channel doping  $(1 \times 10^{15} \text{ cm}^{-3})$ . As described in Section III, the undoped channel solution is preferred for subthreshold-optimized transistors.

Therefore, a workfunction-engineered mid-gap metal gate material [10], [16], [17] should be used to provide symmetric threshold voltages for NMOS and PMOS. There

Fig. 4. Threshold voltages of FDSOI NMOS and PMOS with mid-gap,  $N^+$  poly, and  $P^+$  poly gates as a function of SOI doping concentration. 10 nm-thick SOI and 5 nm-thick gate oxide are assumed. Adapted from Shimada [10].

are several literature examples of successful integration of mid-gap metal gate transistors, including SiGe [15], Ta [10], [18], and TiN [19]-[26].

A metal gate stack typically consists of a thin metal layer sandwiched between a thicker polysilicon layer above, and the gate dielectric below. The gate dielectric may be a conventional SiO2 or SiON gate oxide, or a high-k gate dielectric such as HfSiON. To prevent GOI issues, it is important that there is little diffusion of metal into the gate dielectric, or reaction between the metal and the dielectric. It is also important to minimize trapped charges in the gate dielectric (for example, during plasma sputtering of the metal gate material), which can shift the  $V_t$  of the transistor according to (4). Such charging effects have been noted after Ta gate deposition by Ar+ sputtering, where an oxide charge density of  $5 \times 10^{11}~\text{cm}^{-2}$  caused a 0.1 V shift in  $V_t$  [10].

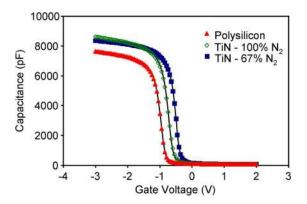

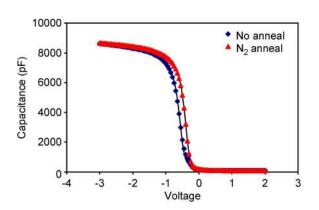

TiN is a suitable mid-gap metal, with the advantage of being an accepted CMOS-compatible material. To evaluate the integration of TiN as a mid-gap metal gate material, capacitors were fabricated using 4 nm-thick SiO2, 20 nmthick TiN, and 200 nm-thick polysilicon. The capacitors were then phosphorous doped and capped with 250 nmthick Al. Fig. 5 shows C-V curves comparing poly and two TiN gates with different N<sub>2</sub> flow rates during TiN PVD. The curves are fit with a quantum-corrected capacitor model from NCSU [27] to extract workfunction, equivalent oxide thickness (EOT), and other parameters. The workfunction of the TiN gates increases toward mid-gap compared to the N<sup>+</sup> poly gates, with  $\Phi_m = 4.45$  eV and 4.60 eV for  $100\% \text{ N}_2$  flow and  $66\% \text{ N}_2$  flow (balance Ar) during TiN deposition. To increase  $\Phi_m$  further, several postdeposition TiN anneal experiments were performed. A subatmospheric 626 °C N2 anneal after TiN deposition increases  $\Phi_m$  by 0.10–0.15 eV (Fig. 6), enabling tuning of the effective workfunction across the mid-gap range [28].

Fig. 5. C-V curves of 1 mm2 MOS capacitors, for TiN metal gates under two different TiN deposition conditions, and a polysilicon gate. TiN gates clearly show an increase in flatband voltage, and thus  $\phi_{

m ms}$ , toward the silicon mid-gap. Metal gates also show increased accumulation capacitance due to elimination of poly depletion. Lines are quantum-corrected model fit to the data.

Etching the TiN gate metal without damaging the polysilicon above the TiN or the gate dielectric below requires a delicate balance of plasma processing conditions. Lateral etching or notching of the overlying polysilicon could lead to undesirable penetration of implant species into the active channel beneath the gate, causing severe SCEs. Notching of the metal gate may lead to similar implant issues, as well as delamination of the narrower gates. A large foot on the metal must be avoided, as this will cause an undesirable increase in  $C_{gd}$ . Plasma etching selectivity to the underlying gate dielectric material is crucial, as punch-through of the gate dielectric will cause severe leakage or complete failure of the thin SOI device. Microloading effects must be minimized, to ensure that both dense and isolated gates have similar critical dimension (CD) and profile, in order to reduce variation in the transistor parametrics across the chip.

Fig. 6. C-V curves of 1 mm2 MOS capacitors, for TiN metal gates with and without 626  $^{\circ}$ C  $N_2$  anneal. Anneal shifts metal gate workfunction by 100 meV toward silicon mid-gap. Solid lines are quantum-corrected model fit to the data.

#### V. SPACER OPTIMIZATION

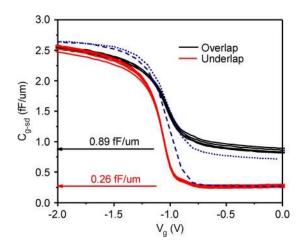

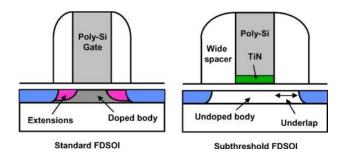

Eliminating the S/D extension implants (LDD implants) and increasing the spacer thickness results in a gate-to-S/D underlap which provides several benefits for ultralowpower operation. Most importantly, reduced overlap capacitance will allow lower CV<sup>2</sup> switching energy. In addition, increased spacer thickness will reduce subthreshold leakage, gate leakage, and DIBL. Simulations have shown that an optimized underlap can yield a 70% reduction in SRAM cell leakage and 200× lower cell read failure probability [11]. Since channel hot carrier (CHC) effects are not significant at low V<sub>dd</sub>, the LDD implants are not required to maintain device reliability. Note that gate-to-S/D underlap can improve performance for FDSOI transistors as described above, whereas for conventional bulk silicon transistors the subthreshold slope would degrade significantly as the underlap increases.

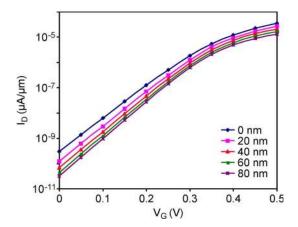

The simulations of NMOS and PMOS  $I_d - V_g$  curves for a ULP device at various gate-to-S/D underlap distances shown in Fig. 7 demonstrate that for  $L_g = 150$  nm an optimized subthreshold slope and off-current occur for a 60 nm underlap. There have been some limited simulations of underlapped designs for shorter gate lengths. The optimum underlap for a FinFET with  $L_g = 20$  nm was shown to be about 12 nm [29]. For a planar double-gate SOI design with  $L_g = 16$  nm, subthreshold slope improves as the underlap increases to 16 nm [30]. Though the "optimum" underlap depends on which performance parameters one is trying to optimize, the above studies suggest the gate-to-S/D underlap should be approximately 0.5 to 1 times the gate length. Connelly has also described the use of an underlapped S/D technology for ultralowpower FDSOI, though in that case the underlap was only 4-9 nm [31]. That work also proposed the use of Schottky S/D to reduce the parasitic resistance of thin-body SOI.

Fig. 7. Simulated NMOS transistor I-V characteristics for 150 nm gate length ULP device, as a function of the S/D to gate underlap distance ( $V_{dd} = \textbf{0.3 V}$ ). Subthreshold swing decreases from 79 mV/decade at O nm underlap to 69 mV/decade at 80 nm underlap.

Fig. 8. Comparison of total gate-to-S/D overlap capacitance ( $C_{\rm gd} + C_{\rm gs}$ ) of conventional and ULP transistor designs, on 180 nm ( $W = 100 \mu m$ ) PMOS transistors. Solid lines: measured data, dashed lines: ATLAS model simulation. ULP underlap design reduces capacitance by 71% compared to the standard overlap transistor design, with good agreement to device simulation.

Fig. 8 compares experimental C-V curves from conventional devices and subthreshold-optimized devices with a 60 nm gate-to-S/D underlap. The capacitance for the underlapped devices is reduced by 71%.

Because of the gate-to-S/D underlap, there is a relatively wide region between the source and the gate which is not effectively controlled by the gate voltage. Carriers must diffuse through this region before they reach the channel under gate control. Simulations provided in Fig. 9 predict that as the doping level in the underlap region (and under the gate) increases above  $1 \times 10^{16}$  cm<sup>-3</sup>, the drive current collapses. The underlap region becomes a high and wide barrier on the source side as body doping increases, and

Fig. 9. Model NMOS transistor I-V characteristics for 150 nm polysilicon gate ULP FDSOI device with 60 nm of gate-to-S/D underlap, as a function of body doping (atoms/cm $^3$ ).  $V_{dd} = 0.3 \ V$ . Increasing body doping causes a strong decrease in drive current due to the high and wide barrier in the source side underlap region.

Fig. 10. Schematic of standard FDSOI and subthreshold-optimized ultralow-power (ULP) FDSOI transistors.

fewer carriers have the energy to tunnel through the barrier into the channel. Thus when a wide underlap is employed, the body doping must be kept very light. Fortunately, this is consistent with using a single mid-gap metal gate to set the threshold voltage.

To summarize, a schematic comparison between conventional and subthreshold-optimized ultralow-power transistors is shown in Fig. 10, illustrating the undoped body, elimination of S/D extension implants, and wide spacers.

#### VI. INTERCONNECT OPTIMIZATION

The current through the interconnect routing will be relatively small for ultralow-power circuits, and the standard interconnect metallization will be significantly oversized. At low current densities, electromigration is not a serious issue, nor is ohmic heating. It is therefore possible to reduce the capacitance of the circuit further by reducing the thickness of the interconnect metal. The increased interconnect resistance is not significant, since the resistance of the thin body transistor will be much larger than that of the interconnect.

Though the maximum possible reduction in interconnect thickness will depend on the details of the individual circuit design, a 50% reduction is conservative for most cases. ATLAS device simulations have been performed on a transistor driving a given length of interconnect to calculate the resistance and capacitance of the device. Due to the 60 nm underlap, the resistance of the FDSOI ultralowpower transistor is 114 times higher than that of a conventional bulk silicon transistor with no underlap. The capacitance, however, is decreased by 78%.

The characteristic switching time of the device is given by:

$$t_c = (R_t + R_i) \cdot (C_t + C_i) \tag{6}$$

where *t* and *i* indicate the transistor and the interconnect lines, respectively. The simulation results are given in

Table 2 ULP Transistor Simulation Results

| Device Design                                | $V_{dd}$ | Switching<br>time<br>(ps) | Switching<br>energy<br>(fJ) | Energy-delay<br>product<br>(fJ•ps) |

|----------------------------------------------|----------|---------------------------|-----------------------------|------------------------------------|

| Conventional Bulk Si<br>+ Conventional Metal | 1.2      | 11                        | 2.59                        | 28                                 |

| ULP Bulk Si<br>+ Conventional Metal          | 0.3      | 2750                      | 0.23                        | 641                                |

| ULP Bulk Si<br>+ ULP Metal                   | 0.3      | 2211                      | 0.21                        | 458                                |

| ULP FDSOI<br>+ Conventional Metal            | 0.3      | 308                       | 0.11                        | 34                                 |

| ULP FDSOI<br>+ ULP Metal                     | 0.3      | 176                       | 0.07                        | 12                                 |

Table 2. A 50% reduction in interconnect metal thickness (designated ULP Metal) reduces  $t_c$  by 40%. The simulation predicts that the total CV2 switching energy of the optimized FDSOI ultralow-power device is reduced by 97% compared to a traditional 1.2 V transistor. This exceeds the requirement for the 20× power reduction called for in Section I to enable the sensor application.

# VII. SUBTHRESHOLD OPTIMIZED TRANSISTOR PERFORMANCE

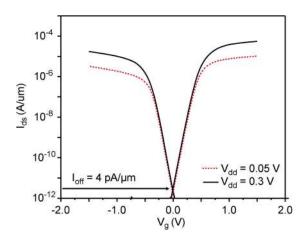

FDSOI ultralow-power transistors were fabricated with the integration optimized for subthreshold operation as outlined above. NMOS and PMOS  $I_d$ – $V_g$  characteristics are shown in Fig. 11, for mid-gap metal gate transistors with  $L_{\rm g}=150$  nm and  $W=8~\mu{\rm m}$ . Nitride spacer thickness is 90 nm, yielding a 60 nm gate-to-S/D underlap after an 8 s, 1022 °C activation anneal. The TiN gate workfunction tuning provides closely matched NMOS and

Fig. 11. Representative ULP transistor I-V curves with a 150 nm TiN metal gate (W = 8  $\mu$ m). The devices show very good subthreshold performance, and nearly ideal workfunction tuning.

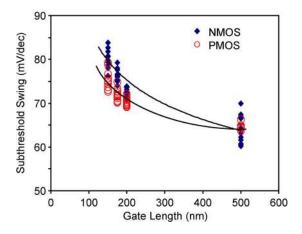

Fig. 12. Subthreshold swing for 12 NMOS and 12 PMOS mid-gap metal gate transistors at 4 gate lengths, on a single wafer. S is near ideal at 64 mV/dec for 500 nm gates, but increases due to SCEs.  $V_{\rm dd} = {\it O.3} \ {\it V}, W = {\it S} \ \mu {\it m}.$

PMOS  $I_{on}(V_g = +/-0.3 \text{ V})$  and  $I_{off}(V_g = 0 \text{ V})$  performance. It has been proposed that a suitable leakage limit for ultralow-power handheld electronics is 20–50 pA/ $\mu$ m, [5] which is well above the 4 pA/ $\mu$ m off-current of these FDSOI subthreshold-optimized transistors.

The subthreshold swing (S) for the fabricated mid-gap gate ultralow-power transistors is shown in Fig. 12 as a function of gate length. For long-channel devices ( $L_g$  = 500 nm) S is nearly ideal at 64 mV/decade. As the gate length decreases, S increases to 80 mV/decade due to SCE. The subthreshold swing is lower for PMOS than for NMOS due to the difference in effective channel length for these underlapped devices; under the current process conditions, the NMOS phosphorus implant apparently diffuses farther than the boron PMOS implant, resulting in a shorter NMOS channel for a given gate length.

# VIII. MANUFACTURABILITY AND **FUTURE DIRECTIONS**

SOI-based CMOS is commonly used today in high performance applications, such as gaming consoles (Wii, Xbox, PS3) [5]. However low-power applications are generally more cost sensitive than are high-performance applications, which has put the more expensive SOI starting material at a disadvantage. The process optimizations outlined in this paper help to minimize cost as well as provide enhanced ultralow-power performance. Using undoped channels with no LDD implants will eliminate four or more mask levels from the process. A single mid-gap metal gate transistor requires many fewer processing steps than a dual band-edge metal gate design. Further, gate-first processing is also much less costly than gate-last (fully silicided or damascene gate) processing. Aside from thinning the silicon thickness to 40 nm or less, there are few

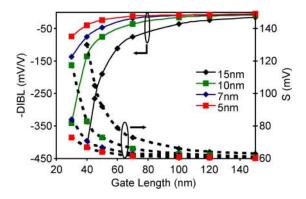

Fig. 13. Quasi-2-D estimates of S and DIBL in FDSOI MOSFETs as a function of  $L_{\rm g}$  for  $t_{\rm Si}=$  15, 10, 7, and 5 nm. As  $t_{\rm Si}$  is reduced, both DIBL and S decrease significantly at shorter gate lengths. Adapted from Trivedi [14].

additional processing challenges associated with fabricating SOI devices compared to bulk silicon devices. FDSOI transistors are susceptible to  $V_t$  shifts due to trapped charge in the buried oxide layer, and they can show kink effect at high currents. However ultralow-power designs by definition are low current, and thus will not show significant kink effects.

Scaling gate length while maintaining reliable device performance is as challenging for ultralow-power transistor design as it is for high-performance transistors. For gate lengths below 100 nm, SCEs will increase DIBL and subthreshold swing unless the silicon channel thickness is also scaled. Fig. 13 is reproduced from Trivedi [12], showing that  $t_{Si}$  will have to be reduced to ultra-thin values below 15 nm to prevent leakage current from increasing. Though ultra-thin SOI devices have been fabricated for several research publications, the technology has not yet been demonstrated in a manufacturable way across 300 mm wafers.

At very thin silicon thicknesses, quantization effects have significant effects and  $V_t$  is again a function of  $t_{Si}$ . Mobility is also degraded, due to higher phonon and surface scattering. If a practical silicon thickness limit of 5 nm is assumed, the minimum gate length which allows acceptable ultralow-power performance is 25–30 nm [14].

Beyond this limit, nonplanar devices with enhanced channel control may be required. Fig. 1(b)-(d) compare several transistor technologies: SOI, double gate SOI, and FinFET. Double or triple gate designs can provide improved channel control, lower leakage, and improved SCEs [11]. Further, it has been shown that a mid-gap double gate will have lower subthreshold leakage and gate leakage than designs with band-edge gates [11]. However, the high cost associated with increased process integration complexity makes them less desirable for ultralow-power electronics at the present time. This may change if FinFETs or other multiple gate transistor designs become mainstream technology at the 22 nm-node or below.

#### IX. CONCLUSION

Widespread adoption of SOI technology will require significant performance advantages over bulk silicon to justify the higher cost of the SOI substrate, the additional processing steps associated with thinning and control of the active silicon thickness, and the development of infrastructure to support design kits, EDAs, and standard cell libraries. The processing technology for subthresholdoptimized transistors described in this paper has enabled the verification of several performance advantages of ultralow-power FDSOI devices. By designing the transistor from the substrate through the interconnect levels for subthreshold operation, the switching energy of the device is decreased by 97% with modest impact to the energydelay product. ■

#### REFERENCES

- [1] D. Bol, R. Ambroise, D. Flandre, and J.-D. Legar, "Sub-45 nm fully-depleted SOI CMOS subthreshold logic for ultra-low-power applications," in 2008 IEEE Int. SOI Conf. Proc., Oct. 2008, pp. 57-58.

- [2] A. Uchiyama, S. Baba, Y. Nagatomo, and J. Ida, "Fully depleted SOI technology for ultra low power digital and RF applications," in 2006 IEEE Int. SOI Conf. Proc., Oct. 2006, pp. 15–16.

- [3] B. H. Calhoun, D. C. Daly, N. Verma, D. F. Finchelstein, D. D. Wentzloff, A. Wang, S.-H. Cho, and A. P. Chandrakasan, "Design considerations for ultra-low energy wireless microsensor nodes," *IEEE Trans. Comput.*, vol. 54, pp. 727-740, Jun. 2005.

- [4] A. Ebina, T. Kadowaki, Y. Sato, and M. Yamaguchi, "Ultra low-power CMOS IC using partially-depleted SOI technology," in Proc. Custom Integrated Circuits Conf., May 2000, pp. 57-60.

- [5] J. Cai, Z. Ren, A. Majumdar, T. H. Ning, H. Yin, D.-G. Park, and W. E. Haensch, "Will SOI have a life for the low-power

- market?" in 2008 IEEE Int. SOI Conf. Proc., Oct. 2008, pp. 15-16.

- [6] M. Gouker, MIT Lincoln Laboratory. Private Communication.

- [7] J.-L. Pelloie, "SOI for low-power low-voltage—Bulk versus SOI," Microelectronic Engineering, vol. 39, pp. 155-166, 1997.

- [8] E. Vittoz, "Micropower techniques," in Design of Analog-Digital VLSI Circuits for Telecommunications and Signal Processing, J. Franca and Y. Tsividis, Eds. Englewood Cliffs, NJ: Prentice-Hall, 1994.

- [9] J. L. Pelloie, C. Raynaud, O. Faynot, A. Grouillet, and I. Du Port de Pntcharra, "CMOS/SOI technologies for low-power and low-voltage circuits," Microelectronic Engineering, vol. 48, pp. 327-334, 1999.

- [10] H. Shimada, Y. Hirano, T. Ushiki, K. Ino, and T. Ohmi, "Tantalum-gate thin-film SOI nMOS and pMOS for low-power applications," IEEE Trans. Electron Devices, vol. 44, pp. 1903-1907, 1997.

- [11] K. Roy, H. Mahmoodi, S. Mukhopadhyay, H. Ananthan, A. Bansai, and T. Cakici,

- "Double-gate SOI devices for low-power and high-performance applications," in Proc.~19thInt. Conf. VLSI Design, Jan. 2006, pp. 445-452.

- [12] E. Simoen and C. Claeys, "The cryogenic operation of partially depeleted silicon-on-insulator inverters," IEEE Trans. Electron Devices, vol. 42, pp. 1100-1105, Jun. 1995.

- [13] Y. Li, G. Niu, J. D. Cressler, J. Patel, S. T. Liu, R. A. Reed, M. M. Mojarradi, and B. J. Blalock, "The operation of 0.35  $\mu\mathrm{m}$ partially depleted SOI CMOS technology in extreme environments," Solid-State Electron., vol. 47, pp. 1111-1115, 2003.

- [14] V. P. Trivedi and J. G. Fossum, "Scaling fully depleted SOI CMOS," IEEE Trans. Electron Devices, vol. 50, pp. 2095-2103, 2003.

- [15] T. C. Hsiao, A. W. Wang, K. Saraswat, and J. C. S. Woo, "An alternative gate electrode material of fully depleted SOI CMOS for low power applications," in *Proc.* 1997 IEEE Int. SOI Conf., Oct. 1997, pp. 20-21.

- [16] H. Shang and M. H. White, "An ultra-thin midgap gate FDSOI MOSFET," Solid State Electron., vol. 44, pp. 1621-1625, 2000.

- [17] J. Chen, B. Maiti, D. Connelly, M. Mendicino, F. Huang, O. Adetutu, Y. Yu, D. Weddington, W. Wu, J. Canelaria, D. Dow, P. Tobin, and J. Mogab, "0.18  $\mu$ m metal gate fully-depleted SOI MOSFETs for advanced CMOS application," in 1999 Symp. VLSI Technol. Dig. Tech. Papers, 1999, pp. 25-26.

- [18] H. Shimada, T. Ushiki, Y. Hirano, and T. Ohmi, "Tantalum-gate SOI MOSFET's featuring excellent threshold voltage control in low-power applications," in Proc. 1995 IEEE Int. SOI Conf., Oct. 1995, pp. 96-97.

- [19] Y. Liu, S. Kijima, E. Sugimata, M. Masahara, K. Endo, T. Matsukawa, K. Ishii, K. Sakamoto, T. Sekigawa, H. Yamauchi, Y. Takanashi, and E. Suzuki, "Investigation of the TiN gate electrode with tunable work function and its application for FinFET fabrication, IEEE Trans. Nanotechnol., vol. 5, pp. 723-726, Nov. 2006.

- [20] R. Singanamalla, J. Lisoni, I. Ferain, O. Richard, L. Carbonell, T. Schram, H. Y. Yu, S. Kubicek, S. De Gendt, M. Jurczak, and K. De Meyer, "Electrical and material evaluation of the MOCVD TiN as metal gate electrode for advanced CMOS technology," in Mater. Res. Soc. Symp. Proc., 2006, vol. 917, pp. 174-197.

- [21] C. Fenouillet-Beranger, S. Denorme, B. Icard, F. Boeuf, J. Coignus, O. Faynot, L. Brevard, C. Buj, C. Soonekindt, J. Todeschini, I.C. Le-Denmat, N. Loubet, C. Gallon, P. Perreau, S. Manakli, B. Mmghetti, L. Pain, V. Arnal, A. Vandooren, D. Aime, L. Tosti, C. Savardi, F. Martin, T. Salvetat, S. Lhostis, C. Laviron, N. Auriac, T. Kormann, G. Chabanne, S. Gaillard, O. Belmont, E. Laffosse, D. Barge, A. Zauner, A. Tarnowka, K. Romanjec, H. Brut, A. Lagha, S. Bonnetier, F. Joly, N. Mayet, A. Cathignol, D. Galpin, D. Pop, R. Delsol, R. Pantel, F. Pionnier, G. Thomas, D. Bensahel, S. Deleombus, T. Skotnicki, and H. Mmgam, "Fully-depleted SOI technology using high-K and single-metal

- gate for 32 nm node LSTP applications featuring 0.179  $\mu\mathrm{m}^2$  6T-SRAM bitcell," in Tech. Dig. Int. Electron Devices Meeting (IEDM), Dec. 2007, pp. 267-270.

- [22] F. Andrieu, C. Dupre, F. Rochette, O. Faynot, L. Tosti, C. Buj, E. Rouchouze, M. Casse, B. Ghyselen, I. Cayrefoureq, L. Brevard, F. Allain, J. C. Barbe, J. Cluzel, A. Vandooren, S. Denorme, T. Ernst, C. Fenouillet-Beranger, C. Jahan, D. Lafond, H. Dansas, B. Previtali, J. P. Colonna, H. Grampeix, P. Gaud, C. Mazure, and S. Deleonibus, "25 nm short and narrow strained FDSOI with TiN/HfO2 gate stack," in 2006 Symp. VLSI Technol. Dig. Tech. Papers, 2006, pp. 134-135.

- [23] V. Barral, T. Poiroux, F. Andrieu, C. Buj-Dufournet, O. Faynot, T. Ernst, L. Brevard, C. Fenouillet-Beranger, D. Lafond, J.M. Hartmann, V. Vidal, F. Allain, N. Daval, I. Cayrefourcq, L. Tosti, D. Munteanu, J.L. Autran, and S. Deleonibus, "Strained FDSOI CMOS technology scalability down to 2.5 nm film thickness and 18 nm gate length with a TiN/HfO<sub>2</sub> gate stack," in *Tech*. Dig. Int. Electron Devices Meeting (IEDM), Dec. 2007, рр. 61-64.

- [24] B. Doris, Y. H. Kim, B. P. Linder, M. Steen, V. Narayanan, D. Boyd, J. Rubino, L. Chang, J. Sleight, A. Topol, E. Sikorski, L. Shi, L. Wong, K. Babich, Y. Zhang, P. Kirsch, Newbury, J. F. Walker, R. Carruthers, C. D'Emic, P. Kozlowski, R. Jammy, K. W. Guarini, and M. Leong, "High performance FDSOI CMOS technology with metal gate and high-k," in 2005 Symp. VLSI Technol. Dig. Techn. Papers, 2005, pp. 214-215.

- [25] F. Andrieu, O. Faynot, X. Garros, D. Lafond, C. Buj-Dufournet, L. Tosti, S. Minoret, V. Vidal, J. C. Barbe, F. Allain, E. Rouchouze, L. Vandroux, V. Cosnier, M. Casse, V. Delaye, C. Carabasse, M. Burdin, G. Rolland, B. Guillaumot, J. P. Colonna, P. Besson, L. Brevard, D. Mariolle, P. Holliger,

- A. Vandooren, C. Fenouillet-Beranger, F. Martin, and S. Deleonibus, "Comparative scalability of PVD and CVD TiN on HfO2 as a metal gate stack for FDSOI cMOSFETs down to 25 nm gate length and width," in IEDM Tech. Dig., 2006, 23.7.

- [26] N. Collaert, M. Demand, I. Ferain, J. Lisoni, R. Singanamalla, P. Zimmerman, Y. S. Yim, T. Schram, G. Mannaert, M. Goodwin, J. C. Hooker, F. Neuilly, M. C. Kim, K. De Meyer, S. De Gendt, W. Boullart, M. Jurezak, and S. Biesemans, "Tall triple-gate devices with TiN/HfO2 gate stack," in 2005 Symp. VLSI Technol. Dig. Tech. Papers, 2005, pp. 108-109.

- [27] N. Yang, W. K. Henson, J. R. Hauser, and J. J. Wortman, "Modeling study of ultrathin gate oxides using direct tunneling current and capacitance-voltage measurements in MOS devices," IEEE Trans. Electron Devices, vol. 46, pp. 1464-1471, Jul. 1999.

- [28] S. A. Vitale, J. Kedzierski, P. Healey, N. Checka, P. W. Wyatt, and C. L. Keast, "Workfunction-tuned TiN metal gate FDSOI transistors for subthreshold operation," IEEE Trans. Electron Devices, in review.

- [29] A. B. Sachid, C. R. Manoj, D. K. Sharma, and V. R. Rao, "Gate fringe-induce barrier lowering in underlap FinFET structures and its optimization," IEEE Electron Device Letters, vol. 20, pp. 128-130, Jan. 2008.

- [30] A. Kranti, Y. Hao, and G. A. Armstrong, 'Performance projections and design optimization of planar double gate SOI MOSFETs for logic technology applications," Semicond. Sci. Technol., vol. 23, pp. 1–13,

- [31] D. Connelly, P. Clifton, C. Faulker, and D. E. Grupp, "Ultra-thin-body fully depleted SOI metal source/drain n-MOSFETs and ITRS low-standby-power targets through 2018," in IEEE Int. Electron Devices Meeting (IEDM) Tech. Dig., Dec. 2005, pp. 972-975.

#### ABOUT THE AUTHORS

Steven A. Vitale received the B.S. degree in chemical engineering from Johns Hopkins University, Baltimore, MD, the M.S. degree in nuclear engineering from Massachusetts Institute of Technology (MIT), Cambridge, and the Ph.D. degree in chemical engineering from MIT.

From 2001 to 2007 he was a Technical Staff Member at Texas Instruments, developing plasma processes for the 90 nm to 45 nm technology nodes. In 2007 he became a Technical Staff

Member at M.I.T. Lincoln Laboratory, and is currently pursuing research activities in the Advanced Silicon Technology Group focused on ultralowpower electronics, micro electron beam arrays, and novel plasma processes

Peter W. Wyatt (Member, IEEE) received the B.S. degree from California Institute of Technology, Pasadena, and the Ph.D. degree from Yale University, New Haven, CT.

Prior to joining Massachusetts Institute of Technology (MIT) Lincoln Laboratory in 1977, he worked for several years at Bell Laboratories on tantalum thin-film integrated circuits. He is currently a Senior Member of Technical Staff in the Advanced Silicon Technology Group, with partic-

ular interest in SOI transistor fabrication, modeling, and testing. He led efforts at Lincoln Laboratory in wafer-scale integration and in SPICE model development for FDSOI transistors.

Nisha Checka received the S.B., M.Eng., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, in 2001, 2001, and 2005, respectively.

From 2005 to 2008, Dr. Checka was a technical staff member of the Advanced Silicon Technology Group at MIT Lincoln Laboratory, where she worked on ultralow-power electronics and circuit architectures for 3-D integration. In 2008, she founded GoofyFoot Labs, where she is currently Chief Executive Officer. Her research interests include low-power electronics and CAD tools for advanced semiconductor technologies.

Jakub Kedzierski received the Ph.D. degree in electrical engineering from the University of California, Berkeley, in 2001.

Following his graduation he worked at IBM's T. J. Watson Research Center on advanced silicon devices. In 2005 he moved to Massachusetts Institute of Technology (MIT) Lincoln Laboratory, where he is currently the Assistant Group Leader in the Advanced Silicon Technology Group. His research interests have included: FinFETs, silicon

nanowires, fully silicided gates, metal source/drains, and FDSOI technology. Current research efforts are focused on graphene transistors, low-power electronics, and electrocapillary microfluidics.

Craig L. Keast received the B.A. degree from Hamilton College, Clinton, NY, and the S.M., E.E., and Ph.D. degrees in electrical engineering and computer science from Massachusetts Institute of Technology (MIT), Cambridge.

He is the Associate Head of the Solid State Division and Director of Operations for the Microelectronics Laboratory at MIT Lincoln Laboratory. From 1981 to 1988 he was employed at Lincoln Laboratory, where he worked on semiconductor

processing and technology development for the Digital Wafer-Scale Electronics group. After completing his Ph.D. degree in 1992, he returned to Lincoln Laboratory, where he first worked with the Submicrometer Technology Group on deeply-scaled device development using advanced optical lithography techniques. His current research activities center on deep-submicron, low-power CMOS process development, RF and optical MEMS, and 3-D circuit integration technologies.