Received 17 July 2018; revised 5 October 2018 and 23 November 2018; accepted 22 January 2019. Date of publication 31 January 2019; date of current version 1 March 2019. The review of this paper was arranged by Editor M. K. Radhakrishnan.

Digital Object Identifier 10.1109/JEDS.2019.2895367

# Ferroelectric Field Effect Transistors Based on PZT and IGZO

CRISTINA BESLEAGA<sup>®</sup>, ROXANA RADU, LILIANA-MARINELA BALESCU, VIORICA STANCU, ANDREEA COSTAS, VIOREL DUMITRU<sup>®</sup>, GEORGE STAN, AND LUCIAN PINTILIE

Laboratory of Multifunctional Materials and Structures, National Institute of Materials Physics, 077125 Măgurele, Romania

CORRESPONDING AUTHOR: C. BESLEAGA (e-mail: cristina.besleaga@infim.ro)

This work was supported in part by the Romanian Ministry of Research and Innovation and in part by the Executive Unit for Financing Higher Education and Innovation, National Council of Scientific Research (CNCS-UEFISCDI) under Grant PN-II-RU-TE-2014-4-1122 and Grant PN-III-P1-1.1-PD-2016-1546.

**ABSTRACT** Ferroelectric field effect transistors (FeFETs) based on lead zirconate titanate (PZT) ferroelectric material and amorphous-indium-gallium-zinc oxide (a-IGZO) were developed and characterized. The PZT material was processed by a sol-gel method and then used as ferroelectric gate. The a-IGZO thin films, having the role of channel semiconductor, were deposited by radio-frequency magnetron sputtering, at a temperature of  $\sim 50^{\circ}$ C. Characteristics of a typical field effect transistor with SiO<sub>2</sub> gate insulator, grown on highly doped silicon, and of the PZT-based FeFET were compared. It was proven that the FeFETs had promising performances in terms of  $I_{on}/I_{off}$  ratio (i.e.,  $10^{6}$ ) and  $I_{DS}$  retention behavior.

**INDEX TERMS** Ferroelectric transistor, PZT, IGZO.

## I. INTRODUCTION

Ferroelectric field effect transistors (FeFET) are highly attractive as non-volatile memories due to characteristics like non-destructive read-out, high-density integration possibility, high speed of reading and writing and low power consumption [1], [2]. CMOS compatible FeFET employing silicon (Si) transistors and Al doped HfO<sub>2</sub> as ferroelectric material were recently reported [3]–[5]. Ferroelectric gate thin film transistors (FeTFT) were developed using different ferroelectrics such as PZT [6]–[10], poly(vinylidene fluoride-trifluoroethylene) [P(VDF-TrFE)] [11]–[14], (Bi,La)<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub> (BLT) [15] or HfO<sub>2</sub>-based materials (e.g., Si-doped or Zr-doped HfO<sub>2</sub>) [16]–[19]. In terms of architecture, the [P(VDF-TrFE)] based FeTFT devices are generally top-gate, whilst the fully inorganic structures are bottom-gate.

Among the above mentioned ferroelectrics, HfO<sub>2</sub>-based materials recently attracted significant attention. Since the breakthrough of Böscke *et al.* [20], which reported in 2011 the ferroelectricity of Si-doped HfO<sub>2</sub>, incremental focused researches have been performed in order to asses if HfO<sub>2</sub> based-materials can overcome some of the limitations of conventional ferroelectrics (such as PZT), markedly their (*i*) reduced compatibility with metal-oxide-semiconductor (CMOS) technologies or (*ii*) limited

scalability. The ferroelectricity of HfO<sub>2</sub> films manifests when the layer thickness is reduced to few nm (e.g., 10 nm) [16], [21]. However, this could generate an important technological hindrance, since a non-uniformity of only 1 nm will correspond to a thickness variation of 10%, with a negative impact on the overall performance reproducibility. One the other hand, PZT presents ferroelectricity even at film thicknesses of tens or hundreds of nm, and thereby a similar thickness non-uniformity will not induce a deleterious effect of the same magnitude.

A disadvantage shared by all polycrystalline ferroelectrics (HfO<sub>2</sub>, PZT included) is the random orientation of the crystalline grains, which will determine a random behavior of the correlation between the polarization and direction of the electric field along the crystalline grains. Moreover, in PZT the binding of cations to oxygen is relatively weak (thus, the oxygen vacancies formed relatively easy) and this can cause reliability concerns. However, PZT, as gate in FETs, is appealing due to its high remnant polarization and low coercive voltages. Moreover, this material can be obtained via solution methods, offering high scalability, while maintaining the good ferroelectric response [22]. Still, a drawback of PZT is the difficulty of integration in the mature Si technology because of the poor quality of

the PZT/Si interface [23]. Nevertheless, this issue can be overcome by combining the ferroelectric PZT with an oxide semiconductor, such as indium-gallium-zinc oxide (IGZO). First suggested by Nomura *et al.* [24], amorphous IGZO (a-IGZO) is already acknowledged as a suitable material for application in transparent transistors, acting as the semiconductor channel. The notoriety of a-IGZO was gained in the last decade due to its relatively large carrier mobility, high transparency and good uniformity on large areas. Consequently, IGZO has been used so far in FeFETs as channel semiconductor in combination with [P(VDF-TrFE)] [11], [12], BLT [15], and bilayer gates, e.g., [P(VDF-TrFE)]/Al<sub>2</sub>O<sub>3</sub> [25]–[27].

At an energy band gap of  $\sim$ 3 eV and a work function of 4.5 eV, IGZO has an unsuitable band alignment with Si- [28] and Zr-doped HfO<sub>2</sub> [29] for FET-type applications. In the case of PZT and un-doped HfO<sub>2</sub>, the band alignment is presumed to be favorable (type I-straddled), but with low valence band offset ( $\sim$ 0.4 eV) and low conduction band offset ( $\sim$ 0.2 eV) for PZT. Nevertheless, the band offset may vary as both the band gap and the work function of polycrystalline films are greatly influenced by the synthesis method variables. For example, the IGZO band gap was found to vary in the range 2.5 – 3.5 eV [30], [31].

For the design of FeFETs, PZT has been combined with MoS<sub>2</sub> [6], [7], graphene [8], [32], ITO [9] or ZnO [10]. Graphene, ITO and ZnO are transparent in visible range, whilst MoS<sub>2</sub> has a band gap of  $\sim$ 1.2 eV. The use of graphene in PZT- FeFETs (memory window of 4.1 - 4.3 eV,  $\sim 72\%$ of Ihigh/Ilow can be retained after 10 years) devices produces good performances, but it cannot substitute IGZO, as it has a p-type conduction. In ZnO the free carriers are generated as consequence of oxygen vacancies (VO), and therefore, the electron concentration and its reproducibility is difficult to be managed. In the case of IGZO, the free carriers density is governed by indium concentration, while the VOs, which are the predominant defects also in type of material, have the highest formation energy in the vicinity of gallium atoms. Thereby, the modification of gallium concentration in IGZO can be used to control the formation of VOs, and consequently, to tune the free carriers density [33]. Although ITO/PZT based FeFETs were considered promising, they are affected by large leakage currents, which can be associated with the unfavorable band alignment (valence offset of -1.1 eV) [34].

To the best of our knowledge, no reports on the fabrication and performance of FeFETs using  $HfO_2$  – doped or un-doped – or PZT (as ferroelectric gate) and a-IGZO (as channel semiconductor), have been published yet. In this article we advance the use of one of these combinations (i.e., PZT and IGZO) for the development of a new ferroelectric transistors.

### II. DEVICE FABRICATION AND EXPERIMENTAL METHODS

Two types of bottom-gate field effect transistors (FET) were fabricated: (i) with 50 nm thick SiO<sub>2</sub> gate insulator grown on highly doped Si ("SiMat") and (ii) with 230 nm

thick PZT (PbZr<sub>0.2</sub>Ti<sub>0.8</sub>O<sub>3</sub>) deposited by sol-gel method onto temperature resistant glass substrate. The fabrication steps of the PZT layers are described elsewhere [35]. The 40 nm thick IGZO channel semiconductor was deposited by radio-frequency magnetron sputtering (RF-MS) (using a customized AJA Phase II J system) on both SiO2 and PZT, at room-temperature (i.e., without intentional heating; the substrate temperature reaching a temperature of  $\sim$ 50 °C under the deposition conditions, due to plasma bombardment processes only), in the same deposition session. The sputtering of In:Ga:Zn (1:1:2) oxide target was performed in inert atmosphere, using an Ar flow of 20 sccm, and a substrate-to-target separation distance of 80 mm. To ensure good uniformity the substrates were rotated at a speed of 30 rpm. The Ti/Au layers for the gate (only on PZT based transistors) and source-drain electrodes were deposited by RF-MS, subsequently to the patterning of the substrates by photolithography. In both SiO<sub>2</sub> and PZT-based transistor cases, the channel width - length ratio was W/L = 20 µm/20 µm. The as-fabricated transistors and metalferroelectric-metal structures - MFM (the schematics given in Figd. 1 (d – f) were thermal-treated in air at 250 °C, on a hot plate in two consecutive sessions of 2 h, under dark conditions. Subsequently, the devices were analyzed.

The structure of the PZT layers was analyzed by X-ray diffraction (XRD) in symmetric geometry, using a Bruker D8 Advance machine ( $CuK_{\alpha}$  radiation). The morphology of the PZT/IGZO based FET was investigated by scanning electron microscopy (SEM), with a Zeiss Merlin Compact field emission scanning electron microscope. The transfer and output characteristics of the FETs were evaluated with a Keithley 4200 semiconductor parameter analyzer, in dark conditions, using 0.5 s per one step of 0.2 V in sweeping V<sub>GS</sub> and 0.1 V in sweeping V<sub>DS</sub>. The electrical measurements were performed in normal atmospheric conditions at roomtemperature, and in vacuum (at  $2 \times 10^{-6}$  mbar) at various temperatures. Furthermore, the capacitance-voltage (C-V) characteristics of SiO<sub>2</sub>/IGZO/Ti/Au and PZT/IGZO/Ti/Au structures were carried out directly on FETs; the C-V curves were recorded at 100 kHz frequency of the a.c. small signal of 100 mV amplitude using a Hioki LCR meter, by sweeping the voltage from negative to positive values and back. The polarization-voltage (P-V) measurements were performed at 100 Hz by employing a TF2000 ferritester system equipped with a FE-Module (aixACCT).

# **III. RESULTS AND DISCUSSION**

The polycrystalline nature of PZT layers structure can be depicted based on Fig. 1 (c). The identified diffraction maxima are ascribed to crystallized PZT [35]. Crystalline coherence length  $(D_{h00})$  and mean square strain values of 73 nm and 0.02, respectively, were determined by the Williamson-Hall method. In addition, the top-view and crossview SEM analyses revealed that the PZT layer is dense and elicits a clear separation interface with the IGZO thin film (see Fig. 1 (a) and (b)). MFM structures, having areas of

FIGURE 1. (a) Cross-sectional SEM image of PZT/IGZO based FET; (b) Top-view SEM image of the PZT layer's surface; (c) XRD pattern of the sol-gel synthesized PZT thin film; Schematics of the (d) SiO<sub>2</sub> based FET, (e) PZT based FeFET; and (f) metal-ferroelectric-metal (MFM) structures.

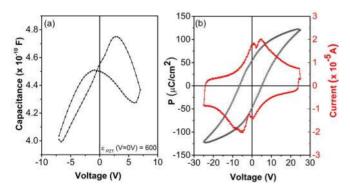

FIGURE 2. (a) Capacitance-voltage (C-V) characteristics of the PZT based MFM; (b) Hysteresis loop recorded for the PZT film.

0.0196 mm<sup>2</sup>, were fabricated on the same glass wafer as the FET structures, to enable performing the C-V and hysteresis loop measurements.

The C-V characteristics (Fig. 2 (a)) are asymmetric in terms of capacitance values, and moreover, show a small shift towards negative voltages. The asymmetry of the C-V curves can be caused by the different PZT interface formed with the bottom (Ti/Au/PZT) and top (PZT/Ti/Au) electrodes, respectively. Moreover, the bottom electrode was subjected to an annealing temperature of 650 °C after the deposition of the

TABLE 1. Performance parameters of FeFETs. This work: electrical properties of SiO<sub>2</sub> and PZT based FETs. In the case of PZT-based FET, the threshold voltage (consequently,  $\mu_{fe}$ ) has two values, corresponding to forward and reverse sweeps.  $I_{on}(SiO_2)$  base FET) =  $2.6 \times 10^{-6}$  A,  $I_{off}$  (PZT based FET) =  $2.1 \times 10^{-6}$  A; Other works: [P(VDF-TrFE] [25], [36], [37], BLT [15], PZT [9], [32] and HfZrO [18], [19].

| Gate                                                | Channel | Ion/Ioff                                     | V <sub>th</sub> (V) | SS<br>(V/dec) | $\mu_{fe}$ $(cm^2/Vsec)$ $(V_{DS} = 0.1 V)$ |

|-----------------------------------------------------|---------|----------------------------------------------|---------------------|---------------|---------------------------------------------|

| This work                                           |         |                                              |                     |               |                                             |

| SiO <sub>2</sub>                                    | IGZO    | $7.6 \times 10^2$                            | -2.7                | 1.35          | 29                                          |

| PZT                                                 | IGZO    | 1.5 x 10 <sup>6</sup>                        | 1.2/2.6             | 1.25          | 1.5/3                                       |

| Other works                                         |         |                                              |                     |               |                                             |

| [P(VDF<br>-TrFE]                                    | IGZO    | 10 <sup>5</sup> [36]<br>10 <sup>7</sup> [37] | 0.5<br>[37]         | 0.4 [37]      | 1<br>[37]                                   |

| [P(VDF<br>-TrFE]<br>/Al <sub>2</sub> O <sub>3</sub> | IGZO    | 108 [25]                                     | 3.1<br>[25]         | 0.34<br>[25]  | 49.2 [25]                                   |

| BLT                                                 | IGZO    | 10 <sup>4</sup> [15]                         | -                   | 0.1 [15]      | -                                           |

| PZT                                                 | ITO     | 10 <sup>5</sup> [9]                          | 1.5 [9]             | -             | 0.092 [9]                                   |

| PZT                                                 | SLG     | 6 [32]                                       | -                   | -             | 1500 [32]                                   |

| HfZrO/<br>Al <sub>2</sub> O <sub>3</sub>            | IZO     | -                                            | -0.4<br>[19]        | 0.82<br>[19]  | 5.5 [19]                                    |

| HfN/<br>HfZrO/<br>SiO <sub>2</sub>                  | p-Si    | 104[18]                                      | -6/5<br>[18]        | -             | -                                           |

PZT film, and this caused its degradation. The significant impact of the thermal annealing on the bottom electrodes is revealed by the cross-section SEM image (Fig. 1 (a)), which evidenced the presence of voids with diameters up to 100 nm in the Au layer.

The hysteresis loops (Fig. 2 (b)) were recorded using a triangular voltage wave with a frequency of 100 Hz. The current hysteresis shows the presence of the characteristic peaks associated to polarization reversal. The value for remnant polarization (Pr) is around 53  $\mu$ C/cm², while the coercive voltages of -6.5 V and +5.2 V lead to a coercive field of 240 kV/cm. It should be mentioned that the hysteresis loops have a small shift towards negative voltages.

The typical pinch-off of n-type semiconductor FETs was shown by the output characteristics of  $SiO_2$  or PZT based FETs (Fig. 3 (a) and (d)). Both devices showed a good saturation tendency, while the linear regime was recorded for  $V_{DS}$  biases lower than 1 V for both devices.

Table 1 summarizes the essential parameters for FET devices ( $I_{on}-I_{DS}$  at maximum  $V_{GS}$  bias; the  $I_{on}/I_{off}$  ratio, where  $I_{off}$  and  $I_{on}$  are the  $I_{DS}$  at minimum and maximum  $V_{GS}$  bias, respectively; the threshold voltage –  $V_{th}$ ; the subthreshold slope – SS; field effect mobility –  $\mu_{fe}$ ). The leakage current,  $I_{GS}$ , in the case of SiO<sub>2</sub> based FET was  $10^{-10}A$ , thus, with two orders of magnitude higher with respect to the one of FeFET, degrading the  $I_{off}$  level and consequently the  $I_{on}/I_{off}$  ratio.

The field effect mobility values were calculated using the equation 1, where oxide capacitance values are

270 VOLUME 7, 2019

FIGURE 3. SiO<sub>2</sub>/IGZO/Ti/Au structure: (a) Output characteristics; (b) Linear transfer characteristics with inset of sub-threshold region, and (c) C-V curve; PZT/IGZO/Ti/Au structure: (d) Output characteristics; (e) Linear transfer characteristics with inset of sub-threshold region; and (f) C-V curve.

$C_{ox}(SiO_2) = 6.9 \times 10^{-8} F/cm$  and  $C_{ox}(PZT) = 2 \times 10^{-6} F/cm$ . The obtained  $\mu_{fe}$  values are underestimated with  $\sim 24\%$ , due to the contact resistance effect,  $R_c = 29 k\Omega$  (extracted using Transmission Line Method [38]).

$$\mu = \frac{L}{W} \frac{I_{DS}}{C_{ox}(V_{GS} - V_{th})V_{DS}} \tag{1}$$

The transfer characteristics ( $I_{DS}$  vs.  $V_{GS}$ ) with a double sweep of the  $V_{GS}$ , under  $V_{DS}=0.1V$ , are presented in Fig. 3 (b) and (e). For SiO<sub>2</sub> based FET, the hysteresis width – defined as the  $\Delta$   $V_{GS}$  at ( $I_{on}-I_{off}$ )/2 – has a negligible value of 0.2 V. The insignificance of the hysteresis width for this device is confirmed by the C-V measurements (Fig. 3 (c)). However, in the case of PZT based FET,  $\Delta$   $V_{GS}$  is 3.2 V and the hysteresis width in capacitance – defined as  $\Delta$  V at ( $C_{max}-C_{min}$ )/2 – is 6.2 V. (Fig. 3 (f)). Both I-V and C-V hysteresis loops show a clock-wise behavior, which is intriguing since, in a proper FeFET, the hysteresis loops have to be counter clock-wise when the ferroelectric is grown on a n-type semiconductor.

Equation (2) [39], [40] was used to estimate (considering the product of the deep bulk states density and the IGZO thickness as much lower-than the interface states density) the maximum the interface states densities,  $D_{it}$ , of  $1 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> for SiO<sub>2</sub>/IGZO and  $1.3 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> for PZT/IGZO structures. This interface quality difference is reflected also in the sub-threshold performance of the TFTs (inset – Fig. 3 (b) and (e)), i.e., the higher sub-threshold

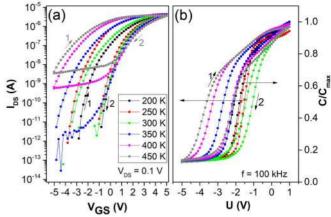

FIGURE 4. PZT FeFET structure: (a) Linear transfer characteristics; (b) (C-V) characteristics measured at different temperatures.

current for SiO2-TFT.

$$D_{it} = \frac{C_{ox}}{q^2} \left( \frac{qSS}{kT \ ln10} - 1 - \frac{C_D}{C_{ox}} \right)$$

(2)

where  $C_D \sim 10^{-7}$  F/cm is depletion capacitance.

Considering the IGZO thickness of 40 nm and its electron concentration of  $6\times10^{17}$  cm<sup>-3</sup> (extracted from Hall measurements, data not shown here), it results that the free carriers from the channel can compensate a polarization of maximum 0.4  $\mu$ C/cm<sup>2</sup>. This is a much smaller value than the one extracted from the hysteresis loop presented in Fig. 2 (b). On the other hand, the  $D_{it}$  extracted for the PZT/IGZO interface corresponds to about 6  $\mu$ C/cm<sup>2</sup>.

The result is that the hysteresis loops at room-temperature are dominated by the interface traps. PZT-based FeFETs with clock-wise loops are not unprecedented [6], [7]. The observed hysteresis loops were described by the dynamic charge trapping and de-trapping which take places when V<sub>GS</sub> is swept from negative to positive, and back. Nevertheless, even in the case of a clock-wise hysteresis, the field effect can be modulated by changing the polarization value in the ferroelectric gate, as shown in Sun *et al.* [6].

We have also performed temperature-dependent hysteresis measurements on the PZT/IGZO FeFET (Fig. 4). One can see that, up to 420 K, the counter clock-wise hysteresis could not be recovered. A possible explanation for this is that the capacitance measurement was performed between the gate and source/drain electrodes, thus the results are affected by some parasitic capacitances (e.g., overlap capacitance between the gate electrode and the source/drain electrodes with only PZT in between).

It is shown that the hysteresis width (memory window) increases with temperature. This effect can be attributed to the presence of ferroelectric polarization in the gate layer. As the temperature increases the trapping on the interface states is no longer active, and thus the effect of ferroelectric polarization is more visible in the device characteristics. Moreover, a peculiar behavior was revealed by the C-V vs.

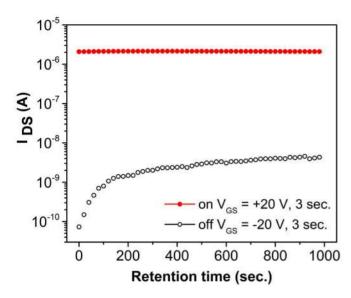

FIGURE 5. Retention behavior of the PZT-IGZO based FeFET; Variation of the "On" and "Off" states with a time lapse of 1000 seconds.

temperature measurements: from 200 K to 250 K, the C-V curve has a positive shift, while, from 250 K to 420 K, the C-V curves show a shift towards negative voltage. Up to 250 K, the positive shift could be caused by the trapping of electrons by the existing defects at the given top electrode (with activation energy larger than 21.4 meV), which partially screens the applied gate bias and makes the effective gate voltage smaller. As the temperature is further increased, the curves are shifted toward negative V<sub>GS</sub> values due to the carriers thermal activation (electron detrapping) from trapping states.

The memory function (as non-volatile memory) was tested by applying a voltage pulse of +20 V or -20 V for 3 seconds on the gate electrode, orienting in this way the polarization upward (towards the IGZO channel) or downward (towards the gate electrode), and then measuring the drain current at regular time intervals with no potential applied on the gate (floating gate).

Two I<sub>DS</sub> values were obtained, for On and Off states (Fig. 5), corresponding to the two orientations of the polarization. Thus, the memory function is present although the ferroelectric hysteresis is masked by the parasitic effect of the interface states. The memory property can be explained by the fact that, after removing the external poling field applied on the gate, the polarization value and orientation stabilizes to the value allowed by the available charges for compensating the depolarization field. The values/orientations appear to be different leading to different values of the drain current. We can speculate that the upward value (for positive gate voltage) is very stable (induces accumulation in the channel), leading to an almost constant value of the drain current up to 1000 seconds. The opposite orientation of polarization seems to stabilize after about 100 seconds, as suggested by the fact that the drain current value increases from few tens of picoamps to few nanoamps. This is owned to the fact that during the poling period and immediately after removing the poling field, the polarization value is close to the one extracted from the hysteresis loop (about 50  $\mu$ C/cm²). After removing the poling field, the polarization value decreases, probably around 0.4  $\mu$ C/cm² or less, leading to an increase drain current value. One can observe that the increase in the value of the drain current is about the same order of magnitude with the assumed decrease in polarization value after removing the poling field.

There is an apparent inconsistency between the clockwise hysteresis (Fig. 3e) and the presence of  $I_{DS}$  retention (Fig. 5). The question of how both behaviors can characterize the same FeFET can arise. We believe that this may be a result of the measurement procedure. The current-voltage characteristic in Fig. 3e is a dynamic one ( $V_{GS}$  sweeping); in this case, both voltages are applied on the structure,  $V_{GS}$  and  $V_{DS}$ .

The retention measurement results, presented in Fig. 5, were obtained after the gate probe was mechanically lifted (open gate); in this case only  $V_{DS}$  is applied on the structure. The fact that there is a certain superposition between the gate electrode on one hand and the source/drain electrodes on the other hand, may lead to different behavior of charges in the structure when both  $V_{GS}$  and  $V_{DS}$  are applied, compared to the situation when only  $V_{DS}$  is applied and the gate is not grounded.

When a positive voltage is applied on the gate, then polarization will be oriented towards the IGZO channel, attracting electrons to the interface for compensating the positive polarization charges. Some of these electrons are trapped on the interface states. When the applied  $V_{GS}$  is higher than +9~V (Fig. 3e), the device is not completely trapped. Therefore, applying a  $V_{GS}$  bias of +20~V before measuring the  $I_{DS}$  retention time is enough for obtaining the maximum accumulation current,  $\sim 2$  microamps, the same as the one measured in Fig. 3e. Moreover, because the gate contact is open, there are no parasitic conduction channels for the charges in the structure and the drain current remains at the value set after poling the ferroelectric with positive  $V_{GS}$ .

The functionality of here presented FeFET device is inferior to those based on [P(VDF-TrFE)] and IGZO, which show field effect mobility higher than 40 cm<sup>2</sup>/Vs, I<sub>on</sub>/I<sub>off</sub> of 10<sup>8</sup> and retention time of days [25]. However, contrary to PZT, P(VDF-TrFE) suffers of permanent degradation of its ferroelectric properties when is exposed to temperatures higher that 65 °C, being unsuitable for high temperature applications.

# IV. CONCLUSION

Thin PZT layers were obtained by sol-gel, a low-cost fabrication method, and successfully integrated into FeFETs. The device provided good performances in terms of both  $I_{\rm on}/I_{\rm off}$  ratio and threshold voltage. However, the interface states between PZT and IGZO acted as traps and affected the ferroelectric memory window. In spite of this, good retention

272 VOLUME 7, 2019

behavior was shown due to the polarization switching in the gate ferroelectric.

Therefore, PZT/IGZO based FeFETs could become interesting alternatives, even for transparent electronics, if the contribution of interface states acting as traps will be reduced (ideally, completely removed). This could be the solution to recover the ferroelectric memory window and to manufacture an accurate FeFET that may compete with the existing nonvolatile memories based on trap charges or floating gate. One possible route to optimize the interface quality is to use a textured or even epitaxial ferroelectric layer instead of a polycrystalline one. However, such an approach, based on ferroelectric layers of higher structural quality would imply the use expensive deposition technologies (i.e., PVD or CVD) and would introduce certain restrictions in what concerns the substrate choices.

### **REFERENCES**

- [1] B.-E. Park, H. Ishiwara, M. Okuyama, S. Sakai, and S.-M. Yoon, "Ferroelectric-gate field effect transistor memories: Device physics and applications," in *Topics in Applied Physics*. Dordrecht, The Netherlands: Springer, 2016, p. 131. doi: 10.1007/978-94-024-0841-6.

- [2] S. Das and J. Appenzeller, "FeTRAM. An organic ferroelectric material based novel random access memory cell," *Nano Lett.*, vol. 11, no. 9, pp. 4003–4007, Aug. 2011. doi: 10.1021/nl2023993.

- [3] H. Mulaosmanovic et al., "Switching kinetics in nanoscale hafnium oxide based ferroelectric field-effect transistors," ACS Appl. Mater. Interfaces, vol. 9, no. 4, pp. 3792–3798, Jan. 2017. doi: 10.1021/acsami.6b13866.

- [4] J. Müller et al., "Ferroelectricity in HfO<sub>2</sub> enables nonvolatile data storage in 28 nm HKMG," in Proc. Symp. VLSI Technol. (VLSIT), Jun. 2012, pp. 25–26. doi: 10.1109/VLSIT.2012.6242443.

- [5] J. Muller et al., "Nanosecond polarization switching and long retention in a novel MFIS-FET based on ferroelectric HfO<sub>2</sub>," IEEE Electron Device Lett., vol. 33, no. 2, pp. 185–187, Jan. 2012. doi: 10.1109/LED.2011.2177435.

- [6] Y. Sun et al., "Temperature-dependent transport and hysteretic behaviors induced by interfacial states in MoS<sub>2</sub> field-effect transistors with lead-zirconate-titanate ferroelectric gating," Nanotechnology, vol. 28, no. 4, Dec. 2017, Art. no. 045204. doi: 10.1088/1361-6528/28/4/045204.

- [7] A. Lipatov, P. Sharma, A. Gruverman, and A. Sinitskii, "Optoelectrical molybdenum disulfide (MoS<sub>2</sub>)-ferroelectric memories," ACS Nano, vol. 9, no. 8, pp. 8089–8098, Jul. 2015. doi: 10.1021/acsnano.5b02078.

- [8] A. Lipatov et al., "Polarization-dependent electronic transport in graphene/Pb(Zr,Ti)O<sub>3</sub> ferroelectric field-effect transistors," Adv. Electron. Mater., vol. 3, no. 7, May 2017, Art. no. 1700020. doi: 10.1002/aelm.201700020.

- [9] D. H. Minh, N. V. Loi, N. H. Duc, and B. N. Q. Trinh, "Low-temperature PZT thin-film ferroelectric memories fabricated on SiO<sub>2</sub>/Si and glass substrates," *J. Sci. Adv. Mater Devices*, vol. 1, pp. 75–79, Mar. 2016. doi: 10.1016/j.jsamd.2016.03.004.

- [10] X. Zhang et al., "ZnO field-effect transistors with lead-zirconate-titanate ferroelectric gate," Mater. Res. Innov., vol. 19, pp. 181–184, May 2015. doi: 10.1179/1432891715Z.0000000001412.

- [11] G. H. Gelinck, B. Cobb, A. J. J. M. van Breemen, and K. Myny, "Large scale integration of flexible non-volatile, re-addressable memories using P(VDF-TrFE) and amorphous oxide transistors," *Semicond. Sci. Technol.*, vol. 30, Jun. 2015, Art. no. 074003. doi: 10.1088/0268-1242/30/7/074003.

- [12] A. van Breemen et al., "Ferroelectric transistor memory arrays on flexible foils," Org. Electron., vol. 14, no. 8, pp. 1966–1971, Aug. 2013. doi: 10.1016/j.orgel.2013.04.025.

- [13] H. Tian et al., "High performance top-gated ferroelectric field effect transistors based on two-dimensional ZnO nanosheets," Appl. Phys. Lett., vol. 110, no. 4, Jan. 2017, Art. no. 043505. doi: 10.1063/1.4975061.

- [14] Y. Wang et al., "High-performance non-volatile field-effect transistor memories using an amorphous oxide semiconductor and ferroelectric polymer," J. Mater. Chem. C, vol. 4, no. 34, pp. 7917–7923, Jul. 2016. doi: 10.1039/C6TC01768A.

- [15] K.-I. Haga and E. Tokumitsu, "Fabrication and characterization of ferroelectricgate thin-film transistors with an amorphous oxide semiconductor, amorphous In-Ga-Zn-O," *Jpn. J. Appl. Phys.*, vol. 53, no. 11, Oct. 2014, Art. no. 111103. doi: 10.7567/JJAP.53.111103.

- [16] T. Ali et al., "Silicon doped Hafnium oxide (HSO) and Hafnium zirconium oxide (HZO) based FeFET: A material relation to device physics," Appl. Phys. Lett., vol. 112, no. 22, May 2018, Art. no. 222903. doi: 10.1063/1.5029324.

- [17] T. Ali et al., "High endurance ferroelectric hafnium oxide-based FeFET memory without retention penalty," IEEE Trans. Electron Devices, vol. 65, no. 9, pp. 3769–3774, Sep. 2018. doi: 10.1109/TED.2018.2856818.

- [18] B. Zeng et al., "Compatibility of HfN metal gate electrodes with Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric thin films for ferroelectric field-effect transistors," *IEEE Trans. Electron Devices*, vol. 39, no. 10, pp. 1508–1511, Oct. 2018. doi: 10.1109/LED.2018.2868275.

- [19] Y. Li et al., "A ferroelectric thin film transistor based on annealing-free HfZrO film," J. Electron. Dev. Soc., vol. 5, no. 5, pp. 378–383, Sep. 2017. doi: 10.1109/JEDS.2017.2732166.

- [20] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide thin films," *Appl. Phys. Lett.*, vol. 99, Aug. 2011, Art. no. 102903. doi: 10.1063/1.3634052.

- [21] M. H. Park et al., "Evolution of phases and ferroelectric properties of thin Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> films according to the thickness and annealing temperature," Appl. Phys. Lett., vol. 102, Jun. 2013, Art. no. 242905. doi: 10.1063/1.4811483.

- [22] L. Pintilie et al., "Temperature induced change in the hysteretic behavior of the capacitance-voltage characteristics of Pt–ZnO– Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub>–Pt heterostructures," Appl. Phys. Lett., vol. 96, Jan. 2010, Art. no. 012903. doi: 10.1063/1.3284659.

- [23] T. Yamaguchi, M. Koyama, A. Takashima, and S.-I. Takagi, "Improvement of memory characteristics of metal-ferroelectrics/ insulating buffer layer/semiconductor structures by combination of pulsed laser deposited SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> films and ultra-thin SiN buffer layers," *Jpn. J. Phys.*, vol. 39, no. 4B, pp. 2058–2062, Apr. 2000.

- [24] K. Nomura et al., "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, pp. 488–492, Nov. 2004. doi: 10.1038/nature03090.

- [25] S.-M. Yoon et al., "Oxide semiconductor-based organic/inorganic hybrid dual-gate nonvolatile memory thin-film transistor," IEEE Trans. Electron Devices, vol. 58, no. 7, pp. 2135–2142, Jul. 2011. doi: 10.1109/TED.2011.2139212.

- [26] S.-M. Yoon et al., "Impact of interface controlling layer of Al<sub>2</sub>O<sub>3</sub> for improving the retention behaviors of In–Ga–Zn oxide-based ferroelectric memory transistor," Appl. Phys. Lett., vol. 96, no. 23, May 2010, Art. no. 232902. doi: 10.1063/1.3452339.

- [27] S.-M. Yoon et al., "Polymeric ferroelectric and oxide semiconductor-based fully transparent memristor cell," Appl. Phys. A, Solids Surf., vol. 102, no. 4, pp. 983–990, Jan. 2011. doi: 10.1007/s00339-011-6280-9.

- [28] D. C. Hays, B. P. Gila, S. J. Pearton, and F. Ren, "Energy band offsets of dielectrics on InGaZnO<sub>4</sub>," *Appl. Phys. Rev.*, vol. 4, no. 2, Mar. 2017, Art. no. 021301. doi: 10.1063/1.4980153.

- [29] F. Ambriz-Vargas et al., "Tunneling electroresistance effect in a Pt/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/Pt structure," Appl. Phys. Lett., vol. 110, no. 9, Feb. 2017, Art. no. 093106. doi: 10.1063/1.4977028.

- [30] A. C. Galca, G. Socol, L. M. Trinca, and V. Craciun, "Stoichiometry dependence of the optical properties of amorphous-like  $In_{x-w}Ga_wZn_{1-x}O_{1+0.5x-\delta}$  thin films," *Appl. Surface Sci.*, vol. 281, pp. 96–99, Sep. 2013. doi: 10.1016/j.apsusc.2013.01.176.

- [31] W.-G. Kim et al., "High-pressure gas activation for amorphous indium-gallium-zinc-oxide thin-film transistors at 100°C," Sci. Rep., vol. 6, Mar. 2016, Art. no. 23039. doi: 10.1038/srep23039.

- [32] S. Lee and Y. Lee, "Graphene/lead-zirconate-titanate ferroelectric memory devices with tenacious retention characteristics," *Carbon*, vol. 126, pp. 176–182, Jan. 2018. doi: 10.1016/j.carbon.2017.10.005.

- [33] W.-J. Lee, E.-A. Choi, J. Bang, B. Ryu, and K. J. Chang, "Structural and electronic properties of crystalline InGaO<sub>3</sub>(ZnO)<sub>m</sub>," Appl. Phys. Lett., vol. 93, no. 11, Jul. 2018, Art. no. 111901. doi: 10.1063/1.2980583.

- [34] F. Chen, R. Schafranek, S. Li, W. B. Wu, and A. Klein, "Energy band alignment between Pb(Zr,Ti)O<sub>3</sub> and high and low work function conducting oxides—From hole to electron injection," *J. Phys.* D Appl. Phys., vol. 43, no. 29, Jul. 2010, Art. no. 295301. doi: 10.1088/0022-3727/43/29/295301.

- [35] V. Stancu et al., "The study of the electric and magnetic properties of PbZr<sub>0.2</sub>Ti<sub>0.8</sub>O<sub>3</sub>-BiFeO<sub>3</sub> multilayers" *Thin Solid Films*, vol. 519, no. 19, pp. 6269–6277, Apr. 2011. doi: 10.1016/j.tsf.2011.03.136.

- [36] J.-H. Yang et al., "Investigations on the effects of electrode materials on the device characteristics of ferroelectric memory thin film transistors fabricated on flexible substrates," *Jpn. J. Appl. Phys.*, vol. 57, no. 3S1, Feb. 2018. doi: 10.7567/JJAP.57.03DB02.

- [37] G.-G. Lee et al., "The flexible non-volatile memory devices using oxide semiconductors and ferroelectric polymer poly(vinylidene fluoride-trifluoroethylene)," Appl. Phys. Lett., vol. 99, no. 1, Art. no. 012901, Jul. 2011. doi: 10.1063/1.3608145.

- [38] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd ed. New York, NY, USA: Wiley, 2005. doi: 10.1002/0471749095.

- [39] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. New York, NY, USA: Wiley, 2006, ch. 6, p. 315. doi: 10.1002/0470068329.

- [40] R. M. Swanson and J. D. Meindl, "Ion-implanted complementary MOS transistors in low-voltage circuits," *IEEE J. Solid-State Circuit*, vol. SSC-7, no. 2, pp. 146–153, Apr. 1972. doi: 10.1109/JSSC.1972.1050260.

CRISTINA BESLEAGA was born in Romania, in 1986. She received the Diploma degree in Bologna system from the Faculty of Physics, University of Bucharest, Romania, in 2008, with the diploma thesis entitled "Ba0.75Sr0.25TiO3 thin films deposited by RF magnetron sputtering," the master's degree from the Faculty of Physics, University of Bucharest, in 2010, with the thesis entitled "Metal to semiconductor transition in highly disordered bi-dimensional systems," and the Ph.D. degree from the Solid State Physics

Department, Faculty of Physics, University of Bucharest, in 2013 with the thesis entitled "Wide band gap semiconductors with application in transparent electronics." From 2008 to 2009, she was a Research Assistant with the National Institute of Research and Development for Optoelectronics, Mägurele, Romania: from 2009 to 2012, she was a Research Assistant with the Research and Development Center for Materials, Electronics and Optoelectronic Devices, Faculty of Physics, University of Bucharest; since 2012, she has been a Team Member with the Laboratory of Multifunctional Materials and Structures, National Institute for Materials Physics, Măgurele. She has published to date 36 articles (with Web of Science impact factor) with an H-index of 11. She hold strong expertise in synthesis of thin films by RF-magnetron sputtering; characterization of thin film structures: structural (X-ray diffraction, X-ray reflectometry), morphological (atomic force microscopy, scanning electron microscopy), optical (UV-Vis-IR spectroscopy), and electrical (resistivity /conductivity, Hall effect, dielectric spectroscopy); fabrication of electronic and optoelectronic devices in clean room conditions and their characterization: photovoltaic cells, metal-insulator-metal structures, metal-insulator-semiconductor structures, and thin film field effect transistors.

**ROXANA RADU** was born in Romania, in 1984. She received the Ph.D. degree in physics from the University of Bucharest, Romania, in 2015 with the thesis entitled "Bulk radiation damage in silicon: From point defects to clusters." Her research interests are concentrated on the development of the silicon detectors with applications in fundamental research, such as elementary particles and nuclear physics. She has a vast experience with radiation-induced defects and modeling of defect generation in n-type silicon detectors.

**LILIANA-MARINELA BALESCU** was born in Romania, in 1988. She received the bachelor's and master's degrees in chemical engineering from the University Politehnica of Bucharest in 2011 and 2013, respectively, and the Ph.D. degree in condensed matter physics from the University of Bucharest, Romania, in 2017. She is a Senior Researcher with the National Institute of Materials Physics, Romania, where she published 15 scientific papers, for 4 articles she is first author. Her expertise lies in fabrication and characterization of

oxide-based structures, with various electrical properties, from ferroelectrics, insulators to semiconductors and metal-like ones.

VIORICA STANCU was born in Romania, in 1975. She received the M.Sc. degree in analytical chemistry from the Faculty of Chemistry, University of Bucharest in 2000 and the Ph.D. degree in solid state physics from the Faculty of Physics, University of Bucharest in 2009. In 2001, she joined the National Institute of Materials Physics as a Researcher. Her research interests employ preparation and characterization of inorganic semiconductors, ferroelectric materials, and perovskite solar cells

ANDREEA COSTAS was born in Romania, in 1988. She received the bachelor's degree in physics, the master's degree in polymer physics, and the Ph.D. degree in condensed matter physics from the University of Bucharest, Romania, in 2010, 2012, and 2016, respectively. She is currently a Young Researcher with the Laboratory of Multifunctional Materials and Structures, National Institute of Materials Physics, Mägurele, Romania, and was involved as a Team Member in over ten national research projects. Her current research

interests include metallic and semiconductor nanostructures, lithographic techniques, and opto-electronic devices.

VIOREL DUMITRU was born in Romania, in 1972. He received the Diploma degree in physics and the M.S. degree in semiconductor physics from Bucharest University in 1996 and 1997, respectively, and the Ph.D. degree from Stuttgart University in 2004 with the thesis concerning GaN laser diodes physics and technology. From 2005 to 2017, he was researching in sensors Research and Development field as a Senior Research Scientist with Honeywell Romania SRL. She is currently a Senior Researcher with the National Institute of

Materials Physics, Bucharest, Romania. He has co-invented over 35 international patents and has co-authored over 20 scientific papers on various types of sensors, optoelectronic devices, and thin films technology. His current research interests include piezoelectric materials, electronic devices, and sensors based on thin films and neuromorphic devices.

274 VOLUME 7, 2019

**GEORGE STAN** was born in Romania, in 1981. He received the Ph.D. degree in materials engineering from the University Politehnica Bucharest, Bucharest, Romania, in 2011. He is currently a Senior Researcher with the Department of Multifunctional Materials and Structures, National Institute of Materials Physics, Mägurele, Romania. He possesses a rich experience on the fabrication of thin films by physical vapor deposition methods, gained during the participation to/coordination of interdisciplinary research projects and univer-

sity/work stages at prestigious European institutions. He has published to date 70 articles in journals with Web of Science impact factor with an H-index of 18, three patents, and three book chapters. The vast majority of his works have a profound experimental character, encompassing an applicative range which spans from medicine to microelectronics.

LUCIAN PINTILIE was born in Romania, in 1959. He received the M.Sc. degree from the Faculty of Physics, Applied Physics, Semiconductor Materials, University of Bucharest in 1984 and the Ph.D. degree (ceramic materials for pyroelectric detection of IR) from the Institute of Atomic Physics, Bucharest, Romania, in 1995. From 1984 to 1987, he was a Physicist with Giurgiu Chemical Plant. Since 1987, he has been a Researcher with the National Institute of Materials Physics (NIMP), Magurele, Romania. From 1997 to 2004,

he was the Head of the Laboratory (Semiconductor Physics and Complex Heterostructures). From 2001 to 2003, he was a Visiting Scientist with the Institute for Crystal Growth, Berlin, Germany. From 2002 to 2003, he was an NATO Fellow with the University of Braga, Portugal. From 2003 to 2007, he was a Visiting Researcher with the Max Planck Institute, Halle Germany. From 2008 to 2013, he was the General Director of NIMP. He is currently the Scientific Director with NIMP. He has extensive experience in ferroelectric ceramics and thin films, electrical characterization; artificial multiferroics; photoelectric and photovoltaic properties in thin films and complex heterostructures; structures for field effect devices; and materials for UV and IR detection. He was the Director and the Co-Director (or responsible) of 15 international and national projects, about seven million euro. He has over 200 entries on Web of Science, over 2300 citations (self citations excluded) with an *H*-index of 31 (on Web of Science) and with an *H*-index of 38 (on Google Scholar).