## Ferroelectric gate tunnel field-effect transistors with low-power steep turn-on

Cite as: AIP Advances 4, 107117 (2014); https://doi.org/10.1063/1.4898150 Submitted: 13 March 2014 • Accepted: 30 September 2014 • Published Online: 10 October 2014

M. H. Lee, Y.-T. Wei, J.-C. Lin, et al.

## ARTICLES YOU MAY BE INTERESTED IN

A critical review of recent progress on negative capacitance field-effect transistors Applied Physics Letters **114**, 090401 (2019); https://doi.org/10.1063/1.5092684

On device design for steep-slope negative-capacitance field-effect-transistor operating at sub-0.2V supply voltage with ferroelectric  $HfO_2$  thin film

AIP Advances 6, 025113 (2016); https://doi.org/10.1063/1.4942427

Ferroelectricity in hafnium oxide thin films Applied Physics Letters **99**, 102903 (2011); https://doi.org/10.1063/1.3634052

**AIP Advances**

Mathematical Physics Collection

READ NOW

AIP Advances 4, 107117 (2014); https://doi.org/10.1063/1.4898150 © 2014 Author(s). 4, 107117

## Ferroelectric gate tunnel field-effect transistors with low-power steep turn-on

M. H. Lee,<sup>1,a</sup> Y.-T. Wei,<sup>1</sup> J.-C. Lin,<sup>1</sup> C.-W. Chen,<sup>2</sup> W.-H. Tu,<sup>3</sup> and M. Tang<sup>4</sup> <sup>1</sup>Institute of Electro-Optical Science and Technology, National Taiwan Normal University, Taipei, Taiwan <sup>2</sup>Institute of Microelectronics, National Cheng Kung University, Tainan, Taiwan <sup>3</sup>Department of Electrical Engineering and Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

<sup>4</sup>Device Design Division, PTEK Technology Co., Ltd, Hsinchu, Taiwan

(Received 13 March 2014; accepted 30 September 2014; published online 10 October 2014)

Using a ferroelectric PbZrTiO<sub>3</sub> gate stack, the range of the steep subthreshold swing in tunnel field-effect transistors was extended by 3.5 orders of magnitude demonstrating an improvement in the swing (by approximately double the slope). The drain conductance (g<sub>d</sub>) shows only 16% enhancement with large V<sub>DS</sub> (~-1.5V) indicates internal voltage amplification with ferroelectric negative capacitance effect beneficial to small lateral drain-source bias voltages (-0.1 V). The concept of coupling the ferroelectric polarization is proposed. The power consumption is also discussed in low-power applications of steep subthreshold slope devices. © 2014 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4898150]

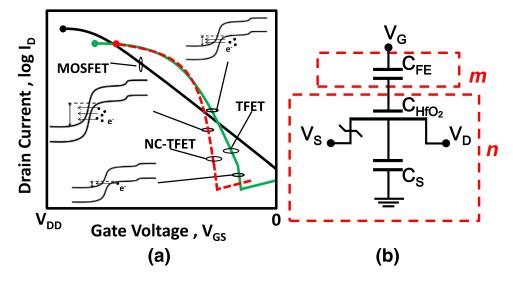

Tunnel field-effect transistors (TFETs) have attracted a great deal of attention for achieving a steep subthreshold swing with band-to-band tunneling (BTBT) operation in future sub-10-nm technology nodes. Because of its small bandgap energy relative to Si, Ge could enhance the tunneling probability of tunnel-based field-effect transistors with high current requirements.<sup>1–3</sup> Recently, epitax-ially grown Ge (epi-Ge) p-TFETs on bulk (110) Si substrates<sup>4</sup> and planar p-TFETs on SOI (Si on insulator)<sup>5</sup> substrates have been reported. The hetero-tunnel field-effect transistor was proposed and modeled,<sup>6</sup> demonstrating steeper switching and higher currents than conventional TFETs.<sup>7</sup> However, one issue associated with the development of TFETs is the small range of the steep swing, caused by the saturation of the surface potential which bends with increasing gate voltage [Fig. 1(a)].

The steep swing range of a TFET is typically 1–3 orders of magnitude, which is less than that of a metal-oxide-semiconductor field-effect transistor (MOSFET) (4–6 orders of magnitude).<sup>8</sup> The subthreshold swing (SS) equation for a TFET is:

$$SS = \frac{\partial V_g}{\partial (\log_{10} I_d)} = \ln (10) \left[ \frac{\partial V_d}{V_d \partial V_g} + \frac{E+b}{E^2} \frac{\partial E}{\partial V_g} \right]^{-1},\tag{1}$$

where  $V_g$  and  $V_d$  are the gate and drain voltages, respectively, *E* is the electric field, and *b* is a constant. Equation (1) shows the dependence of *SS* on voltage and electric field. A higher applied voltage is beneficial for swing. However, the higher driving voltage required by the circuit is not feasible in device applications. A high electric field at the tunneling junction is expected to achieve a steep swing. The dopant segregation of a steep junction profile was reported to have a steep swing that had a range over ~4 orders of magnitude.<sup>5</sup>

In this work, device integration by ferroelectric (FE) polarization coupling is applied to TFETs. This was established experimentally in validating negative capacitance (NC). Incorporating NC into a gate stack is beneficial for energy band bending as it amplifies the internal voltage. It also assists in enhancing the BTBT probability, as shown in Fig. 1(a).

$\odot$

<sup>&</sup>lt;sup>a</sup>Corresponding author: E-mail: mhlee@ntnu.edu.tw Tel.: 886-2-77346747, Fax: 886-2-86631954.

FIG. 1. (a) Schematic of the transfer characteristics of MOSFETs, TFETs, and NC-TFETs. The increased current in the TFET was slowed because of the bending saturation of the surface potential with the gate voltage sweep. Using an integrated ferroelectric material as a negative capacitance feature would extend the steep subthreshold swing range in a TFET. (b) The equivalent circuit of a NC-TFET, including the  $C_{FE}$ ,  $C_{HfO2}$ , and  $C_s$  for the TFET. *m* and *n* can be found using Equation (2).

Standard 6-inch MOS (metal-oxide-semiconductor) base line and gate-last processes were employed in this study. Nominally pure Ge layers were directly grown on 150-mm p-type Si substrates at 525 °C by UHVCVD (ultra-high-vacuum chemical-vapor deposition) using GeH<sub>4</sub> as the precursor and H<sub>2</sub> as the carrier gas. A Si cap was grown on top of the epi-Ge to passivate and smooth the surface.<sup>9–11</sup> To fabricate the devices, p+ and n+ regions were defined and implanted into the epi-Ge with BF<sub>2</sub> (40 keV,  $4 \times 10^{15}$  cm<sup>-2</sup>) and P (10 keV,  $5 \times 10^{15}$  cm<sup>-2</sup>) for the drain and source electrodes, respectively. The dopants were activated by rapid thermal annealing (RTA) in ambient  $N_2$  in two steps: 650 °C for 60 s in step 1 and 700 °C for the spike ramp in step 2. A 7.8-nm-thick HfO<sub>2</sub> gate dielectric was formed using atomic layer deposition and a 120-nm-thick TiN metal gate was deposited by sputtering. To improve the interface between  $HfO_2$  and the semiconductor, the samples were annealed at 550 °C for 30 s before the metal gate was deposited. The TiN and HfO<sub>2</sub> layers were defined by dry etching to create the metal gate in the final process. After definition of the gate stack, a  $\sim$ 30-nm-thick SiO<sub>x</sub> layer was deposited using plasma-enhanced chemical vapor deposition and spacer formation. A 10-nm-thick Ni layer was deposited using a sputtering system, followed by RTA in ambient N<sub>2</sub> at 250 °C for 30 s and 500 °C for 30 s to form a Ni silicide/germanide film. This was accompanied by a dopant-segregated process as a result of the specific implant conditions and the Ni thickness. Finally, the gate electrode was defined by lithographic patterning and Ag/PbZrTiO<sub>3</sub> (PZT) (10 nm/30 nm) was deposited using an electron-beam evaporator and a lift-off process. The characteristics of the TFET and NC-TFET devices (before and after FE (PZT) deposition, respectively) were the same device for easy comparison.

The general expression for SS for a FET is:

$$SS = \frac{\partial V_g}{\partial (\log_{10} I_d)} = \underbrace{\frac{\partial V_g}{\partial \psi_s}}_{m} \underbrace{\frac{\partial \psi_s}{\partial (\log_{10} I_d)}}_{n} = \left(1 + \frac{C_s}{C_{ins}}\right) \frac{\partial \psi_s}{\partial (\log_{10} I_d)},\tag{2}$$

where  $\psi_s$  is the surface potential, and  $C_s$  and  $C_{ins}$  are the semiconductor and insulator capacitances, respectively. The FE polarization of NC-TFETs improved SS values in both the body factor (m) and the *n*-factor (i.e., according to the Boltzmann tyranny,  $\ln(10)k_bT/q$  for a MOSFET at room temperature; here  $k_b$ , T and q are the Boltzmann constant, the absolute temperature and the electronic charge, respectively). The equivalent circuit for the TFET included  $C_{FE}$ ,  $C_{HfO2}$  and  $C_s$ , which denote the capacitances of the ferroelectric material, HfO<sub>2</sub> and the semiconductor, respectively

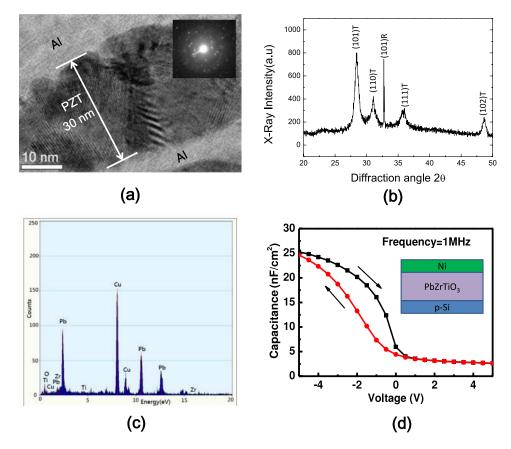

FIG. 2. (a) Cross-sectional TEM of a ~30-nm-thick PZT film on the metal. The inset shows the diffraction pattern of PZT, indicating that it is polycrystalline. (b) The XRD of PZT. The crystalline is identified as tetragonal and rhombohedral phase. (c) The EDX of PZT using an E-gun evaporator system; a low oxygen content was observed. (d) The capacitance-voltage (C-V) of MFS. It shows a clockwise hysteresis and indicates due to FE behavior not traps.

[Fig. 1(b)]. The NC approach is beneficial for body factors are less than unity, such as for polymer FE MOSFETs with SS < 60 mV/decade.<sup>12,13</sup> PZT was used and designed with simulations and experiments to obtain an enhancement in capacitance concomitant with NC in the crystal-line ferroelectric–dielectric bilayer.<sup>14–16</sup> The possible lowering of the *n*-factor can be addressed by employing a new transport mechanism, such as TFETs with a BTBT mechanism.

To experimentally validate FE NC, a top gate metal and PZT layers were deposited on the metal and Si as MFM (metal/FE/metal) and MFS (metal/FE/semiconductor) structure [Fig. 2(a) and (d)]. PZT was deposited on all samples at the same time, including metal, Si and the TFET. Figure 2(a) displays a cross-sectional TEM (transmission electron micrograph) of the PZT after it was annealed at 400  $^{\circ}$ C, showing the resulting ~30-nm-thick polycrystalline layer with a 10- to 30-nm grain size. This was confirmed by the TEM diffraction pattern, shown in the inset in Fig. 2(a). Besides, the crystalline of PZT is identified as tetragonal and rhombohedral phase by XRD (X-ray Diffraction) (Fig. 2(b)). The low oxygen content of PZT, caused by E-gun evaporation growth, was observed by EDX (energy-dispersive X-ray spectroscopy) (Fig. 2(c)) and is beneficial for polarization in ferroelectric applications.<sup>17</sup> The Cu signal originates from the Cu ring holding the TEM samples. The hysteresis FE was validated on MFS with capacitance-voltage measurement. It shows a clockwise hysteresis in Fig. 2(d), i.e., negative shift in capacitance with reverse sweep (+5V to -5V). The MFS with reverse sweep attracts positive charges (holes) have to overcome coercive field of PZT, therefore, the more negative applied bias is necessary. Note that the positive shift in capacitance is attributed to electrons trapping and de-trapping process with localized states of dielectric, like flash memory operation concept. However, the capacitance with reverse sweep in Fig. 2(d) is stretched out since the electrons are released from the interface trap state, which is occupied by electrons with sweep from +5V. This results the recombination with generated holes and capacitance increases gently as compare with that of forward sweep. The polarization was experimentally extracted from hysteretic internal voltage ( $V_{int}$ ) versus  $V_g$  and obtained the amplification of the  $V_g(dV_{int}/dV_g)$  and the ratio was greater than 1.<sup>16</sup> The voltage was amplified during the positive-to-negative sweeps and was applicable to the p-type operations of both the MOSFETs and TFETs.

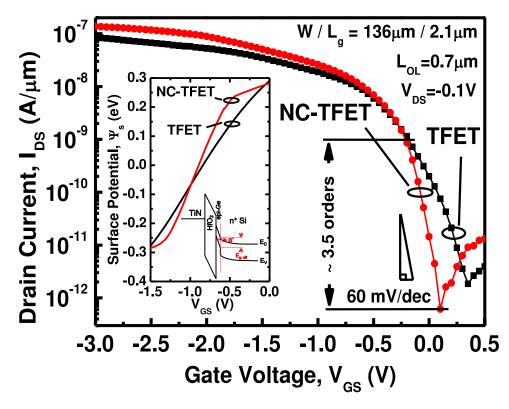

Coupling the FE gate stack with the TFET displayed the features of gate voltage amplification along with surface potential amplification. The transfer characteristics of the NC-TFET significantly improve the SS value (Fig. 3), by about 3.5 orders of magnitude, which then enhanced the output current characteristics. The TFET and the NC-TFET was the same device before and after PZT deposition, respectively. They were the same TFET for comparison and to avoid TFET uniformity issues. The  $V_{int}$  was amplified by the non-linear behavior of the FE NC, leading to a surface potential ( $\psi_s$ ) with the  $V_g$  sweep and a reduction in the m ( $\partial V_g / \partial \psi_s$ ) below 1 [see inset in Fig. 3]. This indicated that the surface potential of the NC-TFET was amplified by the  $V_g$  sweep, in comparison with that of the TFET. However, with a large  $V_g$ , the amplification vanished and both surface potentials were similar.

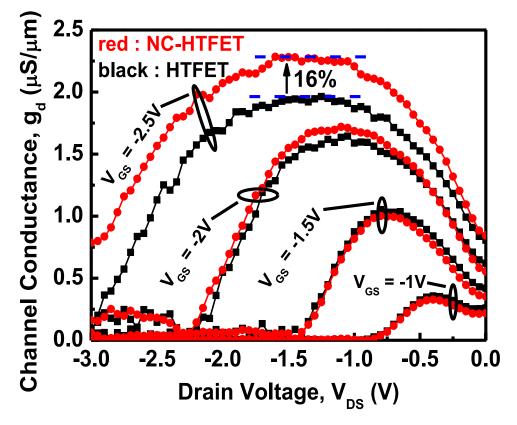

Figure 4(a) shows that the drain conductance  $(g_d)$  only had a 16% increase with a large  $V_{DS}$  (~-2.5 V) [Fig. 4], when compared with the peak  $g_m$  ( $V_{DS} = -0.1$  V).<sup>16</sup> This indicates internal voltage amplification with FE NC effect beneficial to small lateral drain-source bias voltages (-0.1 V). The FE NC showed an improvement in the subthreshold range, while the BTBT boost was slightly enhanced by the saturation current.

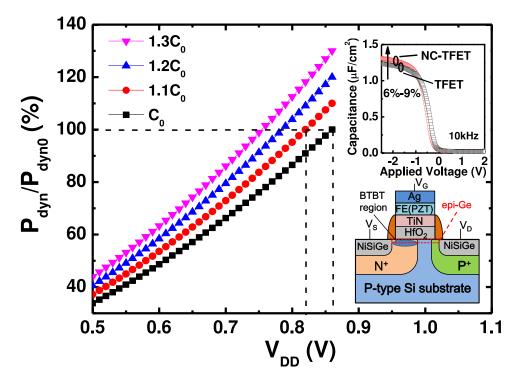

The power consumption is an important issue for the application of NC technologies. The dynamic power consumption is proportional to  $CV^2f$ , where C is the capacitance, V is the power supply voltage, and f is the frequency. The insets in Fig. 5 show the gate capacitances of a

FIG. 3. Transfer characteristics  $(I_d-V_g)$  of the NC-TFET. The subthreshold swing was improved significantly with a FE NC. The current of the NC-TFET was enhanced with a large  $V_{GS}$ . Note that the TFET and NC-TFET used were the same TFET, before and after deposition of the PZT, respectively, for comparison and to avoid TFET uniformity issues. The inset shows the calculated surface potentials of the TFET and NC-TFET. The surface potential of the NC-TFET was amplified during the  $V_g$  sweep and enhanced the BTBT. The inset shows the BTBT mechanism in the TFET.

FIG. 4. Drain conductance  $(g_d)$  vs  $V_{DS}$ . The peak  $g_d$  increased by 16% with the integration of NC. The FE NC showed an improvement in the subthreshold range, while the BTBT boost was slightly enhanced by the saturation current.

FIG. 5. The estimated dynamic power consumption with power supply voltage  $(V_{dd})$  and capacitance (C). The insets show the gate capacitances of the NC-TFET with an enhancement of 6–9%, compared with that of a TFET. The bottom right is a schematic of the NC-TFET.

107117-6 Lee et al.

NC-TFET, which were enhanced by 6–9% compared with a TFET. Figure 5 also shows a schematic of the NC-TFET. The enhanced capacitance was attributed to NC effects, according to the series capacitance in the effective circuits. However, the purpose of a steep subthreshold slope FET, such as a TFET or the NC concept, is to lower the power supply voltage ( $V_{dd}$ ). The  $V_{dd}$  is expected to go below 0.5 V in future generations. Note that  $V_{dd} = 0.86$  V for 16/14 nm in the current technology node. Therefore, increasing the capacitance and decreasing the square of the voltage may lead to a lower consumption of the dynamic power for ferroelectric negative capacitance devices under fixed frequencies. The estimated dynamic power consumption is shown in Fig. 5. If capacitance is increased by 10% for an integrating FE NC, into the current technology node, the  $V_{dd}$  would decrease from 0.86 V to 0.83 V, while maintaining the same power consumption.

In conclusion, a significant improvement in the subthreshold swing (by approximately twice the slope) and an extended range of the steep swing by  $\sim$ 3.5 orders of magnitude were demonstrated with a FE NC gate stack integrated with a TFET. The internal voltage amplification with FE NC effect beneficial to the subthreshold range, while the BTBT boost was slightly enhanced by the saturation current. The validity of the FE NC characteristics was established experimentally, and the power consumption is also discussed in low-power applications of steep subthreshold slope devices. The performance of a steep subthreshold slope device with an integrated FE could be improved in future applications by optimizing the device structure and processing conditions.

## ACKNOWLEDGMENTS

The authors gratefully acknowledge financial support from the National Science Council Taiwan under Grant Nos. 103-2221-E-003-023, 102-2221-E-003-030-MY3 and 102-2622-E-002-014. The processes were supported by National Nano Device Laboratories (NDL) and the UHV-CVD was supported by Prof. C. W. Liu, National Taiwan University (NTU), Taiwan.

- <sup>1</sup> T. Krishnamohan, D. Kim, T. Viet Dinh, A. Pham, B. Meinerzhagen, C. Jungemann, and K. Saraswat, *Tech. Dig., Int. Electron Device Meeting* (2008), p. 947.

- <sup>2</sup> K. K. Bhuwalka, J. Schulze, and I. Eisele, Japn. J. of Appl. Phys. 43, 4073 (2004).

- <sup>3</sup> O. M. Nayfeh, C. N. Chleirigh, J. L. Hoyt, and D. A. Antoniadis, IEEE Electron Device Letter 29, 468 (2008).

- <sup>4</sup> M. H. Lee, S. T. Chang, T.-H. Wu, and W.-N. Tseng, IEEE Electron Device Letter 32, 1355 (2011).

- <sup>5</sup> K. Joen, W.-Y. Lop, P. Patel, C. Y. Kang, J. Oh, A. Bowonder, C. Park, C. S. Park, C. Smith, P. Majhi, H.-H. Tseng, R. Jammy, T.-J. King Liu, and C. Hu, *Tech. Dig.*, VLSI Symp. (2010), p. 121.

- <sup>6</sup> C. Hu, D. Chou, P. Patel, and A. Bowonder, *Proceeding of International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA)* (2008), p. 14.

- <sup>7</sup> M. H. Lee, J.-C. Lin, and C.-Y. Kao, IEEE Trans. on Electron Device **60**, 2423 (2013).

- <sup>8</sup> A. Villalon, C. Le Royer, M. Casse, D. Cooper, B. Previtali, C. Tabone, J.-M. Hartmann, P. Perreau, P. Rivallin, J.-F. Damlencourt, F. Allain, F. Andrieu, O. Weber, O. Faynot, and T. Poiroux, *Tech. Dig.*, *VLSI Symp.* (2012), p. 49.

- <sup>9</sup> C.-Y. Peng, F. Yuan, C.-Y. Yu, P.-S. Kuo, M. H. Lee, S. Maikap, C.-H. Hsu, and C. W. Liu, Appl. Phys. Lett. **90**, 012114 (2007).

- <sup>10</sup> S. Maikap, M. H. Lee, S. T. Chang, and C. W. Liu, Semicond. Sci. Technol. 22, 342 (2007).

- <sup>11</sup> M. H. Lee, S. T. Chang, S. Maikap, C.-Y. Peng, and C.-H Lee, IEEE Electron Device Lett. **31**, 141 (2010).

- <sup>12</sup> G. A. Salvatore, D. Bouvet, and A. M. Ionescu, Tech. Dig., Int. Electron Device Meeting (2008), p. 167.

- <sup>13</sup> A. Rusu, G. A. Salvatore, D. Jimenez, and A. M. Ionescu, Tech. Dig., Int. Electron Device Meeting (2010), p. 395.

- <sup>14</sup> S. Salahuddin and S. Datta, Tech. Dig., Int. Electron Device Meeting (2008), p. 693.

- <sup>15</sup> A. I. Khan, C. W. Yeung, C. Hu, and S. Salahuddin, Tech. Dig., Int. Electron Device Meeting (2011), p. 255.

- <sup>16</sup> M. H. Lee, J.-C. Lin, Y.-T. Wei, C.-W. Chen, W.-H. Tu, H.-K. Zhuang, and M. Tang, *Tech. Dig., Int. Electron Device Meeting* (2013), p. 104.

- <sup>17</sup> M. T. Escote, F. M. Pontes, E. R. Leite, E. Longo, R. F. Jardim, and P. S. Pizani, J. of Applied Phys. 96, 2186 (2004).