Received 26 October 2018; revised 25 November 2018; accepted 6 December 2018. Date of publication 11 December 2018; date of current version 1 March 2019. The review of this paper was arranged by Editor M. Liu.

Digital Object Identifier 10.1109/JEDS.2018.2885932

# Ferroelectric HfO<sub>2</sub> Tunnel Junction Memory With High TER and Multi-Level Operation Featuring Metal Replacement Process

MASAHARU KOBAYASHI® (Member, IEEE), YUSAKU TAGAWA, FEI MO, TAKUYA SARAYA,

AND TOSHIRO HIRAMOTO<sup>(D)</sup> (Member, IEEE)

Institute of Industrial Science, University of Tokyo, Tokyo 153-8505, Japan

CORRESPONDING AUTHOR: M. KOBAYASHI (e-mail: masa-kobayashi@nano.iis.u-tokyo.ac.jp) This work was supported in part by JST PRESTO and in part by Tokyo Electron Ltd.

**ABSTRACT** We have investigated device design of  $HfO_2$ -based ferroelectric tunnel junction (FTJ) memory. Asymmetry of dielectric screening property in top and bottom electrodes is the key for high tunneling electroresistance (TER) ratio. Thus, metal and semiconductor electrodes are proposed. There exists a design space of ferroelectric material parameters to achieve high TER ratio under the constraint of depolarizing field. We have developed an FTJ fabrication process to realize the design. Large polarization charge and symmetric switching voltage are obtained by top metal replacement process. High TER ratio >30 and multi-level cell operation have been successfully demonstrated. Retention characteristics is promising, however, endurance characteristics should be improved for reliable operation.

**INDEX TERMS** Ferroelectric tunnel junction (FTJ), ferroelectric HfO<sub>2</sub>, tunneling electroresistance.

## I. INTRODUCTION

In highly information-oriented society, cyber physical system is an important platform where IoT edge devices sense and communicate data, and cloud servers collect and analyze big data. Under the constraint of power consumption, transistors and memories have to be energy-efficient. Non-volatile memory (NVM) will play a key role to enable energy-efficient computing. IoT edge devices need a low-cost and low-power nonvolatile memory (NVM), and servers need a storage class memory to fill the gap in the memory hierarchy. Moreover, new artificial intelligence (AI) algorithms and applications need massive parallel computing. In-memory computing with NVM can overcome the von-Neumann bottleneck.

Among various NVMs, ferroelectric (FE) memory have revived thanks to the recent discovery of FE-HfO<sub>2</sub> [1]. FE-HfO<sub>2</sub> is expected to overcome several issues in conventional FE materials such as scalability, stability, reliability and environmental safety. If all these issues are solved by FE-HfO<sub>2</sub>, FE memory can be a promising candidate of low power NVM due to its field driven operation principle.

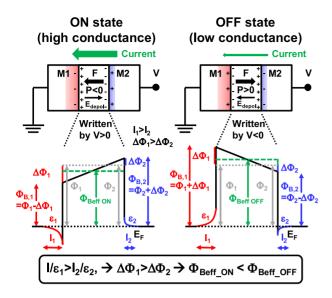

Ferroelectric tunnel junction (FTJ) memory is an emerging memory. It is a two terminal resistive change memory, which can be a competitor for high-density cross-bar memory. FTJ typically consists of a thin FE layer and top and bottom electrodes as shown in Fig. 1. Tunneling current flows through the FE layer. By applying voltage and flipping polarization, tunneling barrier height can be modulated and resistance of the FTJ is changed. FTJ memory was originally proposed as "polar switch" by Esaki *et al.* back in 1971 [2]. Since then, there are reports on experiments and theories for FTJ using conventional FE materials [3]–[11]. Although there are several experimental reports on FTJ with FE-HfO<sub>2</sub> [12]–[19], however, design guideline and process issues [13] are not fully addressed yet.

In this work, first, we address the issues of FTJ design. Next we show a design guideline. Then we develop a fabrication process with FE-HfO<sub>2</sub>. Finally, we realize high on/off resistance ratio and multi-level cell operation. Reliability issues are discussed.

**FIGURE 1.** Schematic illustration of the operation principle of FTJ. Tunneling barrier height and thus TER can be modulated by applying voltage and switching polarization in the FE layer.

(1) Screening length

$$l_{i} = \sqrt{\frac{\varepsilon_{i}k_{B}T}{q^{2}n}} \quad for Bottzmann \\ \sqrt{\frac{2\varepsilon_{i}E_{F}}{3q^{2}n}} \quad for Bottzmann \\ \sqrt{\frac{2\varepsilon_{i}E_{F}}{3q^{2}n}} \quad for Femi-Drac \\ \sqrt{\frac{3\varepsilon_{i}k_{B}T}{3q^{2}n}} \quad for Femi-Drac \\ \sqrt{\frac{1}{3}q^{2}n} \quad for Femi-Drac \\ \sqrt{\frac{1}{3}q^{2}n} \quad for Femi-Drac \\ \sqrt{\frac{1}{3}q^{2}n} \quad for Femi-Drac \\ \sqrt{\frac{1}{2}\varepsilon_{0}\varepsilon_{i}}q, i = 1, 2$$

(2) Potential modulation

$$\Delta \Phi_{i} = \frac{I_{Q}}{\varepsilon_{0}\varepsilon_{i}}q, i = 1, 2$$

(3) Depolarization field

$$E_{depol} = -\frac{P-Q_{s}}{\varepsilon_{0}\varepsilon_{sut}}$$

(4) Screening charge density

$$Q_{s} = \frac{Pd}{\varepsilon_{stat}\left(\frac{I_{1}}{\varepsilon_{1}} + \frac{I_{2}}{\varepsilon_{2}}\right) + d}$$

(5) Screening charge density

$$Q_{s} = \frac{Pd}{\varepsilon_{stat}\left(\frac{I_{1}}{\varepsilon_{1}} + \frac{I_{2}}{\varepsilon_{2}}\right) + d}$$

(5) Screening charge density

$$D_{s} = \frac{J(ON) - J(OFF)}{J(OFF)}$$

FIGURE 2. Simulation framework for FTJ based on direct tunneling model and dielectric screening length. This model can capture device characteristics in low read voltage region.

#### **II. FTJ DEVICE DESIGN**

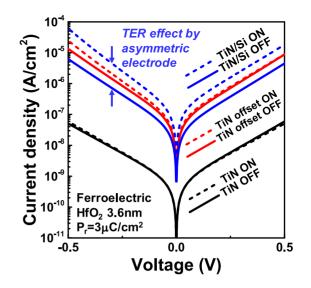

First, we study the impact of top and bottom electrodes by using a simple model. The FTJ model is based on direct tunneling current model with finite screening length and barrier height modulation [6] as shown in Fig. 2. The model is valid in that read voltage of FTJ is supposed to be low, where direct tunneling should be dominant. Note that the TER ratio is defined as  $(I_{on}-I_{off})/I_{off}$ . Fig. 3 shows *I-V* curves with different top and bottom electrodes. With identical metals such as TiN for top and bottom electrodes have different band offsets, TER ratio is still very small. Then, if top and bottom electrodes have different dielectric screening properties, TER ratio becomes large. More specifically, effective dielectric screening length (debye length / dielectric constant) should be different between top and bottom electrodes. Based

FIGURE 3. Simulated *I-V* curves of FTJ with different top and bottom electrodes based on the framework of direct tunneling and dielectric screening length.

on these results, asymmetric dielectric screening property is important to obtain high TER ratio. In this work, we propose to use a metal and a semiconductor for top and bottom electrodes, respectively.

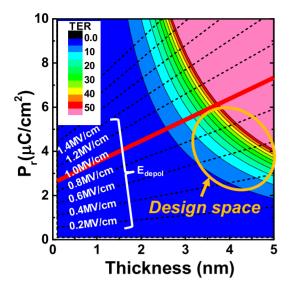

With the asymmetric dielectric screening property of metal-ferroelectric-semiconductor (MFS) structure FTJ, we explore design space of material parameters such as remanent polarization ( $P_r$ ) and ferroelectric thickness ( $t_F$ ). Fig. 4 shows the contour plot of the simulated TER ratio as a function of  $P_r$  and  $t_F$ . In general, as  $P_r$  and  $t_F$  increase, TER ratio increases. However, there is a constraint; depolarizing field ( $E_{depol}$ ) should not exceed coercive field ( $E_c$ ) [12]. Otherwise FTJ does not have data retention.  $E_{depol}$  was also calculated and indicated by dotted lines in Fig. 4. Typical  $E_c$  of FE-HfO<sub>2</sub> is about 1 MV/cm, which is the boundary. Design space should be explored below this boundary in Fig. 4.  $P_r$  is  $3\sim5 \ \mu C/cm^2$  and  $t_F$  is  $3\sim5 \ nm$ .

## **III. PROCESS DEVELOPMENT FOR FTJ**

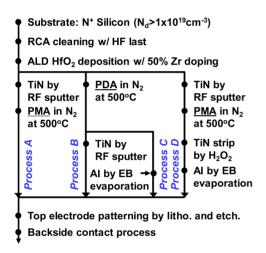

To realize the device design in Section II, we develop FE-HfO<sub>2</sub> FTJ processes. Fig. 5 shows the process flow. Starting from N<sup>+</sup>-Si substrate which is doped by  $1 \times 10^{19} \text{cm}^{-3}$ , the substrate was cleaned by RCA wet clean. HfO2 film was deposited by atomic layer deposition (ALD) system at 250°C with 50% Zr doping (HZO). Then there are four different types of process from A to D for top metal and anneal process. In process A, TiN is deposited and then post metallization anneal (PMA) is performed. In process B, post deposition anneal (PDA) is performed and then TiN is deposited. In process C, PDA is performed and then Al is deposited. In process D, TiN is deposited and PMA is performed. Then TiN is stripped and Al is deposited instead. TiN is deposited by radio-frequency (RF) reactive sputtering in N<sub>2</sub> ambient and the thickness is 50 nm. PDA and PMA are performed in RTA system at 500 °C for 10 sec.

**FIGURE 4.** Contour plot of the simulated TER ratio of FE-HfO<sub>2</sub> FTJ as a function of  $P_r$  and  $t_F$ .  $E_{depol}$  is indicated by dotted lines. Red line shows the typical  $E_c = 1$  MV/cm of FE-HfO<sub>2</sub>.

FIGURE 5. Fabrication process flow of FE-HfO<sub>2</sub> FTJs. There are four different types of process from A to D for top metal and anneal process.

TiN is stripped by  $H_2O_2$ . Al is deposited by EB evaporation and the thickness is 100 nm. the samples are finished with patterning top electrode and back side contact process. X-ray photoelectron spectroscopy (XPS) is used for characterizing the surface of the HZO film. X-ray diffraction (XRD) and transmission electron microscope (TEM) are used for characterizing crystalline property of the HZO film. FTJs are tested by electrical measurement.

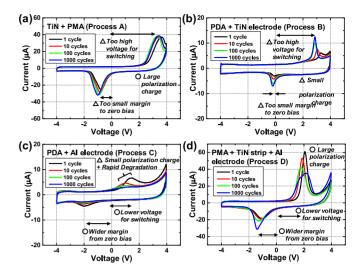

We fabricated and characterized ferroelectric property of 10 nm-thick FE-HfO<sub>2</sub> for process A to process D. Fig. 6 shows low frequency *I-V* measurement results with electrical cycling.

Process A is a default process. The polarization charge is large but the switching voltages are very asymmetric. This means that large voltage is needed for switching in the positive voltage side and voltage margin is very small in the

FIGURE 6. Measured low frequency *I-V* curves for (a) process A, (b) process B, (c) process C, and (d) process D, with electrical cycling.

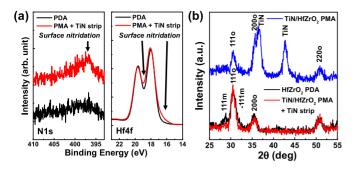

negative voltage side. This can be attributed to the internal field caused by the workfunction difference between top and bottom electrodes. Top TiN electrode should be replaced by another metal such as Al. Since Al cannot endure PMA process, PDA was evaluated. In process B, the polarization charge becomes small because of less FE-phase formation than in process A. The switching voltages are still asymmetric. In process C with Al electrode, the switching voltages become symmetric thanks to the workfunction adjustment. However, the polarization charge is still small for PDA similarly to process B. Furthermore, after electrical cycling, ferroelectricity is severely degraded possibly because of the interaction between the Al electrode and the HZO film. In process D, the switching voltages become symmetric while large polarization charge is maintained. There are three reasons why process D works. First, with TiN capping on top, HZO film can be crystallized as FE-phase more effectively by PMA than by PDA without TiN capping. Second, during PMA, the surface of HZO film is nitrided so that the interaction between Al and HZO is suppressed. Third, workfunction of the top metal is properly adjusted by Al top electrode. The surface nitridation was confirmed by XPS spectra of samples with PMA + TiN strip, and PDA as shown in Fig. 7 (a). N1s spectrum signal and the chemical shift by nitrogen bonding in Hf4f spectra are clearly seen. FE-phase formation is confirmed by comparing XRD spectra of the samples with PMA, PDA and PMA + TiN strip. FE orthorhombic phase is maintained even after stripping TiN without monoclinic phase.

## **IV. FTJ CHARACTERIZATION RESULTS AND DISCUSSIONS**

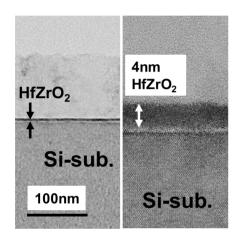

Based on the process D developed in Section III, we thinned the thickness of HZO down to 4 nm and fabricated FTJ. Fig. 8 shows the cross sectional TEM images of the fabricated FTJ. HZO is uniformly deposited and fully crystallized.

**FIGURE 7.** (a) Measured XPS spectra of N1s and Hf4f for the samples with PMA + TiN strip and PDA. (b) Measured XRD spectra for the samples with PMA, PDA and PMA + TiN strip.

FIGURE 8. Cross sectional TEM images of the fabricated FTJ with 4 nm-thick HZO film. Top electrode is Al. HZO is uniformly deposited and fully crystallized.

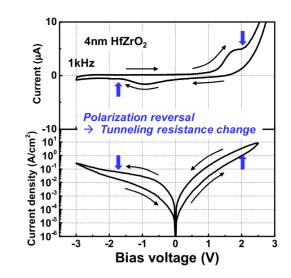

Then we measured low frequency and direct-current (DC) *I-V* curves of the FTJ as shown in Fig. 9. Hysteresis is seen in the DC *I-V* curve which corresponds to the polarization switching in the low frequency *I-V* curve at 1 kHz. Polarization charge is estimated to be 5  $\mu$ C/cm<sup>2</sup> at 4 nm thickness from transient measurement, which is within the design space as described in Section II.

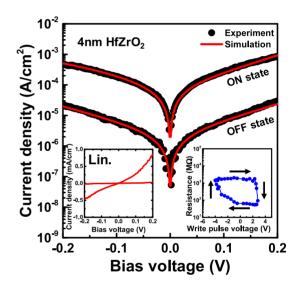

Then we measured read *I-V* current with write pulse voltage. Read voltage is limited to 0.2 V to avoid disturbance by read operation. As shown in Fig. 10, with +2.8 V/-4.0 V write/erase voltage, TER ratio as high as 30 is achieved. The simulation result fits very well to the measured *I-V* curve in the direct tunneling regime at low read voltage. The key fitting parameters are as follows. For FE-layer,  $P = 5 \,\mu\text{C/cm}^2$ ,  $d = 4 \,\text{nm}$ ,  $\varepsilon_{\text{stat}} = 30$ . For bottom semiconductor electrode,  $l_1 = 0.9 \,\text{nm}$ ,  $\varepsilon_1 = 12$ ,  $\Delta \Phi_1 = 0.23 \,\text{eV}$ . For top metal electrode,  $l_2 = 0.05 \,\text{nm}$ ,  $\varepsilon_2 = 2.0$ ,  $\Delta \Phi_2 = 0.076 \,\text{eV}$ .

Write pulse dependence on resistance of the FTJ is shown in the inset of Fig. 10. The curve is obtained by changing write pulse voltage gradually. In the positive write pulse region, the resistance changes abruptly from the high resistance state (HRS) to the low resistance state (LRS). This is because accumulation charge is formed in the

FIGURE 9. Measured (top) low frequency *I-V* curve at 1 kHz and (bottom) DC *I-V* curve of the fabricated FTJ. Polarization charge is estimated to be 5  $\mu$ C/cm<sup>2</sup> at 4 nm thickness.

**FIGURE 10.** Measured read *I-V* current with +2.8 V/-4.0 V write/erase pulse voltage. The left inset shows the same *I-V* curve with the linear scale. The right inset shows the resistance versus write pulse voltage.

bottom N<sup>+</sup>-Si electrode and large voltage is induced on the FE layer. On the other hand, in the negative write pulse region, the resistance changes gradually from LRS to HRS. This is because depletion layer is formed in the bottom N<sup>+</sup>-Si electrode and large voltage drops on the depletion layer.

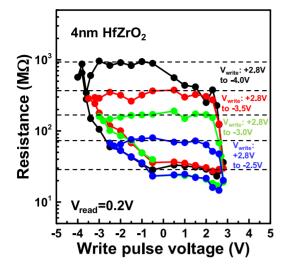

Since the depletion layer works like a voltage buffer in the negative write pulse voltage, the resistance in HRS can be changed by adjusting the maximum write pulse voltage with moderate write noise margin. Fig. 11 shows the resistance versus write pulse voltage with different maximum write pulse voltages. Multi-level cell operation is achieved by first setting to the lowest resistance state in positive write pulse voltage and then applying negative write pulse voltage for target resistance level. Each level has a flat level of the

FIGURE 11. Measured resistance of the FTJ versus write pulse voltage as a function of maximum write pulse voltages.

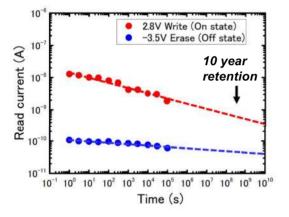

**FIGURE 12.** Measured retention characteristics of FTJ with 2.8 V/ – 3.5 V write/erase pulse voltages.

resistance versus write pulse voltage, which means that each level is immune to disturb voltage.

Lastly, we examined reliability of the FTJ in terms of retention and endurance characteristics. Fig. 12 shows the retention characteristic of the FTJ, where 10-year retention is expected. Note that LRS is degraded toward HRS and the amount of degradation in LRS is larger than HRS. This could be due to the internal field at retention state. As shown in Fig. 6(d), there is slight asymmetry of switching voltages even with process D. Therefore, the negative internal field is applied to both LRS and HRS at retention state, and thus LRS is gradually erased and drifted to HRS.

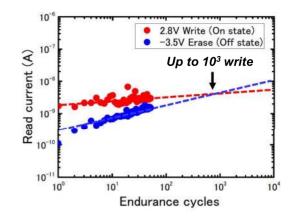

Fig. 13 shows the endurance characteristics of the FTJ, where only up to  $10^3$  cycles are expected but breakdown occurs before the expected cycle times. Endurance degradation can be attributed to the stress induced leakage current by formation of defects and percolation paths during electrical cycling [20]. Further investigation on the degradation mechanism and improvement of endurance characteristics are important and our future work.

FIGURE 13. Measured endurance characteristics of FTJ with 2.8 V/ -3.5 V write/erase pulse voltages.

### **V. SUMMARY**

We investigated the device design for FE-HfO<sub>2</sub> FTJ. Asymmetric dielectric screening property in top and bottom electrodes is important. MFS structure FTJ was proposed. Design space in material parameters was explored for high TER ratio under the constraint of  $E_{\text{depol}}$ . We developed the metal replacement process to realize the design. With 4 nm-HZO film, TER as high as 30 was achieved with multi-level cell operation, which are promising results for storage memory and emerging AI applications. While retention characteristics of the FTJ is satisfying, however, endurance characteristics is only up to  $10^3$  cycles and needs to be significantly improved.

## REFERENCES

- J. Muller *et al.*, "Ferroelectricity in simple binary ZrO<sub>2</sub> and HfO<sub>2</sub>," *Nano Lett.*, vol. 12, no. 8, pp. 4318–4323, 2012.

- [2] L. Esaki, B. B. Laibowitz, and P. J. Stiles, "Polar switch," *IBM Tech. Discl. Bull.*, vol. 13, no. 8 p. 2161, 1971.

- [3] E. Y. Tsymbal and H. Kohlstedt, "Tunneling across a ferroelectric," *Science*, vol. 313, no. 5784, pp. 181–183, 2006.

- [4] H. Kohlstedt, N. A. Pertsev, J. R. Contreras, and R. Waser, "Theoretical current-voltage characteristics of ferroelectric tunnel junctions," *Phys. Rev. B, Condens. Matter*, vol. 72, no. 12, 2005, Art. no. 125341.

- [5] A. Gruverman *et al.*, "Tunneling electroresistance effect in ferroelectric tunnel junctions at the nanoscale," *Nano Lett.*, vol. 9, no. 10, pp. 3539–3543, 2009.

- [6] D. Pantel and M. Alexe, "Electroresistance effects in ferroelectric tunnel barriers," *Phys. Rev. B, Condens. Matter*, vol. 82, Oct. 2010, Art. no. 134105.

- [7] V. Garcia and M. Bibes, "Ferroelectric tunnel junctions for information storage and processing," *Nat. Comm.*, vol. 5, p. 4289, Jul. 2014.

- [8] H. Yamada *et al.*, "Giant electroresistance of super-tetragonal BiFeO3based ferroelectric tunnel junctions," *ACS Nano*, vol. 7, no. 6, pp. 5385–5390, 2013.

- [9] A. Chanthbouala *et al.*, "Solid-state memories based on ferroelectric tunnel junctions," *Nat. Nanotech.*, vol. 7, no. 2, pp. 101–104, 2012.

- [10] B. B. Tian *et al.*, "Tunnel electroresistance through organic ferroelectrics," *Nat. Comm.*, vol. 7, May 2016, Art. no. 11502.

- [11] M. Asa and R. Bertacco, "Impact of semiconducting electrodes on the electroresistance of ferroelectric tunnel junctions," *Appl. Phys. Lett.*, vol. 112, no. 8, 2018, Art. no. 082903.

- [12] S. Fujii *et al.*, "First demonstration and performance improvement of ferroelectric HfO<sub>2</sub>-based resistive switch with low operation current and intrinsic diode property," in *Proc. VLSI Tech. Symp.*, 2016, pp. 1–2.

FEI MO received the B.S. degree in micro-

electronics and solid-state electronics engineering

from the University of Electronic Science and

Technology of China, Chengdu, China, and the

M.S. degree in electronics engineering from the

Kyoto Institute of Technology, Kyoto, Japan, in

2013 and 2017, respectively, where he is currently

pursuing the Ph.D. degree with the Department of

Electrical Engineering and Information Systems,

University of Tokyo. His current research inter-

ests include ferroelectric nonvolatile memory and

neuromorphic applications of resistive switching memories.

- [13] M. Kobayashi, Y. Tagawa, F. Mo, T. Saraya, and T. Hiramoto, "Device and process design for HfO<sub>2</sub>-based ferroelectric tunnel junction memory with large tunneling electroresistance effect and multi-level cell," in *Proc. Silicon Nano Workshop*, 2018, p. 29.

- [14] Z. Fan et al., "Ferroelectricity and ferroelectric resistive switching in sputtered Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films," Appl. Phys. Lett., vol. 108, no. 23, 2016, Art. no. 232905.

- [15] F. Ambriz-Vargas et al., "Tunneling electroresistance effect in a Pt/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/Pt structure," Appl. Phys. Lett., vol. 110, no. 9, 2017, Art. no. 093106.

- [16] X. Tian and A. Toriumi, "New opportunity of ferroelectric tunnel junction memory with ultrathin HfO<sub>2</sub>-based oxides," in *Proc. Electron Devices Technol. Manuf. (EDTM) Conf.*, 2017, pp. 36–64.

- [17] A. Chouprik *et al.*, "Electron transport across ultrathin ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> films on Si," *Microelectron. Eng.*, vol. 178, pp. 250–253, Jun. 2017.

- [18] Y. Goh and S. Jeon, "Enhanced tunneling electroresistance effects in HfZrO-based ferroelectric tunnel junctions by high-pressure nitrogen annealing," *Appl. Phys. Lett.*, vol. 113, no. 5, 2018, Art. no. 052905.

- [19] Z. Dong, X. Cao, T. Wu, and J. Guo, "Tunneling current in HfO<sub>2</sub> and Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-based ferroelectric tunnel junction," *J. Appl. Phys.*, vol. 123, no. 9, 2018, Art. no. 094501.

- [20] M. Yamaguchi *et al.*, "Impact of specific failure mechanisms on endurance improvement for HfO<sub>2</sub>-based ferroelectric tunnel junction memory," in *Proc. Int. Rel. Phys. Symp. (IRPS)*, 2018, pp. 6D.2-1–6D.2-6.

**MASAHARU KOBAYASHI** (M'09) received the B.S. and M.S. degrees in electronics engineering from the University of Tokyo, Tokyo, Japan, in 2004 and 2006, respectively, and the Ph.D. degree in electronics engineering from Stanford University, Stanford, CA, USA, in 2010. He joined IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, in 2010. Since 2014, he has been an Associate Professor with the Institute of Industrial Science, University of Tokyo.

**YUSAKU TAGAWA** received the B.S. degree in electrical engineering and computer science from Kyushu University, Fukuoka, Japan, in 2017. He is currently pursuing the M.S. degree in electronics engineering with the University of Tokyo, Tokyo, Japan. His research interests include the development of ferroelectric tunnel junction memory for reliable and high energy-efficiency operation, and fabrication of nanostructured device.

**TAKUYA SARAYA** received the B.S. and M.S. degrees in electrical and electronics engineering from Chiba University in 1993, and 1995, respectively. Since 1995, he has been a Research

Associate with the Institute of Industrial Science,

University of Tokyo. His research interests are debice physics in silicon MOSFET and IGBTs.

**TOSHIRO HIRAMOTO** (M'92) received the B.S., M.S., and Ph.D. degrees in electronic engineering from the University of Tokyo, Japan, in 1984, 1986, and 1989, respectively. In 1989, he joined the Device Development Center, Hitachi Ltd., Ome, Japan. In 1994, he joined the Institute of Industrial Science, University of Tokyo, where he has been a Professor since 2002.

He is a fellow of the Japan Society of Applied Physics and a member of IEICE.