# Filter Integration in Ultra Thin Organic Substrate via 3D Stitched Capacitor

Sunghwan Min, Seunghyun Hwang, Daehyun Chung, Madhavan Swaminathan, Vivek Sridharan, Hunter Chan, Fuhan Liu, Venky Sundaram, and Rao R. Tummala

> School of Electrical and Computer Engineering, Georgia Institute of Technology Atlanta, GA 30332, USA

sunghwan.min@ece.gatech.edu

*Abstract*— This paper presents filters integrated in ultra thin multilayer organic substrate using 3D stitched capacitor alleviating shunt parasitics and providing tunable capacitors. Insertion loss of less than 2.2dB, return loss of greater than 15dB at 2.4 GHz and attenuation of greater than 30dB below 2.0 GHz and at 4.7 GHz were measured. The measured results showed good agreement with simulated results. This paper demonstrated 2.4 GHz bandpass filters with size of 2.2mm x 3.0mm x 0.2mm (1.2mm<sup>3</sup>) in ultra thin organic RXP substrate.

# I. INTRODUCTION

Wireless communication systems and technologies have been the most active part of our modern electronics for last few decades. This will continue in the foreseeable future to bring us into the ubiquitous era. For building our future information society with wireless communications, there have been significant researches and numerous developments in radio frequency (RF), microwave and millimeter-wave frequency spectrums ranging from 300 MHz to 300 GHz. This has led to the development of wireless communication standards such as GSM, WCDMA, WLAN, WiMAX, LTE, UWB and WPAN in RF and microwave spectrums.

In the semiconductor society, fragile active devices need to be encapsulated and protected by a mixture of metallic, dielectric, magnetic, and semiconductive packaging materials. The most critical requirement in electronic packaging is that the encapsulated devices should be electrically and reliably interconnected. Hence, packaging materials and their fabrication processes have been engineered in order to meet the product-specific requirements [1-2]. With advances in packaging materials and fabrication processes, packageoriented system integration solutions such as system-inpackage (SIP) and system-on-package (SOP) enable wireless communication systems to be integrated into a package [3-6].

Today, low temperature co-fired ceramic (LTCC) technology having high dielectric constant and low loss tangent has provided component, module and system integration solutions for RF, microwave and millimetre-wave applications. However, LTCC may not necessarily provide a long-term effective packaging solution due to thicker substrate, higher processing temperature (>900°C), heavier weight and smaller panel size as compared to organic technologies. This barrier led to the development of organic-based SOP solutions. Over the last few years, liquid crystal polymer (LCP) organic-based SOP technology has been considered as a promising candidate for system integration because of its superior

electrical properties up to millimeter-wave frequencies [7]. LCP has solved the issues that LTCC is facing. However, LCP also requires a relatively higher processing temperature (290°C) compared to FR-4, which can be a bottleneck for low-cost system integration.

Recently, the nano-scale SOP based on ultra-thin organic dielectric material called RXP [8] has been developed. Unlike LCP, RXP can be made ultra thin under low processing temperature (220°C), which is compatible with standard printed circuit board manufacturing processes. RXP supports ultra fine-pitch wiring with low surface profile copper. The RXP-based SOP technology is under development for embedding active dies into cavities using chip last technology to achieve less than 0.5mm thick module. A supply chain for the RXP material that includes fabrication is also being developed as part of the Embedded Actives and Passives (EMAP) consortium at the Georgia Institute of Technology's 3D-Systems Packaging Research Center (GT-PRC).

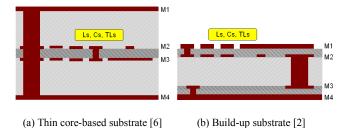

For the first time, this paper presents lowest volume WLAN 2.4 GHz filters integrated in the ultra thin RXP substrate developed during the EMAP consortium. A cross section of the RXP substrate with four-metal layers is shown in Fig. 1.

Fig. 1 Cross section of ultra thin RXP substrate

## II. FILTER INTEGRATION CHALLENGES IN THIN SUBSTRATE

In RF/microwave/millimeter-wave applications, a filter is an essential device for transmitting passband signals and rejecting stopband signals, which requires low insertion loss at passband frequencies and high attenuation at stopband frequencies [9]. Depending upon the specifications, filters are synthesized and implemented as lumped elements such as inductors and capacitors and/or distributed elements such as transmission lines and are physically realized on planar substrates. The use of planar substrates allows filters to be cost effective under volume production.

In [6], filters were integrated in an LCP substrate where inductors and capacitors were realized on a thin dielectric and sandwiched between two ground planes as shown in Fig. 2(a). For having known good substrates before assembly, there has been a clear need for eliminating the top ground plane in order to allow engineers to debug and test the embedded passive devices. After the top ground plane is eliminated, the substrate is becoming similar to a build-up substrate, which is widely used for low-cost electronic packaging [2]. A typical build-up substrate consisting of one thick dielectric core and two thin dielectric prepregs with four metal layers is shown in Fig. 2(b).

Fig. 2 Filter integration schemes

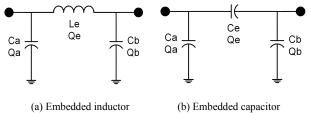

Fig. 3 shows the parameterized two-port models of embedded inductors and capacitors in multilayer substrate. The parameterized models are useful for modeling of embedded inductors and capacitors at the frequency band below the self resonant frequency and for providing design insights without relying on complex equivalent circuit models. The circuits and quality factors for inductor ({Le, Ca, Cb}, {Qe, Qa, Qb}) and capacitor ({Ce, Ca, Cb}, {Qe, Qa, Qb}) were analytically extracted from simulated or measured scattering parameters [6]. The capacitances Ca and Cb are shunt parasitics at input and output ports.

Fig. 3 Parameterized two-port equivalent circuit models [6]

For having high quality inductors with high inductance (Le), inductors require a large separation from the ground plane with smooth conductor surface. For having high quality capacitors with high capacitance (Ce), capacitors require a thin dielectric with high dielectric constant and low loss tangent. For high performance filter integration into the buildup substrate shown in Fig. 2(b), it is appropriate for inductors and capacitors to be integrated on the top metal layers (M1 and M2) with a ground plane on M4. However, filter integration in the build-up substrate presents its own design challenges due to the asymmetric ground plane allocation. The challenges originate from unbalanced shunt parasitics (Ca, Cb) of parallel plate capacitor in the build-up substrate.

When a parallel plate capacitor is implemented on the M1 and M2 metal layers, it is to be noted that Ca is different from Cb. It is because the bottom plate of the capacitor only faces the ground plane. This imbalance of shunt parasitics of the parallel plate capacitor worsens as the thickness between the bottom plate of the capacitor and the ground plane decreases or the effective dielectric constant increases.

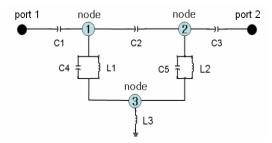

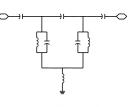

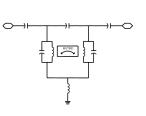

For further discussion of the effect of shunt parasitic capacitances in filter integration, a schematic of two-pole bandpass filter with a grounding inductor is shown in Fig. 4. It is assumed that the bandpass filter is symmetric (C1=C3, C4=C5, L1=L2) and all capacitors are only realized by parallel plate capacitors. It should be noted that when all the circuits in the schematic shown in Fig. 4 are replaced by the parameterized circuit models, the nodes 1 and 2 will definitely have different shunt capacitances due to the unbalanced shunt capacitance of C2. In ultra-thin substrate, the unbalanced shunt parasitics cause filters to be swamped by shunt parasitics, which may not be compensated by circuit augmentation [10]. This can result in performance degradation of the filters and contribute to a long design cycle time.

Interdigitated capacitor can solve the unbalanced shunt parasitic issue. However, it loses the high capacitance density advantage of the parallel plate capacitor. Therefore, this paper proposes a novel capacitor called 3D stitched capacitor, which can alleviate shunt parasitics and provide tunable capacitors and filters in ultra-thin substrate.

Fig. 4 Second-order bandpass filter with a grounding inductor

### **III. 3D STITCHED CAPACITOR**

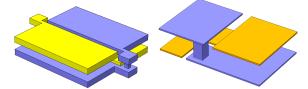

The basic idea of the stitched capacitor is to combine the advantages of the parallel plate capacitor with the capability of high density capacitance integration and of the interdigitated capacitor with the controllability of parasitic shunt capacitance.

The design flow for making the stitched capacitor starts with segmenting the parallel plate capacitor into sections with an arbitrary shape and then stitching the segmented sections using vias. The desirable shunt parasitics can be obtained by controlling the surface area. For example, a 3D view of two stitched capacitors is illustrated in Fig. 5.

Fig. 5 Stitched capacitors

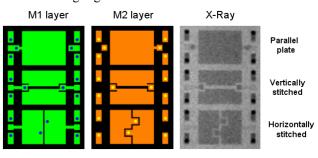

For demonstration of the stitched capacitor, a parallel plate capacitor and two stitched capacitors were designed on the build-up substrate shown in Fig. 2(b). Three capacitors located on M1 and M2 with a ground plane on M4 were fabricated and measured. Fig. 6 shows the top view of M1 and M2 metal layers and the X-ray photo of three capacitors. The measured capacitances Ce, Ca, Cb at 2 GHz are detailed in Table 1. As

noted in the table below, Ca is not equal to Cb for the parallel plate capacitor and Ca is close to Cb for two stitched capacitors. It should be also noted that the shunt parasitic capacitances of stitched capacitors are reduced to half of the parallel plate capacitor, which demonstrates that the stitched capacitor can alleviate shunt parasitics. The minor reduction of capacitance in stitched capacitors is due to the gaps and vias for stitching segmented sections.

Fig. 6 Parallel plate and stitched capacitors (layout, fabricated)

TABLE I

Parameterized capacitances @ 2 GHz

| Capacitor                | Ce<br>(pF) | Ca<br>(pF) | Cb<br>(pF) | Note    |

|--------------------------|------------|------------|------------|---------|

| Parallel<br>Plate        | 2.96       | 0.05       | 0.58       | Ca ≠ Cb |

| Vertically<br>Stitched   | 2.65       | 0.29       | 0.31       | Ca ≈ Cb |

| Horizontally<br>Stitched | 2.78       | 0.31       | 0.30       | Ca ≈ Cb |

In addition to the controllability of shunt parasitics by changing the bottom surface area, the shape on top metal surface can be controlled by filling, etching and carving conductors so that the capacitance Ce can be tuned after substrate fabrication and during assembly. Additionally, extra capacitors can be directly mounted on the exposed top metal layer of 3D stitched capacitors using surface-mount technology, which allows the capacitance Ce of stitched capacitors to be tuned. Similarly, a resonator or filter can be realized by mounting inductors, MEMS devices or dies on the exposed surface during assembly. The stitched capacitor can be also integrated and implemented in planar substrates including semiconductor substrates.

#### IV. FILTER INTEGRATION

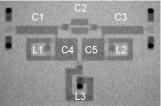

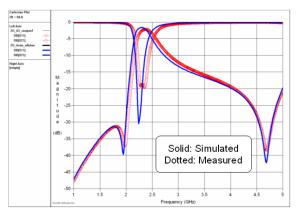

For demonstration of filter integration in ultra-thin substrate, three bandpass filters with stitched capacitor were designed: 1) a second-order bandpass filter with a grounding inductor that provided a transmission zero around 2.0 GHz, 2) a second-order coupled bandpass filter with a grounding inductor that provided two transmission zeroes around 2.0 and 4.7 GHz, and 3) a second-order coupled bandpass filter with a grounding inductor and a shunt inductor at port that provided four transmission zeroes around 1.8, 2.0, 3.7 and 4.7 GHz. The circuit topologies of three filters are shown in Figs. 7(a), 8(a) and 9(a). The filters were synthesized by using the filter synthesis procedure and were optimized by using a circuit simulator [12].

The circuits were implemented on the ultra-thin RXP substrate shown in Fig. 2(b) by using the closed-loop RF design flow [6]. The designed thickness of core, prepreg and metal is 115um, 20um, and 9um, respectively. The overall thickness of RXP substrate is less than 0.2mm. The core (called RXP1) and prepreg (called RXP4) were characterized up to 110 GHz [11]. The characterized RXP1 has dielectric constant of 3.4 and loss tangent of 0.0038 and RXP4 has dielectric constant of 3.0 and loss tangent of 0.0043 [11].

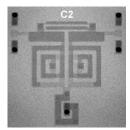

Inductors and capacitors were implemented on M1 and M2 while M4 was dedicated to the ground plane and M3 was a dummy metal layer for grounding. The final layout was achieved after layout optimization using an electromagnetic simulator [13]. The X-ray photos of the three filters are shown in Figs. 7(b), 8(b) and 9(b). As seen in the photos, filters are symmetric and the coupling capacitor C2 shown in Fig. 4 was realized as a stitched capacitor. The size of three filters in order is  $3.6 \text{mm x } 2.4 \text{mm x } 0.2 \text{mm} (1.7 \text{mm}^3)$ ,  $2.2 \text{mm x } 3.0 \text{mm x } 0.2 \text{mm} (1.2 \text{mm}^3)$  and  $3.6 \text{mm x } 0.2 \text{mm} (4.9 \text{mm}^3)$ , respectively.

(a) Filter topology

(b) X-ray photo (3.6mm x 2.4mm)

(a) Filter topology

(b) X-ray photo (2.2mm x 3.0mm)

Fig. 8 Second-order coupled bandpass filter with a grounding inductor

(a) Filter topology

(b) X-ray photo (3.6mm x 6.9mm)

Fig. 9 Second-order coupled bandpass filter with a grounding inductor and a shunt inductor at port

The designed filters were fabricated by GT-PRC under EMAP consortium. The measurement was carried out using short-open-load-thru (SOLT) calibration by Agilent PNA 8363B with Cascade GSG 500um coplanar probes. The measurement equipment is shown in Fig. 10.

Fig. 10 Measurement equipment with GSG probes

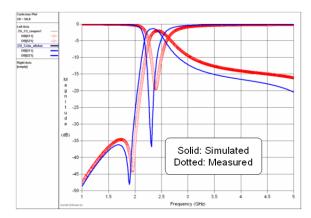

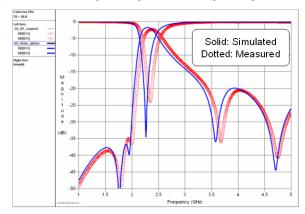

Figs. 11, 12 and 13 show the correlation between simulated (solid) and measured (dotted) frequency responses (S11 and S21) of the three filters. Measured responses show good correlation with simulated responses. The small discrepancies may be attributed to material and process variations in fabrication. Measured insertion loss of less than 2.2dB and return loss of greater than 15dB at 2.4 GHz were achieved and attenuation of greater than 30dB below 2.0 GHz and 35dB at 4.7 GHz was achieved.

# V. CONCLUSIONS

This paper presents filters integrated in ultra thin RXP organic substrate with four metal layers using the 3D stitched capacitor. The 3D stitched capacitor alleviates shunt parasitics and provides tunable capacitors and filters. Lowest volume  $(1.2\text{mm}^3)$  2.4 GHz bandpass filters with size of 2.2mm x 3.0mm x 0.2mm were integrated in ultra thin RXP substrate. Insertion loss of less than 2.2dB, return loss of greater than 15dB at 2.4 GHz and attenuation of greater than 30dB below 2.0 GHz and at 4.7 GHz were measured.

#### ACKNOWLEDGMENT

The authors would like to thank the GT-PRC Embedded Actives and Passives (EMAP) consortium member companies for mentoring and supporting this work.

#### REFERENCES

- [1] Rao R. Tummala and Madhavan Swaminathan, *Introduction to System-on-Package (SOP)*, McGraw-Hill, 2008.

- [2] Clyde F. Coombs, Jr, Printed Circuits Handbook, McGraw-Hill, 2008.

- [3] Rao R. Tummala and Joy Laskar, "Gigabit wireless SOP technology," IEEE Proceeding, vol. 92, pp. 376-387, Feb. 2004

- [4] Lap K. Yeung, Ke-Li Wu, and Yuanxum E. Wang, "Low-temperature cofired ceramic LC filters for RF applications," IEEE Magazine, pp. 118-128, Oct. 2008.

- [5] M. Swaminathan, et al., "Design and fabrication of integrated RF modules in liquid crystalline polymer (LCP) substrates," 32nd Annual Conference of IEEE Industrial Electronics Society, Nov. 2005

- [6] S.-H. Min, et al., "RF design methodology for design-cycle-time reduction using parameterization of embedded passives on multilayer organic substrates," IEEE MTT-S Digest, pp. 1397-1400, June 2008.

- [7] D. Thompson, et al., "Characterization of liquid crystal polymer (LCP) material and transmission lines on LCP substrates from 30-110 GHz," IEEE Trans. on Microwave Theory Tech., vol. 52, pp. 1343-1352, April 2004

- [8] V. Sundaram, et al., "Super high density two metal layer ultra-thin organic substrates for next generation system-on-package (SOP), SiP and ultra-fine pitch flip-chip packages," in Pan Pacific Microelectronics Symposium, Hawaii, 2009

- [9] J.-S. Hong and M. J. Lancaster, *Microstrip Filters for RF/Microwave Applications* John Wiley & Sons, Inc., 2001.

- [10] J. Kolstad, et al., "A new circuit augmentation method for modeling of interconnects and passive components," IEEE Trans. on Advanced Packaging, vol. 29, no. 1, pp. 67-77, Feb. 2006.

- [11] S. Hwang, et al., "Characterization of next generation thin low-K and low-loss organic dielectrics from 1 to 110 GHz" accepted for publication on IEEE Advanced Packaging, 2009

- [12] Agilent ADS, www.agilent.com

- [13] Sonnet EM, www.sonnetusa.com

Fig. 11 Second-order bandpass filter with a grounding inductor

Fig. 12 Second-order coupled bandpass filter with a grounding inductor

Fig. 13 Second-order coupled bandpass filter with a grounding inductor and a shunt inductor at port