# Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

January 2016

## FINITE ELEMENT AND IMAGING APPROACHES TO ANALYZE MULTISCALE ELECTROTHERMAL PHENOMENA

Amir Koushyar Ziabari Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open access dissertations

### Recommended Citation

Ziabari, Amir Koushyar, "FINITE ELEMENT AND IMAGING APPROACHES TO ANALYZE MULTISCALE ELECTROTHERMAL PHENOMENA" (2016). *Open Access Dissertations*. 1278. https://docs.lib.purdue.edu/open\_access\_dissertations/1278

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## **PURDUE UNIVERSITY** GRADUATE SCHOOL **Thesis/Dissertation Acceptance**

This is to certify that the thesis/dissertation prepared

| By Amirkoushyar Ziabari                                                                                                                                                                                                                   |                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Entitled Finite Element and Imaging Approaches to Analyze Multisca                                                                                                                                                                        | le Electrothermal Phenomena     |

| For the degree of Doctor of Philosophy                                                                                                                                                                                                    |                                 |

| Is approved by the final examining committee:                                                                                                                                                                                             |                                 |

| ALI SHAKOURI                                                                                                                                                                                                                              |                                 |

| CHARLES A. BOUMAN                                                                                                                                                                                                                         |                                 |

| GANESH SUBBARAYAN-SHASTRI                                                                                                                                                                                                                 |                                 |

| MARK S. LUNDSTROM                                                                                                                                                                                                                         |                                 |

| To the best of my knowledge and as understood by the student in the T Publication Delay, and Certification/Disclaimer (Graduate School Formadheres to the provisions of Purdue University's "Policy on Integrity is copyrighted material. | m 32), this thesis/dissertation |

| ALI SHAKOURI Approved by Major Professor(s):                                                                                                                                                                                              |                                 |

| Approved by: V. Balakrishnan                                                                                                                                                                                                              | 07/25/2016                      |

| Head of the Department Graduate Program                                                                                                                                                                                                   | Date                            |

## FINITE ELEMENT AND IMAGING APPROACHES TO ANALYZE MULTISCALE ELECTROTHERMAL PHENOMENA

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Amirkoushyar Ziabari

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2016

Purdue University

West Lafayette, Indiana

To My Wife, Maryam, for her indefinite kindness, patience, love, and support.

To My Parents, Sonia and Farrokh, who paved the way for me to achieve my goals.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my adviser Prof. Ali Shakouri for his constant support and encouragement. His positive attitude, flexibility, trust, and guidance helped me all along throughout my PhD and directed me to make the right decisions and advance in my research. I cannot be thankful enough for all he has done for me and hope to do something someday to make him proud of being my adviser.

I would like to express my sincere gratitude to my PhD committee, Prof. Mark Lundstrom, Prof. Charlie Bouman and Prof. Ganesh Subbarayan, for allotting the time to guide me whenever needed, and for their invaluable feedback throughout my PhD studies.

My QUEST groupmates and collaborators were not only supportive colleagues but also amazing friends without them I could not make this far. Kaz Yazawa, J.H. Bahk, J.H. Park, Bjorn Vermeersch, Xi Wang, Gilles Pernot, Kerry Maize, Yeerui Koh, Amr Mohammed, Yu Gong Wang, Alexander Shakouri, Xufeng Wang, Doosan Back, Harsha Eragamreddy, Hossein Pajouhi, Sajid Choudhurry and many other wonderful colleagues that cannot be listed in one paragraph.

The staff at Birck Nanotechnology Center at Purdue University are amazingly helpful and kind people and I really appreciate their service during my residence at Birck.

I want to thank my parents Sonia Masoumi and Farrokh Ziabari for their love and support in my entire life, and helping me finding and following this path. I would also like to thank my siblings Kavian and Kamiar, and my extended family, my in-laws, Parviz, Gita, Moti, Mina, and Ali for their support and encouragement.

Last but not least, I wish to thank my wife Maryam Parsa. I have not been able to find a word to describe how grateful I am to your unconditional love and nonpareil devotion and support. Thank you for pushing me when I needed, thank you for providing a calm and friendly environment at home so I could follow my dreams, and thank you for standing by me patiently throughout this journey.

## TABLE OF CONTENTS

|    |                                                           | Page |

|----|-----------------------------------------------------------|------|

| LI | ST OF TABLES                                              | viii |

| LI | ST OF FIGURES                                             | ix   |

| AI | BSTRACT                                                   | xii  |

| 1. | INTRODUCTION                                              | 1    |

|    | 1.1. Introduction                                         | 1    |

| 2. | POWER BLURRING IN 3D ICs INCLUDING THERMAL VIAS           | 12   |

|    | 2.1. Introduction                                         | 12   |

|    | 2.2. Power Blurring (PB) Method                           | 15   |

|    | 2.3. Power Blurring (PB) in 3D ICs including thermal vias | 23   |

|    | 2.4. Case studies results and discussion.                 | 26   |

|    | 2.5. Summary                                              | 33   |

| 3. | DESIGNING A MECHANICALLY ROBUST THERMOELECTRIC MODULE     | Ξ    |

|    | FOR HIGH TEMPERATURE APPLICATIONS                         | 35   |

|    | 3.1. Introduction                                         | 35   |

|    | 3.2. Analytical Modeling                                  | 38   |

|    | 3.2.1. Assumptions                                        | 38   |

|    | 3.2.2. Interfacial Compliance                             | 39   |

|    | 3.2.3. Shearing Stress in Two-leg TE Module               | 42   |

|    | 3.2.4. Shearing Stress in Multileg TE Module              | 45   |

|    | 3.3. Casa Studies                                         | 16   |

|    |                                                       | Page |

|----|-------------------------------------------------------|------|

|    | 3.3.1. Two-leg simplified TE Module                   | 46   |

|    | 3.3.2. Multileg High Temperature TE Module            | 53   |

|    | 3.4. Summary                                          | 62   |

| 4. | EXPERIMENTAL OBSERVATION OF CURRENT-DEPENDENT PELTIER |      |

|    | COEFFCIIENT IN LOW DOPED SEMICONDUCTORS               | 64   |

|    | 4.1. Introduction                                     | 64   |

|    | 4.2. Experimental Methodology                         | 67   |

|    | 4.2.1. Microrefrigerator Fabrication                  | 67   |

|    | 4.2.2. Electrical Characterization                    | 67   |

|    | 4.2.3. Thermal Characterization                       | 70   |

|    | 4.2.4. Results and discussions                        | 73   |

|    | 4.3. Summary                                          | 79   |

| 5. | SUBDIFFRACTION LIMIT THERMAL IMAGING                  | 81   |

|    | 5.1. Introduction                                     | 81   |

|    | 5.2. Methodologies                                    | 82   |

|    | 5.2.1. Thermoreflectance Imaging Microscopy           | 82   |

|    | 5.2.2. Nano-heater-line fabrication                   | 82   |

|    | 5.2.3. Analytical Modeling                            | 84   |

|    | 5.2.4. Finite element numerical modeling              | 85   |

|    | 5.3. Results and discussions                          | 90   |

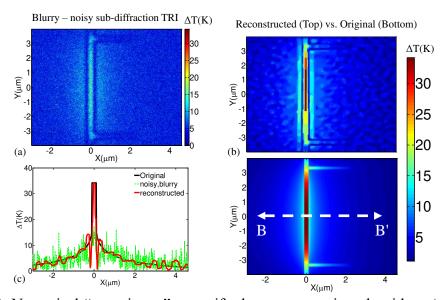

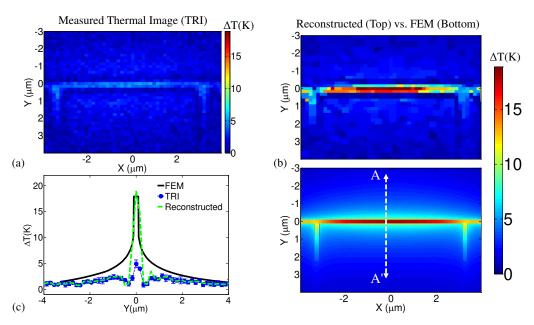

|    | 5.4. Temperature map reconstruction                   | 93   |

|    | 5.5. Summary                                          | 97   |

| 6  | STUDY OF SUBMICEON HEAT TRANSPORT IN INGAAS           | 100  |

|    | Page                                                                                                                    |

|----|-------------------------------------------------------------------------------------------------------------------------|

|    | 6.1. Introduction                                                                                                       |

|    | 6.2. Fabrication and Experimental Setup                                                                                 |

|    | 6.3. Finite Element Modeling                                                                                            |

|    | 6.4. Results and Discussions                                                                                            |

|    | 6.5. Conclusions 116                                                                                                    |

| 7. | FUTURE WORK                                                                                                             |

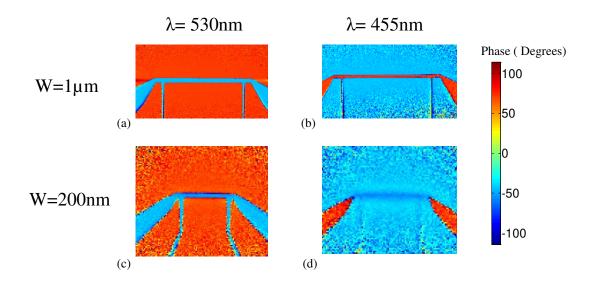

|    | 7.1. Effect of Surface Plasmonic Resonances On TR Imaging of Nanoscale devices                                          |

|    | 7.2. Sub-diffraction Thermal Imaging and Thermal Image Reconstruction for State-Of-The-Art Nanoscale Electronic Devices |

|    | 7.3. Study of Non-Local and Collective Heat Transport in Single Crystal Materials such as Silicon                       |

| LI | ST OF REFERENCES                                                                                                        |

| Αŀ | PPENDICES                                                                                                               |

| A. | Individual via vs. via region                                                                                           |

| В. | Hybrid analytical-numerical model                                                                                       |

| C. | 3ω and TDTR Techniques                                                                                                  |

| D. | Analytical Model for Nano-heater Lines on InGaAs                                                                        |

| E. | Extracted Gold properties                                                                                               |

| VI | TA146                                                                                                                   |

| L  | ST OF PURLICATIONS 147                                                                                                  |

## LIST OF TABLES

| Table                                                                             | Page |

|-----------------------------------------------------------------------------------|------|

| 2.1. Analogy Between Image Processing and Power Blurring                          | 16   |

| 2.2. Comparison between HotSpot, and Power Blurring                               | 21   |

| 2.3. Material properties and dimensions of packaged model                         | 28   |

| 2.4. Detailed Comparison between PB And ANSYS.                                    | 31   |

| 3.1. Mechanical properties of materials employed in TEM                           | 47   |

| 3.2. Material properties and dimension for the proposed TEM for high temperature. | 54   |

## LIST OF FIGURES

| Figure                                                                                  | Page |

|-----------------------------------------------------------------------------------------|------|

| 1.1. Optical image and thermal intensity overlay of a GaN HEMT device                   | 11   |

| 2.1. A typical 3D stacking with thermal vias.                                           | 14   |

| 2.2. The thermal mask                                                                   | 17   |

| 2.3. Method of Image.                                                                   | 18   |

| 2.4. The floorplan and power map for steady-state case study                            | 21   |

| 2.5. Schematic overview of power blurring transient thermal simulation                  | 23   |

| 2.6. A Schematic diagram of heat flow in a two-layer 3D IC chip                         | 24   |

| 2.7. Algorithm for PB in 3D ICs with thermal vias.                                      | 25   |

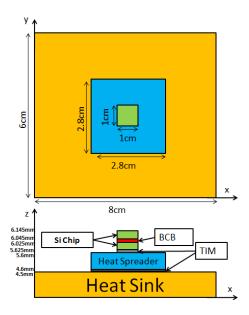

| 2.8. Schematic of a packaged 3D IC chip                                                 |      |

| 2.9. Top view of the meshed package IC structure                                        | 28   |

| 2.10. Power dissipation maps                                                            | 29   |

| 2.11. Temperature map                                                                   | 30   |

| 2.12. Comparison between temperature profiles along chip diagonal                       | 31   |

| 2.13. Comparison between temperature profiles between PB results in 3D ICs with ar      |      |

| without implementation of thermal vias.                                                 | 32   |

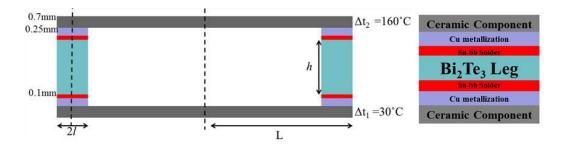

| 3.1. Thermo-electric Module;                                                            | 37   |

| 3.2. Interfacial compliance in a stipe.                                                 | 41   |

| 3.3. Thermo-Electric Module 2D structure                                                |      |

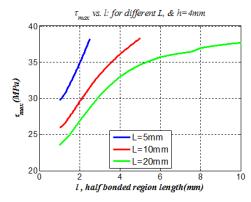

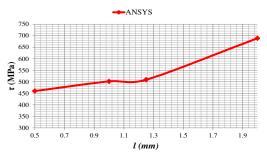

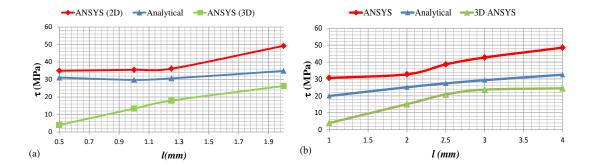

| 3.4. Variation of maximum interfacial shear stress (\taumax) vs bonded region's length. | 48   |

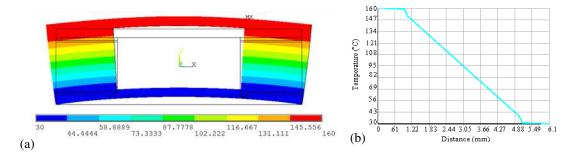

| 3.5. Thermoelectric Module deformed shape due to high temperature                       | 48   |

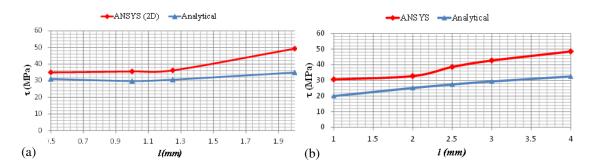

| 3.6. Maximum interfacial shear stress against TE leg length (ANSYS vs Analytical).      |      |

| 3.7. Maximum interfacial shear stress.                                                  | 50   |

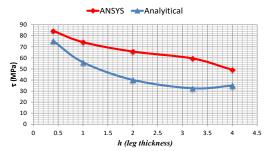

| 3.8. Maximum interfacial shear stress ANSYS vs Analytical for different thicknesses.    | 50   |

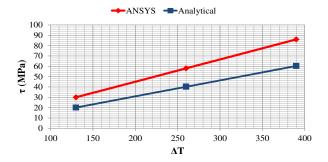

| 3.9. Maximum interfacial shear stress vs. top and bottom components temperature         |      |

| difference (ANSYS vs Analytical)                                                        | 51   |

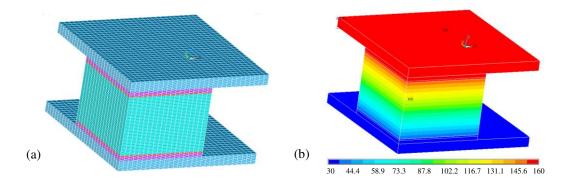

| 3.10. 3D Modeling ANSYS.                                                                |      |

| 3.11. Comparison between Analytical results with 3D and 2D ANSYS results                | 53   |

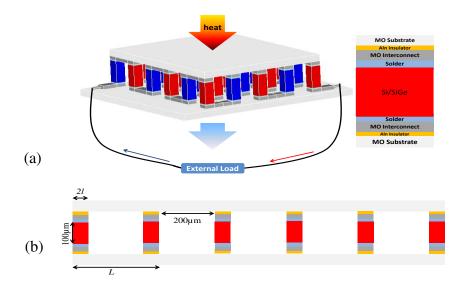

| 3.12. Multileg TE module structure.                                                     | 54   |

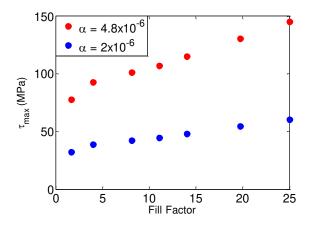

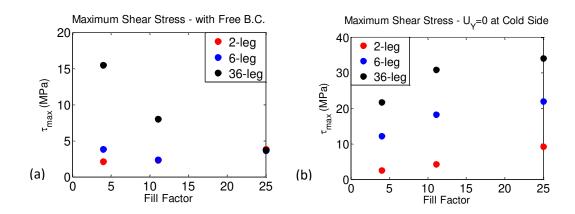

| 3.13. Analytical modeling result for maximum shear stress as a function of fill factor  |      |

| variations of α                                                                         |      |

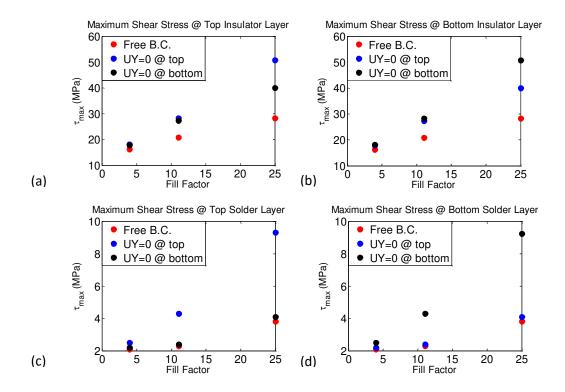

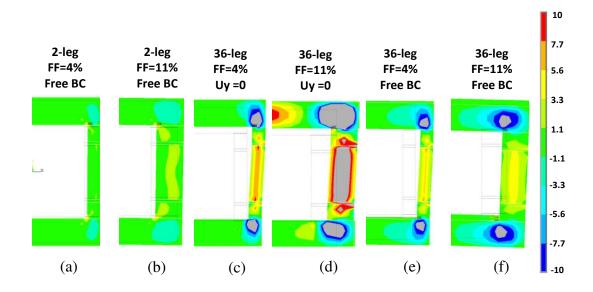

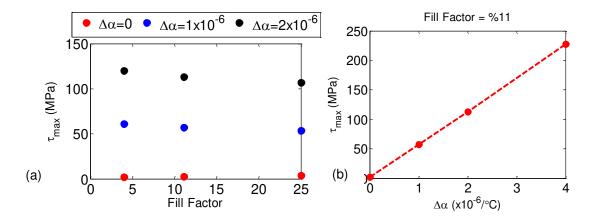

| 3.14. Maximum shear stress against fill factor for three different boundary conditions  | 58   |

| 3.15. Maximum shear stress at the interconnect/solder interface against Fill Factor for |      |

| three different structures considering different boundary conditions                    | 59   |

| 3.16. Shear stress distribution in TEM structures.                                      | 60   |

| Figure Page                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.17. Effect of CTE mismatch and Fill Factor on maximum shear stress                                                                                        |

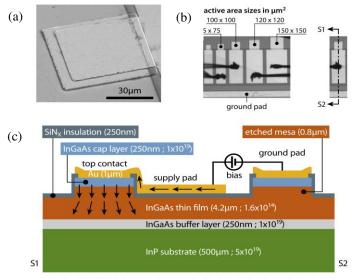

| 4.1. Nonlinear Microrefrigerators. 69                                                                                                                       |

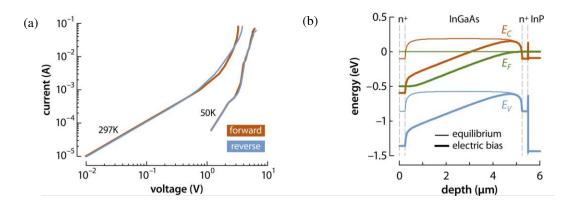

| 4.2. I-V characteristic and band diagram of the microrefrigerators                                                                                          |

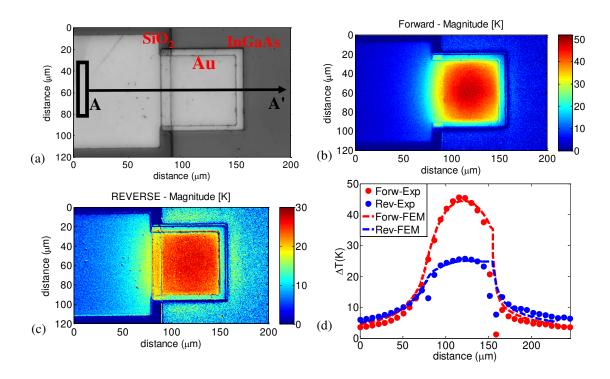

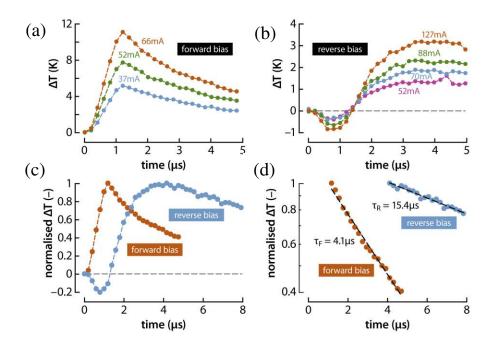

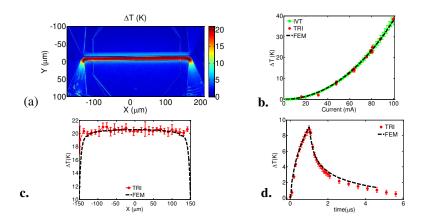

| 4.3. Thermal Imaging of Microrefrigerators                                                                                                                  |

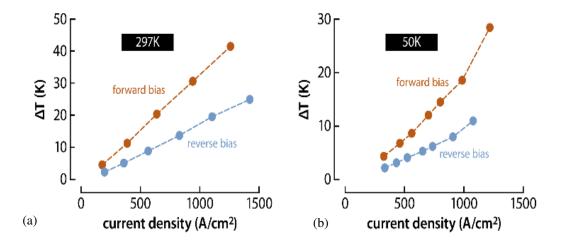

| 4.4. Average temperature change at the top surface of 75×75μm2 device under forward                                                                         |

| (red) and reverse (blue) polarities vs current density (A/cm2)                                                                                              |

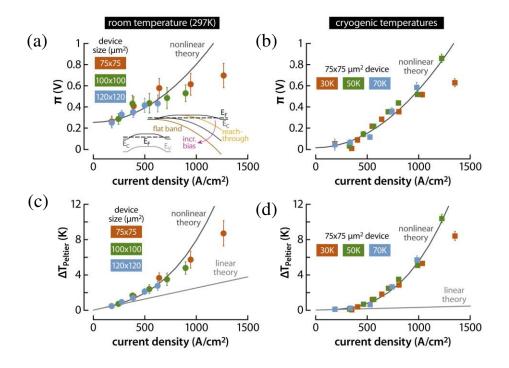

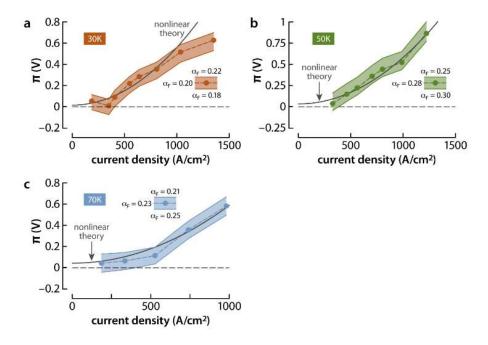

| 4.5. Nonlinear Peltier coefficient and cooling at room and cryogenic temperatures 78                                                                        |

| 4.6. Transient response of a nonlinear microrefrigerator                                                                                                    |

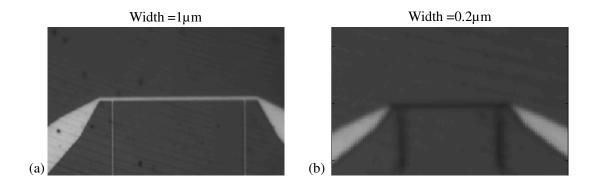

| 5.1. Optical CCD images of nanoheaters lines                                                                                                                |

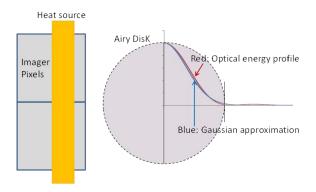

| 5.2. Schematic of heat source 100 nm wide, imager pixel 300×300 nm2, Airy disk ~ 1.3                                                                        |

| μm (if N=1)                                                                                                                                                 |

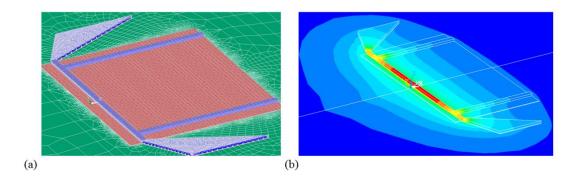

| 5.3. ANSYS modeling of nanoheaters lines                                                                                                                    |

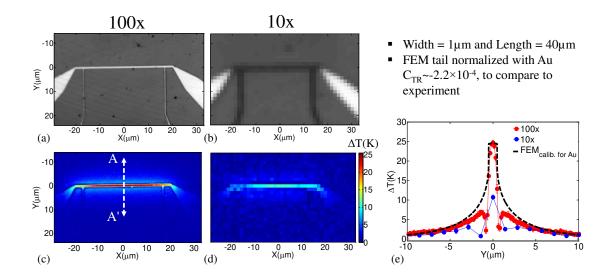

| 5.4. Optical and thermal image of 1µm heater line with different objective lenses. CCD                                                                      |

| images under (a) 100x, and (b) 10x, objective lenses                                                                                                        |

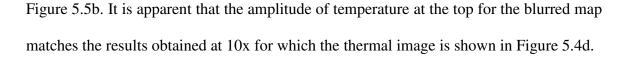

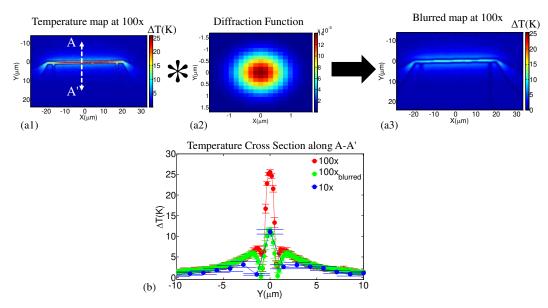

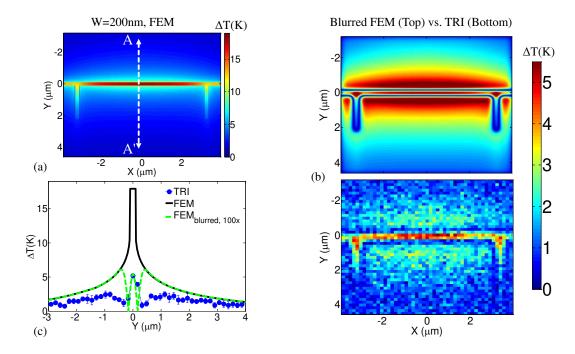

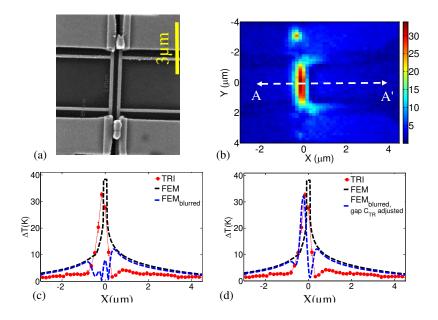

| 5.6. Comparison between TR Imaging, FEM and Image Blurring Cross sections                                                                                   |

| 5.7. Comparison between TR Imaging, and Blurred FEM Temperature profile                                                                                     |

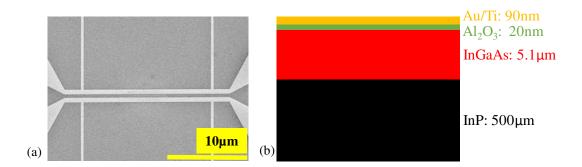

| 6.1. Nanoheater lines device structure.                                                                                                                     |

| 6.2. Thermoreflectance thermal imaging (TRI) and IVT results for 10µm wide heater line                                                                      |

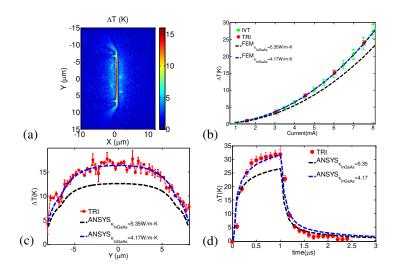

| 6.3. Thermoreflectance thermal imaging (TRI) and IVT results for 400nm heater line. 110                                                                     |

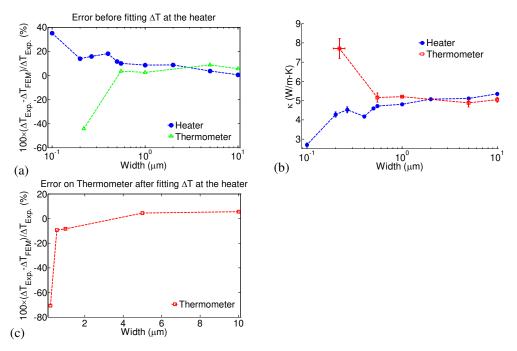

| 6.4. Differences between temperature changes obtained from the Fourier diffusive model and the experimental temperatures and corresponding Apparent Thermal |

| Conductivities to fit the temperature at the heater and the thermometer                                                                                     |

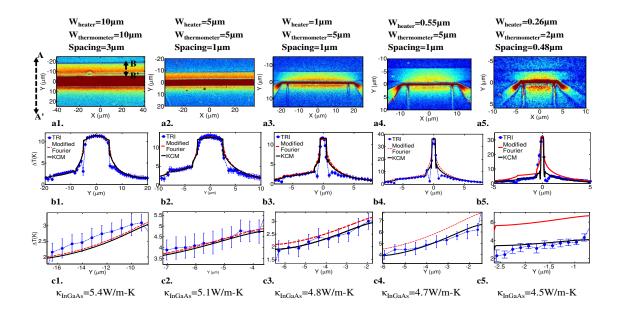

| 6.5. Experimental 2D temperature profiles on top of the heater line, thermometer line and the substrate.                                                    |

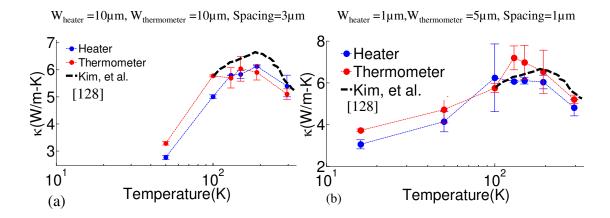

| 6.6. Temperature dependent thermal conductivity of InGaAs                                                                                                   |

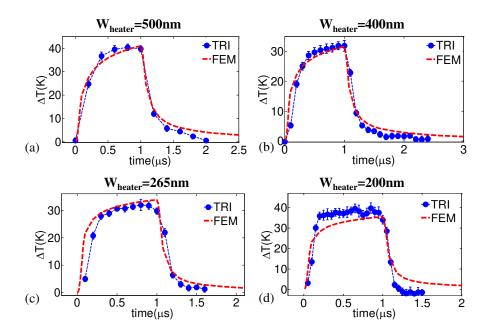

| 6.7. Deviations between Fourier diffusive model and the experimental transient                                                                              |

| temperature response. 116                                                                                                                                   |

| 7.1. Thermal imaging of two 160nm heater lines that are spaced 284nm apart from each                                                                        |

| other119                                                                                                                                                    |

| 7.2. Change in sign of CTR due to the size of metal line at certain wavelengths 120                                                                         |

| Appendix Figure                                                                                                                                             |

| A.1. Schematic of a packaged 3D IC chip                                                                                                                     |

| A.2. A schematic from top view of the chip                                                                                                                  |

| A.3. Power maps in 3D IC                                                                                                                                    |

| A.4. Temperature profile results in different layers of the 3D IC                                                                                           |

| A.5. Comparison between temperature profiles along path A-A' for the two cases of modeling the individual vias and thermal via regions with average thermal |

| conductivity137                                                                                                                                             |

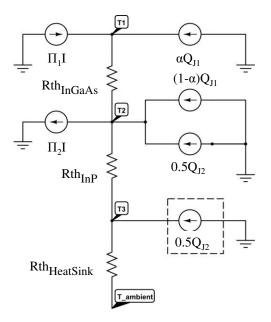

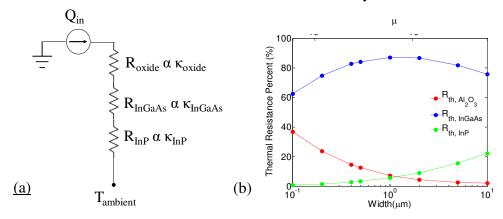

| B.1. Equivalent 1D thermal network of the nonlinear microrefrigerator                                                                                       |

| Appendix Figure                                                                    | Page |

|------------------------------------------------------------------------------------|------|

| B.2. Sensitivity of the extracted Peltier coefficient to the value of αF different |      |

| temperatures.                                                                      | 142  |

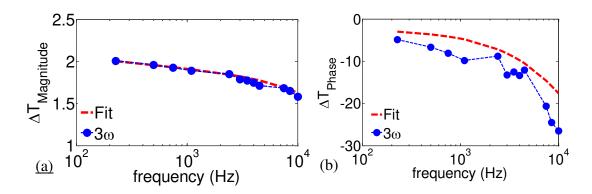

| C.1. 3\omega Magnitude and Phase for thermal conductivity extraction               |      |

| D.1. Simple analytical model for thermal conductivity estimation.                  | 144  |

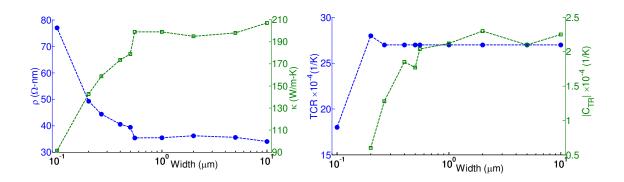

| E.1. Gold measured material properties.                                            | 145  |

#### **ABSTRACT**

Ziabari, Amirkoushyar. Ph.D. Purdue University, August 2016. Finite Element and Imaging Approaches to Analyze Multiscale Electrothermal Phenomena. Major Professor: Ali Shakouri

Electrothermal effects are crucial in the design and optimization of electronic devices. Thermoreflectance (TR) imaging enables transient thermal characterization at submicron to centimeter scales. Typically, finite element methods (FEM) are used to calculate the temperature profile in devices and ICs with complex geometry. By comparing theory and experiment, important material parameters and device characteristics are extracted. In this work we combine TR and FEM with image blurring/reconstruction techniques to improve electrothermal characterization of micron and nanoscale devices.

We present an ultrafast yet highly accurate technique, based on image blurring and FEM, for thermal modeling of 3D ICs that include thermal vias. Modeling shows the impact of thermal vias placement on the reduction of maximum temperature in different layers of 3D IC. Next, we experimentally investigate high field non-equilibrium in electron gas and its impact on thermoelectric cooling. When there is a large temperature gradient or a high current density, thermoelectric coefficients can become non-linear. We provide the first detailed experimental study of non-linear Peltier coefficient in low-doped InGaAs

semiconductor. A hybrid analytical-numerical model is developed to extract current-dependent Peltier coefficient from TR thermal images of nonlinear InGaAs microrefrigerators at room and cryogenic temperatures. Finally, we combine FEM, image deconvolution techniques and TR to accurately reconstruct thermal images of devices with spatial resolution below visible light diffraction limit. We present full thermal distribution around submicron size heat sources on InGaAs thin films on InP substrate both in steady-state and in transient regime indicating emergence of non-diffusive heat transport.

## 1. INTRODUCTION

#### 1.1. Introduction

When electrons flow through a conductor their collisions with atoms in the lattice lead to irreversible heat generation and in turn, temperature elevation. The average energy of electron gas also changes when carriers move from one conductor to another and this can lead to reversible Peltier heating and cooling. These interactions are the foundation to a class of phenomena, called electrothermal phenomena. Studying these effects has been an integral part of research in a diverse spectrum of technologies such as electronic devices and integrated circuits, thermoelectric energy conversion, phase change memory, and microelectromechanical systems (MEMS), to improve efficiency, performance, and reliability.

According to Moore's law, as the feature size of transistors shrinks, the number of transistors in integrated circuits (IC) will double approximately every two years [1]. This has resulted in a large on-chip power density, evolving hot-spots, and temperature non-uniformity across the chip. Such localized high temperatures may cause reliability phenomena such as Negative/Positive Bias Temperature Instability (NBTI/PBTI) and Time Dependent Dielectric Breakdown (TDDB), and hence accelerate the degradation of transistors. Additionally, the leakage power will increase. Leakage power is exponentially

dependent on the temperature and can degrade the performance or even cause complete circuit failure.

Three dimensional vertically integrated circuits (3D ICs) offer a promising solution to continue the CMOS performance trend in the next decade. Stacking multiple device layers in 3D ICs enables higher transistor densities and shorter interconnect lengths than planar (2D) ICs [2]. Due to an increase in the die effective area and also presence of low thermal conductivity interlayers, the power density and the thermal resistance from die to package will increase, and thus, thermal issues are expected to be a key limitation in high performance 3D ICs [3], [4]. Such electrothermal effects impose restrictions on IC designers to maintain the reliability and to deal with power management issues, requiring close collaboration between chip and package designers and electrothermal cooptimization to achieve desirable circuit performance.

Thermoelectric (TE) materials have been employed for energy conversion applications for many years. In order to increase the efficiency of TE materials, one has to enhance their figure of merit ( $ZT = \frac{S^2\sigma}{\kappa}T$ ). Enhancing ZT implies increasing electrical conductivity ( $\sigma$ ) and Seebeck coefficient (S), which are inversely related, and decreasing thermal conductivity ( $\kappa$ ). Due to their poor efficiency, TE energy conversion devices had limited niche applications. Since the early nineties, the interest towards thermoelectrics has increased significantly after it was theoretically predicated that semiconductor nanostructuring could significantly improve ZT [5]–[7]. By introducing complex structures and nanocomposites one can engineer material properties at nanoscale. Lattice thermal conductivity will be reduced by scattering phonons at the boundaries using superlattice

materials or with embedding nanoparticles distributed with periods/spacing smaller than the phonon mean free path, while electronic contribution to thermal conductivity remains unchanged; hence, the total thermal conductivity will be reduced with minimal decrease in electrical conductivity [8]–[12]. Further, through electron filtering and modification of the density of states, Seebeck and electrical conductivity can be decoupled in these nanostructures, leading to an enhancement in Seebeck effect and improved figure of merit (ZT) [12]–[14]. In addition to optimizing the material properties, integration of the TE materials into reliable, and cost-effective thermoelectric modules for application such as localized cooling of hot spots [15]–[18] and waste heat recovery [15], [19] demands a thorough optimization of device geometry and design [20]–[22]. Electrothermal effects play a crucial role in optimizing the performance of the TE materials, as well as in designing a mechanically robust TE module when taking thermally-related reliability concerns into consideration.

Numerical and analytical modeling are required to investigate electrothermal effects in semiconductor materials and devices. Due to nonlinear interactions and close correlation between power dissipation, temperature, performance and reliability, modeling is an essential element in design optimization and accurate estimation of each of these parameters. For instance, at the early stages of the IC design, electrothermal modeling plays a significant role in thermal aware design (floorplanning), placement and routing of functional blocks [3], [23], [24]. Conventionally, finite element (FE) numerical method is used to find a near exact solution to boundary value problem for the heat diffusion equation. This requires the entire domain (the device structure as well as heat spreader) to be

discretized to smaller subdomain (elements). The variational method is then used to minimize the total potential energy functional, which is a summation of the energy contribution of each individual element [25].

The accuracy of finite element method comes at the cost of increasing the mesh density of the structures. The denser the mesh, the more accurate the results and the longer the computation time. For the complex structures in planar and 3D ICs, it is impractical to use FEM for thermal aware floorplanning, and placement and routing of functional blocks in ICs. Therefore, it is necessary to develop techniques that are capable of analyzing and predicting the thermal behavior of an IC with fast computation and high accuracy. In Chapter 2, we present a fast convolution-based technique, deemed Power Blurring (PB), for static and dynamic thermal modeling of planar (2D) and 3D ICs. In particular, we emphasize thermal modeling of 3D ICs with thermal vias. The PB method will be compared against FEM in terms of accuracy and speed of computation.

In thermoelectrics (TE) applications, electrothermal modeling is critically important for material and design optimization to maximize the efficiency, and to avoid reliability issues due to the thermal stress induced fracture or delamination. Thermoelectric generators (TEGs) are emerging as a possible solution for high temperature energy conversion applications and waste heat recovery systems. The key challenges are improving the efficiency of thermoelectric power generator module (TEM) and its material cost in large scale production. A system optimization for TE waste heat recovery system and minimization of the TEM cost is presented in Ref. [20]. The closed form analytical solution reveals that the optimum solution for the maximum output power can be obtained by

thermal impedance matching with heat source and the heat sink (hot and cold reservoirs) as well as electrical impedance matching with the load. Upon finding the optimum solution, cost-performance analysis is conducted to find the minimum cost design at a given system efficiency. This optimization elucidates that the fractional area coverage of the thermoelectric (TE) leg, called fill factor (FF), plays a significant role in minimizing the mass of the TE material used in thermoelectric waste heat recovery systems. It is shown that improving the figure-of-merit (ZT) along with decreasing the fill factor would further reduce the total cost [20]. Because the maximum power output from a thermoelectric system is proportional to square of temperature difference between the hot and cold reservoirs [22], employing a thermoelectric generator with optimum design in high temperature applications and with large temperature difference, such as on top of a steam turbine cycle, will be an economical approach to increase energy production [21]. However, both reduced fill factor and higher temperature range imply a larger impact on reliability of TEMs. In Chapter 3, we employ analytical modeling and FEM to investigate the impact of lower fill factor and high temperature on thermally induced interfacial shearing stress, one of the factors responsible for mechanical stability of TE module. Additionally, we utilize FEM to study the impact of variations in the geometry, boundary conditions, and the coefficient of thermal expansion (CTE) of the materials on the maximum shearing stress, focusing on the fill factor, in a thermoelectric power generator module (TEM) designed for high temperature applications.

Akin to theoretical modeling, experimental characterization techniques are indispensable in analysis and understanding of the electrothermal effects in semiconductor materials and

devices. One has to perform thorough measurements and analysis to extract material properties and in turn estimate the performance of semiconductor devices. Moreover, electrothermal phenomena such as non-uniform current and heat distribution and consequently localized high temperature or hot spots limit the operational temperatures of semiconductor devices and may degrade their performance [26]. These effects can only be revealed by techniques that are able to measure the full spatial distribution of temperature profiles in devices.

Thermoreflectance (TR) microscopy is a noninvasive optical technique that is suitable for the 2D mapping of temperature field in active semiconductor devices [27]. TR detects a small change in the sample surface reflectivity due to a change in the temperature. The reflectivity (R) of a material is related to its temperature change ( $\Delta T$ ) through the thermoreflectance coefficient ( $C_{TR}$ ), by equation (1).

$$\frac{\Delta R}{R} = \left(\frac{1}{R}\frac{\partial R}{\partial T}\right)\Delta T = C_{TR}\Delta T \tag{1.1}$$

The magnitude of the thermoreflectance coefficient ( $C_{TR}$ ) is usually on the order of  $10^{-2}$  -  $10^{-5}$  (1/K) depending on the materials measured. This coefficient is influenced by sample composition, wavelength of probing light, and numerical aperture of the imaging system [28]. TR microscopy can be employed for both quasi-static and transient 2D temperature profiles of devices. This method is sensitive to mK temperature variations with subnanosecond temporal resolution, and can render images with submicron spatial resolution [27], [29]–[33]. In Chapter 4, we exploit TR to experimentally investigate high field non-equilibrium in electron gas and its impact on thermoelectric cooling.

Thermoelectric cooling occurs due to the Peltier effect that is the change in the average energy of electrons when current flows through an interface between two dissimilar conductors or semiconductors. When current traverses a junction between two conductors A and B, where in A the average transport energy of electrons is lower than B, electrons will absorb heat from the lattice at the junction to compensate for their lower energy and therefore cool down the junction. This is called Peltier cooling. The amount of Peltier heat carried at the junction is proportional to the applied current according to the Peltier coefficient  $\Pi$ . The Peltier coefficient is independent of the electrical current and is related to the Seebeck coefficient by the Kelvin relation,  $\Pi = S \times T$ . Using Monte-Carlo simulations, it is demonstrated that under strong electric field, electronic temperature starts to exceed the lattice temperature. This non-equilibrium electron heating leads to nonlinearity in the Peltier coefficient. It is predicted that nonlinearity is proportional to effective mass, square of current density and inversely proportional to square of the carrier concentration of the semiconductor [34]. Additionally, due to weaker electron-phonon coupling, the nonlinearity will be more prominent at lower temperatures. It is predicted that nonlinearity can be utilized to enhance thermoelectric cooling at large current densities [34].

In an effort to measure the anticipated nonlinear Peltier coefficient in low doped semiconductors and the corresponding cooling, a set of thin film InGaAs microrefrigerators is designed and fabricated. The temperature change on the top of these devices is obtained using thermoreflectance thermal imaging at different current densities. Exploiting TR thermal imaging results and the four-point probe electrical characterization, at room and

cryogenic temperatures (30-70K), along with a hybrid analytical-numerical model, we extract the reversible non-linear Peltier coefficient at different current densities and separate it from irreversible non-linear Joule heating in the device. In chapter 4, we describe the methodology and present the extracted Peltier coefficient. We also discuss how this will affect the amount of the Peltier cooling/heating and in turn the performance of microrefrigerator devices at room and cryogenic temperatures.

Exploring electrothermal effects at nanoscale is critical for many current and future applications of nanostructures. Reducing the size of devices to the nanoscale and engineering the nanoscale material properties is used to enhance the performance of the ICs and TE materials and devices. At smaller dimensions comparable to electron or phonon mean free paths in the materials, the charge and heat transport cannot be treated based on classical diffusive model and their non-diffusive behavior needs to be considered. It has been predicted and shown that Fourier diffusion equation fails to explain the thermal behavior [35]–[38]. Nonlocal and nonequilibrium effects due to phonons carrying heat ballistically away from the heat source are the main cause of the departure from the Fourier law. In such a non-equilibrium condition at nanoscale, where assumptions of continuum and second law of thermodynamic may not hold, questions emerge concerning the definition of temperature and its measurements. To answer the question "whether we are able to define temperature at the nanometer scale?", Hartman et. al. analyzed a harmonic chain of quantum particles with next neighbor interactions and found minimum length scales at which the local temperature can be defined at different ambient temperatures [39], [40]. About 0.1m at 1K and 100nm at 680K are the minimum length scale predicted for 1D

silicon atoms. Although these numbers seem to be oddly large, this may only be due to the 1D nature of their calculations and ignoring phonon scattering events. Nevertheless, their approach captures the essential physics and can be a path toward finding more accurate estimation models. In the cases where local equilibrium assumption is no longer valid, then one needs to modify the equilibrium concepts such as entropy to be able to define temperature in non-equilibrium situations. Such approaches, e.g. Extended Irreversible Thermodynamics (EIT), are discussed in the review done by Vazquez et. al. [41] and more Experimental investigations using laser based Time Domain recently in [42]. Thermoreflectance (TDTR) [43]–[47] and Frequency Domain Thermoreflectance (FDTR) [48] techniques, using Coherent Soft X-ray beams [49], as well as using  $2\omega/3\omega$  electrical measurement [50], have probed the non-diffusive thermal transport in semiconductor materials and alloys. In these experiments, a heat source such as a laser source or Joule heating due to current flow through a metal heater are used to heat up the substance under study. Because of the fast electron-electron interactions in the metal transducer, the sensor temperature can often be defined unambiguously. An important question is to relate temperature variation of the sensor to the "energy" transport in the crystal and if a unique temperature could be defined for various phonon modes. When the size of the heat source is large, phonons emitted from the heat source go through a random walk, scatter, change the equilibrium entropy of the system and therefore temperature change in a classical sense can be defined. Reducing the size of the heat source or increasing the modulation frequency result in quasiballistic phonon transport in which some of the phonons maybe in nonequilibrium (e.g. ballistic transport of long mfp phonons in Si [45]) while others scatter and dissipate energy which translate to change in the non-equilibrium entropy of the system and therefore translate into the temperature. In an alternative explanation, long jumps are intermingled with short random walks in a Lévy flight picture which does not require introducing different temperature for ballistic and diffusive model (see [46]).

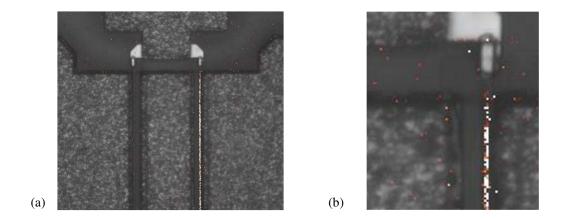

To truly understand the physics behind the heat transport at nanoscale, and to investigate various theories described in aforementioned references, versatile thermal characterization technique with high thermal, spatial and temporal resolution is necessary. TR spectroscopy is proven useful for 2D mapping of thermal effects at nanoscale and qualitative elucidation of physical phenomenon at small scales [51]-[53]. TR is employed to create 2D temperature map of electrically biased single crystalline VO<sub>2</sub> nanobeams, and to observe strongly localized alternating Peltier heating and cooling as well as Joule heating at the Metal-Insulator domain boundaries [51]. Furthermore, the technique is used to observe super-Joule self-heating at the transport bottlenecks in networks of silver nanowires and silver nanowire/single layer graphene hybrid films [52]. Figure 1.1 shows the optical images of a GaN HEMT device with 0.1 micron wide gate metal under 20x and 100x objective lens magnification with overlay of thermal intensity obtained by TR microscopy when one of the two parallel gates is biased [54]. Although, illumination with visible wavelengths enables TR to have a high spatial resolution compared to methods such as IR thermal imaging, the optical diffraction still limits accurate quantitative temperature profiles in devices with feature sizes below Rayleigh resolution criterion [55]. In Chapter 5, we first describe why TR thermal imaging is capable of acquiring the thermal images below diffraction limit despite the fact that the optical images are obscured at those scales.

Then, we combine FEM, image processing, and TR thermal imaging to accurately reconstruct thermal images of devices at scales below diffraction limit. We present a maximum *a posteriori* (MAP) framework [56], using Markov Random Field priors [57], to reconstruct true thermal images from the diffraction-limited ones. Reconstruction is performed both on *numerically-designed experiments* and true thermal images. Independent measurements to verify the results are performed. In Chapter 6, we present TR imaging results to study nanoscale heat transport in heater lines fabricated on InGaAs semiconductor alloys, and to examine superdiffusive heat transport model presented in Refs [46], [58]. Room and cryogenic temperature measurements were performed at both steady-state and transient regimes. Signatures of non-diffusive heat transport are observed and analyzed in these measurements. In Chapter 7, we provide some proposals for future prospect and continuation of the research presented in this dissertation.

Figure 1.1. Optical image and thermal intensity overlay of a GaN HEMT device. The magnifications are (a) 20x and (b) 100x. The gate length is  $35 \mu m$ . The top surface gate contact is approximately  $150 \mu m$  wide and the gaps to the drain and source contacts are approximately  $400 \mu m$  and  $200 \mu m$ , respectively.

### 2. POWER BLURRING IN 3D ICs INCLUDING THERMAL VIAS

### 2.1. Introduction

In recent years, the scaling of supply voltage has departed from the ideal scaling predicted by Moore [59] and Dennard et al. [60]. The threshold voltage ( $V_{th}$ ) has stopped scaling. This in turn has stopped the scaling of supply voltage ( $V_{dd}$ ) to maintain circuit performance. This results in higher power densities, which promotes temperature as one of the primary design parameters as the scaling advances to smaller feature sizes. In addition, non-uniform activities in an IC chip yield non-uniform surface temperature distributions, since localized heating occurs much faster than chip-wide heating [61]. Thus the temperature of certain regions can become much higher than that in the neighboring areas. These higher temperature regions are called hot spots. Hot spots and spatial temperature gradients in VLSI ICs have become critical issues due to their limiting effects on both the performance and the reliability of packaged IC chips[62].

Moreover, the increasing leakage power and its exponential dependence on the temperature require more attention to thermal-aware simulations and optimizations. Hence, precise estimation of temperature distribution is essential for accurate analysis of performance, reliability, and power management. Generally, thermal simulations and design optimizations are done under steady-state worst-case conditions due to the high computational cost, causing reliance on the use of conservative margins in thermal designs.

However, the temperature non- uniformity evolves over time and thus hot spots are of spatio- temporal nature. The transient temperature spike or localized heating also can cause timing errors, non-uniform current flow or reliability failures. As the thermal budget becomes increasingly tight, the worst-case approach becomes too costly and ineffective. It is also known that the simulated worst-case peak power and its corresponding peak temperature are rarely observed [26], [61].

Even with the state-of-the-art tools, the chip-level transient thermal simulation with a realistic package configuration is too costly for physical design optimization or performance verification in the packaged environment. In addition, in the early stages of chip design, i.e. architectural specification stage, specific package information and thermal boundary conditions may not be available. At these stages, designers rely on simulation to consider the trade-offs. However, slow simulation limits the scope of analysis. For these reasons, a fast transient thermal analysis method is highly desired [63].

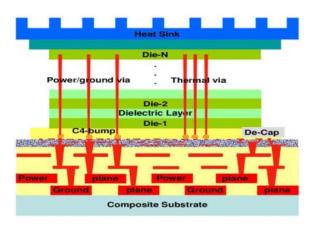

Three dimensional vertically integrated ICs (3D ICs) offer a promising solution to continue the CMOS performance trend in the next decade. Stacking multiple device layers in 3D ICs enables realizing higher transistor densities and shorter interconnect lengths than two-dimensional (2D) ICs [2]. Due to increase in the die effective area and, in turn, the power density and thermal resistance, thermal issues are expected to be a key limitation in high performance 3D ICs. This prompted the IC designers to incorporate electrical vias into the 3D ICs to lower the interconnect length between device layers. Since vias are good thermal conductors as well, placing "thermal vias" between device layers and heat sink is effective to lower the temperature [64]. Figure 2.1 shows a typical 3D stacking of multiple active

layers inside a single package. "Thermal vias" can be inserted to remove heat from bottom device layers to the heat sink while "power/ground vias" are used to carry power supply between active layers [64].

As a result of thermal challenges such as temperature non-uniformity, thermal-aware design has become an essential aspect of 3D IC design. Accurate estimation of the temperature profile in each active layer is very important. For example, the need for fast thermal analysis is indisputable in placement and routing of active blocks and/or thermal vias in 3D ICs [65].

Figure 2.1. A typical 3D stacking with thermal vias [64].

In the reminder of this chapter, we present a fast, yet accurate steady-state and transient temperature computation method suitable for VLSI planar (2D) and 3D ICs in packages. In order to validate the new method, called Power Blurring (PB), simulation results are compared to those of a Finite Element Analysis obtained by ANSYS [66]. The main emphasis is on 3D ICs including thermal vias. In section 2.2 we describe the Power

Blurring methodology for fast static and transient thermal modeling in ICs. In Section 2.3, we present the algorithm for Power Blurring in 3D IC including thermal vias followed by case study results and discussion.

## 2.2.Power Blurring (PB) Method

To obtain the temperature profile in a chip, the heat diffusion equation shown in Equation (2.1) has to be solved with appropriate boundary conditions

$$k\frac{\partial^2 T}{\partial x^2} + k\frac{\partial^2 T}{\partial y^2} + k\frac{\partial^2 T}{\partial z^2} + q^* = \rho c_p \frac{\partial T}{\partial t}$$

(2.1)

where k is the thermal conductivity (W/m·K),  $\rho$  is the density (kg/m³), and  $c_p$  is the specific heat (J/kg·K),  $q^*$  is the heat generation per unit volume (W/m³), and T is the temperature of the location (x, y, z) at time t. In 3D IC thermal analysis, the heat diffusion equation has been conventionally handled by grid-based methods, such as Finite Difference Method (FDM) or Finite Element Method (FEM), which generate 3D volumetric meshes of solid structure. The accuracy of these FDM and FEM methods comes at the price of long execution times, and exhaustive CPU and memory usage. A matrix convolution technique, called *Power Blurring (PB)*, has been developed to expedite the computation of temperature distribution in IC chips. This PB method has its theoretical basis on the Green's function method [67], [68]. Implementation is similar to image blurring used for image processing.

Equations (2.2) and (2.3) govern the Green's function method and its equivalent implementation in PB, respectively. In (2.2),  $G(\rho, \rho')$  is the Green's function, and V' is the volume over which the heat, q(x', y', z'), is generated.

$$\Delta T = \iiint G(\rho, \rho') q(x', y', z') dV'$$

(2.2)

Thus the Green's function (response to a delta-function excitation) is a building block to construct the solution.

In image processing, an image is blurred by a convolution with a filter mask. The filter mask is a matrix whose elements define a process in which the modification (i.e. blurring) of an image occurs. For instance, an image, f, is convoluted with a filter mask, w, to produce a blurred image g by the Equation (2.3).

$$g(x,y) = \sum_{s=-a}^{a} \sum_{t=-b}^{b} w(s,t) f(x+s,y+t)$$

(2.3)

where a=(m-1)/2 and b=(n-1)/2 for a  $m \times n$  mask [56].

In thermal analysis, if we think of the power map as an image, f, the resulting temperature profile can be regarded as a blurred image, g, where the filter mask, w, corresponds to the thermal mask.

Table 2.1 summarizes the analogy between the image blurring and the PB methods.

TABLE 2.1. ANALOGY BETWEEN IMAGE PROCESSING AND POWER BLURRING.

| Image Processing  | Power Blurring          |  |

|-------------------|-------------------------|--|

| Image (f)         | Power Map               |  |

| Filter Mask (w)   | <b>Impulse Response</b> |  |

| Blurred Image (g) | Temperature Profile     |  |

As mentioned earlier, thermal mask is the impulse response of the system in space domain. According to the Green's function method, we can build a solution to a partial differential equation with an arbitrary driving function once we have a solution corresponding to an impulse (a point source). In thermal analysis of IC chips, temperature distribution is the physical quantity of interest, and heat (i.e. power consumption in ICs) is the driving

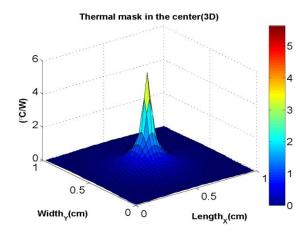

function. Thus, the thermal mask conforms to a steady-state temperature distribution induced by a point heat source which is applied to the center of the Si die. In practice, the die area is discretized into grids and an approximate delta function simulating a point heat source is applied to the center element of the grid. Subsequently, the difference between the resulting temperature and ambient temperature is normalized with the amount of the input power. Although the thermal mask can be obtained in analytical form for a simple 1D geometry, measurement or 3D finite element analysis (FEA) simulator is needed for a realistic structure shown in Figure 2.2, where 3D heat spreading in the package is important. Figure 2.3 shows the thermal mask for a given package model. Its unit is that of thermal resistance (°C/W), and hence the thermal mask generates a temperature profile when it is convoluted with a power distribution map (W).

Figure 2.2. The thermal mask; the surface of the Si die is discretized into 40×40 grids.

The shape of the thermal mask depends on the location of the point heat source. Method of images is developed to avoid necessity of obtaining thermal mask at different locations of

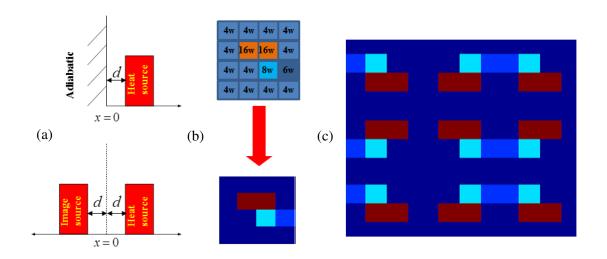

the chip. The principle of the method of image for power blurring is similar to Method of Image in electromagnetism [69]. Consider the case of a heat source located at a distance, d, from an adiabatic surface as shown in Figure 2.3a. No heat transfer can occur at the adiabatic boundary. This means the net outgoing heat flux at x = 0 and x = L is zero. If we replace the adiabatic boundary with an image source, the adiabatic boundary condition is satisfied. The problem then becomes more manageable with this approach. One need to convolve the extended power map with the thermal mask, obtained at the center, to calculate the temperature profile rather than using different thermal masks at edges, center and corner of the chip.

Figure 2.3. Method of Image. (a) Method of Image. (b) An arbitrary power map on Si die. (c) Power map with its eight nearest neighbor mirror images.

The extended power map can be calculated from equation (2.4).

$$P_{image} = [P(x,y) + P(x,-y) + P(-x,y) + P(x,2W-y) + P(-x,-y) + P(-x,2W-y) + P(2L-x,y) + P(2L-x,2W-y)]$$

$$(2.4)$$

Here,  $P_{\text{image}}$  is the extended power map, P is the power map, and W and L are the width and the length of the power map, respectively.  $P_{\text{image}}$  extends from (-W, -L) to (2W, 2L) which is 9 times larger than P. For final calculation of temperature profile two third of this matrix is only needed.

The direct convolution result is given by

$$T_{DCMI}(x, y) = h(x, y) * [P_{image}(-\frac{L}{2}; \frac{3L}{2}, -\frac{W}{2}; \frac{3W}{2})]$$

(2.5)

where, T is the thermal profile, and h is the thermal mask shown in Figure 2.2. This is called Direct Convolution with Method of Image (DCMI). DCMI does not handle the 3D heat spreading at the boundary properly. Another error reduction step is added, which is called intrinsic error reduction, in which the results obtained by DCMI will be normalized by the intrinsic error between FEM and DCMI response to a uniform heat source [70]. Intrinsic error can be calculated from equation (2.6), in which  $T_{DCMI\_Uniform}$  and  $T_{ANSYS\_Uniform}$  are responses of DCMI method and ANSYS FEM to uniform heat source on top of the die.

$$E_r = (T_{DCMI\_Uniform} - T_{ANSYS\_Uniform}) / T_{ANSYS\_Uniform}$$

(2.6)

The final temperature for an arbitrary thermal map can be calculated from equation (2.7).

$$T_{final} = \frac{T_{DCMI}}{1 + E_r} + T_{ambient} \tag{2.7}$$

Where T<sub>ambient</sub> is the ambient temperature around the package.

It should be pointed out that although calculating thermal mask and intrinsic error require FEM, these calculations need to be done once offline for the package and used in a convolution algorithm for thermal management and thermal aware floorplanning in ICs with arbitrary power dissipation profile.

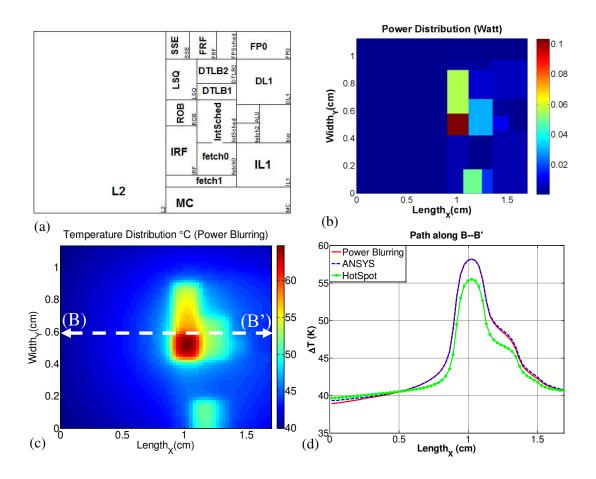

A case study for temperature profile calculation using power blurring in an AMD Bobcat mobile processor model is shown in Figure 2.4. Figures 2.4a, and 2.4b, show the floorplan and the 2D power dissipation map for this processor. Figure 2.4c, shows the temperature profile obtained by power blurring. In Figure 2.4d, we compared power blurring results along vertical cross section with ANSYS and HotSpot thermal simulator [71]. HotSpot is a widely used thermal simulator in computer architecture community, and similar to other architectural level simulators, is designed to calculate temperature profiles which are accurate for the experiments at the architecture level (block sizes in tens of micro to millimeter range), and still fast enough to allow for the simulation of long dynamic temperature traces on the order of seconds. HotSpot is based on an equivalent circuit of thermal resistances and capacitances that correspond to the microarchitecture blocks. The essential aspects of the thermal package are also taken into account. In Table 2.2. a comparison in terms of accuracy and speed between PB, and HotSpot is carried out.

Figure 2.4. The floorplan and power map for steady-state case study. (a) The floorplan of the device; (b) A typical mobile processor model power map; (c) Temperature profile obtained by Power Blurring (PB); (d) Comparison between PB, ANSYS [66] and HotSpot [71] along B-B'.

Table 2.2. Comparison between HotSpot, and Power Blurring.

| Computation Time         56s         0.11s         0.041s           Err. in hot-spot         -         12.9%         0.14%           Avg. Err         -         6.5%         2.5% |                  | ANSYS | HotSpot  | PB        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|----------|-----------|

| •                                                                                                                                                                                 | Computation Time | 56s   | 0.11s    | 0.041s    |

| Avg. Err - 6.5% 2.5%                                                                                                                                                              | Err. in hot-spot | -     | 12.9%    | 0.14%     |

|                                                                                                                                                                                   | Avg. Err         | 1     | 6.5%     | 2.5%      |

| Abs. Err. range - 0-4.2 °C 0- 0.56 °C                                                                                                                                             | Abs. Err. range  | -     | 0-4.2 °C | 0- 0.56°C |

An adaptive power blurring technique is developed in [72] which can solve non-linear problems, e.g. when the thermal conductivity of the silicon is modified based on the local

temperature of the chip, using two or three iterations. Excellent agreements with selfconsistent finite element simulations have been obtained.

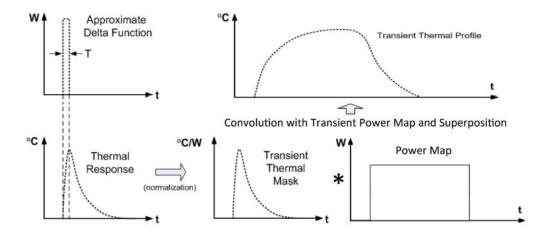

PB further extended so that it can be applied for transient thermal simulations [70]. The difference is that the time evolution of the thermal mask resulting from spatiotemporal impulse is employed for the transient simulation. To obtain an impulse response in the time domain, a delta function needs to be applied to the center of the die. In practice, a point heat source is applied for a very short time period (approximate delta function), and the corresponding thermal response is recorded at each time step, which is shorter than the width of the approximate delta function. The width of the delta function is determined by the desired level of temporal resolution. The resulting thermal responses are normalized with respect to the amount of applied power. The series of thermal masks acquired at the end of this procedure constitutes a transient thermal mask (i.e. time evolution of the thermal mask). Once the transient thermal mask is prepared, the transient temperature profile is obtained by means of the superposition principle. A schematic overview of the transient thermal simulation process is presented in Figure 2.5. Three orders of magnitude and 28 times speed up compared to FEM and HotSpot simulator are shown, respectively, for a sample transient power dissipation map [70], [73].

Figure 2.5. Schematic overview of power blurring transient thermal simulation.

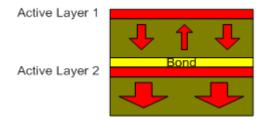

#### 2.3. Power Blurring (PB) in 3D ICs including thermal vias

We extended PB for thermal modeling in 3D ICs. In this case the temperature profile in each active layer is not only due to heat dissipated in that layer but also due to its neighboring active layers. Therefore, the coupling between neighboring layers must be considered. This is shown in Figure 2.6. In order to take this coupling into account, for e.g. a two layers chip, two thermal masks will be needed for each active layer. The first one is the temperature rise in the layer as a result a applying a point heat source in it and the second one is the temperature rise in its neighboring layer as a result of the same point heat source.

Figure 2.6. A Schematic diagram of heat flow in a two-layer 3D IC chip. Heat sink (not drawn) is on the bottom surface [74].

After obtaining thermal masks for each die, in a two-layer 3D IC, the following equations are used to calculate each layer's temperature profile:

$$T_1 = Mask_{11} * P_1 + Mask_{12} * P_2$$

and  $T_2 = Mask_{21} * P_1 + Mask_{22} * P_2$  (2.8)

where  $P_1$  and  $P_2$  represent the power maps of layers 1 and 2, respectively.

For 3D ICs when there are thermal vias, the temperature distribution profile is significantly affected since a uniform silicon chip is not dominating heat spreading. One needs to calculate heat spreading in both silicon chip and the thermal via regions. We introduce two thermal masks: *Si thermal mask* and *via thermal mask*. Instead of convolving the entire power maps with the Si thermal masks, we need to convolve each element of power map with the appropriate thermal mask.

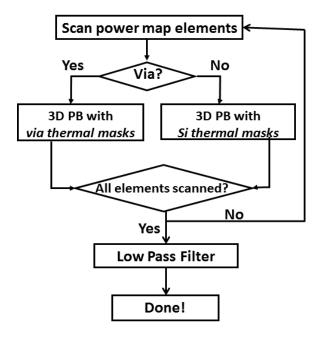

Figure 2.7. Algorithm for PB in 3D ICs with thermal vias.

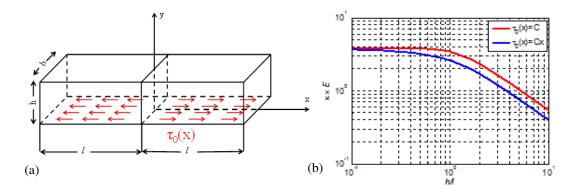

The algorithm for PB in 3D ICs with thermal vias is shown in Figure 2.7. As it can be seen in this new method we should scan all the meshed elements and calculate the temperature profile at each element based on material properties of that element. Each meshed element in the power dissipation profile will be convolved with the appropriate thermal masks, i.e. Si thermal mask or via thermal mask, to calculate the temperature in that element. After temperature values over the entire chip are obtained then a low pass filter is used to smooth out the temperature profile at the edges of Si and via for each layer (this avoids using an additional thermal mask at the boundary between silicon and thermal via).

The significance of this method over the conventional FEA is in that, once the thermal masks for a geometry are calculated then for any power dissipation profile in each layer, the temperature profile can quickly be obtained and there is no need to re-mesh the entire

geometry. Also, comparing the method to 3D power blurring, we are now able to incorporate any non-uniformity in the chip which can be due to thermal vias, or even chip with different material properties in different regions. In the next section the results obtained for a case study and compared with ANSYS.

#### 2.4. Case studies results and discussion

In the following case studies, we will follow the idea proposed in [65], in which the thermal vias are placed in designated regions called thermal via regions, and their density is adjusted with minimal perturbation on routing. The thermal conductivity of each of the regions is determined by the density of thermal vias in that region.

Performing full-chip thermal analysis at the granularity of individual thermal vias is unreasonable, because it will lead to very large matrix sizes in both FEA and Power Blurring. Therefore, it is necessary to find a way to alleviate computation complexity. In Appendix A.1., we illustrated that instead of modeling individual vias we can model the via region with the weighted average value of thermal conductivity of via material and the oxide.

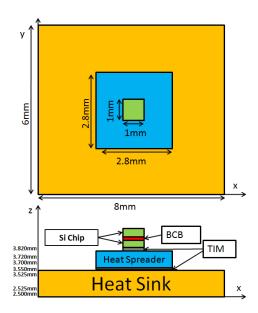

Figure 2.8 shows the full chip thermal model. Material parameters and dimensions are summarized in Table 2.3. The configuration consists of two Si ICs with surface areas of 1cm×1cm and a Cu heat sink with a heat spreading layer. Thermal interface material (TIM) reduces the effect of surface roughness on the contact area, and hence improves heat conduction at the interface. Assuming flip chip package, most of the heat is considered to flow through the bottom surface of the heat sink, and other minor heat transfer paths are

neglected. Heat transfer coefficient of 0.15W/cm<sup>2</sup>-K is employed for the bottom surface of the copper heat sink and adiabatic boundary condition is imposed on other surfaces. 3D IC technology is an emerging technology and bonding process technologies are still being developed. In this study, we assumed bonding approach of adhesive polymer BCB (Benzocyclobutene) and "face-to-back" bonding. 10% of the die area is dedicated to 16 thermal via regions.

Figure 2.8. Schematic of a packaged 3D IC chip, where the heat spreader, the heat sink and the thermal interface material (TIM) are included (Thermal via regions are shown in Figure 2.9).

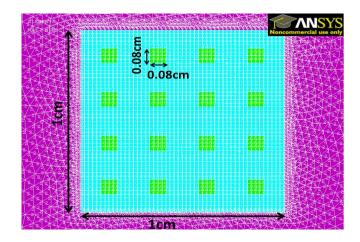

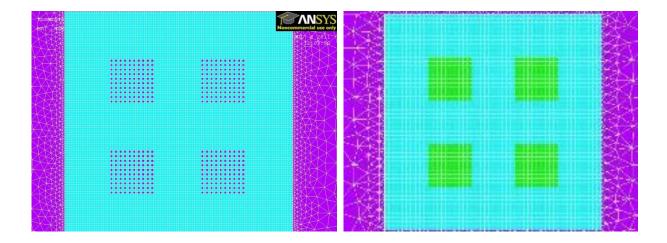

In Figure 2.9, a schematic of top view of top silicon die and the thermal via regions are shown. We assumed the density of thermal via in each region is 50% which leads to 5% of the entire die. The area is meshed by 200 $\mu$ m element size (50×50 grids).

Figure 2.9. Top view of the meshed package IC structure. Thermal via regions are shown with green color in the figure  $(0.08 \times 0.08 \text{cm}^2)$ . Cyan is the Si die, and purple is the heat spreader.

Table 2.3. Material properties and dimensions of packaged model.

|           | Area<br>(mm²) | Thickness (mm) | Thermal<br>Conductivity | Density (kg/m³) | Specific<br>Heat |

|-----------|---------------|----------------|-------------------------|-----------------|------------------|

|           |               |                | (W/m-K)                 |                 | (J/kg-K)         |

| Si Die 1  | 10×10         | 0.2            | 148                     | 2330            | 700              |

| BCB       | 10×10         | 0.02           | 0.2                     | 1051            | 2187             |

| Si Die 2  | 10×10         | 0.5            | 117.5                   | 2330            | 700              |

| TIM1      | 10×10         | 0.025          | 5.91                    | 1930            | 15               |

| Heat      | 28×28         | 1              | 395                     | 8933            | 397              |

| Spreader  |               |                |                         |                 |                  |

| TIM2      | 28×28         | 0.1            | 3.5                     | 1100            | 1050             |

| Heat Sink | 60×80         | 4.5            | 395                     | 8933            | 397              |

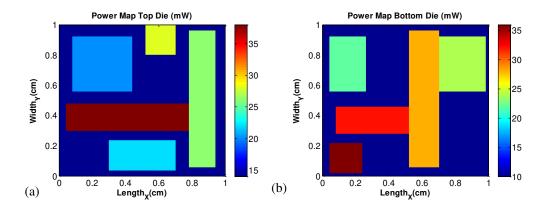

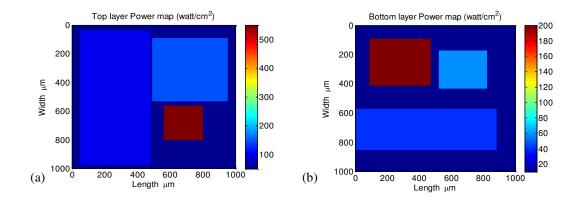

The power dissipation profiles in the top and bottom active layers are shown in Figure 2.10a and Figure 2.10b, respectively.

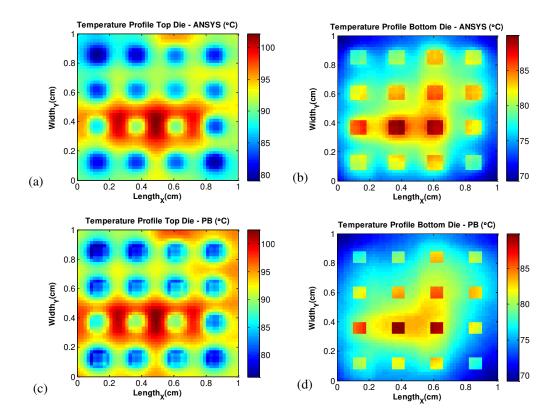

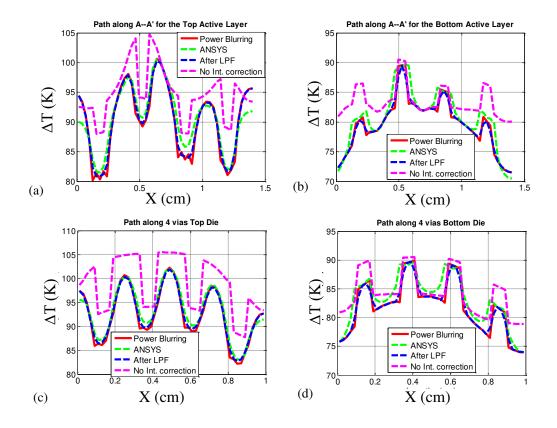

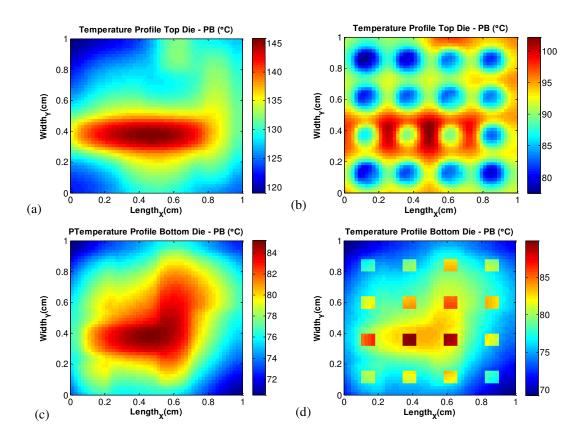

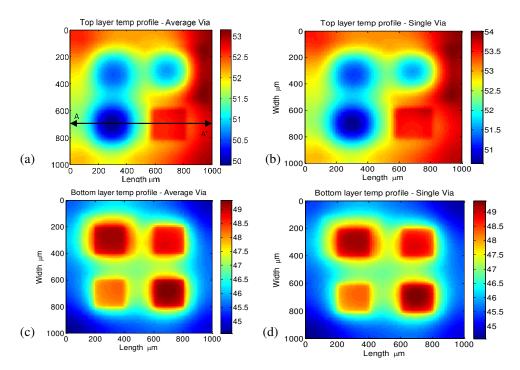

Figure 2.10. Power dissipation maps at the, (a) top active layer, (b) bottom active layer. The temperature calculations using ANSYS and PB are shown in Figure 2.11. For the case of PB, it is important to include corrections using the method of images and also the intrinsic error compensation due to the heat spreading in larger heat sink in the package. In Figure 2.12, a comparison between these temperature profiles along the diagonal of the chip and also along the second row of the vias are presented. Filtered and non-filtered results are both shown and compared with ANSYS results. The significance of including intrinsic error compensation step, is also indicated in this figure. For this case study, including intrinsic error compensation in each layer lead to up to 10% less error in final temperature profiles. The relative temperature error and also computation times are presented in Table 2.4. PB results are obtained 76 times faster than ANSYS. The maximum error of 12% in the entire temperature profile relative to ANSYS is due to temperature difference of less than 2.3 degree (81.2-78.9), which happens at the boundary between via region and the Si chip.

Figure 2.11. Temperature map, ANSYS (a) top, and (b) bottom active layer. Temperature map, PB (c) top, and (d) bottom active layer.

Figure 2.12. Comparison between temperature profiles along chip diagonal at the (a) top, and (b) bottom active layers. Comparison along 2nd row vias (c) top, and (d) bottom active layers.

Table 2.4. Detailed Comparison between PB and ANSYS.

|                       | ANSYS | PB (Top) | PB (Bottom) |

|-----------------------|-------|----------|-------------|

| Max Err.              | -     | 7.98%    | 12.14%      |

| Err. In hottest spot  | -     | 0.023%   | 0.58%       |

| <b>Execution time</b> | 91.1s | 1.2s     | -           |

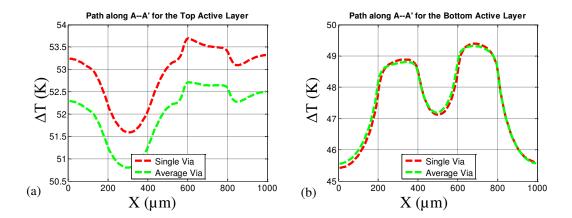

Influence of implementing thermal via into 3D ICs is presented in Figure 2.13. Inclusion of thermal via regions resulted in ~%30 reduction in the maximum temperature at the top surface (Figure 2.13a and 2.13b). However, at the bottom surface and at the bottom of

thermal vias, temperature will increase (Figure 2.13c and 2.13d). This means thermal vias facilitate heat transport from the top die to the package, but because of limitation in spreading at the bottom junction, localized temperature will increase. Thermoelectric modules for localized solid-state cooling at the bottom of thermal vias is a possible solution to resolve this issue.

Figure 2.13. Comparison between temperature profiles between PB results in 3D ICs with and without implementation of thermal vias. Temperature profile at the top: (a) with via, and (b) without vias. Temperature profile at the bottom (c) with via, and (d) without vias.

#### 2.5. Summary

The demands for efficient thermal simulation for VLSI ICs in a thermal package as well as power electronic and optoelectronic devices have risen as the CMOS technology scales down and power densities escalates. In this work, we presented a highly accurate yet fast thermal simulation method, namely Power Blurring (PB). We demonstrated that the PB method is suitable for both static and transient thermal simulations, while, unlike the conventional Green's function based methods, realistic package models can be incorporated. PB is able to solve nonlinear problems (calculating temperature profiles in ICs considering temperature dependence of material properties of the chip) using only two or three iterations. Moreover, the power blurring method is used to estimate the temperature profile in 3D ICs which include thermal vias. The method is validated against FEM (ANSYS), and the results are obtained 76x faster, while the error at the hot spot was less than %0.6. Power Blurring is able to incorporate any non-uniformity in the chip which can be due to thermal vias, or even chip with different material properties in different regions. This advantage becomes more prominent when one considers the fact that every FEA method need to re-mesh and recalculate the temperature profiles for new power distribution profiles while in the case of PB once the thermal masks for a given geometry are obtained, then for any power map the temperature profile can quickly be obtained. In particular, this is very beneficial at the early stage of IC design for placement and routing of the thermal via regions and functional blocks. Obtaining temperature profiles by performing convolution at each meshed element, based on material properties in that element, is another new idea that is used. This will increase the accuracy of resulted

temperature profile and versatility of power blurring at the expense of losing a bit of speed.

The latter can be easily compensated by using a lower level programming (e.g. C) and with the use of dedicated graphical processing units (GPUs).

# 3. DESIGNING A MECHANICALLY ROBUST THERMOELECTRIC MODULE FOR HIGH TEMPERATURE APPLICATIONS

#### 3.1.Introduction

For every unit of energy that is converted into electricity, more than one or two units of energy are not used in power plants today. This excess energy is primarily wasted as heat – or thermal energy. Deploying systems to recover this wasted heat back into the energy stream is a wide spread topic of research. Thermoelectric generators (TEGs) are emerging as a possible solution for high temperature energy conversion applications and waste heat recovery systems. The key challenges are improving the efficiency of thermoelectric power generator module (TEM) and its material cost in large scale production.

A system optimization for TE waste heat recovery system and minimization of the TEM cost is presented in [20]. The closed form analytical solution reveals that the optimum solution for the maximum output power can be obtained by both electrical and thermal impedance matching and together with their heat source and the heat sink (hot and cold reservoirs). Upon finding the optimum solution, cost-performance analysis is conducted to find the minimum cost design at a given system efficiency. This optimization elucidates that the fractional area coverage of the thermoelectric (TE) leg, called fill factor or *FF*, plays a significant role in minimizing the mass of the TE material used in thermoelectric waste heat recovery systems.

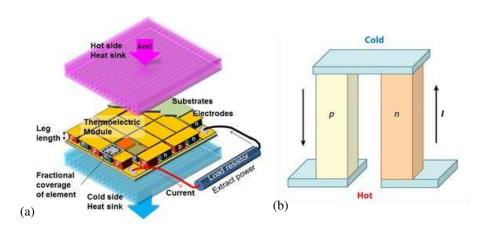

It is shown in [20] that improving the figure-of-merit (*ZT*) along with decreasing the fill factor would further reduce the total cost. Because the maximum power output from a thermoelectric system is proportional to square of temperature difference between the hot and cold reservoirs [75], employing a thermoelectric generator with optimum design in high temperature applications and with large temperature difference, such as on top of a steam turbine cycle, will be an economical approach to increase energy production [21]. However, both reduced fill factor and higher temperature range imply a larger impact on thermo-mechanical reliability. Elevated thermal stresses are viewed today as major bottlenecks for reliability and robustness in high temperature TEM applications. These stresses are caused, first of all, by the significant differences in temperature between the "hot" and the "cold" ceramic plates in a TEM design (Figure 3.1). The thermal stress problem can be solved by selecting adequate thermoelectric materials [76], [77] as well as by finding effective ways to reduce the stress level [78].

In this Chapter, an analytical and a finite-element-analysis (FEA) models are used to evaluate the thermal stresses in a simplified (two-leg) TEM design. We will demonstrate that, in the case of simplified TEM, by reducing fill factor as well as using compliant interface materials, one can reduce the maximum shearing stress occurring at the contacts. The maximum shear stresses are supposedly responsible for the structural robustness of the TEM assembly [78]. It should be pointed out, that reduction of the maximum shear stress by decreasing fill factor is not universal and it depends on other parameters, such as the coefficients of thermal expansion (CTEs) of the different layers and the structural boundary conditions for the TEM assembly. Therefore, we exploit finite element analysis to study

how the geometry, structural boundary conditions, and the CTE of the materials in the TEM structure would change the maximum shear stress particularly in a high temperature application.

Figure 3.1. Thermo-electric Module; (a) General view; (b) A two leg module with n-type and p-type legs.