# Flexible Cryo-Packages for Josephson Devices

Charles J. Burroughs, Samuel P. Benz, Paul D. Dresselhaus, Yonuk Chong, and Hirotake Yamamori

Abstract—We have developed a method of bonding superconductive integrated-circuit chips to interchangeable, microwave-compatible, flexible cryo-packages. This "flip-chip on flex" technology will greatly improve the service life and reliability of our Josephson systems because the present press-contacts to the chip are replaced with directly soldered connections. The new method eliminates the most common failure mode for our Josephson chips, which has been the degradation and variation of the contact resistances of the chip pads due to mechanical wear upon repeated thermal cycles from 4°K to room temperature. The superior microwave properties of this packaging provide improved operating margins for our devices. We have demonstrated the reliability of the bonds with repeated thermal cycling for 100% operational chips with 40 connections (67 410 Josephson junctions).

*Index Terms*—Chip bonding, cryo-packaging, Josephson arrays, Josephson voltage standard.

#### I. INTRODUCTION

When the developed a new packaging technology for our superconductive Josephson devices in which we directly solder our chips to flexible carriers. The primary design considerations for these cryo-packages are long service life, improved microwave performance, and stable, reliable chip-to-carrier contacts. For the past 10 years [1], we have been designing and fabricating a variety of circuits based upon superconductor—normal metal—superconductor (SNS) Josephson junctions including chips for programmable Josephson voltages standards (PJVS) [2]–[4], pulse-driven Josephson arbitrary waveform synthesizers (JAWS) [5], and Johnson noise thermometry (JNT) [6]. Recent efforts have been focused upon increasing the operating margins and long-term reliability of these devices so that they may be used for many years in their respective applications.

Traditionally, our cryoprobes at NIST have been based upon printed circuit boards with beryllium-copper spring-fingers that connect to the chip. This technology is convenient for research and development since the chips can be mounted or removed from the cryoprobe in seconds. The probes allow us to test many chips per day, but they are not a viable long-term package because the chip pads become mechanically worn over time, which eventually degrades the contacts. Furthermore, most of our circuits are used in high-accuracy voltage metrology applications where worn contacts with nonlinear behavior or a few

Manuscript received October 4, 2004. NIST is part of the Technology Administration of the U.S. Department of Commerce.

Digital Object Identifier 10.1109/TASC.2005.849876

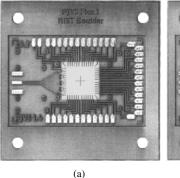

Fig. 1. Two flexible carriers prior to chip solder bonding. The flex are manufactured side by side as illustrated, on panels containing 12 to 20 individual circuits. These two flexes are used for PJVS chips, and they illustrate two different microwave launch structures: (a) has a wide 70° microstrip splitter, and (b) has a narrow 35° microstrip splitter.

ohms of resistance can be a source of small but unacceptable errors including thermal voltages, rf-induced dc-offsets, output waveform distortion, and biasing inaccuracies due to unpredictable contact resistances. In fact, when routinely used chips exhibit reduced performance or become difficult to operate, the cause of the problem has generally been mechanically worn contact pads on the chip. We are able to determine that the problem occurs at the interface between the chip-pad and spring-finger because the four-wire measurement configuration of our circuits allows us to make isolated measurements of the individual contacts.

To resolve the contact issue, we have developed a "flip-chip on flex" method of permanently bonding our chips to a flexible cryo-package. This technology has a number of advantages over our traditional packaging including long-term stability of the contact electrical properties, high reliability with repeated thermal cycling, and superior microwave properties that improve chip operating margins and signal bandwidth.

## II. FLEX BONDING PROCEDURE

The procedure for bonding our chips to flexible cryo-packages has been streamlined into a few simple steps, starting with preparation of the flexible carrier (which we will refer to as simply the *flex* throughout this paper). Fig. 1 shows a typical flex consisting of a 250  $\mu$ m thick sheet of microwave-compatible dielectric with 50  $\mu$ m thick copper wiring layers on both sides, plated-through vias, and four precisely located 3 mm holes that mechanically align the flex to the chip when mounted in our custom-built bonding machine. The copper wiring contacts to the chip have a finished width of 250  $\mu$ m. The flex has a solder mask covering its entire surface except over the area to be occupied by the chip and the pads around the edge of the flex where

C. J. Burroughs, S. P. Benz, P. D. Dresselhaus, and Y. Chong are with the National Institute of Standards and Technology, Boulder, CO 80305 USA (e-mail: burroughs@boulder.nist.gov).

H. Yamamori is with the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, 305-8568, Japan.

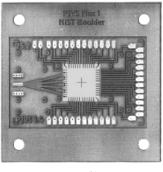

Fig. 2. The bonding head of the custom-built bonding machine with (a) the chip installed on the heater block (in the alignment pocket that positions the chip from all four sides), and (b) with the bonding head fully assembled and the flex aligned face down in contact with the chip, ready to solder the bonds.

copper wires and microwave connectors are installed. Immediately prior to bonding, we apply InSn solder (52% indium, 48% tin) to the flex contacts by dipping the front surface of the flex into a solder bath at 140°C for a few seconds. We use a liquid flux for this process to ensure quick and uniform wetting of the solder. The back-side of the flex is also masked to prevent solder from flowing onto the back-side ground plane.

The next step in the bonding process is the most important one—inspection and touch-up of the InSn bumps under a 10X magnifying lens. The solder bumps must be the proper size on every flex contact even though each chip design uses several different types of contacts including microwave center conductors, plated-through vias to back-side ground, and dc connections. To ensure 100% yield of the bonds, a few flex contacts usually need to have a little solder added using InSn solder paste or removed with a tiny scalpel. This manual step is necessary because the solder bath dip procedure does not provide perfectly uniform solder bumps and because the flex contacts all have slightly different areas. Although this step requires user intervention and oversight, it is still the method of choice because other techniques (such as solder paste using a template) are presently tedious and time consuming for these small contacts. The pads on the chip do not require preparation because their top surface is palladium-gold, which is readily wetted by the solder.

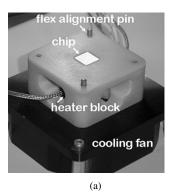

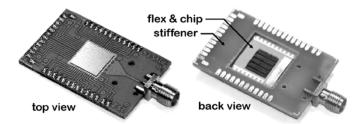

Once the flex is prepared, the procedure to bond the chip is quick and straightforward. The chip is installed face-up on the heater block of the bonding machine as shown in Fig. (2a), where an alignment pocket precisely holds the chip in place from all four sides. A liquid flux is applied to the face of the chip, and the flex is immediately installed face down on top of the chip using the 3 mm diameter pins for precision alignment. Finally, as illustrated in Fig. (2b), the remaining mechanical pieces are installed over the flex that apply a reproducible, adjustable force that presses the flex into contact with the chip. An automatic heating cycle is initiated to ramp the heater temperature to 140°C where it holds for a few seconds and subsequently cools down to room temperature in about a minute. After bonding, the chips are tested at room temperature to verify chip-to-flex continuity. Then the flex is epoxy-bonded to a "stiffener" frame to make the flex rigid where the microwave launches and copper wiring will be soldered. The final package is illustrated in Fig. 3.

Fig. 3. Completed "flip-chip on flex" cyro-package including an SMA connector to the 4-way microstrip splitter, 40 front-side pads for attaching copper wires for dc biases, and a back-side stiffener frame under all soldered regions around the perimeter of the flex.

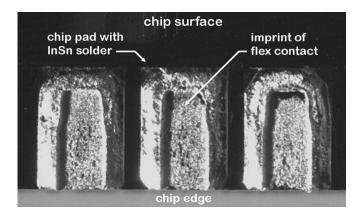

Fig. 4. Photograph of the solder bonds on the chip pads, after the flex has been peeled away. The imprint of the flex contact is clearly visible, as is the 50  $\mu m$  of solder that was between the chip pad and the flex contact.

The custom-built bonding machine provides a quick and convenient way to permanently solder our chips to flex with a minimum amount of heat applied to the chip, while precisely aligning the flex contacts to the chip pads (typically within  $\pm 25~\mu \mathrm{m}$ ). Since the solder bonding process is quick and at a relatively low temperature, we measure no changes to the chip maximum current capacity, SNS junction parameters, or critical currents.

### III. FLEX BOND ANALYSIS

To date, we have bonded a number of different Josephson chips to flex with a variety of chip-pad and flex-contact configurations. The strongest bonds produced so far are for the 40-pad PJVS circuit of Fig. 1. In this case we carefully control the final shape of the solder bonds by making the chip pads wider than the flex contacts by 50  $\mu m$  to 75  $\mu m$  per side, and by confirming that the proper amount of solder has been applied to each flex contact. We also install height adjustment shims under the bonder alignment plate to mechanically prevent the pressure of the flex on the chip from squeezing all of the solder out of the contacts. This technique creates a small "pocket" of InSn on each chip pad in which the flex contact sits, and there is a measurable layer of InSn (about 50  $\mu$ m) remaining between each chip pad and flex contact. Fig. 4 shows the flex-contact imprint in the remaining solder of a flex-bonded chip pad; the flex was deliberately peeled apart from the chip for inspection. These InSn bonds on our PJVS chips are very strong and withstand numerous thermal cycles as well as stress tests where the cryopackage is warmed and cooled to liquid helium temperature in 10 seconds.

| TABLE I                                         |

|-------------------------------------------------|

| CHIP OPERATING MARGINS BEFORE AND AFTER BONDING |

| Cell<br>Number | Number<br>of<br>Josephson | Current<br>Margin (mA)<br>using | Current<br>Margin (mA)<br>using Flex | Percentage<br>Improvement<br>due to Flex |

|----------------|---------------------------|---------------------------------|--------------------------------------|------------------------------------------|

|                | Junctions                 | Spring-Fingers                  | Cryopackage                          | Cryopackage                              |

| 1              | 8800                      | 1.86                            | 3.21                                 | 73%                                      |

| 2              | 8800                      | 1.69                            | 2.99                                 | 77%                                      |

| 3              | 8798                      | 1.97                            | 3.30                                 | 68%                                      |

| 4              | 8800                      | 1.78                            | 2.96                                 | 67%                                      |

| 5              | 8796                      | 1.81                            | 2.92                                 | 61%                                      |

| 6              | 8800                      | 1.82                            | 2.99                                 | 64%                                      |

| 7              | 8792                      | 1.69                            | 2.94                                 | 74%                                      |

| 8              | 3888                      | 1.72                            | 3.78                                 | 120%                                     |

| 9              | 1296                      | 1.60                            | 3.29                                 | 106%                                     |

| 10             | 16                        | 2.27                            | 3.94                                 | 73%                                      |

| 11             | 48                        | 2.09                            | 4.33                                 | 107%                                     |

| 12             | 144                       | 2.31                            | 4.37                                 | 89%                                      |

| 13             | 432                       | 2.08                            | 4.44                                 | 113%                                     |

These data are for a 2.6 Volt PJVS chip measured in our standard coplanar spring-finger cryoprobe (before bonding), and then measured again after being permanently bonded to a flexible cryopackage. In both cases the applied microwave frequency was 18.5 GHz and the microwave power level was optimized so that the output step height for the entire chip was approximately the same for the zero and positive current steps.

## IV. MEASUREMENT RESULTS

The "flip-chip on flex" technology not only solves our problem with long-term contact reliability, but it also produces considerable improvement in operating margins for our PJVS chips. This improvement is most likely due to the excellent microwave characteristics of the flex and its ability to implement compact microstrip splitters and launches with precisely controlled dimensions. Table I shows the operating margins for all thirteen Josephson-array segments of a 2.6 Volt PJVS chip [7]. The chip was measured first in our traditional coplanar spring-finger probe, and then under the same conditions after flex-bonding. These data are for a microwave drive frequency of 18.5 GHz and are representative of the typical improvement in operating current range that we have observed for many similar chips. In this case, the largest array cells show significantly improved operating margins, 61% to 77% larger current range, over which the output voltage exhibits the required flatness.

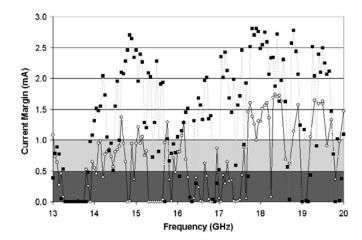

We have measured two different microstrip splitters on flex to determine which type works best for our PJVS application. Both splitters are four-way circular-sector-shaped power dividers [8] designed with a radius of 7 mm for an optimum center frequency of 16 GHz. In the first design, shown in Fig. (1a), we placed the four-way structure as close to the chip as possible, which requires a fairly wide 70° arc sector and the four launches to the chip to be oriented 20° apart. The data for this configuration, shown in Fig. 5, are of the operating current margin for an entire PJVS chip (all 67 410 junctions simultaneously) when it was measured in a coplanar probe, and then again after flex-bonding. At most frequencies, the measured current margin is significantly better using the flex package, and in some cases the margin on flex is two to three times larger.

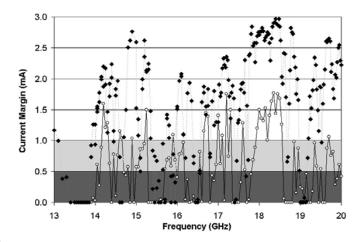

The second design is also a four-way splitter, but elongated so that the four transmission lines to the chip are spaced as closely as possible, every  $10^{\circ}$ . This design uses a narrow  $35^{\circ}$  arc sector,

Fig. 5. Operating-current margin of a 2.6 Volt PJVS chip using all segments. Data points with open circles were measured in a coplanar spring-finger probe, and solid points correspond to the same chip on flex with a "wide 70° arc sector" microstrip splitter. Data in the shaded region below 0.5 mA are considered too small and unusable. The best region for chip operation is where the current margin is 1 mA or larger, and 78% of the data points for the flex package fall in that region compared to only 33% for the coplanar package.

Fig. 6. Operating-current margin of a 2.6 Volt PJVS chip using all segments. Data points with open circles were measured in a coplanar spring-finger probe, and solid points correspond to the same chip on flex with a "narrow 30° arc sector" microstrip splitter. Data in the shaded region below 0.5 mA are considered too small and unusable. The best region for chip operation is where the current margin is 1 mA or larger, and 74% of the data points for the flex package fall in that region compared to only 27% for the coplanar package.

as depicted in Fig. (1b), and the measured data for this geometry (using a different chip of course) are presented in Fig. 6. From 14 GHz to 20 GHz, it is clear that both flex designs work significantly better than our traditional coplanar spring-finger package. The measured operating ranges for both flex packages are much larger than those observed for the coplanar springfinger package, which suggests that the flex packages provide better microwave uniformity delivered to the 8800 junctions in each Josephson array. The improved performance is largely due to the fact that the flex dielectric properties allow us to implement our microwave splitters and launches as microstrip (instead of coplanar waveguide), resulting in structures with five times shorter length, better impedance control, and a backside ground under the entire structure. More flex packages need to be measured to elucidate any significant differences between the two different flex designs.

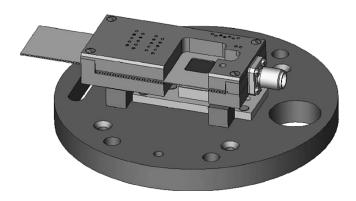

Fig. 7. Interchangeable module for flex-mounted chips. This version mounts on a cryocooler, and a nearly identical version has been created for operation in liquid helium.

One interesting similarity between Figs. 5 and 6 is the region between 17.7 GHz and 18.5 GHz, where the chip works perfectly over the entire frequency range for both flex-bonded packages. We believe that this behavior is a characteristic of the chip itself, and in most applications this is the range where we choose to operate.

#### V. CONCLUSION

Our "flip-chip on flex" technology has demonstrated dramatic improvements in the performance of our superconductive chips in terms of contact reliability and microwave uniformity. We expect to apply this technology in many other applications where our chips will benefit from improved operating margins and increased service-life. In related developments, Fig. 7 shows an interchangeable carrier for the flexes that connects to them securely without the requirement of a back-side stiffener. This configuration allows flex-mounted chips to be conveniently installed and removed in seconds, and can be mounted directly to a cryocooler or utilized in a traditional liquid helium cryoprobe.

This cryopackage has been designed and manufactured, but has not yet been tested on real devices.

#### ACKNOWLEDGMENT

The authors would like to thank J. Plantenberg for his contribution to the early stages of this work in the measurement and analysis of microwave dielectric materials and low-temperature solders. The authors would also like to thank the Astro Endyne Company (Boulder, CO) for fabricating the flexible carriers, and High Precision Devices Inc. (Boulder, CO) for producing the flex-bonding machine, precision flex-panel machining, and collaboration on the development of the bonding procedure.

## REFERENCES

- S. P. Benz and C. A. Hamilton, "Application of the Josephson effect to voltage metrology," *Proc. IEEE*, vol. 92, no. 10, pp. 1617–1629, Oct. 2004

- [2] S. P. Benz, C. A. Hamilton, C. J. Burroughs, T. E. Harvey, and L. A. Christian, "Stable 1-volt programmable voltage standard," *Appl. Phys. Lett.*, vol. 71, pp. 1866–1868, Sep. 1997.

- [3] C. J. Burroughs, S. P. Benz, T. E. Harvey, and C. A. Hamilton, "1 volt dc programmable voltage standard system," *IEEE Trans. Appl. Supercond.*, vol. 9, pp. 4145–4149, Jun. 1999.

- [4] Y. Chong, C. J. Burroughs, P. D. Dresselhaus, N. Hadacek, H. Yamamori, and S. P. Benz, "Practical high-resolution programmable Josephson voltage standards using double- and triple-stacked MoSi<sub>2</sub>-barrier junctions," in this publication.

- [5] S. P. Benz, C. J. Burroughs, and P. D. Dresselhaus, "AC coupling technique for Josephson waveform synthesis," *IEEE Trans. Appl. Supercond.*, vol. 11, pp. 612–616, Jun. 2001.

- [6] S. P. Benz, P. D. Dresselhaus, and J. Martinis, "An ac Josephson source for Johnson noise thermometry," *IEEE Trans. Instrum. Meas.*, vol. 52, no. 2, pp. 545–549, Apr. 2003.

- [7] Y. Chong, C. J. Burroughs, P. D. Dresselhaus, N. Hadacek, H. Yamamori, and S. P. Benz, "2.6 V high-resolution programmable Josephson voltage standard circuits using double-stacked MoSi<sub>2</sub>-barrier junctions," *IEEE Trans. Instrum. Meas.*, vol. 54, no. 2, Apr. 2005.

- [8] M. D. Abouzahra and K. C. Gupta, "Multiport power divider-combiner circuits using circular-sector-shaped planar components," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 12, pp. 1747–1750, Dec. 1988.