# **UCLA**

# **UCLA Previously Published Works**

# **Title**

Flexible Hybrid Electronics Technology Using Die-First FOWLP for High-Performance and Scalable Heterogeneous System Integration

# **Permalink**

https://escholarship.org/uc/item/157262mx

# **Authors**

Fukushima, Takafumi Alam, Arsalan Hanna, Amir <u>et al.</u>

# **Publication Date**

2018-10-01

Peer reviewed

# Flexible Hybrid Electronics Technology Using Die-First FOWLP for High-Performance and Scalable Heterogeneous System Integration

Takafumi Fukushima, *Member, IEEE*, Arsalan Alam, Amir Hanna, Siva Chandra Jangam, Adeel Bajwa, and Subramanian S. Iyer, *Fellow, IEEE*

Abstract— A technological platform is established for scalable flexible hybrid electronics (FHE) based on a novel fan-out wafer level packaging (FOWLP) methodology. Small dielets are embedded in flexible substrates we call FlexTrate<sup>TM</sup>. These dielets can be interconnected through high-density wirings formed in wafer-level processing. We demonstrate homogeneous integration of 625 (25 by 25) 1-mm-sqaure Si dielets and heterogeneous integration of GaAs and Si dielets with various thicknesses in a biocompatible polydimethylsiloxane (PDMS). In this work, die-to-die interconnections are successfully implemented over a stress buffer layer (SBL) formed on the PDMS. In addition, coplanarity between the PDMS and embedded dielets, die shift concerned in typical die-first FOWLP, and the bendability of the resulting FlexTrate<sup>TM</sup> are characterized.

*Index Terms*—flexible substrate, high-density interconnect, heterogeneous integration, Fan-Out Wafer-level Packaging (FOWLP), Polydimethylsiloxane (PDMS), and flexible hybrid electronics (FHE).

#### I. INTRODUCTION

n the past decades, flexible device works can be mainly divided into three categories: the first one is the use of organic semiconductors that are deposited on flexible substrates in sheet-level processing or roll-to-roll processing [1]-[3]. The second strategy utilizes Thin-Film Transistor (TFT) fabrication on flexible substrates [4][5]. The third approaches rely on transfer technologies that can allow the integration of an extremely-thin monocrystalline inorganic semiconductor layer on flexible substrates such as Silicon-On-Insulator (SOI) and III–V semiconductors on Si [6][7]. Although the performance of the organic semiconductors has relatively improved recently [8][9], the performance of inorganic monocrystalline semiconductors represented by Si and III-V compounds will not

Manuscript received Aug 1, 2017; revised ??? ?? ????; accepted ??? ?? ?????. Date of publication ??? ??, ???; date of current version ??? ?? ????. The Defense Advanced Research Projects Agency (DARPA) through ONR grant N00014-16-1-263 and NBMC supported this work. This material is also based on research sponsored by Air Force Research Laboratory under agreement number FA8650-13-2-7311. The review of this paper was arranged by ???? T. Fukushima is with the Department of Mechanical Systems Engineering, Tohoku University, Sendai 980-8579, Japan (e-mail: fukushima@lbc.mech. tohoku.ac.jp) A. Alam, A. Hannna, S. C. Jangam, A. Bajwa, and S. S. Iyer is with the Electrical Engineering Department, University of California, Los Angeles (UCLA), Los Angeles, 90095, (arsalanalam89@ucla.edu, amirhanna@ucla.edu, sivchand@ucla.edu, abajwa@ucla.edu, ss.siyer@ucla.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier ????????

be achieved by the organic semiconductors.

On the other hand, Flexible hybrid electronics (FHE) combine the flexibility of flexible substrates with the performance of inorganic monocrystalline semiconductor devices to create a new category of electronics [10][11]. Traditional rigid/flex packages enable us to integrate thick Si dies on flexible substrates [12][13]. However, these technologies are not based on Wafer-Level Packaging (WLP), and in addition, the flexibility is limited by their rigid substrates. More recently, in order to enhance the flexibility of the rigid monocrystalline semiconductors, ultra-thin dies are mounted on flexible substrates [14] [15]. This is because such thinned dies can be more flexible and follow curved profiles. However, ultra-thin dies are very sensitive to applied stresses [14] by which both the performance degradation and property deviation would be induced with small bending radii. Lee et al. have reported that the retention time of thinned DRAM (Dynamic Random Access Memory) having planar capacitors is shortened when the die thickness is less than 50 µm [16].

We have been working on holistic heterogeneous system integration using silicon interconnect-fabric (Si-IF) that can eliminate the organic laminates and achieve the drastic reduction of interconnect length between hardened intellectual property (IP) dies "dielets" integrated on Si wafers at small inter-die spaces [17][18]. In our FHE approach, the rigid dielets are embedded in flexible polymeric substrates we call FlexTrate<sup>TM</sup> that is fabricated at the wafer level using an advanced die-first FOWLP (Fan-Out Wafer-Level Packaging) technology. Classical FOWLP is expected to reduce package sizes, shorten inter-chip wirings by eliminating laminates, and integrate dies in rigid epoxy mold compounds (EMCs) [19][20]. Several redistributed wiring layers (RDL)-first approaches with and without wafer-level processing have been reported for rigid [21] or flexible [22][23] device system integration. Compared to RDL-first FOWLP with die/flip-chip bonding processes, die-first FOWLP is cost effective [24]. If the die shift issues in die-first FOWLP are mitigated, the production yield would be further increased, leading to drastic cost reduction. The biggest advantage of the die-first FOWLP is that wire bonding, printable wiring, and solder bumping are not required for connecting the neighboring dies and there are no additional packaging processes due to the embedded structure [25][26]. In our embodiment of this approach, the high flexibility is achieved by the unique structure of FlexTrate<sup>TM</sup> consisting of

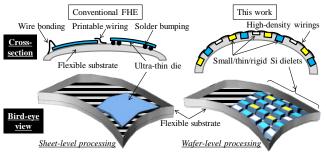

the hard and soft segments analogous to how a bicycle chain is flexible in spite of rigid chain components. As depicted schematically in Fig. 1, the dielets themselves are not expected to bend, whereas the polymer regions are bent in between the dielets which act like the joints in the bicycle chain. Heterogeneous dielets are embedded in a flexible substrate, and then electrically connected with high-density interconnects formed in wafer-level processing. Similar structures using rigid device islands interconnected with horseshoe wirings have been developed for stretchable electronics [13][22][23], but the fabrication concept of these systems is considerably different from FlexTrate<sup>TM</sup> based on scalable WLP using embedded Si dielets that are assembled in a face-down configuration. Landesberger et al. have presented a quite similar approach to our FOWLP-based FlexTrate<sup>TM</sup> although they employ ultra-thin Si dies having equalized die thicknesses and the dies are bonded in a face-up configuration [27]. Due to our advanced die-first FOWLP, the FlexTrate<sup>TM</sup> allows scalable integration of heterogeneous dielets with various thicknesses and much tighter interconnect formation than conventional rigid/flex packages fabricated in sheet-level or roll-to-roll processing. In addition, fine-pitch interconnects can be formed at the wafer level. Nowadays, inkjet printing can draw very fine wirings in parallel, but the wire thicknesses are limited [28]. FlexTrate<sup>TM</sup> with inorganic monocrystalline semiconductor dielets can realize highly integrated flexible device systems without using low performance organic semiconductors, ultra-thin devices/dies, and colloid/paste based wirings.

In this study, we demonstrate fine-pitch (< 10 µm) interconnect formation on a biocompatible PDMS in which Si dielets are embedded by using the advanced die-first FOWLP technology. In addition, coplanarity between PDMS and dielets and die shift concerned in typical die-first FOWLP are characterized to implement the new flexible device system integration processes. High-density interconnect formation on the elastically deformable/stretchable PDMS rubber without cracks is very challenging compared with that on rigid EMCs. From a reliability point of view, the bendability of the FlexTrate<sup>TM</sup> is also evaluated by cyclic bending test.

Fig. 1. Schematic comparison of die integration for FHE: ultra-thin/large die bonded on flexible substrate (left) and small/thin/rigid dielets embedded in flexible substrate "FlexTrate<sup>TM</sup>" (right).

#### II. EXPERIMENTAL

#### A. Materials

A biocompatible PDMS "Silastic MDX4-4210 (Dow)" was used in this work. The biocompatible PDMS consisting of a base resin and a curing agent was uniformly mixed and defoamed with a planetary centrifugal mixer (THINKY, ARE-310) prior to compression soft-molding.

Rivalpha 3195M and 3195V (Nitto denko) were used as the 1<sup>st</sup> and 2<sup>nd</sup> temporary adhesives, respectively. The mechanically peelable layer was typically laminated at room temperature on the 1<sup>st</sup> Si handler. The other thermally removable layer was attached on the PDMS and dielets.

#### B. Measurement

The surface profile was measured with non-contact white light interferometer (cyberTECHNOLOGIES, CT100) and a contact-type stylus (Veeco, DEKTAK 150). The water contact angles were determined with the goniometer (VCA3000S, AST Products, Inc.). Resistances were measured with the probe station with probes (model: 7T-J3/20x1.25", taper: 200-220", radius: 2µm, overall length: 1.25", American Probe & Technologies) and probers (Model 350, The Micromanipulator Co., Inc) equipped with a Count multimeter (5491B, BK PRECISION) and a DC power supply (E3644A, Agilent).

# C. Fabrication

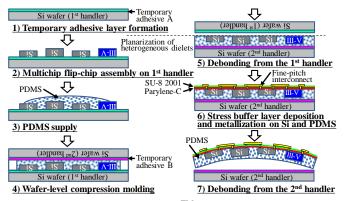

100-μm-thick 1-mm-sqaure Si dielets were fabricated by plasma dicing in GINTI, Tohoku University. Fig.2 shows the total process of FlexTrate<sup>TM</sup> fabrication. A temporary adhesive 3195M was laminated on the 1st Si handler. Then, the Si dielets were precisely aligned in a face-down configuration on the adhesive formed on the 1st handler using a K&S APAMA die to wafer assembly tool. A biomedical grade PDMS was applied on the die-on-wafer structure, followed by vacuum defoaming with a vacuum level of < 133 Pa from the high-viscous PDMS sandwiched with the 2<sup>nd</sup> Si handler for 30 min or more. The 2<sup>nd</sup> handler has another temporary adhesive 3195V. The subsequent compression mold with the 2<sup>nd</sup> handler is done with a wafer bonder (SUSS Micro Tec, SB6) with a compression force of 600 N. The 1st handler was then thermally debonded at 130°C for 2 min, and subsequently, the hundreds of the Si dielets were transferred to the 2<sup>nd</sup> handler. Prior to the following metallization processes, a thin stress buffer layer (SBL) of Parylene-C and a photosensitive planarization layer SU-8 2001 (Microchem) were sequentially formed with a parylene coater (Specialty Coating Systems, PDS 2010,) and simple spin-coating on the PDMS/dielets, respectively. By using standard photolithography processes with a vacuum evaporation technique, fine-pitch Au wirings (10-nm-thick Ti as an adhesion/barier layer and 200-nm-thick Au) were deposited on the SU-8/Parylene-C/Si dielet array and the surrounding PDMS at the wafer-level. Au interconnects were formed by wet etching with chemicals of an iodine complex/potassium iodine/wafer 1/4.2/294.8 (wt%) mixture for Au and a buffered fluoric acid (hydrogen fluoride/ammonium fluoride 1/6 wt%) for Ti. On the other hand, Cu wirings were formed by PVD and wet etching with a mixture of acetic acid/35% hydrogen

peroxide/wafer 1/1/18 by weight. Finally, the FlexTrate<sup>TM</sup> was thermally debonded at 180 °C for 1 min from the 2<sup>nd</sup> handler. The flexible, tough, and less stretchable properties of the Parylene-C can prevent the wires from being elongated, following thermal and mechanical deformation of the PDMS. However, since the non-photosensitive Parylene-C is conformably deposited on the small steps formed at the interface between the PDMS and embedded dielets, the additional photosensitive spin-on layer SU-8 is required to planarize the step and electrically contact to the dielets through the Parylene-C.

Fig. 2. A process flow of FlexTrate<sup>TM</sup> fabrication.

#### III. RESULTS AND DISCUSSION

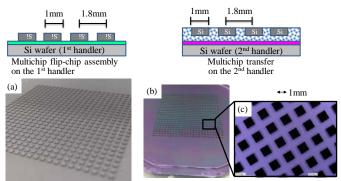

## A. Coplanarity evaluation

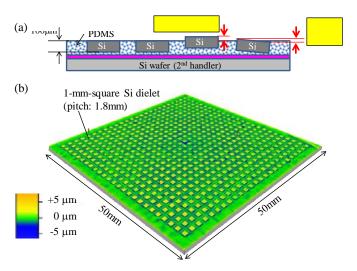

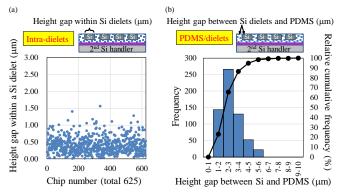

High coplanarity between PDMS and embedded dielets after wafer-level compression molding is needed to integrate fine-pitch interconnects on FlexTrate<sup>TM</sup>. If the coplanarity is low, defocusing when using steppers and large proximity gaps when using mask aligners lower their lithographic resolution for patterning. As shown in Fig. 3, 625 (25 by 25) pieces of Si dielets are successfully transferred from the 1st handler to the 2nd one. The 3D surface profiles are measured with a surface metrology system (cyberTECHNOLOGIES, CT100) equipped with confocal white light. These data are analyzed and the average coplanarity between molded PDMS and transferred dielets in addition to the intra-dielets are summarized in Fig. 4. The PDMS is cured at room temperature. From the coplanarity of the intra-dielets, almost all dielets shows the die tilt with the height gaps of within 1 µm. Concerning coplanarity among the PDMS and embedded dielets, the high frequencies are obtained from 1 µm to 4 µm and the maximum height gap is below 6 µm. These height gaps including die tilt are attributed to die placement and PDMS curing conditions: the die placement force is 5 N/chip (= 5 MPa).

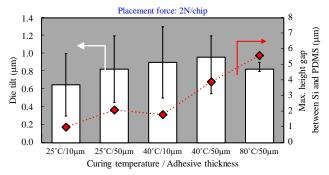

Fig. 5 shows the effect of PDMS curing temperature and adhesive thickness ( $10 \, \mu m$  or  $50 \, \mu m$ ) on these height gaps. Here, die placement force of 2 N/chip is employed. The minimum die tilt of the intra-dielets is obtained by room-temperature PDMS curing and the 10- $\mu m$ -thick temporary adhesive. However, the die tilt is not significantly affected by these conditions. On the

other hand, the impact of these conditions on the height gap between the PDMS and Si dielets is high. The height gaps can be reduced down to 1  $\mu m$  when we employ the 10- $\mu m$ -thick temporary adhesives and room-temperature PDMS curing. These results indicate that elevated curing temperature of PDMS softens the adhesive layer, resulting in dielet sinking down into the layer during compression molding. We assume the differences given by the adhesive thickness would be resulted from their softening behavior at elevated temperature between the two adhesives: one is a thicker thermally removable layer and the other is a thinner mechanically peelable layer. Several micrometers in the height gap between the PDMS and dielets can be mitigated by the subsequent planarization process with SU-8 to be formed on a conformably deposited Parylene-C layer.

Fig. 3. A cross-sectional schematic and the 3D surface profile of Si dielets embedded in molded PDMS after transfer to the  $2^{nd}$  handler.

Fig. 4. Coplanarity between intra-dielets (a) and PDMS and dielets (b).

Fig. 5. Impact of PDMS curing temperature and adhesive thickness on height gaps of intra-dielets and between PDMS/dielet.

## B. Die shift challenges

Die shift is a serious problem in current die-first FOWLP using rigid EMCs. In a previous paper [19], the average die shift is beyond 40 µm and maximum die shift is nearly 80 µm. These large die shift would be given by thermal cure shrinkage, low adhesion strength between temporary adhesives and dies, and CTE mismatch between EMCs and dies. The EMCs including silica fillers have relatively low CTE that is one order magnitude lower than typical epoxies. However, the die shift can not be restricted, and thus, the die shift issues are solved by die pre-shift that makes deliberate misplacement of dies in their pick-and-place process to account for drift [19]. The prediction can compensate for the die shift, but that is not perfect. Nowadays, lithography tools are dedicated to FOWLP applications, and for instance, steppers can accurately follow the large die shift in a die-by-die alignment mode [29]. Although the allowable values for die shift depend on lithographic tools, large die-shift definitely reduces wafer-level packaging density and production yield/throughput for patterning.

Table 1 Properties of a biocompatible PDMS for FlexTrate<sup>TM</sup> and a non-biocompatible rigid epoxy used in typical FOWLP.

| Properties                        | PDMS (MDX4-4210 / Dow)                                   | EMC [30]  |

|-----------------------------------|----------------------------------------------------------|-----------|

| Elongation at break               | ~500%                                                    | < 1%      |

| CTE                               | ~300 ppm/K                                               | 7.5 ppm/K |

| Young's modulus                   | 0.5 MPa                                                  | 22 GPa    |

| $T_g$                             | -120°C                                                   | 165°C     |

| Curing temp.                      | 25°C - 80°C                                              | 125°C     |

| Biocompatibility (screening test) | Passed up to 29 days for implantation in the human body. | None      |

In this work, a biocompatible PDMS elastomer is employed as a flexible substrate. The thermomechanical characteristics of the biocompatible PDMS "Silastic MDX4-4210 (Dow)" and a rigid EMC including silica fillers used in a typical FOWLP research [30] are summarized in Table 1 for comparison. The elongation at break of the PDMS is quite high, compared with the EMC. The PDMS has high CTE with respect to both Si and Cu, 300 vs. 3 and 17 ppm/K, respectively. The glass transition temperature  $T_g$  of the PDMS is much lower than room temperature. The huge difference from the rigid epoxy is the 0.5 MPa of Young's modulus that is 4 orders of magnitude lower

than the EMC.

The PDMS has large  $\alpha 1$  showing a CTE at below  $T_g$ . However, the  $T_g$  is much lower than room temperature, which means thermal stress accumulated with Young's modulus and CTE ( $\alpha$ 1) mismatch in the temperature regions ranging from room temperature to  $T_g$  is experimentally zero [31]. According to the Stoney equation [32] simply calculated with the following PDMS/EMC/Si parameters: Young's modulus: 0.5 MPa/22 GPa/190 GPa, CTE: 300/7.5/2.6, PDMS/EMC curing temperature: 80/125°C, and 0.272 for Si Poisson ratio, the 300-mm-diameter Si wafer warpages of the PDMS and EMC with a thickness of 500 µm are 1.8 µm and 2.4 mm, respectively. The biggest difference is due to the low Young's modulus of the PDMS. Although the Stoney's equation can well assume the film thickness to be less than 1/20 of the substrate thickness and is effective for smaller substrate [33][34], general elastomers represented by PDMS will be estimated to apply extremely low stresses so as not to drift embedded dies.

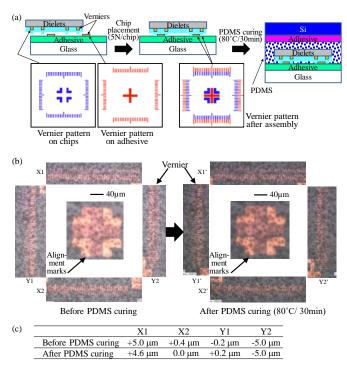

To accurately evaluate die shift between before and after PDMS curing, Vernier scale patterns are formed on the temporary adhesive. The process flow is shown in Fig.6(a), where a 50-nm-thin Cu layer is deposited on the thermally releasable temporary adhesive (Rivalpha 3195M) laminated on a 500-um-thick glass wafer by PVD, followed by wet etching to make the Vernier patterns. The dielets having the corresponding Vernier patterns were fabricated in GINTI, Tohoku University, by using Cu wet etch and plasma dicing processes. The resolution of the Vernier patterns is 0.2 µm and we can evaluate the die shift within 5 µm with the Verniers. These dielets are gently placed upside-down on the temporary adhesive with the flip-chip bonder (K&S, APAMA): placement force is 5 N/mm<sup>2</sup> at bottom stage temperature is 60°C. The adhesion strengths of the temporary adhesive before and after Cu PVD and patterning are 0.75 and 0.60 MPa. The shear bonding strengths are measured with a multi-purpose bond tester (Dage Co., 4000Plus). We evaluate the die shift before and after PDMS curing at 80°C for 30 min by wafer-level compression mold with the 2<sup>nd</sup> Si handler.

The typical images before and after PDMS curing is shown in Fig. 6(b). As compared with these images, the die shift is hardly observed after PDMS curing. The initial die placement errors are nearly 5 µm or more because the alignment marks formed at the center of the die placement position on the temporary adhesive is unclear due to the roughened surfaces of black particles as a thermal bubbling component in the thermally removable layer. Surprisingly, the die shift can be compensated by using the PDMS even though the shear bonding strength between the Rivalpha surface and dielets is not high. The reason why the extremely low die shift is obtained is probably due to the excellent thermomechanical properties of the PDMS such as very low Young's modulus, low curing temperature, and low  $T_g$ much lower than room temperature. Also, we cannot ignore the use of middle-sized wafers with a diameter of 100 mm in this work. The images are captured in the position 30 mm away from the center of the wafers with a high-resolution digital

microscope (Keyence, VHX-6000). The die shift works are still going to well know the mechanism and further investigate the die shift in the subsequent PDMS transfer and metallization processes.

Fig. 6. Die shift evaluation: a flow of sample fabrication and Vernier patterns formed on dielets and adhesives (a), and photographs of the Vernier patterns (b) and die shift values (c) obtained before and after PDMS curing at 80°C for 30 min.

## C. Process integration with high-density interconnect

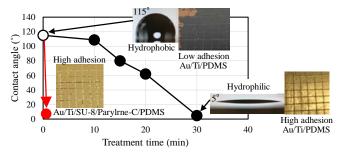

As shown in Fig. 7, 625 square 1mmx1mm dielets were assembled on the 1st Si handler, and were successfully transferred to the 2<sup>nd</sup> handler at 130°C. Then, the metallization with evaporated Ti/Au is performed on the PDMS and embedded Si dielets covered with a 1-µm-thick oxide layer on the top. However, adhesion between the metals and the PDMS is quite low. Therefore, a surface modification step was inserted into the process to enhance the adhesion between the metal and PDMS. By using a UV/O<sub>3</sub> treatment, the water contact angle is dramatically decreased, and consequently, the PDMS surface is rendered highly hydrophilic as shown in Fig. 8. These hydrophilic surfaces can increase the adhesion strength between the metal and PDMS as seen from pictures insets in Fig. 8. The Scotch tape adhesion test was based on ASTM D 3359-87 Method B. Another surface modification with oxygen plasma (power: 65 W, O<sub>2</sub> flow: 100 sccm, and etching time: 30 s) can further reduce process time.

In the metallization process, photoresists are used for the metal patterning as a mask material for photolithography processes. However, cracks were generated in the use of a standard positive photoresists (Microchemicals, AZ5214E) in the cooling step after spin-coating and the subsequent pre-baking. Thus, we propose the use of a SBL between the metals and PDMS. Parylene-C was employed as a SBL. In

addition, the surface of the PDMS after transferring it on the 2<sup>nd</sup> handler is not perfectly smooth because of the small steps at the interface between the PDMS and Si dielets. SU-8 is employed as a planarization layer by spin coating. The spin-on photosensitive material also help to open contact holes down to dielets through their top passivation in future works. Generally, Parylene-C have low adhesion to various polymeric materials and Si/glass substrates etc. [35]. Although several surface modification techniques have been reported [36][37], the adhesion enhancement between the PDMS and parylenes is still a big concern. To enhance the Parylene-C/PDMS adhesion, we newly utilize vinyl triacetoxy silane (AP3000, Dow) that is well known to be an adhesion promotor for BCB (benzo cyclobutene resin) to Si substrates [38]. After PDMS surface modification with oxygen plasma, AP3000 was spin-coated on the treated PDMS. The vinyl functional groups would react with free radicals generated in CH<sub>2</sub>=C< double bonds of di-para-xylylene resulted from the pyrolysis of the parylene monomers in the next step. Then, the Parylene-C surface is treated with the oxygen plasma in the same conditions again, SU-8 2001 was coated and cured, followed by Ti/Au deposition with an EB evaporator (CHA, Solution). After deposition of the metals, the adhesion strength is evaluated by the Scotch tape test. As seen in the image inserted into the bottom left in Fig.8, the adhesion at the interfaces of Au/Ti, Ti/SU-8, SU-8/modified Parylene-C, and Parylene-C/modified PDMS is very high.

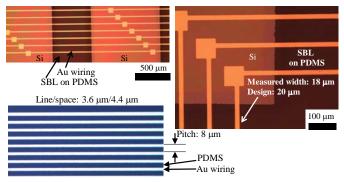

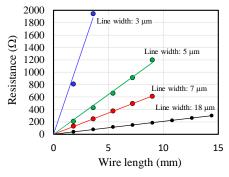

Photoresists can be coated on the metal deposited on the SBL without cracks and dewetting. In addition, the SBL formation can allow the metal deposition without microcracks reported in the previous paper [39] by mitigating the CTE/elongation/modulus mismatches between the PDMS and metals. As a result, Ti/Au wirings with the SBL are electrically connected between the adjacent dielets. 8- $\mu$ m-pitch Au wirings (Line/Space 3.4/4.6  $\mu$ m) are successfully formed on the array of Si dielets and the surrounding PDMS as shown in Fig. 9. Fig. 10 shows that excellent linear relationships are obtained by I-V measurement of the fine Au wirings with the minimum wire width of 3  $\mu$ m.

Fig. 7. Photomicrographs of 1-mm-square multi-dielets placed on the 1<sup>st</sup> Si handler (die pitch: 1.8 mm): bird-eye view (a). Photomicrographs of 1-mm-square multi-dielets transferred to the 2<sup>nd</sup> Si handler: top view (b) and magnified top view (c).

Fig. 8. Water contact angle shift as a function of PDMS surface modification time with UV/O<sub>3</sub> (black) or O<sub>2</sub> plasma (red) and images after Scotch tape test for adhesion strength evaluation.

Fig. 9. Optical images of intra-dielet/fine-pitch wirings formed on Si/PDMS in wafer-level processing.

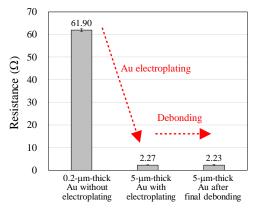

In the present paper, since wafer-level processing is employed, metal layers can be readily thickened by using wafer-level electroplating. Au electroplating was supported by Electroplating Engineers of Japan Ltd. (EEJA). As shown in Fig.11, the 200-nm-thick Au wire resistances are significantly decreased down to nearly 1/30 when thick Au wires with a thickness of approximately 5 µm are used. The low resistances are kept even after final PDMS removal from the 2<sup>nd</sup> handler as shown in Fig.11.

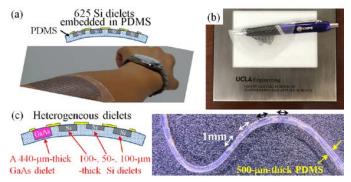

The FlexTrate<sup>TM</sup> embedding large numbers of the 1-mm-sqaure Si dielets in the PDMS can be attached on the curved profiles such as the human arm, Fig. 12 (a), and a pen, Fig. 12 (b). Fig. 12 (c) shows the cross-section of a FlexTrate<sup>TM</sup> embedding heterogeneous dielets composed of a 440-μm-thick GaAs dielets and three 1-mm-sqaure Si dielets with various thicknesses of 50 and 100 μm. As seen from these pictures, rigid dielets can be bent in any chosen direction by the flexible PDMS between the dielets. These FlexTrate<sup>TM</sup> with the heterogeneous dielets embedded in the biocompatible PDMS can be implanted into the human body including the brain.

Fig. 10. The relationship between the resistances and wire lengths formed on a PDMS before removal from the 2<sup>nd</sup> handler.

Fig. 11. Resistances formed on FlexTrate<sup>TM</sup>: 200-nm-thick Au wires and 5-μm-thick Au wires before/after debonding.

Fig. 12. Pictures of FlexTrate<sup>TM</sup> demonstrators: wearable (a) and rollable (b) 100- $\mu$ m-thick / 1-mm-sqaure 625 Si dielets embedded in PDMS, and a cross-sectional image of PDMS embedding heterogeneous dielets composed of GaAs and Si with various thicknesses (c).

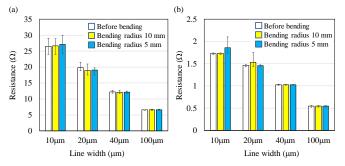

# D. Bendability

The bendability of the FlexTrate<sup>TM</sup> having embedded dielets is evaluated with an endurance testing system: tension-free U-shape folding tester (DLDMLH-FS/Yuasa). Fig.13 shows the resistances of FlexTrate<sup>TM</sup> test vehicles having 600-nm- and 5-μm-thick Cu wirings formed on the PDMS embedding 1-mm-square Si dielets with a thickness of 100 μm. Cu wirings are required for FHE desiring low-resistance applications such as wearable sensors, whereas Au/Ti wirings are desirable for implantable use due to their high biocompatibility. 4-point probe patterns are used for the resistance evaluation. The Cu interconnections are 15 mm long and 100, 40, 20, and 10 μm in

width. The resistances are compared before and after 1,000-bending with a curvature radius of 10 mm and the subsequent additional 1,000-bending with the radius of 5 mm. As a result, both the Cu interconnects between the neighboring dielets embedded in the PDMS are still connected without delamination. The resistance changes are within 2% on average after the sequential bending. In contrast, 200-nm-thick Cu wirings hardly survive the thermal debonding process. From these results, the wide ranges of Cu thicknesses are turned out to be applicable for the FlexTrate<sup>TM</sup>.

Comparison of some of state-of-the-art FHE under stress is summarized in Ref. [40]. 20-µm-thick Si fabricated by dicing before grinding and 15-µm-thick Si fabricated by controlled spalling techniques exhibit the reliable curvature radii of 20 mm [40] and 6.3 mm [41]. These studies show good CMOS characteristics under the bending conditions, however, repeated bending is not evaluated. Our new FHE "FlexTrate<sup>TM</sup>" achieves high durability of 2,000-cycle bending in total with curvature radii of 10 mm and 5 mm as mentioned above.

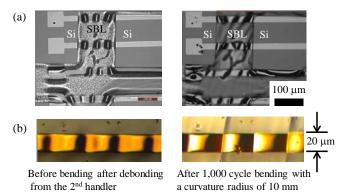

Fig. 14 (a) and (b) shows the SEM images and photomicrographs of the test vehicles before and after bending with the radius of 10 mm. The left image is captured just after debonding from the 2<sup>nd</sup> handler at 180°C. Several wrinkles are observed between the dielets even before bending when the 600-nm-thick Cu wirings are employed. The cracks resulted from the wrinkles are probably formed in the brittle SU-8 on the SBL Parylene-C that is plastically deformed. However, the two polymers SU-8/ Parylene-C formed on the PDMS mitigate the stresses applied when thermal debonding and mechanical repeated bending. On the other hand, compared to 600-nm-thick Cu wirings, half of the 10- and 20-µm-wide Cu wirings with the thickness of 5 µm are working after additional bending of the curvature radius of 2.5 mm. In addition, the 40- and 100-μm-wide Cu wirings exhibit almost the same resistances as the initial values when the wire is thickened. It should be stressed that FlexTrate<sup>TM</sup> fabrication process has a wide margin for wire thickness.

From simulation results using ANSYS, it is found that larger inter-dielet spaces and thicker dielets give smaller stresses to the PDMS underneath metal wires without SBL. We are still on going the stress mapping research of FlexTrate<sup>TM</sup> and working on the stress simulation analyses of the embedded dielets and wirings formed on SBL.

#### IV. CONCLUSION

We have integrated FlexTrate<sup>TM</sup> using the new technology platform based on advanced die-first FOWLP for next-generation FHE. 3-μm-feature Au wirings are successfully formed on the PDMS in which Si dielets are embedded and planarized. High coplanarity, low die shift, and high repeated bendability are achieved by FlexTrate<sup>TM</sup>. The fabrication process of FlexTrate<sup>TM</sup> with 10-μm-feature Cu interconnects exhibits a wide margin for wire thickness in 1,000-cycle repeated bending with a curvature radius of 5 mm or less. This heterogeneous integration using monocrystalline Si dielets

embedded in flexible substrates enables high-performance and scalable flexible device systems with high-density interconnects to create highly-integrated wearable and implantable electronics.

Fig. 13. Resistance comparison between before and after 1,000-cycle bending with curvature radius of 10 and 5 mm for 100-, 40-, 20-, and 10- $\mu$ m-width Cu wirings formed on Si dielets embedded in PDMS: Cu thicknesses are 600 nm (a) and 5  $\mu$ m (b).

Fig. 14. SEM images (a) and the enlarged photomicrographs (b) of 600-nm-thick Cu wirings formed on FlexTrate<sup>TM</sup> with dielets embedded in PDMS before and after bending.

# REFERENCES

- C. Strohhofer, G. Klink, M. Feil, A. Drost, D. Bollmann, D. Hemmetzberger, and K. Bock, "Roll-to-roll microfabrication of polymer microsystems", *Measurement & Control*, vol. 40, no. 3, pp. 80-83, Apr., 2007, DOI: 10.1177/002029400704000305.

- T.-C. Huang, K. Fukuda, C.-M. Lo, Y.-H. Yeh, T. Sekitani, T. Someya, and K.-T. Cheng, "Pseudo-CMOS: a design style for low-cost and robust flexible electronics", *IEEE Trans. Electron Devices*, vol. 58, No. 1, pp. 141-150, Jan., 2011, DOI: 10.1109/TED.2010.2088127.

- T. Sekine, R. Sugano, T. Tashiro, K. Fukuda, D. Kumaki, F. D. D. Santos, A. Miyabo, and S. Tokito, "Fully printed and flexible ferroelectric capacitors based on a ferroelectric polymer for pressure detection", *Jap. J. Appl. Phys.*, vol. 55, pp. 10TA18 (4pp), Sept., 2016, DOI: 10.7567/JJAP.55.10TA18.

- C. C. Wu, S. D. Theiss, G. Gu, M. H. Lu, J. C. Sturm, S. Wagner, and S. R. Forrest, "Integration of organic LED's and amorphous Si TFT's onto flexible and lightweight metal foil substrates", *IEEE Electron Device Lett.*, vol. 18, no. 12, pp. 609-612, Dec., 1997, DOI: 10.1109/55.644086

- K. Myny, "The development of flexible integrated circuits based on thin-film transistors", *Nature Electronics*, vol. 30, pp. 30–39, Jan., 2018, DOI: 10.1038/s41928-017-0008-6.

- D.-H. Kim, J.-H. Ahn, W. M. Choi, H.-S. Kim, T.-H. Kim, J. Song, Y. Y. Huang, Z. Liu, C. Lu, and J. A. Rogers, "Stretchable and foldable silicon integrated circuits", *Science*, vol. 320, pp. 507-511, Apr., 2008, DOI: 10.1126/science.1154367.

- M. Madsen, K. Takei, R. Kapadia, H. Fang, H. Ko, T. Takahashi, A. C. Ford, M. H. Lee, and A. Javey, "Nanoscale semiconductor "X" on substrate "Y" -processes, devices, and applications", *Adv. Mater.*, vol. 23, pp. 3115–3127, Jul., 2011, DOI: 10.1002/adma.201101192

- H. Iino, T. Usui, and J. Hanna, "Liquid crystals for organic thin-film transistors", *Nature Communications*, vol. 6, 6828 (8pp), Apr., 2015, DOI: 10.1038/ncomms7828.

- M. J. Kang, I. Doi, H. Mori, E. Miyazaki, K. Takimiya, M. Ikeda, and H. Kuwabara, "Alkylated dinaphtho[2,3-b:2', 3'-f]thieno[3,2-b]thiophenes (Cn-DNTTs): organic semiconductors for high-performance thin-film transistors", *Adv. Mater.*, vol. 23, pp. 1222–1225, Aug., 2011, DOI: 10.1002/adma.201001283.

- K. Jain, M. Klosner. M. Zemel, and S. Raghunandan, "Flexible electronics and displays: high-resolution, roll-to-roll, projection lithography and photoablation processing technologies for high-throughput production", *Proc. IEEE*, vol. 93, no. 8, pp. 1500-1510, Aug., 2005, DOI: 10.1109/JPROC.2005.851505.

- J. S. Chang, A. F. Facchetti, and R. Reuss, "A circuits and systems perspective of organic/printed electronics: review, challenges, and contemporary and emerging design approaches", *IEEE J. Emerging and Selected Topic in Circuit and Systems*, vol. 7, no. 1, pp. 7-26, Mar., 2017, DOI: 10.1109/JETCAS.2017.2673863.

- M. Fujiwara, Y. Shirato, H. Owar, K. Watanabe, M. Matsuyama, K. Takahama, T. Mori, K. Miyao, K. Choki, T. Fukushima, T. Tanaka, and M. Koyanagi, "Novel optical/electrical printed circuit board with polynorbornene optical waveguide", *Jap. J. Appl. Phys.*, vol. 46, no. 4B, pp. 2395–2400, Apr., 2007, DOI: 10.1143/JJAP.46.2395.

- F. Bossuyt, T. Vervust, and J. Vanfleteren, "Stretchable electronics technology for large area applications: fabrication and mechanical characterization", *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 2, pp. 229-235, Feb., 2013, DOI: 10.1109/tcpmt.2012.2185792.

- N. Wacker, H. Richtel, T. Hoang, P. Gazdzicki, M. Schulze, E. A Angelopoulos, M. Hassan, and J. N. Burghartz, "Stress analysis of ultra-thin silicon chip-on-foil electronic assembly under bending", Semicond. Sci. Technol. vol. 29, 095007 (12pp), Aug., 2014, doi:10.1088/0268-1242/29/9/095007.

- R. L. Chaney, D. E. Leber, D. R. Hackler, B. N. Meek, S. D. Leija, K. J. DeGregorio, S. F. Wald, and D. G. Wilson, "Advances in flexible hybrid electronics reliability", in Proc. 2017 IEEE Workshop on Microelectronics and Electron Devices (WMED), pp. 5-8, Apr., 2017, DOI: 10.1109/WMED.2017.7916924.

- K. Lee, S. Tanikawa, M. Murugesan, H. Naganuma, H. Shimamoto, T. Fukushima, T. Tanaka, and M. Koyanagi, "Degradation of memory retention characteristics in DRAM chip by Si thinning for 3-D integration", *IEEE Electron Device Lett.*, vol. 34, no. 8, pp. 1038-1040, Aug., 2013, DOI: 10.1109/LED.2013.2265336.

- S. S. Iyer, "Heterogeneous integration for performance and scaling", *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 6, no. 7, pp. 973-983, Jul., 2016, DOI: 10.1109/TCPMT.2015.2511626.

- A. A. Bajwa, S. C. Jangam, S. Pal, N. Marathe, T. Bai, T. Fukushima, M. Goorsky, and S. S. Iyer, "Heterogeneous integration at fine pitch (2-10 μm) using thermal compression bonding", in Proc. of the 67th IEEE Electronic Components and Technology Conference (ECTC), pp. 1276-1284, May, 2017, DOI: 10.1109/ECTC.2017.240.

- G. Sharma, A. Kumar, V. S. Rao, S. W. Ho, and V. Kripesh, "Solutions strategies for die shift problem in wafer level compression molding", *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 4, pp. 502-509, April, 2011, DOI: 10.1109/TCPMT.2010.2100431.

- C.-F. Tseng, C.-S. Liu, C.-H. Wu, and D. Yu, "InFO (wafer level integrated fan-out) technology" in Proc. of the 66th IEEE Electronic Components and Technology Conf. (ECTC), pp. 1-6, May, 2016, DOI: 10.1109/ECTC.2016.65.

- Y. Kurita, K. Soejima, K. Kikuchi, M. Takahashi, M. Tago, M. Koike, K. Shibuya, S. Yamamichi, and M. Kawano, "A novel "SMAFTI" package for inter-chip wide-band data transfer", in Proc. of the 56<sup>th</sup> IEEE Electronic Components and Technology Conference (ECTC), pp. 289-297, May, 2006, DOI: 10.1109/ECTC.2006.1645661.

- J. Kim, G. A. Salvatore, H. Araki, A. M. Chiarelli, Z. Xie, A. Banks, X. Sheng, Y. Liu, J. W. Lee, K.-I. Jang, S. Y. Heo, K. Cho, H. Luo, B. Zimmerman, J. Kim, L. Yan, X. Feng, S. Xu, M. Fabiani, G. Gratton, Y. Huang, U. Paik, and J. A. Rogers, "Battery-free, stretchable

- optoelectronic systems for wireless optical characterization of the skin", *Sci. Adv.*, vol. 2, e1600418, Aug., 2016, DOI: 10.1126/sciadv.1600418.

- B. Plovie, Y. Yang, J. Guillaume, S. Dunphy, K. Dhaenens, S. V. Put, B. Vandecasteele, T. Vervust, F. Bossuyt, and J. Vanfleteren, "Arbitrarily Shaped 2.5D Circuits using Stretchable Interconnects Embedded in Thermoplastic Polymers", *Adv. Eng. Mater.*, 1700032 (8pp), Apr., 2017, DOI: 10.1002/adem.201700032.

- A. P. Lujan, "Yield comparison of die-first face-down and die-last fan-out wafer level packaging", in Proc. of the 67th IEEE Electronic Components and Technology Conference (ECTC), pp. 1811-1816, May, 2017, DOI: 10.1109/ECTC.2017.39.

- J.-C. Souriau, O. Lignier, M. Charrier, and G. Poupon, "Wafer level processing of 3D system in package for RF and data applications", in Proc. of the 55th IEEE Electronic Components & Technology Conference (ECTC), pp. 356-361, May, 2005, DOI: 10.1109/ECTC.2005.1441291.

- N. Motohashi, T. Kimura, K. Mineo, Y. Yamada, T. Nishiyama, K. Shibuya, H. Kobayashi, Y. Kurita, and M. Kawano, "System in wafer-level package technology with RDL-first process", in Proc. of the 61st IEEE Electronic Components & Technology Conference (ECTC), pp. 59-64, May, 2011, DOI: 10.1109/ECTC.2011.5898492.

- C. Landesberger, N. Palavesam, W. Hell, A. Drost, R. Faul, H. Gieser, D. Bonfert, K. Bock, and C. Kutter, "Novel processing scheme for embedding and interconnection of ultra-thin IC devices in flexible chip foil packages and recurrent bending reliability analysis", in Proc. 2016 Int. Conf. Electronic packaging (ICEP), pp. 473-478, Apr., 2017, DOI: 10.1109/ICEP.2016.7486872.

- T. Yamada, K. Fukuhara, K. Matsuoka, H. Minemawari, J. Tsutsumi, N. Fukuda, K. Aoshima, S. Arai, Y. Makita, H. Kubo, T. Enomoto, T. Togashi, M. Kurihara, and T. Hasegawa, "Nanoparticle chemisorption printing technique for conductive silver patterning with submicron resolution", *Nature Communications*, vol. 7, 11402 (9pp), Apr., 2016, DOI: 10.1038/ncomms11402.

- H. Suda, M. Mizutani, S. Hirai, K. Mori, and S. Miura, "Photolithography study for advanced packaging technologies", in Proc. 2016 Int. Conf. Electronic packaging (ICEP), pp. 577-580, Apr., 2016, DOI: 10.1109/ICEP.2016.7486893.

- T. Braun, S. Raatz, S. Voges, R. Kahle, V. Bader, J. Bauer, K.-F. Becker, T. Thomas, R. Aschenbrenner, and K.-D. Lang, "Large area compression molding for fan-out panel level packing", in Proc. of the 65<sup>th</sup> IEEE Electronic Components and Technology Conference (ECTC), pp. 1077-1083, May, 2015, DOI: 10.1109/ECTC.2015.7159728.

- H. E. Bair, D. J. Boyle, J. T. Ryan, C. R. Taylor, S. C. Tighe, and D. L. Crouthamel, "Thermomechanical properties of IC molding compounds", *Polym. Eng. Sci.*, vol. 30, pp. 609-617, May, 1990, DOI: 10.1002/pen.760301008.

- M. Shimbo, M. Ochi, and Y. Shigeta, "Shrinkage and internal stress during curing of epoxide resins", *J. Appl. Polym. Sci.*, vol. 26, pp. 2265-2277, Jul., 1981, DOI: 10.1002/app.1981.070260714.

- J. S. Kim, K. W. Paik, J. H. Lim, and Y. Y. Earmme, "Thermomechanical stress analysis of laminated thick-film multilayer substrates", *Appl. Phys. Lett.*, vol. 74, no. 23, pp. 3507-3509, Jun., 1999, DOI: 10.1063/1.124145.

- J. Schicker, W.A. Khan, T. Arnold, and C. Hirschl, "Simulating the warping of thin coated Si wafers using Ansys layered shell elements", *Composite Structures*, vol. 140, pp. 668–674, Apr., 2016, DOI: 10.1016/j.compstruct.2015.12.062.

- D. Zeniieh, A. Bajwa, L. Ledernez, and G. Urban, "Effect of plasma treatments and plasma-polymerized films on the adhesion of parylene-C to substrates", *Plasma Process. Polym.*, vol. 10, pp. 1081–1089, Dec., 2013, DOI: 10.1002/ppap.201300045.

- N. Chou, S. Yoo, and S. Kim, "A largely deformable surface type neural electrode array based on PDMS", *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 21, no. 4, pp. 544-553, Jul., 2013, DOI: 10.1109/TNSRE.2012.2210560.

- M. Gołda, M. Brzychczy-Włoch, M. Faryna, K. Engvall, and A. Kotarba, "Oxygen plasma functionalization of parylene C coating for implants surface: Nanotopography and active sites for drug anchoring", *Mater.* Sci. Eng. C, vol. 33, pp. 4221–4227, Oct., 2013, DOI: 10.1016/j.msec.2013.06.014.

- F. Bu, Q. Ma, and Z. Wang, "Delamination of bonding Interface between benzocyclobutene (BCB) and silicon dioxide/silicon nitride", *Microelectronics Reliability*, vol. 65, pp. 225–233, Aug., 2016, DOI: 10.1016/j.microrel.2016.08.003.

- I. R. Minev, P. Musienko, A. Hirsch, Q. Barraud, N. Wenger, E. M. Moraud, J. Gandar, M. Capogrosso, T. Milekovic, L. Asboth, R. F. Torres, N. Vachicouras, Q. Liu, N. Pavlova, S. Duis, A. Larmagnac, J. Vörös, S. Micera, Z. Suo, G. Courtine, and S. P. Lacour, "Electronic dura mater for long-term multimodal neural interfaces", *Science*, vol. 347, pp. 159-163, Jan., 2015, DOI: 10.1126/science.1260318.

- A. Vilouras, H. Heidari, S. Gupta, and R. Dahiya, "Modeling of CMOS Devices and Circuits on Flexible Ultrathin Chips", *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2038-2046, May, 2017, DOI: 10.1109/TED.2017.2668899.

- D. Shahrjerdi, S.W. Bedell, A. Khakifirooz, and K. Cheng, "Mechanically flexible nanoscale silicon integrated circuits powered by photovoltaic energy harvesters," *Solid-State Electron.*, vol. 117, pp. 117–122, Mar. 2016. DOI: 10.1016/j.sse.2015.11.023

Takafumi Fukushima (Tak) received the B.S., M.S., Ph.D. degrees in Department of Materials Science and Chemical Engineering from Yokohama National University in 1998, 2000, 2003, respectively. From 2001 to 2003, he was a technical advisor at PI R&D Corporation in Yokohama. After that, he worked at Venture Business Laboratory of Tohoku University as a postdoctoral fellow for a year. From 2004 to

2009, he was an assistant professor at Department of Bioengineering and Robotics, Tohoku University. From 2010 to 2014, he was an associate professor at New Industry Creation Hatchery Center (NICHe), Tohoku University. From 2015 to 2016, he was an associate professor at Department of Bioengineering and Robotics, Tohoku University. He worked on many aspects of 3D system integration with TSV (through-silicon via) and capillary self-assembly for 3D image sensor, retinal prosthesis, and implantable Si neural probes etc. From 2013, he also joined a consortium of 8/12-inch R&D fab, called Global INTegration Initiative (GINTI), for new 2.5D/3D integration, Tohoku University. From 2016 to 2017, Ha was a visiting research associate at Center for Heterogeneous Integration and Performance Scaling (CHIPS), Electrical Engineering Department, UCLA. He is currently working on heterogeneous integration and flexible hybrid electronics technologies at Department of Mechanical Systems Engineering, Tohoku University, as an associate professor. He was awarded "German Innovation Award / the Gottfried Wagener Prize 2009" and "2010 Outstanding Paper Award of the 60th Electronic Components and Technology Conference (ECTC)", and so on.

Arsalan Alam received the B.Tech. degree in Electronics and Communication Engineering from the Zakir Hussain College of Engineering and Technology, Aligarh, India, in 2011, and the M. Tech. degree in Microelectronics and Very Large-Scale Integration from IIT Roorkee, Roorkee, India, in 2015. He was a visiting student researcher at King Abdullah University of Science and Technology, Thuwal, Saudi

Arabia, in 2016. He is currently pursuing the Ph.D degree with the Center for Heterogeneous Integration and Performance Scaling (CHIPS) group at University of California, Los Angeles. His current research is focused on the development of FlexTrateTM which is a bio-compatible, physically-flexible platform that allows for heterogeneous integration using Fan-Out Wafer Level Packaging (FOWLP) technique for next generation high-performance implantable and wearable applications.

Amir Hanna is a postdoctoral researcher at CHIPS consortium under supervision of Prof Iyer, Electrical Engineering Department, UCLA. He has experience in semiconductors processing, characterization and reliability of thin film transistors and sensors for flexible electronics applications. His current research focus is on flexible hybrid electronics integration using FOWLP for implantable and

wearable electronics applications.

Siva Chandra Jangam received his Bachelor of Tech. degree in Electrical Engineering from Indian Institute of Technology Kanpur, (IIT Kanpur) India and Master of Science in Electrical Engineering from the University of California, Los Angeles (UCLA). He is currently pursuing his Ph.D. degree at UCLA, working with Prof. Subramanian Iyer. His research interests include heterogeneous integration, system scaling, and

advanced packaging. He is currently working on developing fine pitch integration technologies, heterogeneous system design, and communication protocols. He has previously worked on the modeling of novel devices and their applications. He is the recipient of the Intel Best Student Paper award for ECTC 2017 and Guru Krupa Fellowship 2017.

Adeel Ahmad Bajwa received his B.Sc. degree in Electrical Engineering from the University of Engineering and Technology, Lahore, Pakistan in 2007, and a M.Sc. and Ph.D. degrees in Microsystems Engineering from the Albert-Ludwigs University of Freiburg, Germany, in, respectively 2012 and 2015. Between 2012 and 2015, he held a research assistant position at the Laboratory for Assembly and Packaging

Technology (AVT), Institute for Microsystems Technology (IMTEK), University of Freiburg. He focused on developing the assembly solutions for high-power and high-temperature compound semiconductor (GaN and SiC) devices. Between 2015 and 2017, he joined the University of California, Los Angeles, USA, as a postdoctoral research fellow at the "Center for Heterogeneous Integration and Performance Scaling, (CHIPS)". Here, he worked on developing metal-based ultra-fine pitch ( $\leq 10~\mu m$ ) interconnect technologies for microelectronics integration. Since, November 2017, he is working for Kulicke & Soffa Industries Inc. (K&S) in the R&D Engineering Department, where he focuses on developing ultrasonic bonding and thermal compression bonding techniques for copper-based interconnects.

Subramanian S. Iyer (Subu) is Distinguished Chancellor's Professor and holds the Charles P. Reames Endowed Chair in the Electrical Engineering Department at the University of California at Los Angeles and Director of the Center for Heterogeneous Integration and Performance Scaling (CHIPS). He obtained his B.Tech. from IIT-Bombay, and Ph.D. from UCLA and joined the

IBM T.J. Watson Research Center at Yorktown heights, NY and later moved to the IBM systems and Technology Group at Hopewell Junction, NY where he was appointed IBM Fellow and was till 2015 Director of the Systems Scaling Technology Department. His key technical contributions have been the development of the world's first SiGe base HBT, Salicide, electrical Fuses, embedded DRAM and 45nm technology used at IBM and IBM's development partners to make the first generation smartphone devices. He also was among the first to commercialize bonded SOI for CMOS applications through a start-up called SiBond LLC. He has published over 300 papers and holds over 70 patents. His current technical interests and work lie in the area of advanced packaging and three-dimensional integration for system-level scaling and new integration and computing paradigms as well as the long-term semiconductor and packaging roadmap for logic, memory and other devices including hardware security and supply-chain integrity. He has received several outstanding technical achievements and corporate awards at IBM. He is an IEEE Fellow, an APS Fellow and a Distinguished Lecturer of the IEEE EDS as well as its treasurer. He is a Distinguished Alumnus of IIT Bombay and received the IEEE Daniel Noble Medal for emerging technologies in 2012. He also studies Sanskrit in his spare time.