Provided by the author(s) and University College Dublin Library in accordance with publisher policies. Please cite the published version when available.

|                              | Flicker Noise Upconversion and Reduction Mechanisms in RF/Millimeter-Wave Oscillators for 5G Communications |

|------------------------------|-------------------------------------------------------------------------------------------------------------|

| Authors(s)                   | Hu, Yizhe                                                                                                   |

| Publication date             | 2019-09-19                                                                                                  |

| Item record/more information | http://hdl.handle.net/10197/11459                                                                           |

Downloaded 2022-08-28T01:54:10Z

The UCD community has made this article openly available. Please share how this access benefits you. Your story matters! (@ucd\_oa)

# Flicker Noise Upconversion and Reduction Mechanisms in RF/Millimeter-Wave Oscillators for 5G Communications

Yizhe Hu

# Flicker Noise Upconversion and Reduction Mechanisms in RF/Millimeter-Wave Oscillators for 5G Communications

by

#### Yizhe Hu

Bachelor of Science in Microelectronics Harbin Institute of Technology, China, 2013

The thesis is submitted to University College Dublin in fulfilment of the requirements for the degree of

#### Doctor of Philosophy

School of Electrical and Electronic Engineering

Supervisor: Prof. Robert Bogdan Staszewski Assistant Supervisor: Dr. Teerachot Siriburanon

Examination Committee: Prof. Michael Peter Kennedy, University College Dublin Prof. Andrea Bevilacqua, University of Padova

Copyright © 2019 by Yizhe Hu

To my lovely parents

"Simplicity is the hidden complexity."

# Contents

| C                                                                         | Contents                                                |                                                                       |                                                                                                  | i  |

|---------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----|

| A                                                                         | bstra                                                   | $\mathbf{ct}$                                                         |                                                                                                  | iv |

| 1                                                                         | Intr                                                    | oducti                                                                | on                                                                                               | 1  |

|                                                                           | 1.1                                                     | What                                                                  | is 5G Communications?                                                                            | 1  |

|                                                                           | 1.2                                                     | Why 2                                                                 | 8GHz Frequency Bands?                                                                            | 2  |

|                                                                           | 1.3                                                     | Why A                                                                 | Antenna Array, Beamforming, and CMOS Technology?                                                 | 4  |

|                                                                           | 1.4                                                     | Flicker                                                               | Phase Noise in CMOS Technology                                                                   | 6  |

|                                                                           | 1.5 Evolution of Theories on Flicker Noise Upconversion |                                                                       | ion of Theories on Flicker Noise Upconversion                                                    | 8  |

|                                                                           |                                                         | 1.5.1                                                                 | Phase Noise Model: ISF, Phasor Analysis, PPV, and Matrix $\ . \ . \ .$                           | 8  |

|                                                                           |                                                         | 1.5.2                                                                 | Flicker Noise Upconversion Analysis in Voltage-Biased Oscillators                                | 9  |

|                                                                           | 1.6                                                     | Thesis                                                                | Objectives and Outline                                                                           | 10 |

| 2 A Low-Flicker-Noise 30-GHz Class-F <sub>23</sub> Oscillator in 28-nm CM |                                                         |                                                                       |                                                                                                  |    |

|                                                                           | Imp                                                     | olicit R                                                              | esonance and Explicit Common-Mode Return Path                                                    | 12 |

|                                                                           | 2.1                                                     | Introd                                                                | uction $\ldots$ | 13 |

| 2.2 Flicker Noise Upconversion and Common-Mode Return Path in mmW C       |                                                         | Noise Up<br>conversion and Common-Mode Return Path in mmW Oscillators | 17                                                                                               |    |

|                                                                           |                                                         | 2.2.1                                                                 | Current Return Path in mmW Oscillators                                                           | 17 |

|                                                                           |                                                         | 2.2.2                                                                 | Flicker Noise Modulation and Upconversion                                                        | 20 |

|                                                                           |                                                         | 2.2.3                                                                 | Numerical Verification                                                                           | 24 |

|                                                                           |                                                         | 2.2.4                                                                 | Intuitive Understanding of Waveform-Shaping Due to Different Termi-                              |    |

|                                                                           |                                                         |                                                                       | nations of Harmonic Currents                                                                     | 30 |

|   | 2.3  | Circuit Description                                                    | 33        |

|---|------|------------------------------------------------------------------------|-----------|

|   |      | 2.3.1 Operational Principle of Class- $F_{23}$ Oscillator              | 35        |

|   |      | 2.3.2 Proposed Transformer with Embedded Decoupling Capacitor for Ex-  |           |

|   |      | plicit CM Return Path                                                  | 36        |

|   |      | 2.3.3 Third Harmonic Extraction Using Two-Stage 30-GHz PA(Buffer)      | 37        |

|   | 2.4  | Experimental Results                                                   | 39        |

|   | 2.5  | Conclusion                                                             | 41        |

| 3 | Intu | uitive Understanding of Flicker Noise Reduction via Narrowing of Con-  |           |

|   | duc  | tion Angle in Voltage-Biased Oscillators                               | 42        |

|   | 3.1  | Introduction                                                           | 43        |

|   | 3.2  | Non-Normalized ISF Extraction from PXF                                 | 45        |

|   |      | 3.2.1 Transimpedance in LTI System and Periodic Transimpedance in LPTV |           |

|   |      | System                                                                 | 45        |

|   |      | 3.2.2 ISF Extraction from Positive Sidebands of PXF $\ldots$           | 45        |

|   |      | 3.2.3 ISF Extraction from Negative Sidebands of PXF                    | 48        |

|   | 3.3  | Flicker Noise Up-conversion and Reduction                              | 50        |

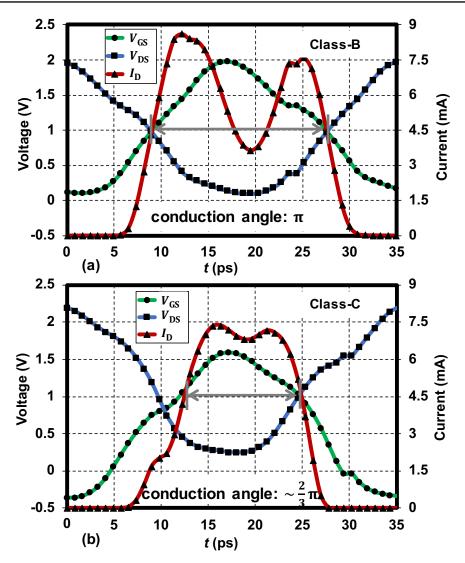

|   |      | 3.3.1 Voltage-Biased Oscillator in Class-B and Class-C                 | 50        |

|   |      | 3.3.2 Flicker Noise Reduction Mechanism in Class-C oscillators         | 51        |

|   | 3.4  | Conclusion                                                             | 57        |

| 4 | A 2  | .4 GHz, Low Flicker Noise Corner, Wide Tuning-Range Digitally Con-     |           |

| - |      | led Oscillator                                                         | <b>58</b> |

|   | 4.1  | Introduction                                                           | 59        |

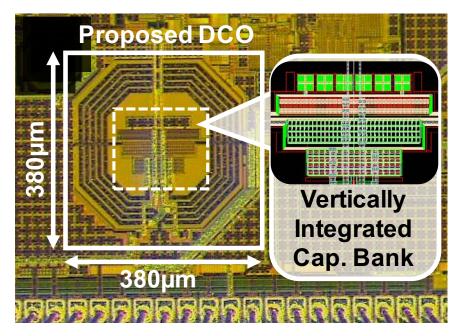

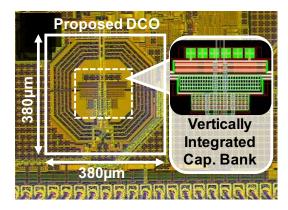

|   | 4.2  | Proposed Vertical Integration with Special Native Layer                | 60        |

|   | 4.3  | Flicker Noise Reduction via Narrowing Conduction Angle                 | 63        |

|   | 4.4  | Experimental Results                                                   | 65        |

|   | 4.5  | Conclusion                                                             | 66        |

| 5 | Cor  | clusion                                                                | 67        |

|   | 5.1  | Summary                                                                | 67        |

|   | 5.2  | Some Suggestions for Future Developments                               | 68        |

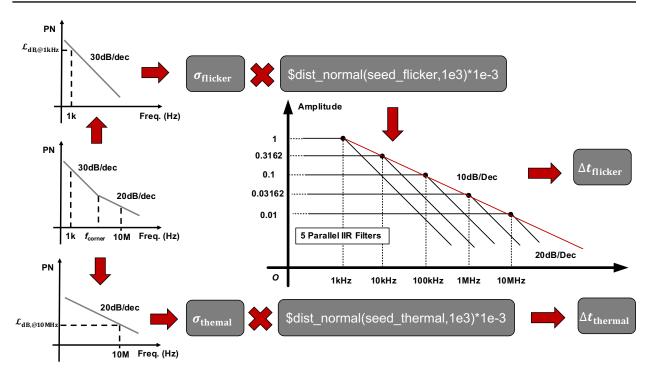

| A Phase Noise Modeling Based on Verilog-AMS                       |    |  |  |

|-------------------------------------------------------------------|----|--|--|

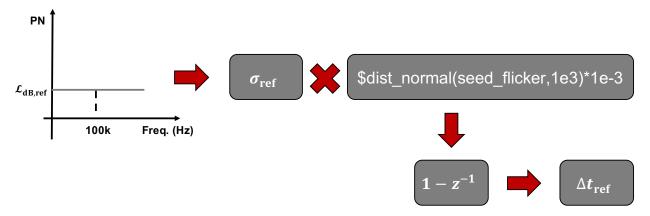

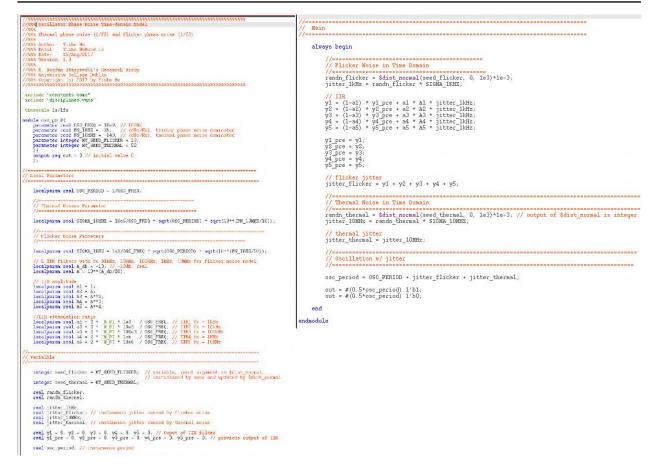

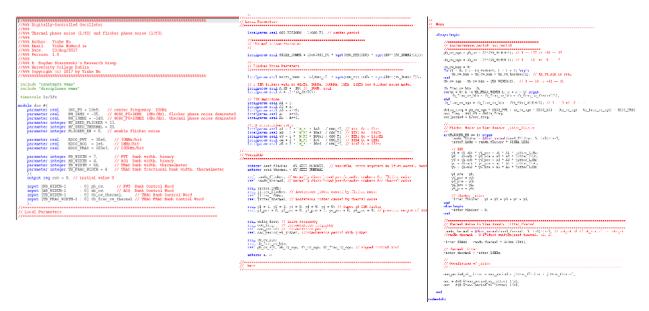

| A.1 Time-Domain Modeling of Flicker Phase Noise Using Verilog-AMS | 70 |  |  |

| A.1.1 Time-Domain Modeling of Thermal Phase Noise                 | 71 |  |  |

| A.1.2 Time-Domain Modeling of Flicker Phase Noise                 | 72 |  |  |

| A.1.3 Time-Domain Modeling of Reference Phase Noise               | 73 |  |  |

| Bibliography                                                      | 76 |  |  |

| List of Figures                                                   |    |  |  |

| List of Tables                                                    |    |  |  |

| List of Publications                                              |    |  |  |

| Chip Micrograph Gallery                                           |    |  |  |

| Acknowledgment                                                    |    |  |  |

| About the Author                                                  |    |  |  |

iii

# Abstract

The fifth generation (5G) cellular communications in millimeter-wave (mmW) bands (e.g. 28 GHz) place very tough requirements on phase noise (PN) of local oscillators (LO). However, in the advanced CMOS technology (e.g., 28nm, 16nm, 7nm, ...), the intrinsic 1/fcurrent noise of MOS transistor is increasingly worsening. It could adversely affect the PN of the LO significantly, especially the flicker PN, leading to a very high  $1/f^3$  PN corner (usually exceeding 1 MHz), which is difficult to be attenuated by a mmW PLL. On the other hand, the current literature is full of conflicts and confusing theories about the flicker noise upconversion, with a large number of ambiguities in the RF range, let alone in the mmW range. Thus, lowering the  $1/f^3$  PN and figuring out its actual mechanisms are highly desired for 5G mmW communications.

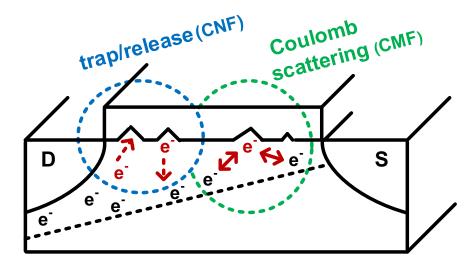

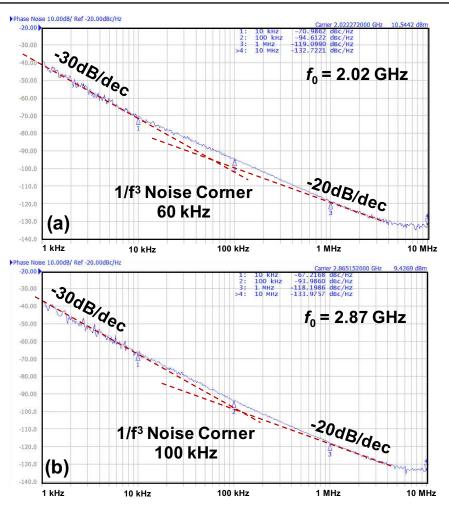

In this thesis, we demonstrate, for the first time ever, a 30 GHz oscillator with a record  $1/f^3$  PN corner of ~100 kHz, which is an order-of-magnitude better than all previous mmW oscillators. Thanks to the special considerations in the common-mode (CM) return path, 2nd harmonic resonance is accurately implemented in this 30 GHz oscillator. Firstly, we numerically verify and illustrate how the 2nd harmonic resonance could reduce the  $1/f^3$  PN, featuring the proposed simulation techniques of the 1/f noise modulation function (NMF) (i.e.,  $I_{1/f,rms}(t)$ ) and impulse sensitivity function (ISF) (i.e.,  $h_{DS}(t)$ ) (based on a periodic transfer function (PXF)). To physically explain the complex process of flicker noise modulation, a new 1/f model is introduced, considering both a carrier number fluctuation (CNF) and a correlated mobility fluctuation (CMF).

Further, we identify and numerically verify a new flicker noise reduction mechanism based on narrowing of a conduction angle, which has been presented in the literature but never properly explained. Through narrowing of the conduction angle, we demonstrate a wide-tuning range low  $1/f^3$  PN corner oscillator for 5G sub-6 GHz applications (i.e., Internet-of-Everything (IoE)).

# Introduction

#### 1.1 What is 5G Communications?

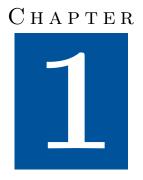

Wireless communications have started with a transmission of voice and messaging with limited data traffic, which were called 1st- and 2nd-generation networks (1G & 2G), as shown in Fig. 1.1(a). With the introduction of 3rd-generation networks (3G), consumers got the real taste of being able to access the Internet, surf the Web, engage in social media, and stream music, all while being mobile. Naturally, the desire for faster data rate suddenly surged, which was further boosted by the advent of the fourth generation networks (4G) in 2010. The 4G communications has been witnessing the explosive growth of mobile Internet, featuring extremely rapid updates of all kinds of smart-phones or other mobile devices.

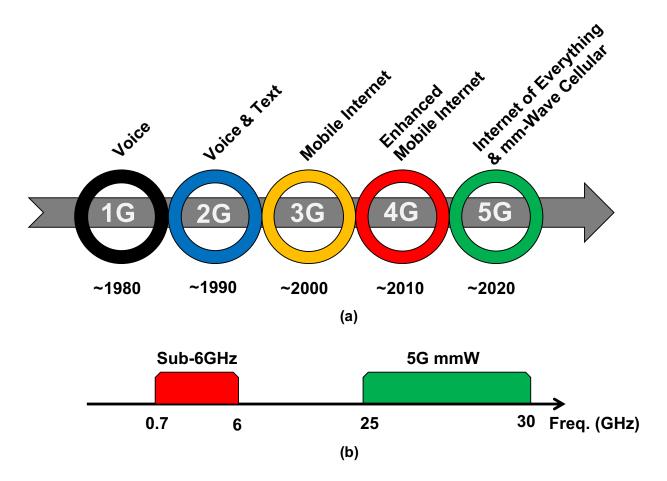

The fifth generation of wireless communications (5G) [1–7] is branching into two frequency bands: sub-6 GHz and near-millimeter wave (e.g., 28 GHz), shown in Fig. 1.1(b). The former, called Internet-of-Everything (IoE), is embracing all the existing technologies, including consumer applications (e.g., smart home, wearable technology,...), commercial applications (e.g., smart transportation, internet of health things,...), infrastructure applications (e.g.,

Figure 1.1: (a) Evolution of wireless communications (1G: voice, 2G: voice & text, 3G: mobile Internet, 4G: enhanced mobile Internet, 5G: Internet-of-Everything (IoE) & millimeter-wave (mmW) cellular). (b) Crowded sub-6 GHz frequency band range and brand-new mmW band range for 5G communications.

smart city, environmental monitoring,...), and industrial of Internet-of-Things (see Fig. 1.2). However, due to the physical limitations and other existing radio standards, the increasingly crowded sub-6GHz bands find it difficult to meet the requirement of the data rate growth. In particular, high-definition (HD) mobile video, virtual reality (VR), and augmented reality (AR) are becoming the main drivers of 5G cellular communications, significantly increasing the requirement of data rate [1].

#### 1.2 Why 28GHz Frequency Bands?

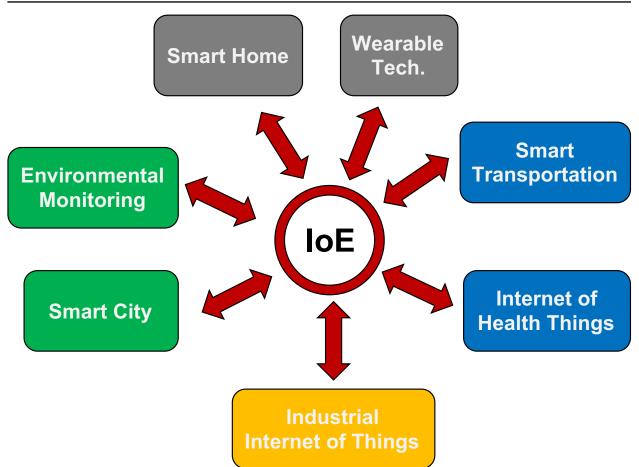

As shown in Fig. 1.3, the mobile video traffic is forecast to account for 75% of all the data traffic in 2023 [1]. Its estimated compound annual growth rate (CAGR) would be up at

Figure 1.2: Some of the trends of 5G communications: Internet-of-Everything (IoE), embracing all existing radio techniques at sub-6GHz frequency bands.

almost 50% from 2017 to 2023. The data rate requirement of HD mobile video, virtual reality (VR), and augmented reality (AR) could be up to 10Gb/s, which forces the 5G cellular to explore brand-new near-mmW bands.

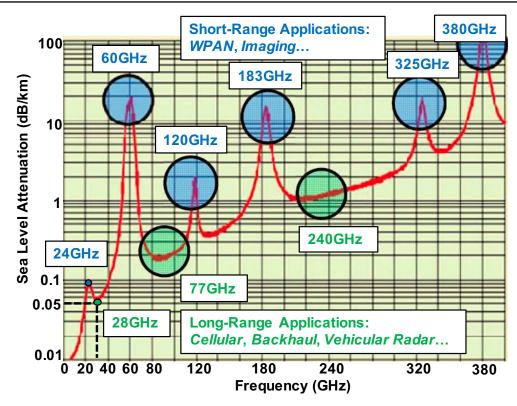

Obviously, the mmW cellular networks will be the most prominent feature of 5G communications. This makes it physically different from previous generations of wireless communications. However, this also poses a main concern of atmospheric absorption of mmW frequencies. Fig. 1.4 shows the atmospheric absorption properties of sub-terahertz radio spectra. The frequency bands with extremely high-attenuation properties (i.e., 60, 120, 183, 325, and 380 GHz) are allocated for short-range applications, such as wireless personal area network (WPAN) and imaging, while the 28, 77, and 240GHz frequency bands with relatively low space attenuation would be suitable for long-range applications, such as cellular, backhaul, and vehicular radar [3]. Especially, among all the mmW bands, the 28GHz band enjoys

Figure 1.3: (a) Estimated compound annual growth rate (CAGR) of mobile traffic by application from 2017 to 2023, in which the CAGR of mobile video will be up to 50% [1]. (b) Mobile video traffic is expected to account for 75% of all mobile-data traffic in 2023.

the lowest attenuation, thus placing it among the best candidates for 5G mmW cellular communications [4].

#### 1.3 Why Antenna Array, Beamforming, and CMOS Technology?

The adoption of 28 GHz can enable a high-gain and small-size of antenna array, which could be fabricated on a printed circuits board (PCB) [8–10] or even on-chip [7] for cellular networks due to its wavelength being an order of magnitude smaller than that of the sub-6 GHz systems. Benefiting from the miniaturized antenna array, a beamforming technique was introduced in 5G mmW cellular for creating electronically-controlled directional links [8–13]. It promotes energy efficiency, massive MIMO (multiple-input and multiple-output), and delivers enough output power, further mitigating the space attenuation of 28 GHz frequency bands. Three possible architectures have been under intensive research in recent years, including RF beamforming [8–11], LO beamforming [13], and digital beamforming [12]. An RF beamformer can be directly added to an existing receiver/transmitter architecture, supporting wide-band signals (using variable true-time-delay (TTD) where applicable) or narrow-band signal (using variable phase shifter). However, since the low-loss, linear, and compact RF variable delay is difficult to be implemented in integrated circuits (ICs), RF phase-shifters [8–11] are the

Figure 1.4: Atmospheric absorption across mmW frequencies in dB/km. The frequency bands of 28GHz shows the smallest space attenuation of all mmW bands, a best candidate for mmW cellular communications (Modification of Fig. 2 in [3]).

mainstream, thus limiting the signal bandwidth. Instead of shifting the phase of an RF transmitting/receiving signal, it would be easier to shift the phase of the LO [13]. But, LO phase shifting is still an inherently narrow-band approach, and it is also challenging to do LO routing for large arrays. Digital beamforming [12] has the highest capacity and flexibility, but has to handle a large number of digital I/Os, thus consuming large power.

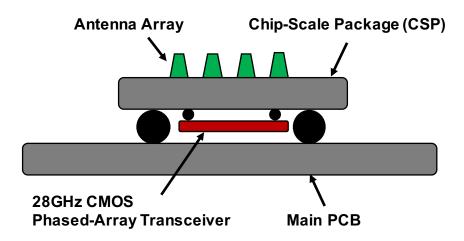

The beamforming technique with an antenna array (power combining of the transmitted signal can be performed in space) can relax the requirement of a single power amplifier (PA) in the array. Thus, the 28 GHz CMOS PAs [14–16] (or CMOS RF/mm-Wave-DACs [17,18]) are becoming increasingly popular, which has been traditionally hampered by its limited breakdown voltage and poor capability for current handling. On the other hand, the technique of beamforming will benefit from the high-integration of CMOS technology, which enables all kinds of digital calibration algorithms. Fig. 1.5 shows a compact 28 GHz phased-array transceiver scheme [9], in which a miniaturized antenna array and a CMOS RFIC are built on two sides of a chip-scale package, respectively.

Figure 1.5: A compact 28 GHz phased-array transceiver scheme: an antenna array is built on one-side of a chip-scale package, while the 28 GHz CMOS phased-array transceiver is packaged as a flip-chip on the other side [9].

#### 1.4 Flicker Phase Noise in CMOS Technology

No matter what architectures of beamforming will be employed in the CMOS phasearray transceiver, the quality of their 28 GHz local oscillators could be a bottleneck limiting further improvements in the data rate. As a result, the 5G mmW cellular will place very tough requirements on phase noise (PN) of local oscillators due to the complex modulation scheme [51].

The quality factor (Q) of capacitor banks will significantly decrease when the resonating frequency of oscillators is above 20 GHz [25], worsening the thermal PN region of mmW oscillators. Several techniques have been proposed to improve the situation: 1) multi-core oscillators [19, 20, 22], 2) harmonic-extraction based on 2nd [21, 22] or 3rd [23] harmonic, and 3) mmW oscillators injection-locked by RF oscillators [24–28]. For multi-core oscillators, the thermal PN will be improved in theory by  $10 \cdot \log_{10} N$  dB when N cores are inter-connected at the cost of  $N \times$  power and area. Operating at a lower frequency (e.g., < 20GHz) and extracting its own higher harmonics, the harmonic-extraction oscillators could have good thermal PN due to the high-Q tank at the low frequency. Unfortunately, the additional harmonic extractors may burn more power than the oscillators themselves. Replacing the harmonic extractor (burning high power) with a high-frequency oscillator (low power), then injecting a low frequency signal (good thermal PN) into the high frequency oscillator, the injection locking technique is able to achieve low thermal PN and low power at the same

Figure 1.6: Challenges of a conventional 30GHz ADPLL architecture for 5G communications.

time. However, the PVT (process, voltage, temperature) robustness and locking range are challenging for this technique [29–31].

Despite these  $1/f^2$  PN improvements in mmW oscillators, their  $1/f^3$  PN corner seems to always exceed 1 MHz per survey in [51] (see Chapter 2). Furthermore, the intrinsic 1/f current noise of MOS transistor is worsening with the CMOS technology advancements [32]. Both the carrier number fluctuation (CNF) and correlated mobility fluctuation (CMF) mechanisms of 1/f noise show largely adverse effects in shorter channel-length devices [33]. The increasingly worse 1/f current noise could up-convert to  $1/f^3$  PN, leading to a further increase in the  $1/f^3$  PN corner.

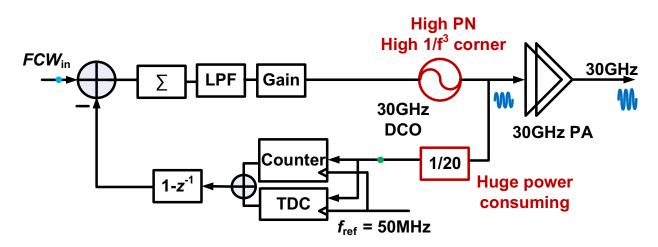

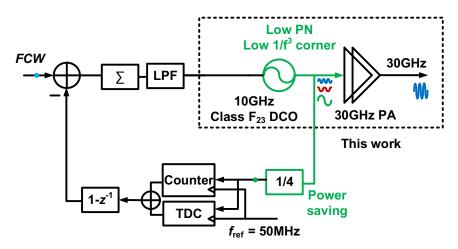

Fig. 1.6 shows a possible conventional architecture of an all-digital phase locked loop (ADPLL) for 5G mmW communications. The bandwidth (BW) of this ADPLL should be maintained quite narrow to prevent reference noise and time-to-digital converter (TDC) noise from dominating its integrated jitter especially amplified by the large frequency ratio N (e.g., 30GHz/50MHz = 600) at mmW. The limited BW of mmW PLLs would fail to effectively attenuate the flicker PN of the mmW oscillator, worsening the total integrated jitter. Thus, the techniques to reduce the 1/f noise upconversion are highly desired for 5G mmW communications.

#### 1.5 Evolution of Theories on Flicker Noise Upconversion

#### 1.5.1 Phase Noise Model: ISF, Phasor Analysis, PPV, and Matrix

To be able to significantly reduce the  $1/f^3$  PN, a deep understanding of the flicker noise upconversion mechanism is necessary. However, the flicker PN theory was not effectively developed [34] until an impulse sensitivity function (ISF) was first introduced by Hajimiri and Lee [35] in 1999. The ISF theory suggests that a symmetric effective ISF (eISF) would suppress the flicker noise upconversion, which could be realized by forcing symmetries in the oscillating waveform. However, the theory was silent on how to achieve that symmetric oscillation waveform. In fact, we will demonstrate in this thesis that, even for asymmetric waveforms (i.e., lack of 2nd harominc resonance), narrowing of conduction angle or adding additional drain-gate phase-shift with consideration of 2nd harmonic termination can also suppress the flicker noise upconversion.

In addition to the ISF theory, other well-known PN theories are listed as follows:

1) Phasor-based analysis [36]. It has been demonstrated to be equal to the ISF theory in the thermal PN range, but the flicker PN analysis is still missing there.

2) Perturbation projection vector (PPV) [37]. The PPV analysis could be seen as an extended (or more rigorous) version of ISF, considering the time-shift of ISF itself when noise is injected into a LC tank [38, 39], which enables the ISF to predict the injection locking phenomenon [39–41]. However, for thermal PN analysis using PPV shows almost the same results as with ISF [38]. Also, there is no discussion in [37] on the flicker noise upconversion.

3) Matrix analysis [42]. Both thermal and flicker PN analyses are discussed in [42]. However, the method neglects the consideration of even-harmonic waveform and commonmode (CM) tank, which are seen as the main contributors to the flicker PN [51]. An interesting point was proposed in which the non-resistive path of 3rd harmonic (any higher odd-order) current will not introduce any flicker noise upconversion.

In summary, the ISF theory could be the most promising method to explain both qualitatively and quantitatively the flicker noise upconversion and reduction mechanisms as long as we can accurately understand and simulate it [51,86].

#### 1.5.2 Flicker Noise Upconversion Analysis in Voltage-Biased Oscillators

Two groundbreaking architectures of the 2nd harmonic resonance (i.e., tail-filtering) [45,46] and class-C operation (i.e., narrowing of conduction angle) [47] have shown quite good thermal and flicker PN performance. In recent years, the technique of 2nd harmonic resonance started to employ an implicit parallel-LC common-mode (CM) tank [44,49–53] or series-LC CM tank [54] (only improving the flicker PN) to save area, while the technique of class-C mode of operation attempted to add two "controlled switches" (e.g., NMOS-based [55], PMOS-based RC coupling [56], and PMOS-based transformer coupling [58]) under the cross-coupled pair to decrease the conduction angle.

As the supply voltage decreases in the advanced CMOS technology, the tail-current source in an LC-tank oscillator would partially enter the triode region, causing only a small amount of flicker noise of the tail-current source to upconvert to flicker PN [43,44]. In recent years, directly replacing the tail-current source with switched tail-resistors (or no tail-resistor at all) has become increasingly popular due to the elimination of one of the most dominant sources of 1/f noise upconversion as well as suitability for low supply operation. These types of oscillators are called voltage-biased oscillators. Consequently, the study of flicker noise upconversion then focuses mainly on the 1/f noise from the cross-coupled pair. The pioneering works of [32, 64, 65] have tried to demonstrate that the non-zero dc value of the effective ISF comes from the 3rd harmonic current entering the capacitive path. Nevertheless, the theory totally neglects the effects of 2nd harmonic current, which has already manifested its significant effects on the flicker noise upconversion [45,46]. Shahmohammadi et al. claims that the asymmetry between rising and falling portions of the oscillation waveform results in 1/f noise upconversion, which is a consequence of the 2nd harmonic current entering a non-resistive path while the 3rd harmonic current is shown as benign. However, this claim lacks a rigorous numerical verification, and also it cannot explain the good  $1/f^3$  PN corner in oscillators with the narrowed conduction angle but with no special considerations of the 2nd harmonic resonance [47, 55–58, 61–63].

The current literature on the theory of flicker noise upconversion suffers from the following drawbacks: 1) Some of the authors merely mention various qualitative aspects [34, 45, 46, 49, 55, 56, 58–60], but rigorous quantitative analysis is missing. 2) Some pioneering quantitative research is conducted in [32, 43, 44, 64, 65], but they neglect the importance of implicit CM

tank and further they employ oversimplified ISF and flicker noise modulation function (NMF), which might damage the credibility of their theories to some extent. Therefore, a unified theory of flicker noise up-conversion and reduction is highly desired, which can perform rigorous numerical verification (e.g., numerical verification of PN@ 10kHz between calculation and simulation) and intuitively explain all the flicker noise reduction mechanisms, such as the 2nd harmonic resonance and narrowing of conduction angle.

#### **1.6** Thesis Objectives and Outline

In this thesis, we claim the first-ever demonstration of a 30 GHz oscillator with an ultralow flicker noise corner ( $\sim 100 \, \text{kHz}$ ) featuring a special consideration of the CM current return path, which up to now has been neglected by RF/mmW designers. Based on the proposed simulation techniques of ISF (derived from positive sidebands of periodic transfer function (PXF)) and flicker NMF, we first rigorously verify in a numerical manner the flicker noise upconversion and reduction mechanisms against the advanced TSMC 28 nm LP CMOS technology. We identify that the 2nd harmonic current entering a non-resistive path (i.e., causing asymmetries in rising and falling edges of the oscillation waveform) is the main contributor to the 1/f noise upconversion, while the 2nd harmonic resonance (i.e., making symmetric the rising and falling parts of the oscillating waveform) and the narrowing of conduction angle but with no consideration to the 2nd harmonic resonance (i.e., decreasing modulated 1/f noise *exposure* to asymmetric rising and falling waveform) are the two effective ways to lower the  $1/f^3$  PN. To intuitively and physically understand the complex behavior of flicker noise modulation in oscillators, the carrier number fluctuation (CNF) and correlated mobility fluctuation (CMF) mechanisms are introduced in analyzing the flicker noise upconversion. Based on the newly identified  $1/f^3$  PN reduction mechanism of narrowing of conduction angle, a 2.4 GHz transformer-based digitally controlled oscillator (DCO) is proposed, achieving around  $100 \,\mathrm{kHz} \, 1/f^3$  PN corner across the whole wide tuning range (TR) up to 35%, while its intrinsic start-up problem of narrowing the conduction angle is mitigated by the passive gain of a 2:3 transformer.

The rest of thesis is organized as follows: Chapter 2 shows an analysis and design of the low-flicker-noise 30 GHz class-F<sub>23</sub> oscillator in 28-nm CMOS using implicit resonance and explicit common-mode return path. The newly identified flicker noise reduction mechanism

of narrowing the conduction angle is revealed in Chapter 3. It also proposes a comprehensive analysis method of flicker noise upconversion and reduction based on simulated flicker NMF and ISF. Based on the narrowing of conduction angle technique, a 0.3 V, 35% TR,  $60 \text{ kHz} 1/f^3$  PN corner DCO with vertically integrated switched capacitor banks is demonstrated in Chapter 4. Chapter 5 concludes the thesis and gives future research suggestions.

A Low-Flicker-Noise 30-GHz Class-F<sub>23</sub> Oscillator in 28-nm CMOS using Implicit Resonance and Explicit Common-Mode Return Path

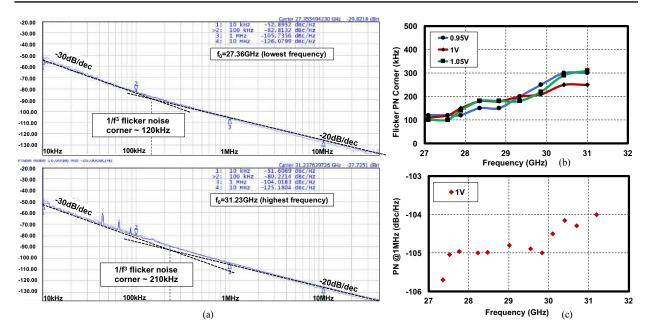

This chapter presents a mm-Wave frequency generation stage aimed at minimizing phase noise (PN) via waveform shaping and harmonic extraction while suppressing flicker noise upconversion via proper harmonic terminations. A second-harmonic resonance is assisted by a proposed embedded decoupling capacitor inside a transformer for the explicit commonmode current return path. Class-F operation with third-harmonic boosting and extraction techniques allow maintaining the high quality factor of a 10 GHz tank at the 30 GHz frequency generation. We further propose a comprehensive quantitative analysis method of flicker noise upconversion mechanism exploiting latest insights into the flicker noise mechanisms in nanoscale short-channel transistors, and it is numerically verified against foundry models. The proposed 27.3–31.2 GHz oscillator is implemented in TSMC 28 nm CMOS. It achieves PN of -106 dBc/Hz at 1 MHz offset and FoM of -184 dBc/Hz at 27.3 GHz. Its flicker PN  $(1/f^3)$  corner of 120 kHz is an order-of-magnitude better than currently achievable at mmW.

#### 2.1 Introduction

Traditional cellular bands, i.e., < 6 GHz, suffer from severe bandwidth (BW) congestion and can barely cope with the increasing demands for data. Consequently, the fifth generation (5G) of cellular communications starts to utilize a lower range of millimeter-wave (mmW) frequency bands, e.g., 28 GHz [1]. To support higher data rates, more complex modulation schemes are being introduced, thus placing challenging requirements on phase noise (PN) of local oscillators. It is well known that for mmW oscillators, the quality (Q) factor degradation of a tuning varactor or a switched-capacitor (sw-cap) tuning network leads to worse PN in the thermal  $(1/f^2)$  noise region. To mitigate such degradation, the following solutions have been devised: the oscillator's resonant frequency gets lowered but then increases via a frequency multiplier, such as a doubler/quadrupler in [21] and [22], multi-core oscillators [22], sub-harmonic injection locking [25, 66], and transformer-based class-F oscillator with a tuned power amplifier (PA) to extract its 3rd harmonic [23].

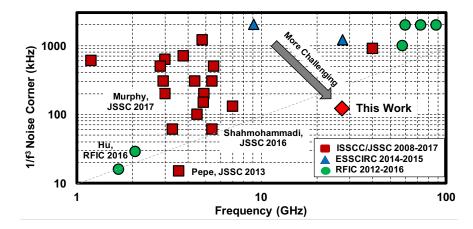

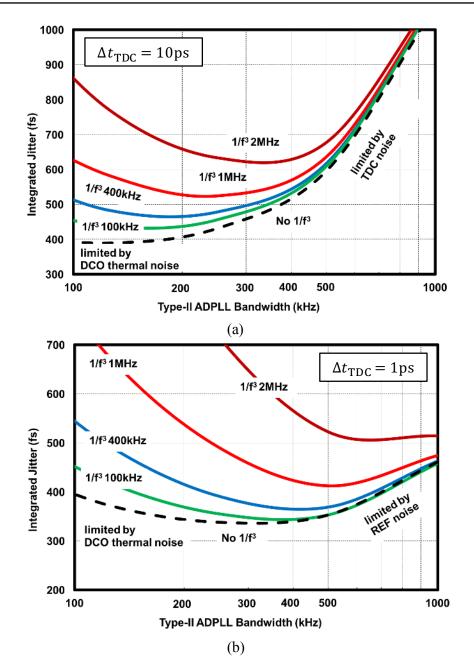

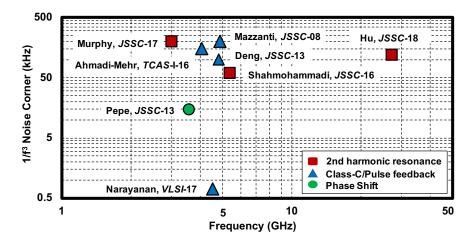

Yet, despite those PN improvements in the  $1/f^2$  region, the flicker PN  $(1/f^3)$  corner of >10 GHz oscillators appears to always exceed  $\sim$ 1 MHz, as surveyed in Fig. 2.1. Moreover, the underlying cause, i.e., the flicker (1/f) noise of MOS transistors, tends to worsen as CMOS scales, which will further degrade the integrated PN, thus limiting the achievable data rates in mmW transceivers. Considering an example of a mmW type-II all-digital PLL (ADPLL) shown in Fig. 2.2, the loop BW needs to be limited to  $< 400 \,\mathrm{kHz}$  to suppress the typical 10 ps quantization noise of its time-to-digital converter (TDC), according to the system simulations in Fig. 2.3 (a). Even with the TDC resolution as fine as 1 ps [see Fig. 2.3 (b)], the loop BW must still be maintained quite narrow in order to prevent the reference noise from dominating the ADPLL's PN. This is due to the high multiplication ratio N of mmW PLLs (e.g., N = 600for a 30 GHz oscillator locked to a typical  $f_{\rm ref} = 50$  MHz reference). Even the best realistic attempts at reducing the remaining ADPLL PN contributors will unfortunately leave the oscillator's  $1/f^3$  PN as the limiting factor preventing from breaking through the 520 fs and 410 fs integrated jitter limits for the TDC resolution of 10 ps (typical state-of-the-art) and 1 ps (yet to be achieved), respectively. Consequently, techniques to lower the  $1/f^3$  PN are highly desired for mmW generation.

Recent studies [44, 49, 65] deal with the flicker noise reduction in voltage-biased RF oscillators, i.e., in which the conventional mechanism of 1/f-noise upconversion via the

Figure 2.1: Survey of  $1/f^3$  corner of state-of-the-art RF and mmW oscillators.

Figure 2.2: An intended architecture of a 30 GHz ADPLL focused on its low-power and high-performance aspects.

tail current source does not appear anymore [43]. In [64, 65], it is suggested that the non-zero dc value of the effective impulse sensitivity function (ISF) is mainly caused by a 3rd harmonic current entering a capacitive path, resulting in the  $1/f^3$  PN degradation. However, the effect of 2nd harmonic current is entirely neglected. Shahmohammadi *et al.* [44] explains that the 1/f noise up-conversion is due to an asymmetry between rising and falling edges of the tank's voltage waveform, which is a consequence of a 2nd harmonic current ( $I_{H2}$ ) entering the capacitive path. The effects of the 3rd harmonic current are shown as benign. That was further experimentally supported in [49], but the rigorous quantitative analysis of flicker noise upconversion is still missing in [44, 49]. It appears that the lack of a complete numerical verification and the over-simplification of the flicker noise model employed cause some contradictions and ambiguities in the currently available theory of

Figure 2.3: Simulated integrated phase noise (translated to jitter) across loop bandwidth of a type-II 30 GHz ADPLL for various  $1/f^3$  noise corners of the oscillator. Conditions:  $PN_{DCO}$  @10 MHz = -120dBc/Hz,  $f_{ref} = 50$ MHz,  $\sigma_{ref} = 1$ ps. TDC resolution: (a) 10 ps, and (b) 1 ps.

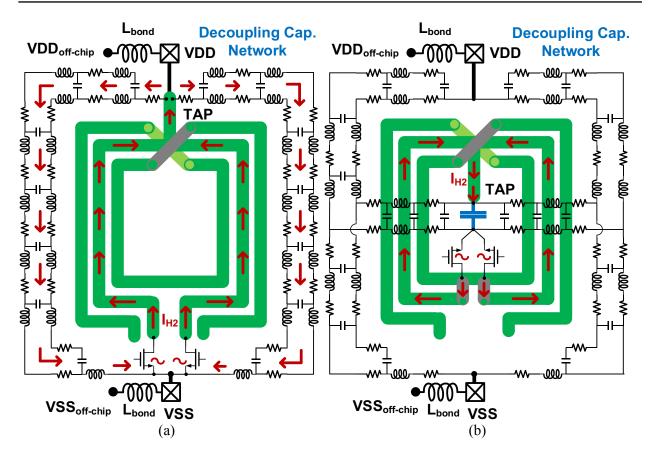

flicker noise upconversion and reduction mechanism. Moreover, a direct translation of the above techniques [44, 49, 65] into mmW does not appear so straightforward. For example, employing a high-frequency oscillator with a one-turn inductor [67] or a conventional 1:2 transformer [44, 48] could suffer from high  $1/f^3$  PN corner due to the uncontrolled 2nd

Figure 2.4: Diagram of a conventional voltage-biased mmW oscillator with a tail inductor further showing its parasitic common-mode return path.

harmonic current return path of the decoupling capacitor, as shown in Figs. 2.4 and 2.5(a), thus shifting the expected common-mode (CM) resonant frequency.

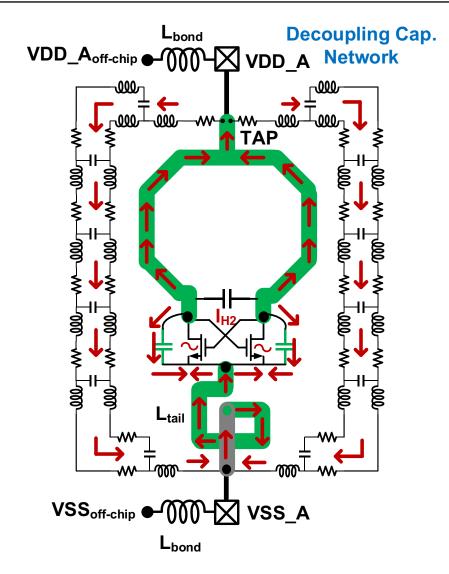

This thesis proposes a 30 GHz frequency generation scheme shown in Fig. 2.6 using a 3rd harmonic extraction from a class- $F_{23}$  oscillator operating at 10 GHz fundamental. It features a special 1:2 transformer including a proposed embedded decoupling capacitor for the precise control of the CM current return path, as illustrated in Fig. 2.5(b) [50]. Its PN in the  $1/f^2$  thermal region is kept low via the 3rd harmonic resonance, and its  $1/f^3$  PN corner is greatly improved (by an order-of-magnitude vs. state-of-the-art) via a precise implementation of the 2nd harmonic resonance and the proposed explicit CM return path.

Figure 2.5: (a) Conventional class- $F_{23}$  oscillator w/o the well-controlled CM return path [44, 48]. (b) Proposed structure to control the CM return path in which the 1:2 transformer features an embedded decoupling capacitor (blue capacitor) [50].

In Section 2.2, the 1/f-noise reduction mechanism based on the 2nd harmonic resonance in mmW voltage-biased oscillators is numerically verified in the 28-nm technology. Details of the proposed 30 GHz frequency generation scheme, focusing on an accurate implementation of the 2nd harmonic resonance, are revealed in Section 2.3. In Section 2.4, the proof-of-concept 30 GHz oscillator demonstrates the lowest  $1/f^3$  PN corner of 120 kHz among mmW oscillators.

### 2.2 Flicker Noise Upconversion and Common-Mode Return Path in mmW Oscillators

#### 2.2.1 Current Return Path in mmW Oscillators

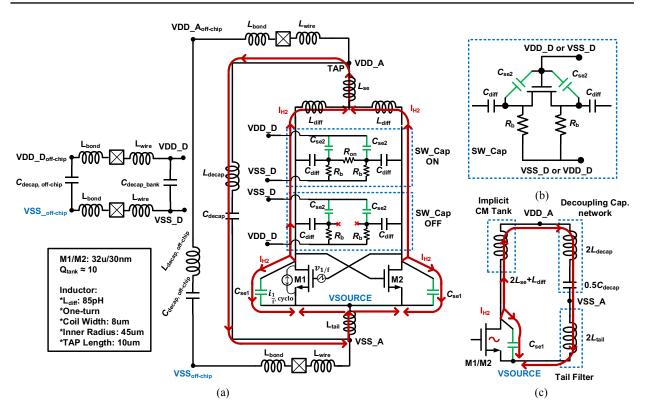

The conventional voltage-biased mmW oscillator with a one-turn inductor [see Fig. 2.4] can be modeled as in Fig. 2.7 (a). The circuit includes a cross-coupled pair (M1, M2, with

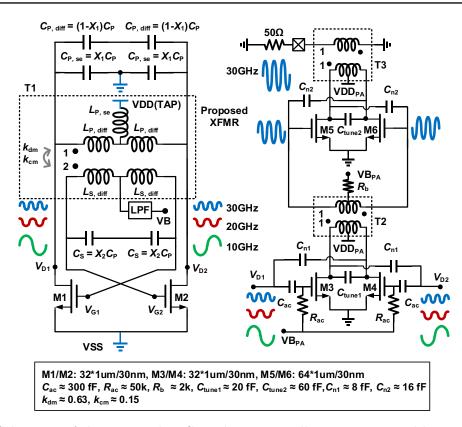

Figure 2.6: Schematic of the proposed 30 GHz class- $F_{23}$  oscillator using second-harmonic resonance and third-harmonic extraction.

their parasitic capacitances  $C_{se1}$ ), switched-capacitor (sw-cap) bank with its elements shown in Fig. 2.7 (b) ( $C_{diff}$  and the switch parasitics  $C_{se2}$ ), main inductor ( $L_{diff}$ ,  $L_{se}$ ), decoupling capacitor network for the supply/ground ( $C_{decap}$  and its parasitic inductance  $L_{decap}$ ), and tail inductor ( $L_{tail}$ ). Two supplies are used, i.e., "analog" supply (VDD\_A/VSS\_A) for the oscillator core and "digital" supply (VDD\_D/VSS\_D) for the sw-cap bank. In addition,  $L_{bond}$  is used to model wire-bonding inductors from the external supply (VDD\_A<sub>off-chip</sub>, VDD\_D<sub>off-chip</sub>, and VSS<sub>off-chip</sub>) to the IC wirebonding pad (PAD), while  $L_{wire}$  models the interconnecting wire inductances from PAD to the local supplies and grounds.  $C_{decap\_bank}$ is used to model a local decoupling capacitor for the sw-cap bank, while  $C_{decap, off-chip}$  and  $L_{decap, off-chip}$  model the off-chip decoupling capacitor and its parasitic inductance, respectively.

In RF, and especially mmW circuits, defining local supply points, i.e., VDD\_A or VSS\_A, as ac grounds is not so straightforward. To start with, "current return path" should be considered. The differential-mode (DM) return path is for the DM current (e.g.,  $I_{\rm H1}$ ,  $I_{\rm H3}$ ) from the drain of M1 to the drain of M2, and then from the source of M2 back to source

Figure 2.7: (a) Model of a conventional 30 GHz oscillator w/ tail filtering and its CM return path. (b) Conventional switched-capacitor tuning element. (c) Half-circuit of the CM return path.

of M1, and vice versa. Thus, the (half-circuit) tank inductance in DM  $(L_{\rm dm})$  is simply  $L_{\rm diff}$ , while the DM capacitance  $(C_{\rm dm})$  is dominated by  $C_{\rm diff}$  when sw-cap is on and by the parasitic  $C_{\rm se2}$  when sw-cap is off. It was only very recently that the common-mode return path got introduced into the RF oscillator design for the purpose of  $1/f^2$  and  $1/f^3$  PN reductions [44], [49], and [48]. The path carries the CM current (e.g.,  $I_{\rm H2}$ ) from the drain of M1/M2 to the source of M1/M2, and then back around. Hence, it is more appropriate to take the source node of the cross-coupled pair (VSOURCE) as a reference rather than VSS\_A for the CM return path analysis. One part of the CM return path includes the implicit CM tank, decoupling capacitor network, and tail filter, while the other part goes directly through the transistor's intrinsic capacitance  $C_{\rm se1}$  (=  $C_{\rm ds1} + C_{\rm gs2}$  for CM signal), shown in Fig. 2.7(c). Note that the parasitic single-ended capacitance of the sw-cap bank ( $C_{\rm se2}$ ) cannot be readily seen by the CM current, irrespective of whether the switch is on or off, since it is connected to a different supply (i.e., "digital") through a large wirebonding inductance. Therefore, for most properly constructed oscillators, their implicit CM tank would comprise only the CM

inductance of the main inductor. The on-chip decoupling capacitor network ( $L_{decap}$ ,  $C_{decap}$ ) needs to be properly constructed to provide a tight local return path for the CM current. However, its parasitic inductance  $L_{decap}$  is typically neglected by RF oscillator designers, often leading to detrimental effects on the flicker noise upconversion [48].

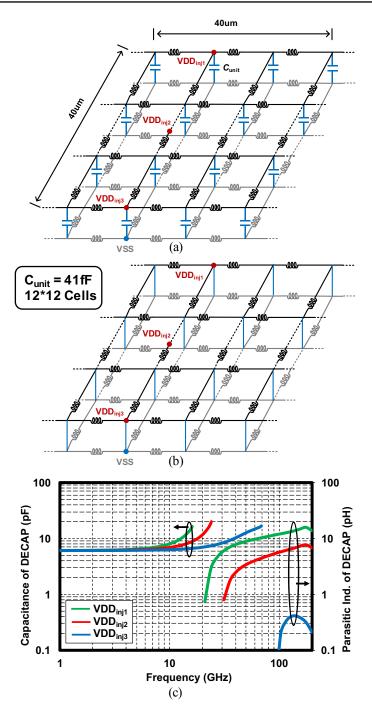

This consequence of neglecting the  $L_{decap}$  effects is becoming more critical now for mmW oscillator designs. As shown in Fig. 2.8(a),  $L_{decap}$  is modeled for different considerations of supply injection points (VDD<sub>inj1,2,3</sub>). According to electromagnetic simulations in Fig. 2.8(c), the parasitic inductance could be neglected only when the injection point (VDD<sub>inj3</sub>) is physically close to VSS. Fig. 2.8(b) offers an intuitive explanation. At very high frequencies, all the  $C_{unit}$  capacitors are seen as a short and so the LC network becomes inductive, resulting in VDD<sub>inj3</sub> having the shortest return path. However, in the conventional mmW oscillator with a one-turn inductor, the supply injection point [VDD\_A as shown in Fig. 2.7(a)] is physically far from VSS\_A, thus introducing a significant inductance (several hundred pH). Finally, a parallel resonant LC tank can be seen by the CM current, [see Fig. 2.7(c)], in which the total CM inductance  $L_{cm}$  can be described as  $L_{diff} + 2L_{se} + 2L_{decap} + 2L_{tail}$ , while the total CM capacitance  $C_{cm}$  is only  $C_{se1}$ . Obviously, both the parasitic  $L_{decap}$  and the deliberate  $L_{tail}$  have a large influence on the CM resonant frequency (i.e.,  $1/(2\pi\sqrt{L_{cm}C_{cm}}))$  in the mmW oscillator.

#### 2.2.2 Flicker Noise Modulation and Upconversion

According to the theory of impulse sensitivity function (ISF) [35], the flicker noise upconversion from  $M_{1/2}$  in Fig. 2.7 to phase noise involves two steps: 1) low-frequency voltage noise at the gate,  $v_{1/f}$  at  $\Delta \omega$  (e.g., 10 kHz), is modulated to cyclostationary current noise  $i_{1/f,cyclo}$  around different harmonics  $k\omega_0 \pm \Delta \omega$  through a noise modulation function (NMF) and 2) the current noise  $i_{1/f,cyclo}$  turns into phase noise through its corresponding ISF.

It is well known that the flicker NMF is modeled by a time-varying transconductance [44]. However, this model only considers the 1/f noise mechanism due to the carrier number fluctuation (CNF), which means the carriers will be randomly trapped and released by impurities on the Si/SiO<sub>2</sub> interface. As CMOS technology scales, another 1/f noise mechanism, called correlated mobility fluctuation (CMF), is becoming increasingly important since the trapped electrons in a short channel will have a larger influence on Coulomb scattering of

Figure 2.8: (a) Decoupling capacitor network for the proposed mmW oscillator. (b) High-frequency model of the decoupling capacitor network. (c) Effective parasitic inductance at different supply injection points.

neighboring free electrons, thus changing the average electron mobility (see Fig. 2.9). A more accurate 1/f noise model for the nanoscale CMOS considering both CNF and CMF was

Figure 2.9: Newly discovered flicker noise mechanism in nanoscale CMOS [33].

verified in [33], which is described as:

$$\overline{I_{1/f}^2} = \overline{V_{1/f}^2} \times \left(g_{\rm m} + \Omega I_{\rm D}\right)^2 \tag{2.1}$$

where  $V_{1/f}^2 = \frac{K}{WL\Delta\omega}$  is the power spectral density (PSD) of flat-band voltage, K and  $\Omega$  (unit:  $V^{-1}$ ) are process parameters. The first and second terms in parentheses represent CNF and CMF, respectively. Thus, the flicker NMF m(t) in nano-scale CMOS could be modified as periodically modulated transconductance and harmonic current:

$$m(t) = G_{\rm m}(t) + \Omega I_{\rm D}(t) \tag{2.2}$$

where  $G_{\rm m}(t)$  and  $I_{\rm D}(t)$  can be obtained by applying the discrete steady-state waveform point of  $V_{\rm GS}$ ,  $V_{\rm DS}$  to dc simulations.

Assume the flicker gate-voltage noise  $v_{1/f}$  at  $\Delta \omega$  (e.g., 10 kHz) in M<sub>1/2</sub> is expressed as

$$v_{1/f}(t) = \sqrt{2V_{1/f,\,\mathrm{rms}}\cos(\Delta\omega t + \gamma)} \tag{2.3}$$

where  $V_{1/f, \text{rms}}$  is rms value of  $\overline{V_{1/f}^2}$ , and  $\gamma$  is an initial random phase. Thus, the cyclostationary

flicker noise current is as follows:

$$i_{1/f,\text{cyclo}}(t) = v_{1/f}(t) \times m(t)$$

=  $\sqrt{2}I_{1/f,\text{rms}}(t)\cos(\Delta\omega t + \gamma)$  (2.4)

where  $I_{1/f,\rm rms}(t)$  ( $\approx V_{1/f,\rm rms} \times m(t)$ ) is the periodically modulated rms value of flicker current noise. It can be directly simulated by dc/NOISE simulations using the discrete waveform point of  $V_{\rm GS}$  and  $V_{\rm DS}$  from periodic steady-state (PSS) simulations, while the introduced model  $V_{1/f,\rm rms} \times m(t)$  is mainly used to intuitively and physically explain the complex behavior of  $I_{1/f,\rm rms}(t)$  in the large-signal operation and advanced CMOS technology.

Further, assume the non-normalized ISF  $h_{\rm DS}$  associated with  $V_{\rm DS}$  of  $M_{1/2}$  is

$$h_{\rm DS}(t) = \frac{1}{2} h_0 \cos \theta_{\rm h0} + \sum_{1}^{N} h_k \cos \left( k \omega_0 t + \theta_{\rm h,k} \right)$$

(2.5)

where  $h_k$  and  $\theta_{h,k}$  are the magnitude and phase of  $k_{th}$  harmonic term, respectively. Note that  $\theta_{h0}$  is either 0 or  $\pi$  depending on the sign of dc term  $h_{DS}$ . Thus, the phase noise is

$$\phi(t) = \int_{-\infty}^{t} h_{\rm DS}(\tau) \cdot i_{1/f,\,\rm cyclo}(\tau) d\tau$$

$$\approx \frac{\sqrt{2}h_{\rm eff,dc}}{\Delta\omega} \sin\left(\Delta\omega t + \gamma\right)$$

(2.6)

where  $\phi(t)$  is mainly dominated by the slow frequency term, and  $h_{\text{eff,dc}}$  is the dc value of non-normalized effective ISF  $h_{\text{eff}}(t)$  (=  $h_{\text{DS}}(t) \times I_{1/f,\text{rms}}(t)$ ), which is defined as

$$h_{\rm eff,dc} = \frac{1}{T} \int_0^T h_{\rm DS}(t) \cdot I_{1/f,\rm rms}(t) dt$$

(2.7)

where  $T(=2\pi/\omega_0)$  is the oscillation period.

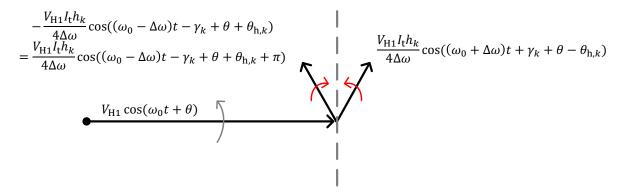

The phase noise  $\phi(t)$  appears at  $V_{\rm DS}$  of  $M_{1/2}$ , showing two correlated terms at  $\omega_0 \pm \Delta \omega$ ,

$$V_{\rm DS} \approx V_{\rm H1} \cos\left(\omega_0 t + \theta + \phi(t)\right) \approx V_{\rm H1} \cos\left(\omega_0 t + \theta\right) + \frac{V_{\rm H1}\sqrt{2}h_{\rm eff,dc}}{2\Delta\omega} \cos\left((\omega_0 + \Delta\omega)t + \theta + \gamma\right) - \frac{V_{\rm H1}\sqrt{2}h_{\rm eff,dc}}{2\Delta\omega} \cos\left((\omega_0 - \Delta\omega)t + \theta - \gamma\right)$$

(2.8)

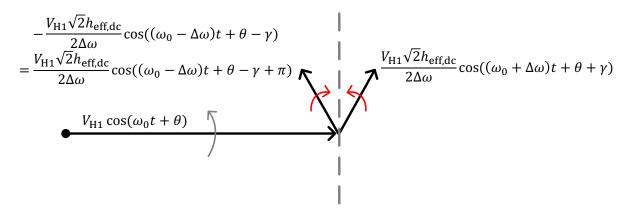

Figure 2.10: Phasor diagram of (2.8).

where  $V_{\rm H1}$  and  $\theta$  are the 1st harmonic amplitude and phase of  $V_{\rm DS}$ , respectively. To gain more insight into (2.8), its phasor diagram is illustrated in Fig. 2.10, where it is evident that the two correlated terms (i.e.,  $\omega_0 \pm \Delta \omega$ ) can only modulate the phase of  $V_{\rm DS}$ . Hence, the single-sideband to carrier ratio (SSCR) can be written as

$$\mathcal{L}(\Delta\omega) = \frac{1}{2} \left( \frac{V_{\rm H1} \sqrt{2} h_{\rm eff,dc}}{2\Delta\omega} \right)^2 / \frac{1}{2} V_{\rm H1}^2 = \left( \frac{\sqrt{2} h_{\rm eff,dc}}{2\Delta\omega} \right)^2$$

$$= \left( \frac{\sqrt{2}}{2\Delta\omega} \cdot \frac{1}{T} \int_0^T h_{\rm DS}(t) \cdot I_{1/f,\,\rm rms}(t) dt \right)^2$$

(2.9)

which is the flicker phase noise at  $\omega_0 \pm \Delta \omega$  caused by a single transistor M1 or M2. The final SSCR caused by cross-coupled pair is  $2 \times \mathcal{L}$ . It is important to address an apparent non-physicality of (2.9):  $h_{\text{eff,dc}}^2$  itself is proportional to  $1/\Delta \omega$ , since  $I_{1/f,\text{rms}}^2(t)$  is proportional to  $1/\Delta \omega$ . Thus,  $\mathcal{L}(\Delta \omega)$  is ultimately proportional to  $1/\Delta \omega^3$ .

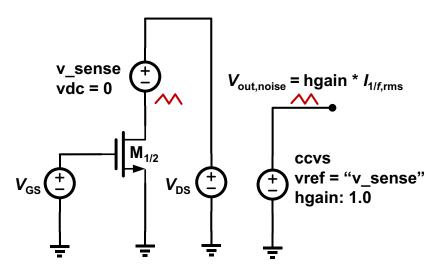

#### 2.2.3 Numerical Verification

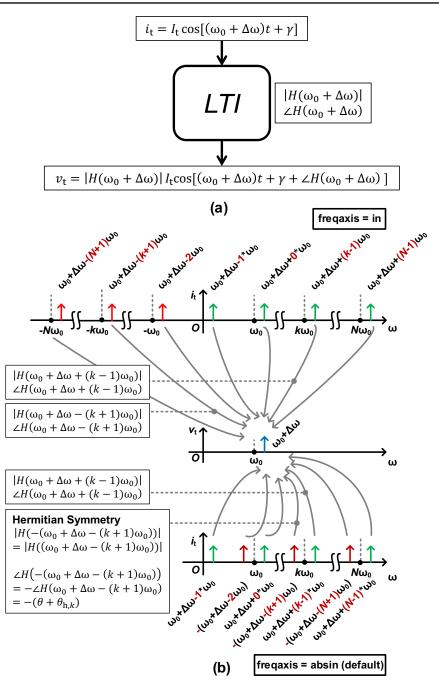

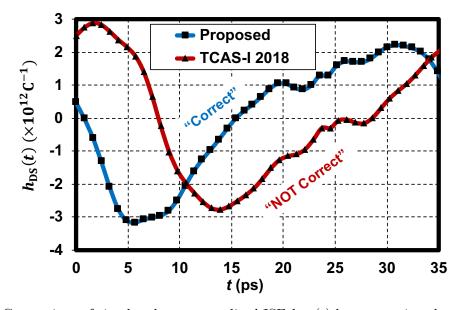

To verify the proposed expression (2.9), it is necessary to get the periodically modulated rms value of flicker current noise  $I_{1/f,rms}(t)$  and non-normalized ISF  $h_{DS}(t)$ . The former is based on the dc/NOISE simulations using the steady-state waveform point of  $V_{GS}$  and  $V_{DS}$ from PSS simulation (see Chapter 3). For the latter, it can be acquired by Periodic Transfer Function (PXF) simulations [86], which is more accurate and much faster than the conventional transient simulation method [35]. The linking equation between the non-normalized ISF and positive sidebands of PXF is derived as follows [86]:

$$h_{\rm DS}(t) = \frac{1}{2} \frac{4\Delta\omega |H(-1)|}{V_{\rm H1}} \cos[\theta - \angle H(-1)] + \sum_{k=1}^{N} \frac{4\Delta\omega |H(k-1)|}{V_{\rm H1}} \cos[k\omega_0 t + \theta - \angle H(k-1)]$$

(2.10)

where N is the number of harmonics for consideration, k - 1(= -1, 0, 1, 2, ..., N - 1) is the index of positive sidebands of PXF, H(k - 1) represents  $H(\omega_0 + \Delta \omega + (k - 1)\omega_0)$ , and  $|H(k - 1)|, \ \angle H(k - 1)$  are the magnitude and phase of periodic transimpedance, respectively. The magnitude  $V_{\rm H1}$  and initial phase  $\theta$  of 1st harmonic  $V_{\rm DS}$  can be simulated by PSS with the Harmonic Balance (HB) engine, which solves for the steady-state of cosines rather than sines.

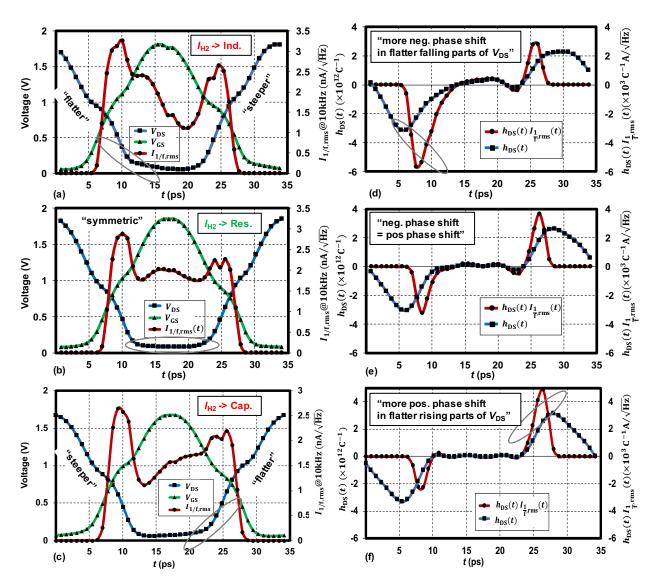

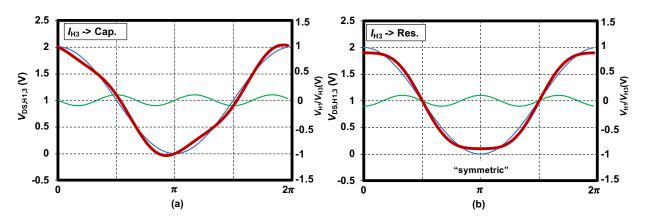

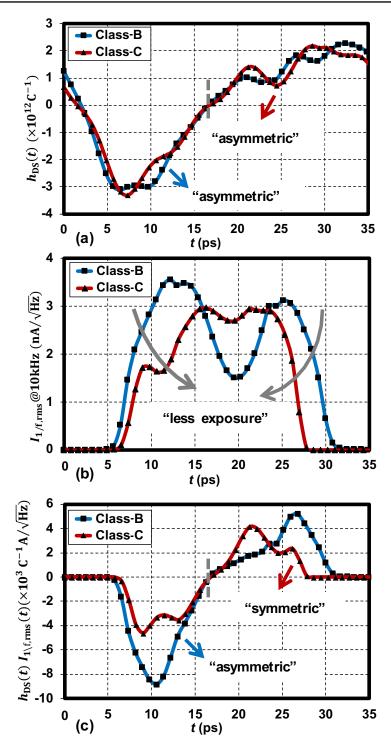

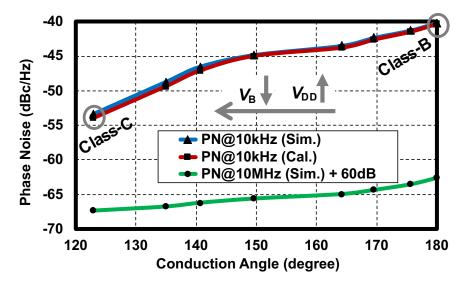

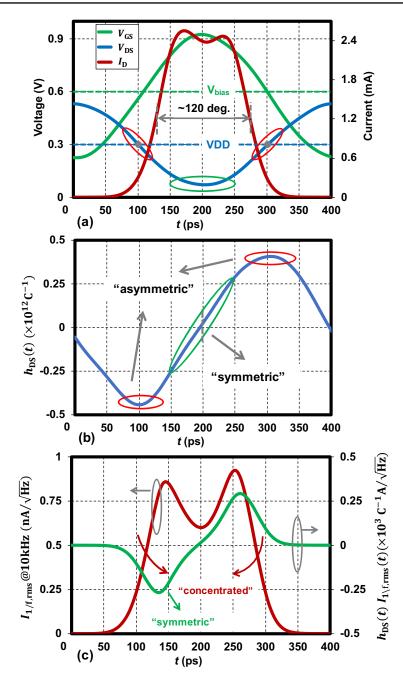

Both qualitative and quantitative analysis of flicker noise upconversion and reduction mechanisms of mmW oscillators are demonstrated in Figs. 2.11 and 2.12. By changing  $L_{\text{tail}} + L_{\text{decap}}$  from 0 to 800pH, the 2nd harmonic current  $I_{\text{H2}}$  will enter the inductive path (e.g.,  $L_{\text{tail}} + L_{\text{decap}} = 0$ ,  $I_{\text{H2}}$  mainly entering  $2L_{\text{se}} + L_{\text{diff}}$ ), resistive path (i.e.,  $L_{\text{tail}} + L_{\text{decap}} = 120 \text{ pH}$ , 2nd harmonic resonance), and capacitive path (e.g.,  $L_{\text{tail}} + L_{\text{decap}} = 800 \text{ pH}$ ,  $I_{\text{H2}}$  mainly entering  $C_{\text{se1}}$ ), successively. As a consequence, it causes less steep falling parts of  $V_{\text{DS}}$ , symmetric rising/falling parts of  $V_{\text{DS}}$ , and less steep rising parts of  $V_{\text{DS}}$ , as illustrated in Figs. 2.11(a), (b), and (c), respectively<sup>1</sup>. Compared with a steeper edge, the flatter edge is vulnerable to noise due to its longer-time exposure to noise. Figs. 2.11(d)–(f) (blue lines) show the corresponding non-normalized ISF  $h_{\text{DS}}(t)$  based on PXF<sup>2</sup>.

The periodically modulated flicker current noise  $I_{1/f,rms}(t)$  at 10 kHz models the process of flicker noise modulation, as shown in Fig. 2.11(a)-(c) (red lines). The flicker noise peaks in the regions where  $M_{1,2}$  operates in saturation, (i.e.,  $t \approx 10$  ps and 25 ps), while it also keeps relatively high levels in the triode region (i.e.,  $t \approx 12$  ps to 22 ps). Although a complex BSIM flicker noise model is employed in the process development kit (PDK) of TSMC 28-nm technology, the CNF/CMF model could still be fairly accurate and provide a physical understanding about flicker noise behavior in large-signal operation. As a means of verifying

<sup>&</sup>lt;sup>1</sup>An intuitive understanding about the waveform-shaping of  $V_{\rm DS}$  due to the different terminations of harmonic currents ( $I_{\rm H2}$  and  $I_{\rm H3}$ ) will be presented in the next subsection, which extends the analysis and clarifies the ambiguities in [44].

<sup>&</sup>lt;sup>2</sup>Note that  $h_{\rm DS}(t)$  is approximately proportional to the derivative of  $V_{\rm DS}(t)$ ), in which only Fig. 2.11(e) shows a symmetric  $h_{\rm DS}(t)$ , due to the symmetric rising and falling portions of  $V_{\rm DS}$  (2nd harmonic resonance).

Figure 2.11: Discrete waveform points of  $V_{\rm GS}$ ,  $V_{\rm DS}$  in one period based on PSS simulations, and corresponding rms value of flicker current noise  $I_{1/f,\rm rms}$  at 10 kHz based on dc/NOISE simulations: (a)  $L_{\rm tail} + L_{\rm decap} = 0 \,\mathrm{pH} (I_{\rm H2}$  mainly entering inductive path (i.e.,  $2L_{\rm se} + L_{\rm diff}$ )), (b)  $L_{\rm tail} + L_{\rm decap} =$ 120 pH (2nd harmonic resonance,  $I_{\rm H2}$  entering resistive path), (c)  $L_{\rm tail} + L_{\rm decap} = 800 \,\mathrm{pH} (I_{\rm H2}$  entering capacitive path (i.e.,  $C_{\rm se1}$ )) Non-normalized ISF function  $h_{\rm DS}(t)$  based on PXF simulations and  $h_{\rm DS}(t) \times I_{1/f,\rm rms}(t)$ : (d)  $L_{\rm tail} + L_{\rm decap} = 0 \,\mathrm{pH}$ , (e)  $L_{\rm tail} + L_{\rm decap} = 120 \,\mathrm{pH}$ , (f)  $L_{\rm tail} + L_{\rm decap} = 800 \,\mathrm{pH}$ .

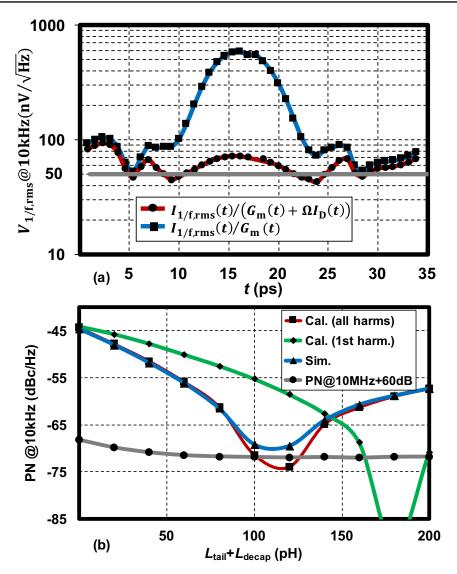

the efficacy of the adopted CNF/CMF model in (2.1), let us contrast it with the currently used CNF-only model by examining the flatness of  $V_{1/f,\rm rms}(t)$  at  $\Delta\omega/2\pi = 10$  kHz in both cases. A quick inspection of Fig. 2.12 (a) reveals that  $I_{1/f,\rm rms}(t)/(G_{\rm m}(t) + \Omega I_{\rm D}(t))$  is fairly constant. Conversely,  $I_{1/f,\rm rms}(t)/G_{\rm m}(t)$  is far from being constant, which means that the presently used CNF model cannot accurately describe the physical flicker noise modulation

Figure 2.12: (a) Verification of flicker noise model. (b) Numerical verification of PN @10 kHz.

process of oscillators in nanoscale CMOS technology.

The effective non-normalized ISFs  $h_{\text{eff}}(t) (= h_{\text{DS}}(t)I_{1/f,\text{rms}}(t))$  are shown in Fig. 2.11(d)-(f) (red lines, the area of  $h_{\text{eff}}(t)$  represents phase shift of  $V_{\text{DS}}$ ). It is obvious that the flicker noise mainly affects the phase noise in the two saturation regions, having an opposing influence on the phase change of  $V_{\text{DS}}$  in each region. As shown in Fig. 2.11(d) ( $I_{\text{H2}}$  enters the inductive path), phase change in the flatter falling part of  $V_{\text{DS}}$  (i.e., negative area of  $h_{\text{eff}}(t)$ , grey circle) is much larger than phase change in the steeper rising part (i.e., positive area of  $h_{\text{eff}}(t)$ ), which means  $h_{\text{eff,dc}} \neq 0$ , i.e., a flicker noise upconversion. The opposite phenomenon happens when the 2nd harmonic enters the capacitive path, where the positive area of  $h_{\text{eff}}(t)$  (i.e., positive

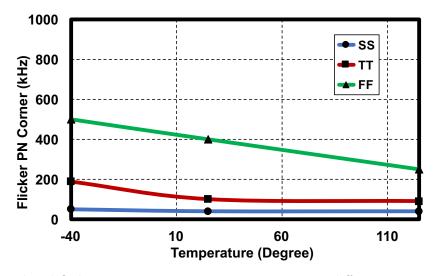

Figure 2.13: Simulated flicker-noise corner across tuning range (TR) in the conventional mmW oscillator ( $L_{\text{tail}} + L_{\text{dec}} = 120 \text{pH}$ ). The  $1/f^3$  PN corner maintains  $\leq 100 \text{ kHz}$  within 15% TR, while it significantly worsens when widening the TR.

Figure 2.14: Simulated flicker-noise corner versus temperature at different process corners in the conventional mmW oscillator  $(L_{\text{tail}} + L_{\text{dec}} = 120 \text{pH})$ .

phase change) is larger than its negative area (i.e., negative phase change) [see Fig. 2.11(f)], still leading to flicker noise upconversion. However, forcing the 2nd harmonic current to enter the resistive path would make the rising and falling parts of  $V_{\rm DS}$  more symmetric (as shown in Fig. 2.11(e)), causing the phase change in the two regions to cancel each other within one period (i.e.,  $h_{\rm eff,dc} = 0$ ).

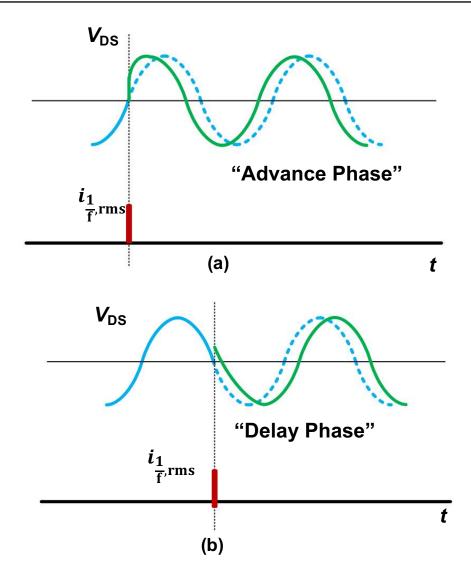

It is necessary to point out that the other flicker noise reduction mechanisms, i.e., the

introduction of phase shift between  $V_{\rm DS}$  and  $V_{\rm GS}$  [65] and the narrowing of the conduction angle [75,86], can also be explained by  $h_{\rm DS}(t)$  and  $I_{1/f,\rm rms}(t)$ . For the former, it is because the positive and negative areas of  $h_{\rm eff}(t)$  can be adjusted to be equal by the phase shift between  $h_{\rm DS}(t)$  (mainly depending on  $V_{\rm DS}$ ) and  $I_{1/f,\rm rms}(t)$  (mainly relying on  $V_{\rm GS}$ ). However, the positive or negative phase shift of  $V_{\rm GS}$  (taking  $V_{\rm DS}$  as a reference) depends on capacitive or inductive terminations of  $I_{\rm H2}$  (see Fig. 2.11), which were not discussed in [65]. An alternative approach would be to use a transformer to introduce a negative phase shift of secondary winding (i.e.,  $V_{\rm GS}$ ), compared with its primary winding (i.e.,  $V_{\rm DS}$ ), and also force the  $I_{\rm H2}$  to enter the inductive path. For the latter, the narrowing conduction angle [75,86] will decrease the  $I_{1/f,\rm rms}(t)$  exposure to the unbalanced  $h_{\rm DS}(t)$  (lack of the 2nd harmonic resonance) to suppress the flicker noise upconversion (see Chapter 3).

The resulting phase noise at 10 kHz offset, shown in Fig. 2.12(b), shows an almost perfect agreement between the calculations (N = 7, red line) based on (2.9) and simulations (N = 10, blue line), thus demonstrating the effectiveness of the proposed theory. Note that merely considering the phase noise contribution from the 1st harmonic ISF (green line) cannot provide the required match to the simulations, except for the single point where  $L_{tail} + L_{decap} = 0 \text{ pH}$ (i.e., Van der Pol oscillator [64]). The thermal PN at 10 kHz (represented by "PN @10 MHz + 60 dB") can be suppressed as long as  $L_{tail} + L_{decap}$  is large enough, suppressing the "loaded-Q" effect no matter whether the 2nd harmonic resonance happens or not (grey line) (see [22] and [36]). Thus, if the 2nd harmonic resonance is difficult to achieve, a general rule to improve the thermal PN is to increase the CM impedance, including decreasing the CM capacitance (e.g., separating the supplies of sw-caps and the oscillator [51]) and increasing the CM inductance (e.g., adding long-tail inductor [22]).

It is worthwhile to calculate the PN at 10 kHz by replacing the precise simulated value of  $I_{1/f,\rm rms}(t)$  with the best-fit CNF/CMF model:  $50 \,\mathrm{nV}/\sqrt{\mathrm{Hz}} \times [G_{\rm m}(t) + \Omega I_{\rm D}(t)]$  with  $\Omega$ =  $3 \,\mathrm{V}^{-1}$ , as calculated during the non-cut-off region (i.e., from 6ps to 28ps) and indicated as the grey curve in Fig. 2.12 (b). When  $L_{\rm tail} + L_{\rm decap} = 0 \,\mathrm{pH}$ , the PN @10 kHz based on CNF/CMF model is -43.73 dBc/Hz, while the accurate PDK result is -44.35 dBc/Hz (i.e., using  $I_{1/f,\rm rms}(t)$ ). As mentioned, the CNF/CMF model shows good accuracy for quantitative analysis and also helps designers to understand intuitively the complex behavior of modulated flicker noise. Of course, the most accurate quantitative analysis is still with the simulated  $I_{1/f,\rm rms}(t)$ , but the demonstrated accuracy of the flicker PN prediction in (2.1) is within 1 dB of the simulation.

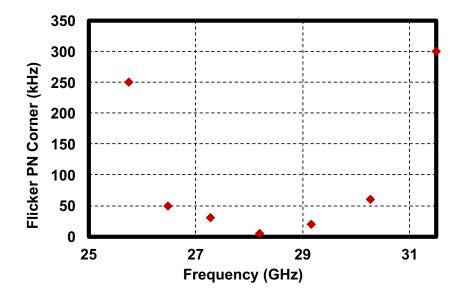

Fig. 2.13 shows the relationship between the simulated flicker noise corner and the tuning range (TR), where  $L_{\text{tail}} + L_{\text{decap}} = 120 \,\text{pH}$  and the resonance frequency of the implicit CM tank is around  $2 \times 28.5 \,\text{GHz}$ . Within a 15% TR, the flicker PN corner can be kept lower than 100kHz (especially, no flicker noise upconversion at 28.5 GHz due to 2nd harmonic resonance), then it would significantly worsen. Obviously, the 2nd harmonic resonance suppressing the flicker noise upconversion is a narrow-band technique. As for the PVT robustness of the 2nd harmonic resonance, temperature changes have less effects on the flicker noise corner, while the variation of technology process could shift the flicker noise corner a lot. This is because the resonance frequency of both DM and CM tanks would shift in the same direction due to temperature, while the threshold voltage changes with the process corner would have a large influence on the voltage-biased oscillator. Further, the optimum  $L_{\text{tail}}+L_{\text{decap}}$ for the 2nd harmonic resonance is only  $\sim 120 \text{ pH}$ , since the inductance in the implicit CM tank  $L_{\text{diff}} + 2L_{\text{se}}$  is already dominant. Unfortunately, due to the physical distance between VDD\_A and VSS\_A in conventional mmW oscillators, the  $L_{tail} + L_{decap}$  could hardly be made less than 200 pH, which means mmW designers would have difficulties in forcing the 2nd harmonic current to enter the resistive path to suppress the flicker noise. Therefore, for mmW oscillators, the CM return path should be properly constructed for accurate harmonic termination.

# 2.2.4 Intuitive Understanding of Waveform-Shaping Due to Different Terminations of Harmonic Currents

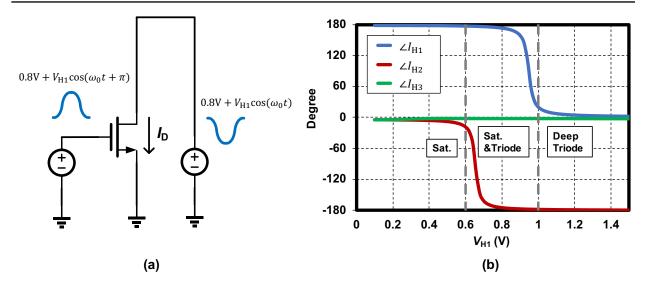

In the previous subsection, we claimed that the falling part of  $V_{\rm DS}$  will be flatter (more vulnerable to noise) than its rising part when  $I_{\rm H2}$  enters the inductive path, while its rising part will become flatter when  $I_{\rm H2}$  enters the capacitive path. To understand these types of waveform-shaping due to the different terminations of harmonic currents, it is necessary to establish the phase relationship between harmonic currents. Fig. 2.15(a) models the condition that a MOS transistor is operating in the cross-couple pair of a voltage-biased oscillator (i.e., the phase difference between  $V_{\rm DS}$  and  $V_{\rm GS}$  is  $\pi$ , taking  $V_{\rm DS}$  as reference), in which the harmonic currents of a MOS transistor come from its non-linearity. With the input amplitude of the sinusoidal signal (i.e.,  $V_{\rm H1}$ ) increasing, the transistor will work first in

Figure 2.15: (a) Test-bench for studying phase relationship between harmonic currents  $(I_{\text{H1},2,3})$  and  $V_{\text{DS}}$ . (b) PSS simulation results (phase degrees are calculated from cosines).

saturation (i.e.,  $V_{\rm H1} < 0.6 \,\rm V$ ), then in saturation and triode (i.e.,  $0.6 \,\rm V < V_{\rm H1} < 1 \,\rm V$ ), and finally in the deep triode regions (i.e.,  $V_{\rm H1} > 1 \,\rm V$ ), respectively [see Fig. 2.15(b)]. Before the transistor enters the deep-triode region (i.e.,  $V_{\rm H1} < 1 \rm V$ ),  $I_{\rm H1}$  is in-phase with  $V_{\rm GS}$  (in fact, due to the Groszkowski effect [68], there will still be a small difference between  $\angle V_{\rm GS}$ and  $\angle I_{\rm H1}$ , see [50]), but out-of-phase with  $V_{\rm DS}$ , behaving as a "negative resistor" for  $V_{\rm DS}$ . However, for  $\angle I_{\rm H2}$ , it is 0° in saturation, but -180° in the saturation and triode regions, while  $\angle I_{\rm H3}$  is always 0°. For the voltage-biased oscillator, the swing of  $V_{\rm DS}$  and  $V_{\rm GS}$  will be same as the supply voltage (e.g., 0.8 V), forcing the transistor to operate in the saturation and triode regions, thus, the harmonic current is derived as

$$I_{\rm D} = I_{\rm H0} + I_{\rm H1} \cos(\omega_0 t + \pi) + I_{\rm H2} \cos(2\omega_0 t - \pi) + I_{\rm H3} \cos(3\omega_0 t)$$

(2.11)

where the direction of current entering the MOS transistor is assumed as "positive",  $I_{\rm H1,2,3}$  represent the magnitude of the 1st, 2nd, and 3rd harmonic voltages, respectively.  $I_{\rm D}$  injects into the DM ( $I_{\rm H1,3}$ ) and CM tanks ( $I_{\rm H2}$ ); hence the sinusoidal  $V_{\rm DS}$  will be affected.

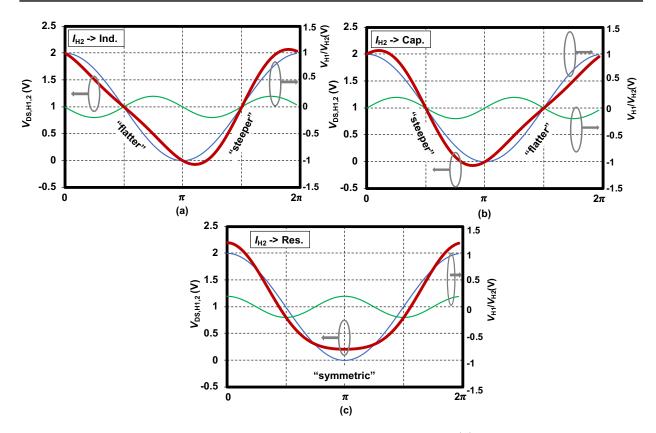

For simplicity, let us study the effects of the 2nd harmonic current first. The harmonic voltage, considering 1st and 2nd harmonic currents (i.e.,  $V_{\text{DS},\text{H1,2}}(=-I_{\text{D}} \times Z_{\text{DM or CM}})$ ), is

Figure 2.16: Waveform shaping due to different terminations of  $I_{\text{H2}}$ . (a) Flatter falling part due to inductive termination. (b) Flatter rising part due to capacitive termination. (c) Symmetric rising and falling parts due to resistive termination.

derived as

$$V_{\text{DS,H1,2}} \approx \begin{cases} V_{\text{H0}} + V_{\text{H1}} \cos \omega_0 t + V_{\text{H2}} \cos(2\omega_0 t + \frac{\pi}{2}), & I_{\text{H2}} -> \text{Ind.} \\ V_{\text{H0}} + V_{\text{H1}} \cos \omega_0 t + V_{\text{H2}} \cos 2\omega_0 t, & I_{\text{H2}} -> \text{Res.} \\ V_{\text{H0}} + V_{\text{H1}} \cos \omega_0 t + V_{\text{H2}} \cos(2\omega_0 t - \frac{\pi}{2}), & I_{\text{H2}} -> \text{Cap.} \end{cases}$$

(2.12)

where  $V_{\text{H0,1,2}}$  are the magnitude of dc, 1st, and 2nd harmonic voltages. Fig. 2.16 shows the waveform shaping of  $V_{\text{DS}}$  when  $I_{\text{H2}}$  enters different terminations, in which we assume  $V_{\text{H0}} = 1$ V,  $V_{\text{H1}} = 1$ V, and  $V_{\text{H2}} = 0.2$ V.<sup>1</sup> Similar as in the simulation results in Figs. 2.11(a)-(c), the falling edge will become flatter when  $I_{\text{H2}}$  enters the inductive path, while rising edge will become flatter when  $I_{\text{H2}}$  enters the capacitive path.

The 3rd harmonic current will enter the capacitive path for most inductor-based oscillators,

<sup>&</sup>lt;sup>1</sup>The phase relationship between  $V_{\rm H1}$  and  $V_{\rm H2}$  in Figs. 5(a) and 6(a) of Shahmohammadi's work [44] may not be correct.

Figure 2.17: Waveform shaping due to different terminations of  $I_{\text{H3}}$ . (a) Capacitive termination of  $I_{\text{H3}}$ . (b) Symmetric rising and falling parts due to resistive terminations.

since it sees the same DM tank as  $I_{\rm H1}$  (entering resistive path). However, in class-F oscillators [51], it could enter the resistive path. Thus, the harmonic voltage considering the 1st and 3rd harmonic current (i.e.,  $V_{\rm DS,H1,3}(=-I_{\rm D} \times Z_{\rm DM})$ ) is as follows,

$$V_{\text{DS,H1,3}} \approx \begin{cases} V_{\text{H0}} + V_{\text{H1}} \cos \omega_0 t + V_{\text{H3}} \cos(3\omega_0 t + \pi), & I_{\text{H3}} -> \text{Res.} \\ V_{\text{H0}} + V_{\text{H1}} \cos \omega_0 t + V_{\text{H3}} \cos(3\omega_0 t + \frac{\pi}{2}), & I_{\text{H3}} -> \text{Cap..} \end{cases}$$

(2.13)

The waveform shaping due to the capacitive and resistive terminations of  $I_{\rm H3}$  is shown in Figs. 2.17(a) and (b), respectively, where we assume  $V_{\rm H3} = 0.1$ V. Compared with the  $I_{\rm H2}$ entering capacitive path (see Fig. 2.16(b)), the capacitive termination of  $I_{\rm H3}$  will have much less effects on the symmetries between the rising and falling edges of  $V_{\rm DS}$ , since it is the peak and bottom (*slow* change) of  $V_{\rm H3}$  (green line) (rather than "transition" edge (*fast* change) like  $V_{\rm H2}$ ) appearing at the falling and rising edges of  $V_{\rm H1}$ . Recently, Pepe *et al.* [42] have theoretically demonstrated that the non-resistive termination of  $I_{\rm H3}$  has nothing to do with the flicker noise upconversion.

# 2.3 Circuit Description

In [23], a class-F oscillator (first introduced in [70]) with a 3rd harmonic extraction has demonstrated low  $1/f^2$  PN at mmW frequencies. However, the  $1/f^3$  PN corner still exceeds to 1 MHz. In [44], a class-F<sub>23</sub> oscillator has achieved both low  $1/f^2$  PN and low  $1/f^3$  PN corner at carrier frequencies below 7 GHz. Unfortunately, direct application of those techniques

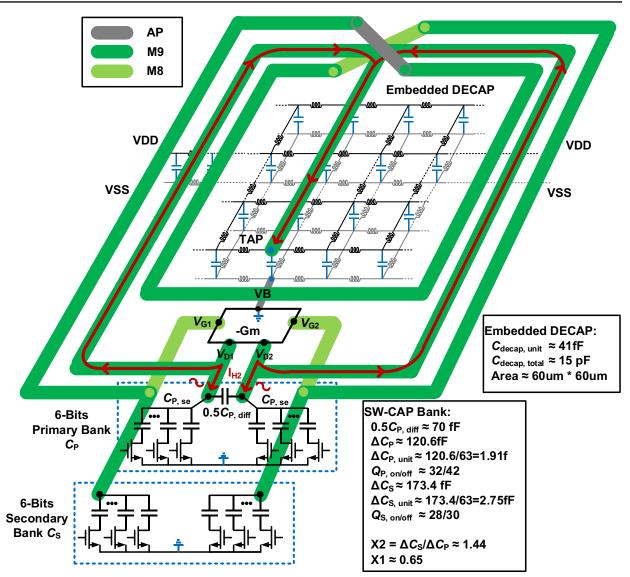

Figure 2.18: Proposed layout of class- $F_{23}$  oscillator with embedded decoupling capacitor and the design switched-capacitor banks.

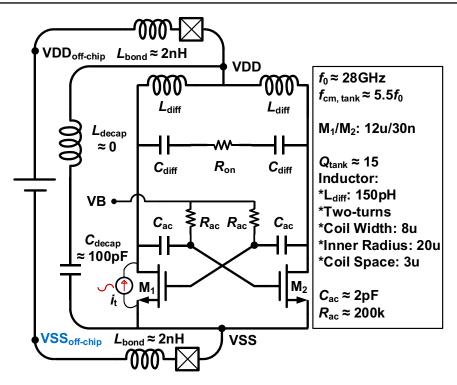

at mmW frequencies may not deliver the same level of  $1/f^3$  performance. In this section, we demonstrate the proposed class-F<sub>23</sub> oscillator with the 3rd harmonic extraction, which achieves both the best-in-class  $1/f^2$  PN and record low  $1/f^3$  PN corner at mmW frequencies. As discussed in Section II, the uncontrolled return path of the 1:2 transformer could shift the desired CM resonance which will lead to the degradation of the  $1/f^3$  corner. To solve the above issue, the proposed class-F<sub>23</sub> oscillator employs a transformer with an explicit CM return path using an embedded decoupling capacitor [50]. The detailed circuit operation of the oscillator as well as details of the transformer with embedded decoupling capacitor and the capacitor bank design will be discussed below.

#### 2.3.1 Operational Principle of Class-F<sub>23</sub> Oscillator

Fig. 2.6 showed the circuit schematic of the proposed class- $F_{23}$  oscillator, while the proposed layout is presented in Fig. 2.18. The oscillator exploits the 3rd harmonic resonance in the DM tank (class- $F_3$  operation), and the 2nd harmonic resonance in the CM tank (class- $F_2$ operation). The former deals with the DM tank, including the primary DM inductance  $L_{P, dm}$  (=  $L_{P, diff}$ ), secondary DM inductance  $L_{S, dm}$  (=  $L_{S, diff}$ ), DM magnetic coupling factor  $k_{dm}$ , primary DM capacitance  $C_{P, dm}$  (=  $C_P$ ), and secondary DM capacitance  $C_{S, dm}$ (=  $C_S$ ). According to [70], the fundamental frequency  $\omega_0$  can be approximately derived as:  $\omega_0 = 1/\sqrt{L_{P, diff}C_P + L_{S, diff}C_S}$ , while the ratio betwen two DM resonance frequencies  $\omega_3/\omega_0$ is determined by

$$\frac{\omega_3}{\omega_0} = \sqrt{\frac{1 + X + \sqrt{1 + X^2 + X(4k_{\rm dm}^2 - 2)}}{1 + X - \sqrt{1 + X^2 + X(4k_{\rm dm}^2 - 2)}}}$$

(2.14)

where  $X = (L_{\rm S,diff}C_{\rm S})/(L_{\rm P,diff}C_{\rm P})$ . Thus, for the assumed 1:2 turns-ratio transformer (given  $L_{\rm S,diff}/L_{\rm P,diff}$ ), through tuning of the secondary-to-primary capacitor ratio  $X_2$  (=  $C_{\rm S}/C_{\rm P}$ ), the  $\omega_3/\omega_0 = 3$  condition can be achieved for the class-F operation. Note that  $k_{\rm dm}$  is generally chosen around 0.61 to get a strong 3rd harmonic [23]. Due to the low CM coupling factor  $k_{\rm cm}$ , only the primary CM tank is considered [44], which includes the primary CM inductance  $L_{\rm P,cm}$  (=  $L_{\rm P, diff} + 2L_{\rm P, se}$ ) and the primary CM capacitance  $C_{\rm P, cm}$  (=  $C_{\rm P, se}$ ). Thus, the CM resonance frequency  $\omega_2$  is  $1/\sqrt{(L_{\rm P, diff} + 2L_{\rm P, se})C_{\rm P, se}}$ . The ratio between  $\omega_2$  and  $\omega_0$  is derived as follows:

$$\frac{\omega_2}{\omega_0} = \sqrt{\frac{L_{\rm P, \, diff}C_{\rm P} + L_{\rm S, \, diff}C_{\rm S}}{(L_{\rm P, \, diff} + 2L_{\rm P, \, se})C_{\rm P, se}}} = \sqrt{\frac{L_{\rm P, \, diff} + L_{\rm S, \, diff}X_2}{(L_{\rm P, \, diff} + 2L_{\rm P, \, se})X_1}}$$

(2.15)

where  $X_1 (= C_{P,se}/C_P)$  is the ratio of CM capacitance in the primary tank. Through tuning of  $X_1$  to the  $\omega_2/\omega_0 = 2$  condition, class-F<sub>2</sub> operation can be achieved. Thus, the secondary-toprimary capacitor ratio  $(X_2)$  helps in achieving class-F<sub>3</sub> operation, forcing the 3rd harmonic current to enter the resistive path, thus boosting the 3rd harmonic voltage. On the other hand, the primary CM capacitance ratio  $(X_1)$  enables the class-F<sub>2</sub> operation, forcing the 2nd harmonic current to enter the resistive path, thus maintaining the symmetry between the rising and falling parts of the output waveform, and ultimately helping to reduce the flicker noise upconversion.

Figure 2.19: Trade-offs between the area of embedded decoupling capacitor and (a) quality factor of the primary coil, and (b) quality factor of the secondary coil.

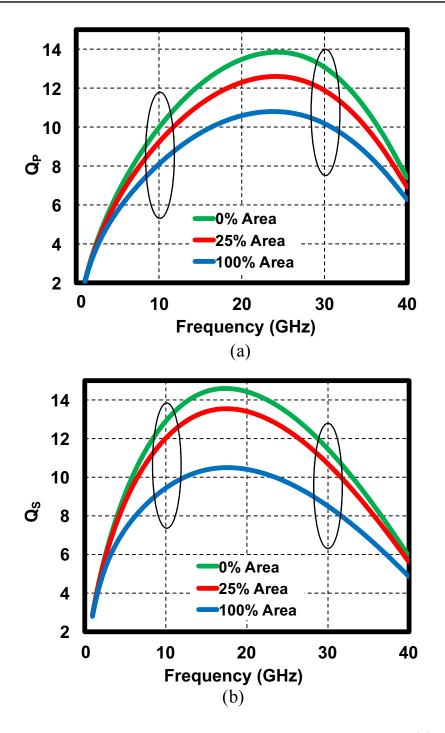

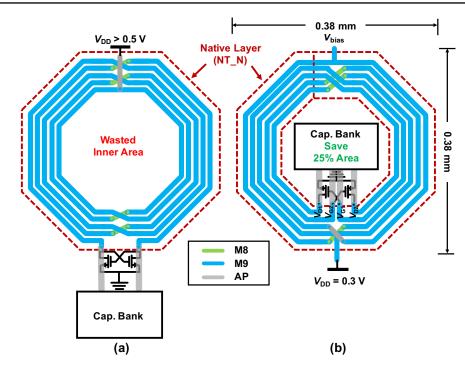

# 2.3.2 Proposed Transformer with Embedded Decoupling Capacitor for Explicit CM Return Path

To explicitly define the CM return path, the proposed 1:2 transformer with the embedded decoupling capacitor is shown in Fig. 2.18. By bringing the tap of primary coil as close as

practically possible to the source node of the MOS transistors, the shortest return path for the CM current can be achieved. According to the study shown in Fig. 2.8, the parasitic

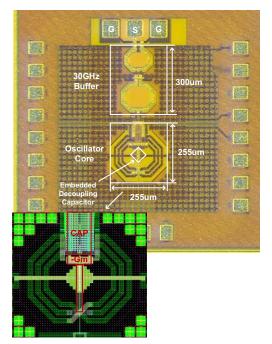

the CM current can be achieved. According to the study shown in Fig. 2.8, the parasitic inductance of the embedded decoupling capacitor network can be safely neglected, thus allowing for the CM inductance  $L_{\rm cm}$  to be modeled accurately. The size of the 1:2 transformer is optimized for the intended operating frequency to achieve a high Q-factor but without too much coupling to the substrate. In this work, the self-resonant frequency (where DM coupling factor  $k_{\rm dm}$  reaches 0) is about 5× of the operating frequency. Thus, the outer diameter of the transformer is chosen as 220  $\mu$ m (see Fig. 2.20), with the self-resonance at ~50 GHz. The coil width is set at 10  $\mu$ m with consideration of skin effect, while the coil space is 7  $\mu$ m to make  $k_{\rm dm}$  about 0.63. It is well recognized that placing the embedded decoupling capacitor inside the coil may degrade the Q-factor. From the EM simulation (see Fig. 2.19), if the decoupling capacitor area is less than 25% of the coil's internal area, the degradation would be about 1 without affecting the inductance or coupling factor. On the other hand, the embedded decoupling capacitor should still be large enough to provide the short path for the CM current, which is 15 pF in this case. According to simulations using the circuit model in Fig. 2.6,  $X_2$  is about 1.44 to get the 3rd harmonic resonance. It means that

$$\frac{C_{\rm S,\,min}}{C_{\rm P,\,min}} = \frac{C_{\rm S,\,max}}{C_{\rm P,\,max}} = \frac{\Delta C_{\rm S}}{\Delta C_{\rm P}} = X_2. \tag{2.16}$$

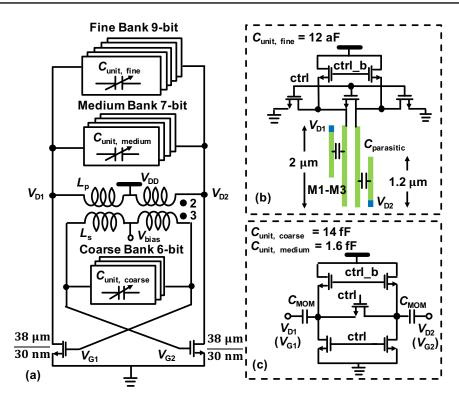

Two 6-bit single-ended capacitor banks  $C_{\rm P, se}$  and  $C_{\rm S, se}$  are designed for the primary and secondary banks (shown in Fig. 2.18), in which  $\Delta C_{\rm P} = 120.6$  fF and  $\Delta C_{\rm S} = 173.4$  fF. The quality factor of the capacitor banks is about 30 at 10 GHz, thus facilitating the overall high Q-factor of the tank. A fixed differential capacitor of  $0.5C_{\rm P, diff}$  (=70 fF) is placed in the primary tank, to enable the 2nd harmonic resonance when the sw-cap control word is in the middle (= 32 for the 6-bit code), which makes  $X_1$  about 0.65. For a more accurate control of the CM resonance, the fixed differential capacitor can be replaced with several bits of the differential capacitor bank [49].

#### 2.3.3 Third Harmonic Extraction Using Two-Stage 30-GHz PA(Buffer)

As shown in Fig. 2.6, a two-stage 30 GHz PA (buffer) is used to boost the 3rd harmonic signal and to suppress the fundamental and 2nd harmonics [23, 73]. The passive ac-coupling circuit ( $R_{\rm ac}$  and  $C_{\rm ac}$ ) is inserted between the oscillator and PA.  $C_{\rm ac}$  is chosen  $\sim 10 \times$  of the

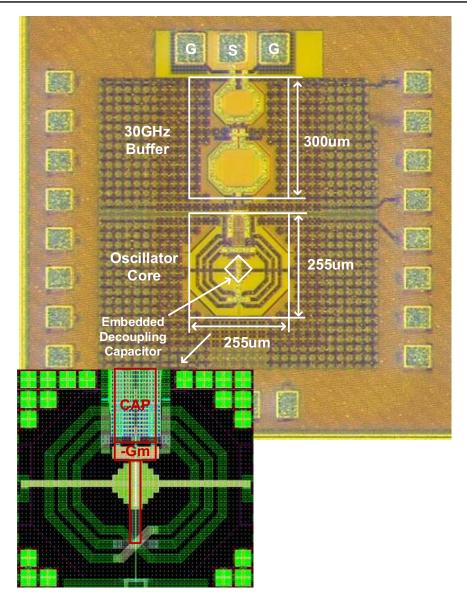

Figure 2.20: Chip micrograph and zoomed-in layout area of the embedded decoupling capacitor network.

input capacitance of 1st stage PA, and  $R_{\rm ac}$  (= 50 k $\Omega$ ) is chosen large enough to make the corner frequency much lower than the oscillator output frequency to ensure low coupling losses. Two 1:1 transformers (T2 and T3) vertically stack two one-turn inductors (M9 for the primary coil, and AP for the secondary coil). They are used for coupling between the 1st and 2nd stages, and also to the GSG (ground-signal-ground) PAD (see Fig. 2.20). To decrease the insertion loss in each transformer for the given frequency (i.e., 30 GHz), the diameter of the transformer's coils is optimized for high Q-factor. With the help of EM simulations, the diameters of T2 and T3 are chosen around 120  $\mu$ m. Two tuning capacitors ( $C_{\rm tune1} =$

|                               |            | JSSC'17<br>[44]      | JSSC'13<br>[60]      | JSSC'16<br>[39]      | JSSC'13<br>[65] | ESSCIRC'15<br>[66] | ESSCIRC'15<br>[64] | JSSC'16<br>[20] | A-SSCC'15<br>[62] | This Work                                                                            |            |

|-------------------------------|------------|----------------------|----------------------|----------------------|-----------------|--------------------|--------------------|-----------------|-------------------|--------------------------------------------------------------------------------------|------------|