# SCIENTIFIC REPORTS

### **OPEN**

SUBJECT AREAS: ELECTRONIC DEVICES ELECTRONIC PROPERTIES AND DEVICES

> Received 6 May 2014

Accepted 8 July 2014

Published 31 July 2014

Correspondence and requests for materials should be addressed to C.S.L. (cslai@mail.cgu. edu.tw) or C.Y.S. (cysu@ncu.edu.tw)

## Fluorinated Graphene as High Performance Dielectric Materials and the Applications for Graphene Nanoelectronics

Kuan-I Ho<sup>1</sup>, Chi-Hsien Huang<sup>2</sup>, Jia-Hong Liao<sup>1</sup>, Wenjing Zhang<sup>3</sup>, Lain-Jong Li<sup>3</sup>, Chao-Sung Lai<sup>1</sup> & Ching-Yuan Su<sup>4</sup>

<sup>1</sup>Department of Electrical Engineering, Chang Gung University, Tao-Yuan 333, Taiwan, <sup>2</sup>Department of Materials Engineering, Ming Chi University of Technology, New Taipei City 24301, Taiwan, <sup>3</sup>Institute of Atomic and Molecular Sciences, Academia Sinica, Taipei, 11529, Taiwan, <sup>4</sup>Graduate Institute of Energy Engineering and Department of Mechanical Engineering, National Central University, 300 Chung-Da Rd, Chung-Li, 32001, Taiwan.

There is broad interest in surface functionalization of 2D materials and its related applications. In this work, we present a novel graphene layer transistor fabricated by introducing fluorinated graphene (fluorographene), one of the thinnest 2D insulator, as the gate dielectric material. For the first time, the dielectric properties of fluorographene, including its dielectric constant, frequency dispersion, breakdown electric field and thermal stability, were comprehensively investigated. We found that fluorographene with extremely thin thickness (5 nm) can sustain high resistance at temperature up to 400 °C. The measured breakdown electric field is higher than 10 MV cm<sup>-1</sup>, which is the heightest value for dielectric materials in this thickness. Moreover, a proof-of-concept methodology, one-step fluorination of 10-layered graphene, is readily to obtain the fluorographene/graphene heterostructures, where the top-gated transistor based on this structure exhibits an average carrier mobility above 760 cm<sup>2</sup>/Vs, higher than that obtained when SiO<sub>2</sub> and GO were used as gate dielectric materials. The demonstrated fluorographene shows excellent dielectric properties with fast and scalable processing, providing a universal applications for the integration of versatile nano-electronic devices.

raphene is a potential candidate material for use in building next-generation nanoelectronic and optoeplectronic devices due to its unique properties (e.g., optical transparency, mechanical flexibility and superior high carrier mobility)<sup>1-6</sup>. Mono- or few-layer graphene is typically used to build field effect transistors (FETs) on oxidized silicon wafers (graphene-on-insulator architecture); these devices can then be used to investigate the carrier transport properties of such component materials<sup>7-9</sup>. However, graphene-on-insulator architectures, so-called pseudo-MOS structures, are not realistic device architectures. To be compatible with standard CMOS and IC architectures, top-gated graphene transistors are required. Top-gated FETs based on graphene are made by first depositing  $SiO_2$  as gate dielectric material<sup>10</sup>. Unfortunately,  $SiO_2$  dielectric layers degrade the carrier mobility of graphene due to the trapping charge density at the interface and damaging the graphene itself. Uniform gate insulators with a reduced number of interfacial defects and trapping states must be fabricated for use in graphene-based devices. For instance, uniform Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> layers with well-defined thickness can be deposited using atomic layer deposition (ALD) systems. However, seed layers composed of materials such as oxidized aluminum and low-k polymers are required for  $H_2O$ -based ALD deposition on graphene because of the hydrophobic nature of the graphene surface<sup>11-13</sup>. Recently, hexagonal boron nitride (h-BN) has been utilized as a novel gate dielectric; this material shows promising electrical and dielectric properties in transistor devices, but integration and scaling are still challenging<sup>14</sup>. One type of graphene-based insulator, graphene oxide (GO), is often applied as a gate dielectric material in electronic devices, such as resistive random-access memory (RRAM) and thin film transistors<sup>15-20</sup>. However, the low thermal stability of GO reduces its dielectric resistivity, which is a drawback since thermal processing steps are often used during device fabrication. Thus, it is of great challenge to find new suitable dielectric materials for use in the fabrication of nano-scale devices.

dependent frequency dispersion of 10 L of fluorographene. The

Fluorinated graphene (fluorographene), one of the thinnest insulators known, is an attractive 2D material. Fluorographene exhibits a mechanical strength comparable to that of pristine graphene, and its conductivity can be modulated from semi-metallic to insulating by tuning its stoichiometry (i.e., its carbon-to-fluorine ratio (C/F))<sup>21</sup>. A theoretical calculation reveals that by partially fluorinating graphene (from  $C_{32}F$  to  $C_4F$ ) the energy bandgap of the material can be modulated from 0.8 to 2.9 eV. Several experimental results have demonstrated the band gap and electronic transport properties of fluorinated graphene<sup>22-24</sup>. As a result, versatile graphene-based devices have been fabricated by chemically insolating pristine graphene. Withers et al. demonstrate the approach to selectively reduce insulating fluorinated graphene to conducting and semiconducting graphene by electron beam irradiation<sup>25</sup>. Lee et al. selectively fluorinated graphene using irradiating a fluoropolymer-covered graphene sample with a laser<sup>26</sup>. Graphene nano-ribbon (GNR) transistors with 35 nm channel widths were also realized using probe lithography. Specifically, a polymer nanowire mask was used to selectively expose graphene to ambient XeF<sub>2</sub> gas ambient<sup>27</sup>. Recently, we have successfully fabricated a unique semi-metal/semiconductor/insulator heterojunction structure directly using a single graphene sheet via a selective fluorination process<sup>28</sup>. This technique can potentially be used for the integration of electronics at the single atomic layer scale. Herein, we present a novel graphene-based field effect transistor architecture in which fluorographene is introduced as the gate dielectric material. The CVD-grown graphene was fluorinated using a lowdamaged CF<sub>4</sub> plasma treatment, which allows for its integration with IC fabrication to achieve large-area processing<sup>28</sup>. During this process, a filter is inserted between the CF<sub>4</sub> plasma and graphene sheet to reduce damage caused by high energy radicals and UV photons.

The dielectric properties of multi-layer fluorographene (e.g., dielectric constant, frequency dispersion, breakdown electric field  $(E_{BD})$  and thermal stability) were comprehensively investigated. We found that fluorographene with extremely thin thickness(5 nm) can sustain high effective resistance when it is annealed at temperatures up to 400°C in an ambient environment. The dielectric constant was found to be  $\sim$ 1.2, and the breakdown electric field (E<sub>BD</sub>) was found to be higher than 10 MV cm<sup>-1</sup>. This E<sub>BD</sub> value is much higher than that reported for stacked graphene oxide, and it is comparable to that of bulk Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub><sup>29</sup>. More importantly, a proof-of-concept methodology, one-step fluorination of 10-layered graphene, is used to obtain the fluorographene/graphene heterojunction structure, where the top-gated transistor based on this structure exhibits an average carrier mobility above 760 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (higher than that of graphene oxide and AlO<sub>x</sub>). The proposed device fabrication is very promising for future integration of scaled and highdensity electronics.

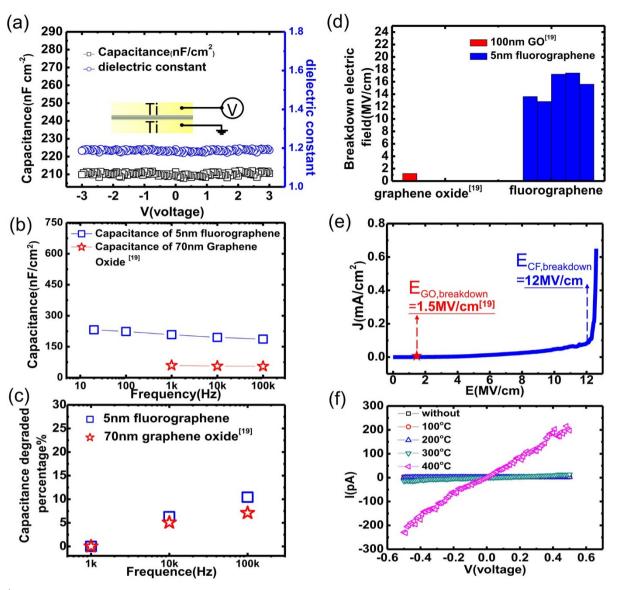

#### Results

Metal-insulator-metal (MIM) capacitors with a Ti/fluorographene/ Ti sandwich structure were fabricated to study the gate dielectric properties of fluorographene. The fluorographene was made by transferring and stacking 10-layers (10-L) of fluorinated graphene monolayer that was initially grown on Cu by CVD (see experimental section for details). It is worth noting that stacks of fluorographene less than 10-L thick show high leakage currents (~150 nA). Therefore, the measured dielectric properties shown in this work are based on 10-L of fluorographene (thickness  $\sim$ 5 nm as measured by TEM). Figure 1a shows the measured capacitance and the dielectric constant as a function of the applied voltage (-3 to +3 V). A stable capacitance value of  $\sim 210 \text{ nF/cm}^2$  (normalized to 1 cm<sup>2</sup>) was observed; variations in the capacitance up to a voltage bias of  $\pm 3$  V were not observed. Moreover, the dielectric constant of fluorographene was found to be  $\sim$ 1.2, independent of the sweep in the bias voltage. These results suggest the stable dielectric properties of this multi-layered fluorographene. Figure 1b shows the capacitancecapacitance of fluorographene decreased from 230 to 200 nF cm<sup>-2</sup> as the frequency increased from 20 to 100 kHz, indicating that this material could be steady under high frequency operation. The reported frequency dispersion based on GO as the dielectric material is indicated by the red star in Figure 1b for comparison<sup>16</sup>. As concluded from the data shown in Figure 1c, the capacitance of both fluorographene and GO are reduced by about 10% when the frequency is increased up to 100 kHz. Moreover, the breakdown strength of fluorographene was measured by varying the electric field from 0 to 20 MV cm<sup>-1</sup> at room temperature. The statistical data compiled in Figure 1d reveal that the breakdown electric fields of GO16 and fluorographene were found to be 1.5 MV cm<sup>-1</sup> and 12 MV cm<sup>-1</sup>, respectively. The fluorographene sample with 10 L is highly insulating with a low electric field-dependent leakage current 46.2  $\mu$ A cm<sup>-2</sup> at a bias field up to 10 MV cm<sup>-1</sup> (Figure 1e). The dielectric performance of the fluorographene sample (5 nm thick) is superior to that of the GO sample (70 nm thick). It is unexpected that the as-prepared thin fluorographene sample could sustain a high electric field comparable to bulk silicon dioxide<sup>29</sup>. To further investigate the thermal stability of dielectrics made from fluorographene, we prepared a two-terminal diode using Ti contact electrodes by annealing the samples in a furnace using temperatures ranging from 100°C to 400°C in an ambient environment. According to their I-V curves, those samples subjected to temperatures less than 200°C retained high dielectric resistivities, showed non-ohmic contact behavior, and sustained measured currents of a few pAs. At higher annealing temperatures (up to 400°C), the samples exhibited diodelike behavior with currents as high as 200 pA. It is likely that in this case, the as-synthesized fluorographene was beginning to decompose because the C-F bonds become unstable at temperatures above  $260^{\circ}C^{30}$ . However, the effective resistivity (R = V/I) of the sample at 400°C was measured to be 1.45 G $\Omega$ ; thus, the sample was still highly insulating (the applied source-drain voltage is normally less than 10 V). The maintain of insulating character is possibly due to the formation of highly defective(vacancies) layers, where CF4 and C<sub>2</sub>F<sub>6</sub> gas are evolved during thermal defluorination resulting in defects and disruption within the layer. Dielectric materials used in IC and CMOS fabrication must be able to withstand high temperature post-annealing processes. The fluorographene dielectrics in this work maintain high resistivities up to temperatures of 400°C; thus, their properties are comparable to those of Teflon® and superior to those of GO, which rapidly undergoes oxygen desorption at 200°C<sup>31</sup>. Moreover, it is important to investigate the dependence of the electric field stress on the device resistance. Fluorographene exhibits insulating behavior  $(\sim 10^9 \,\Omega \,\text{sq}^{-1})^{21}$ , while the resistivity of GO<sup>32</sup> is only few 10 s of M $\Omega$  sq<sup>-1</sup>. GO has been used as a dielectric material in resistive random-access memory (RRAM)<sup>15</sup>, but GO becomes unstable under electric field stress because conductive paths are formed as oxygen migrates along the GO stacking layers. Therefore, GO dielectric materials at least 70 nm thick must be used so that leakage currents are eliminated<sup>16</sup>. Table S1 compares the electrical performance of graphene-based FETs composed of various dielectric materials, including thermally evaporated SiO<sub>2</sub>, ALD-synthesized Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, CVD-synthesized Si<sub>3</sub>N<sub>4</sub>, h-BN films, and GO films. The amount of drain-induced barrier lowering(DIBL), an effect of short-channel effect in MOSFETs, is often quantified to evaluate the integrity of a device upon downscaling. The electrostatic scaling length can be modeled as  $\lambda = (\epsilon_s t_s t_{ox} / \epsilon_{ox})^{1/2}$  for a planar device structure<sup>33</sup>, where t<sub>s</sub> and t<sub>ox</sub> are the thicknesses of the channel and gate oxide, respectively, and  $\varepsilon_{s}$  and  $\varepsilon_{ox}$  are the dielectric constants of the channel and gate oxide, respectively. The common approach to suppressing this DIBL effect is to decrease the scaling length  $\lambda$  by reducing the channel thickness; thus, a reduced Si thickness was pursued by the extremely thin silicon-on-insulator (ETSOI) method. Unfortunately, the mobility decreased as the thickness was scaled

**Figure 1** | Analysis of the dielectric properties of fluorographene: (a) Capacitance value and dielectric constant of fluorographene. The inset shows a schematic of a MIM capacitor. (b) and (c) Frequency dependence and the percentage of capacitance degradation for fluorographene and GO. (d) Dielectric breakdown of 10 L of fluorographene and graphene oxide (GO). (e) The current density of the fluorographene capacitor in (d). (f) Current-voltage measurement of single-layer fluorographene subjected to different annealing temperatures.

down<sup>34</sup>. Alternatively, this issue can be addressed by reducing the thickness of the channel and gate dielectric, preserving the high gate dielectric constant. Our presented structure, composed of atomically thin graphene and fluorographene as channel and dielectric materials, respectively, is therefore a promising candidate in this regard. The data indicate that, although they are very thin (<10 nm), the fluorographene samples studied here are sustainable at high gate voltages. Moreover, lower sub-threshold swing(SS) implies the channel current can be efficiently gated by applying lower gate voltage, suggesting the less power dissipation to operate a transistor<sup>35</sup>. For transistor with fluorinated graphene as dielectric layer, larger capacitance and lower sub-threshold swing could be achieved. A device made from such an extremely thin material would have the potential to be scaled down to the atomic level and be operated with less power dissipation.

#### Discussion

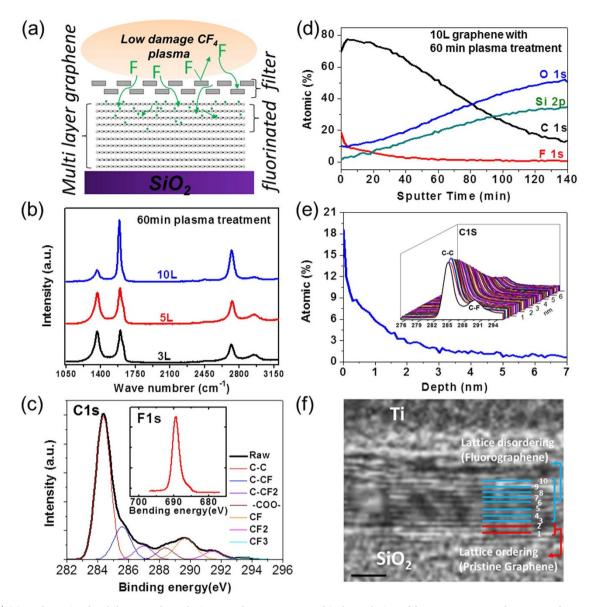

The fluorographene dielectric film studied here is made by stacking ten individual fluorographene layers (a transfer process was performed 10 times). This process is complicated and could hinder the use of such a material in particular applications. Consequently, we devised a way to synthesize the dielectric layer using a one-step fluorination process (a 60 min treatment) on a multi-layered graphene film, composed of either 3, 5, or 10 layers of graphene (the schematics shown in Figure 2a). Briefly, multi-layered fluorographene is created when high energy fluorine radicals induced by the plasma diffuse into the multi-layer graphene film. Figure 2b shows a typical Raman spectrum of a fluorinated multi-layer graphene sample, where the G peak (at  $\sim$ 1585 cm<sup>-1</sup>) and 2D peak (at  $\sim$ 2700 cm<sup>-1</sup>) are characteristic of the *sp*<sup>2</sup>-hybridized C-C bonds in graphene. Compared with pristine graphene, the D peak of the fluorographene at 1358 cm<sup>-1</sup> is much more intense, indicative of lattice disorder. Moreover, the G peak of the fluorographene is broad, and the shoulder D' peak is pronounced due to intra-valley scattering<sup>31</sup>, indicative of the formation of sp3-defects (C-F bonding) on the graphene plane. Figure 1c shows a typical XPS spectrum of a fluorinated graphene sample; the C 1s peak at 288.2 eV and the F 1s peak at 688.8 eV indicate the formation of C-F bonding states. The detail bonding states, including C-CF(286.3 eV), CF(289.4 eV), CF<sub>2</sub>(292.2 eV), CF<sub>3</sub>(293.1 eV), were also observed from the de-

**Figure 2** (a) A schematic of multilayer graphene during  $CF_4$  plasma treatment. (b) The evolution of the Raman spectra of 3 L, 5 L and 10 L of graphene after 60 min of plasma treatment. (c) XPS analysis of fluorographene, where the C 1s core level and several carbon-fluorine components are labeled. The inset shows the fluorine peak (F 1s) at 688.8 eV. (d) The elemental distribution of XPS depth profile for 10 L graphene and (e) the magnification of the changes for F at%, the inset shows the C1s spectra acquired along sample depth. (f) A TEM image of 10 L of fluorographene subjected to one-step fluoridation. The top 6–8 layers exhibit disordered lattice fringes (fluorographene) while the bottom 2–3 layers exhibit a highly ordered lattice (pristine graphene). The inset scale bar is 2 nm.

convolution of C1s spectrum. The spectra of fluorographene samples that are 3 and 5 layers thick are shown in Figure S1. According to XPS on 3 L sample, the estimated F/C ratio is 0.25, higher than that of 5 L(0.22) and 10 L(0.21). To further clarify the stoichiometric distribution along the depth profile of multi-layer fluorographene, we performed XPS depth profile analysis on the samples. The C and F signals from this spectral survey on the sample surface are clearly observed (Figure S2). The XPS depth profile shows that the distribution of fluorine atoms (Figure 2d and 2e) decreases as deeper sample depths are probed (from 15.9  $\pm$  2.6 at% on surface to 0.06  $\pm$  0.014 at % near the bottom), suggesting that different degrees of fluorination are achieved (e.g., from high near the surface to low near the bottom) during this one-step fluorination process. The F/C and CF<sub>2</sub>/CF ratio for this sample have been concluded in Table S2. The C-F<sub>2</sub> and C-F<sub>3</sub> indicate the structural defects on graphene and occurs mainly at defect such as vacancies, edge, or graphene boundaries<sup>21</sup>. The defects were introduced from the graphene transfer process.

Therefore, it is reasonable that more transferred graphene layers result in higher ratio of  $CF_2/CF$  ratio. The stacking layer preserves its layer structure (Figure 2f), indicating that CF plasma treatment does not severely harm the sample. Moreover, the bright-field TEM image (Figure 2f) of the top 6–8 atomic layers shows a disordered lattice fringe, while the bottom 2–3 layers exhibit a highly ordered lattice arrangement. The disordered arrangement can be attributed to the formation of fluorographene, where the lattice distortion resulted from the introduction of carbon fluoride bonds (C-F2, C-F3 and C-F), while the unfluorinated graphene (i.e, pristine graphene)is characterized by a highly ordered lattice. This result is consistent with the reported work on fluorinated carbon nano-fibers (CNF), for which the fluorinated part located near the surface and the unfluorinated CNF core can be distinguished by their lattice ordering<sup>37</sup>.

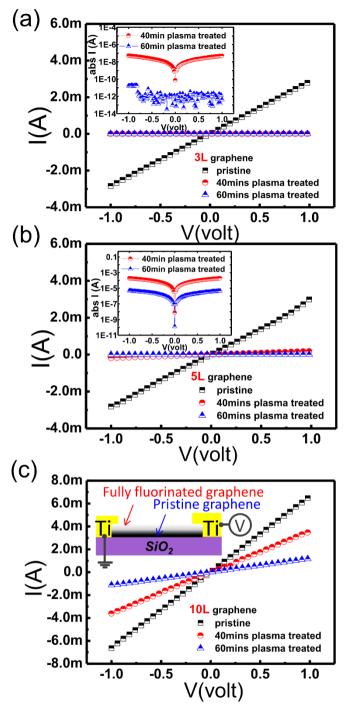

We characterized the electrical transport properties of 3-, 5- and 10- layered fluorographene samples (60 min plasma treatment; the resistor shown in inset in Figure 3c). Prior to the fluorination of these

Figure 3 | Current-voltage curves for (a) 3 L, (b) 5 L and (c) 10 L of graphene after different durations of plasma treatment. The insets in (a) and (b) are the log-scaled I–V curves for 40 and 60 min fluorinations, respectively. The inset in (c) shows a schematic of the graphene resistor.

multi-layered graphene (MLG) samples, their *I*–*V* curves shows perfect ohmic contact (Figure 3). The current values (at 1 V) obtained were proportional to the number of graphene layers. The current values decreased when the fluorination time was increased from 40 to 60 min. For 3-layer fluorographene, the currents decreased from 40 to 60 minutes, indicating that the sample was highly fluorinated(F/C:0.25). For the 5-layer fluorographene sample, the measured current did not decrease to the pA level, implying that the top 3 layers of the sample were highly fluorinated (insulating), while the bottom 2 layers were partially fluorinated (semiconducting) (Figure 2b). Here,

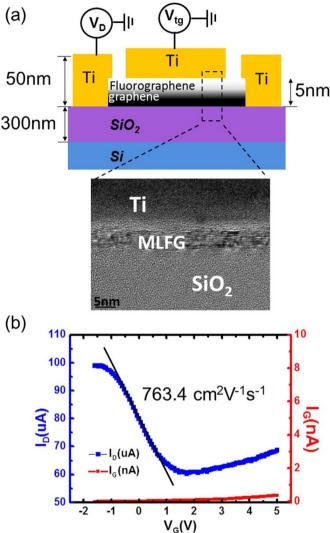

Figure 4 | (a) An illustration of a graphene-based FET composed of a fluorographene gate dielectric and the corresponding TEM cross-sectional image. (b) The transfer characteristics and the monitored gate current ( $I_G$ ) of these transistors, which demonstrate hole mobilities of 760 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at V<sub>D</sub> = 0.5 V.

it was found out that fluorination occurs deep within the bottom layers of a multi-staked graphene sample, while fluorination in previous work employing XeF<sub>2</sub> exposure was limited to the top layer of the sample<sup>21</sup>. In Figure 3c, currents of a few mini-amperes are observed for both the fluorinated and unfluorinated 10-L graphene samples, indicating that highly conductive pristine graphene persists in the bottom few layers of the sample (near the SiO<sub>2</sub>/graphene interface) even after 60 min of plasma treatment. These results are consistent with those obtained from the XPS depth profile and TEM analysis (Figure 2e–f).

As a proof-of-concept, the 10-layered fluorographene sample was investigated as a dielectric material in a graphene-based FET. Figure 4a shows a schematics of the device structure; the channel (length = 20  $\mu$ m, width = 4  $\mu$ m) was patterned using traditional photolithography techniques. The cross-sectional TEM image clearly shows that multi-layered graphene, composed of fluorographene and pristine graphene (Figure 2f), is formed between the top gate (Ti) and the SiO<sub>2</sub> substrate. Figure 4b shows the transfer curve for this device, where the drain-source voltage (V<sub>ds</sub>) was kept at 0.5 V and the gate voltage was swept from -2 to 5 V. The neutrality point appears at a positive voltage, indicating *p*-type doping on the gra-

phene channel likely because there is a strong electron acceptor above the fluorographene. Moreover, the leakage current is less than 0.5 nA when gate voltages up to 5 V are applied, suggesting that the sample has excellent dielectric properties. The equation,  $\mu = (L/$  $WC_{OX}V_D$ ) $(\Delta I_D/\Delta V_G)^{38}$ , was used to extract the field effect carrier mobility from the linear regime of the transfer curves, where L, W and  $C_{ox}$  are the channel length, the channel width and the gate capacitance, respectively. The field effect hole mobility was measured to be greater than 763.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (detailed calculation in S3), higher than that obtained when SiO<sub>2</sub> and GO were used as gate dielectric materials<sup>16,17,20</sup>. Thus, the fluorographene devices investigated here have superior mobilities compared to silicon-based FETs composed of ultra-thin Si films ((3.7 nm) (silicon-on-insulators (SOIs)) that typically have mobilities of 60 cm<sup>2</sup> V<sup>-1</sup> s<sup>-139</sup>. These fluorographene devices are promising for device scaling in CMOS applications.

#### Conclusion

In summary, fluorographene was utilized as the gate dielectric in a graphene-based field effect transistor. The fluorographene dielectric exhibited a high breakdown electric field (10 MV cm<sup>-1</sup>), and it is promising for use in applications and, in principle, for wafer-scale fabrication. Moreover, a one-step process for fluorinating multi-layered graphene (5 nm thick) that could be used to form a unique vertical heterostructures was demonstrated. This structure could readily be used as graphene-based FET, and it was found to have a high carrier mobility (760 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>). This present method has the potential to be used in the fabrication of next-generation nano-electronic devices.

#### **Methods**

**CVD growth and transfer process.** We described a detailed process for using CVD to grow graphene on Cu in previous work<sup>24</sup>. Briefly, copper (Cu) foil was loaded into a tube furnace. The growth temperature was set to 1000°C. A gas composed of methane and hydrogen (CH<sub>4</sub>/H<sub>2</sub> = 20 sccm/20 sccm) was introduced for 20 min. The system was then cooled down to room temperature (cooling rate ~5°C s<sup>-1</sup>), completing the growth process. The transfer process was based on the conventional poly(methyl methactylate) (PMMA) method.

**Graphene fluorination.** The PECVD chamber was evacuated to ~5 mTorr, and the temperature was increased from room temperature to 200°C. After the CF<sub>4</sub> gas was introduced into the chamber, the gas flow and pressure were controlled. The degree of fluorination of the sample was adjusted by controlling the exposure time (from 40 to 60 min) after the plasma was ignited.

**Ti/fluorographene/Ti capacitor.** The MIM capacitor was made according to the following steps: (i) evaporate Ti (100 nm) onto SiO<sub>2</sub>/Si (300 nm) to make the bottom electrode, (ii) grow graphene on Cu foil and fluorinate the sample for 30 min, (iii) transfer the fluorinated graphene onto the Ti (10 times) and (iv) deposit the Ti top electrode and pattern it using a lift-off technique.

**Graphene-based field effect transistor**. The device was made using the following process: (i) 10 layers of CVD-grown graphene (on SiO<sub>2</sub>/Si) sheets were stacked using a transfer process and the device channel was patterned using traditional lithography followed by a O<sub>2</sub> plasma etching step, (ii) the source and drain Ti electrodes (50 nm) were deposited using a thermal evaporator, (iii) the fluorographene dielectric layer was completed after 60 min of fluorination and (iv) the Ti top gate electrode (50 nm) was formed during thermal evaporation and lift-off.

**Raman scattering spectral analysis.** Raman scattering spectra were collected using a NT-MDT confocal Raman microscope system (laser excitation wavelength = 473 nm; laser spot-size ~0.5  $\mu$ m). The Raman scattering peak of Si at 520 cm<sup>-1</sup> was used as a reference for wavenumber calibration.

**X-ray photoelectron spectroscopy**. The chemical configurations were determined using an X-ray photoelectron spectrometer (XPS, Phi V6000). The XPS measurements were performed using a Mg K $\alpha$  x-ray source for sample excitation. The energies were calibrated relative to the C-1 s peak to eliminate the charging of the

energies were calibrated relative to the C 1 s peak to eliminate the charging of the sample during analysis. The XPS depth profile analysis was carried out by comprised of Ar ion sputtering(Iron gun:3 kV,1  $\mu$ m) and the X-ray probe(probing energy of X-ray: 108 w and 15 kV). The etching rate is 0.1 nm/sec and it was more than 70 points been acquired for 10 L graphene sample.

- 1. Schwierz, F. Graphene transistors. Nat. Nanotechnol. 5, 487-496 (2010).

- 2. Geim, A. K. Graphene: Status and Prospects. Science 324, 1530-1534(2009).

- 3. Lin, Y. M. et al. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. Science **327**, 662–662 (2010).

- Nair, R. R. et al. Fine structure constant defines visual transparency of graphene. Science 320, 1308–1308 (2008).

- 5. Bae, S. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotechnol. 5, 574–578 (2010).

- Cao, H., Yu, Q., Childres, I., Pei, S. S. & Chen, Y. P. High mobility ambipolar field effect transistors made from large-scale CVD graphitic thin films. *Proceedings of The IEEE Device Research Conference:IEEE DRC 2009*, Penn State University, PA, USA, (DOI:10.1109/DRC.2009.5354876), (2009, June 22–24), 133–134.

- Zhang, Y. B., Tan, Y. W., Stormer, H. L. & Kim, P. Experimental observation of the quantum Hall effect and Berry's phase in graphene. *Nature* 438, 201–204 (2005).

- Novoselov, K. S. *et al.* Electric field effect in atomically thin carbon films. *Science* 306, 666–669 (2004).

- 9. Berger, C. *et al.* Electronic confinement and coherence in patterned epitaxial graphene. *Science* **312**, 1191–1196 (2006).

- Lemme, M. C., Echtermeyer, T. J., Baus, M. & Kurz, H. A Graphene Field-Effect. Device. Electron Device Letters, IEEE 28, 282–284 (2007).

- Lee, B. et al. Conformal Al<sub>2</sub>O<sub>3</sub> dielectric layer deposited by atomic layer deposition for graphene-based nanoelectronics. App. Phys. Lett. 92, 203102-1-3 (2008).

- Kim, S. *et al.* Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric. *App. Phys. Lett.* **94**, 062107-1-3 (2009).

- Zou, K., Hong, X., Keefer, D. & Zhu, J. Deposition of High-Quality HfO2 on Graphene and the Effect of Remote Oxide Phonon Scattering. *Phys Rev Lett.* 105, 126601 (2010).

- Meric, I. *et al.* Graphene field-effect transistors based on boron nitride gate dielectrics, *Inter. Elec. Dev. Meet.:IEEE IEDM 2010*, San Francisco, CA, USA. IEEE International. (DOI: 10.1109/IEDM.2010.5703419), (2010, Dec 6–8), 23.22.21-23.22.24.

- Jeong, H. Y. et al. Graphene Oxide Thin Films for Flexible Nonvolatile Memory Applications. Nano Lett. 10, 4381–4386 (2010).

- Lee, S.-K. et al. All Graphene-Based Thin Film Transistors on Flexible Plastic Substrates. Nano Lett. 12, 3472–3476 (2012).

- 17. Eda, G. *et al.* Graphene oxide gate dielectric for graphene-based monolithic field effect transistors. *App. Phys. Lett.* **102**, 133108-1-4 (2013).

- He, C. L. *et al.* Nonvolatile resistive switching in graphene oxide thin films. *App. Phys. Lett.* **95**, 232101-1-3 (2009).

- Ki Hong, S., Eun Kim, J., Kim, S. O. & Jin Cho, B. Analysis on switching mechanism of graphene oxide resistive memory device. *J. Appl. Phys.* 110, 044506-1-5 (2011).

- Standley, B., Mendez, A., Schmidgall, E. & Bockrath, M. Graphene-Graphite Oxide Field-Effect Transistors. *Nano Lett.* 12, 1165–1169 (2012).

- Robinson, J. T. et al. Properties of Fluorinated Graphene Films. Nano Lett. 10, 3001–3005 (2010).

- 22. Withers, F. *et al.* Electron properties of fluorinated single-layer graphene transistors. *Phys. Rev. B* **82**, 073403-1-4 (2010).

- 23. Withers, F. *et al.* Tuning the electronic transport properties of graphene through functionalisation with fluorine. *Nanoscale Res. Lett.* **6**, 526-1-11 (2011).

- 24. Martins, S. E. et al. Tuning the transport gap of functionalized graphene via electron beam irradiation. New J. Phys. 15,033024-1-10 (2013).

- 25. Withers, F. *et al.* 3. Nanopatterning of Fluorinated Graphene by Electron Beam Irradiation. *Nano Lett.* **11**, 3912–3916 (2011).

- Lee, W. H. et al. Selective-Area Fluorination of Graphene with Fluoropolymer and Laser Irradiation. Nano Lett. 12, 2374–2378 (2012).

- Lee, W.-K. *et al.* Chemically Isolated Graphene Nanoribbons Reversibly Formed in Fluorographene Using Polymer Nanowire Masks. *Nano Lett.* 11, 5461–5464 (2011).

- Ho, K.-I. *et al.* One- Step Formation of a Single Atomic- Layer Transistor by the Selective Fluorination of a Graphene Film. *Small* 10, 989–997 (2014).

- Osburn, C. M. & Ormond, D. W. Dielectric Breakdown in Silicon Dioxide Films on Silicon: I. Measurement and Interpretation. *J. Electrochem. Soc.* 119, 591–597 (1972).

- Nair, R. R. *et al.* Fluorographene: A Two-Dimensional Counterpart of Teflon. Small 6, 2877–2884 (2010).

- Becerril, H. A. *et al.* Evaluation of Solution-Processed Reduced Graphene Oxide Films as Transparent Conductors. ACS Nano 2, 463–470 (2008).

- 32. Zhu, Y. *et al.* Graphene and Graphene Oxide: Synthesis, Properties, and Applications (vol 22, pg 3906, 2010). *Adv. Mater.* **22**, 5226–5226 (2010).

- 33. Yan, R. H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET from bulk to SOI to bulk. *IEEE Trans. Electron Dev.* 39, 1704–1710 (1992).

- Low, T. et al. Modeling study of the impact of surface roughness on silicon and Germanium UTB MOSFETs, IEEE Trans. Electron Dev. 52, 2430–2439 (2005).

- 35. Sze, S. M. et al. Chapter 6.2 Basic Device Characteristics, Physics of Semiconductor Devices. Sze, S. M.(ed.) 315(Wiley, New York, 2007).

- 36. Cancado, L. G., Pimenta, M. A., Neves, B. R. A., Dantas, M. S. S. & Jorio, A. Influence of the atomic structure on the Raman spectra of graphite edges. Phys Rev Lett. 93, 247401-1-4 (2004).

- 37. Chamssedine, F. et al. Reactivity of Carbon Nanofibers with Fluorine Gas. Chem. Mater. 19, 161-172 (2007).

- 38. Liu, K.-K. et al. Growth of Large-Area and Highly Crystalline MoS<sub>2</sub> Thin Layers on Insulating Substrates. Nano Lett. 12, 1538-1544 (2012).

- 39. Uchida, K. & Takagi, S.-I. Carrier scattering induced by thickness fluctuation of silicon-on-insulator film in ultrathin-body metal-oxide-semiconductor fieldeffect transistors. App. Phys. Lett. 82, 2916-2918 (2003).

#### Acknowledgments

This research was supported by the Ministry of Science and Technology, Taiwan (NSC 101-2218-E-182-003-MY2 and 102-2221-E-008-113-MY3).

#### **Author contributions**

K.I.H. performed the major part of the experiments. C.H.H. and J.H.L. help on XPS and device fabrication. W.Z. and L.J.L. help to do Raman characterization on graphene sample. C.S.L. analysis the device performance. C.Y.S. conceived the idea and wrote the paper. All the authors discussed the results, commented on and revised the manuscript.

#### Additional information

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Ho, K.-I. et al. Fluorinated Graphene as High Performance Dielectric Materials and the Applications for Graphene Nanoelectronics. Sci. Rep. 4, 5893; DOI:10.1038/srep05893 (2014).

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http:// creativecommons.org/licenses/by-nc-nd/4.0/