# Frequency-Independent Equivalent-Circuit Model for On-Chip Spiral Inductors

Yu Cao, Student Member, IEEE, Robert A. Groves, Member, IEEE, Xuejue Huang, Member, IEEE, Noah D. Zamdmer, Jean-Olivier Plouchart, Member, IEEE, Richard A. Wachnik, Member, IEEE, Tsu-Jae King, Senior Member, IEEE, and Chenming Hu, Fellow, IEEE

Abstract—A wide-band physical and scalable  $2\text{-}\Pi$  equivalent circuit model for on-chip spiral inductors is developed. Based on physical derivation and circuit theory, closed-form formulas are generated to calculate the RLC circuit elements directly from the inductor layout. The  $2\text{-}\Pi$  model accurately captures R(f) and L(f) characteristics beyond the self-resonant frequency. Using frequency-independent RLC elements, this new model is fully compatible with both ac and transient analysis. Verification with measurement data from a SiGe process demonstrates accurate performance prediction and excellent scalability for a wide range of inductor configurations.

Index Terms—Circuit model, current-crowding effect, frequency dependence, quality factor, spiral inductor, 2- $\Pi$ .

### I. INTRODUCTION

N SILICON-BASED radio-frequency (RF) integrated circuits (ICs), on-chip spiral inductors are widely used due to their low cost and ease of process integration [1]. As a necessary tool for circuit design, equivalent circuit models of spiral inductors, using lumped *RLC* elements, efficiently represent their electrical performance for circuit simulation with other design components. Compared with the generic electromagnetic field solver (e.g., Maxwell) or other partial-element-equivalent-circuit (PEEC)-based solvers [2] (e.g., Sonnet, ASITIC [3]), a lumped equivalent-circuit model dramatically reduces computation time and supports rapid performance optimization. On the other hand, model inaccuracy, which stems from the complexity of on-chip inductor structures and high-frequency phenomena, presents one of the most challenging problems for RF IC designers [4].

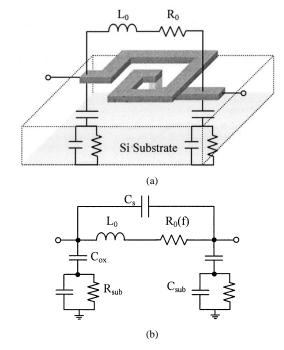

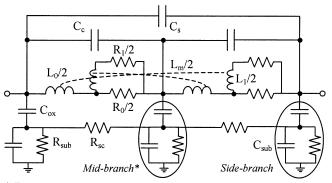

Current equivalent-circuit approaches simply represent the inductor as a lumped single- $\Pi$  circuit [5]–[8]. Fig. 1 reviews the single- $\Pi$  structure. In this scalable model, series metal resistance and inductance, feedthrough capacitance, dielectric isolation, and substrate effects are modeled. In [6], a variable  $R_0$  is used to model the skin effect, and in [8], a more physical

Manuscript received July 16, 2002; revised October 5, 2002.

Y. Cao, T.-J. King, and C. Hu are with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720-1772 USA (e-mail: ycao@eecs.berkeley.edu, tking@eecs.berkeley.edu, hu@eecs.berkeley.edu).

X. Huang is with Rambus Inc., Los Altos, CA 94022 USA (e-mail: xuejue@cal.berkeley.edu).

R. A. Groves, N. D. Zamdmer, J.-O. Plouchart, and R. A. Wachnik are with IBM, Microelectronics Division, Hopewell Junction, NY 12533 USA (e-mail: grovesr@us.ibm.com, noahz@us.ibm.com, plouchar@us.ibm.com, wachnik@us.ibm.com).

Digital Object Identifier 10.1109/JSSC.2002.808285

Fig. 1. Conventional single- $\Pi$  circuit structure. (a) On-chip implementation of a spiral inductor. (b) Equivalent single- $\Pi$  representation.

model is proposed to capture the high-frequency behavior. Although physical considerations are included in such a structure, the single- $\Pi$  model lacks the following important features.

- Strong frequency dependence of R and L as a result of current crowding in the conductor, i.e., both the skin effect and the proximity effect, which leads to significant degradation of the quality factor Q at gigahertz frequencies.

- Distributed characteristics to match high-frequency behavior, especially for inductors with large dimensions. In addition, metal-line-coupling capacitance is also nonnegligible for thick metal cases.

- Frequency-independent circuit elements for compatibility

with transient analysis and broad-band design. A fixed R<sub>0</sub>

is proper for narrow-band design [5]; it is difficult to incorporate R<sub>0</sub> in SPICE-type simulators [6].

As RF circuit design requires precise performance prediction, the shortcomings of the single- $\Pi$  model limit its design optimization capability [9]. To overcome the model inaccuracies, a new wide-band physically based scalable equivalent-circuit model for on-chip spirals is demonstrated in this work.

Addressing the current crowding effect and distributed characteristics, our approach is formulated to capture R(f) and L(f) behavior with an equivalent 2- $\Pi$  ladder circuit containing frequency-independent RLC elements. All element values can be analytically calculated based on the inductor layout parameters. This new model extends the region of model validity beyond the self-resonant frequency and fully supports both ac and transient circuit simulations. Verification with measurement data demonstrates excellent scalability for a wide range of inductor configurations. This new 2- $\Pi$  equivalent circuit was first introduced in [10], and we present the detailed model development in this paper.

# II. PHYSICAL GENERATION OF 2-∏ MODEL

When operating frequencies enter the multigigahertz regime, silicon-based spiral inductors suffer from three major energy dissipation mechanisms that lead to poor inductor Q. The challenge for establishing a lumped circuit model is to properly account for the following mechanisms:

- 1) Ohmic  $(I^2R)$  loss in the conductive substrate, which is due to the displacement current conducted through the metal-to-substrate capacitance. It is modeled by a substrate RC network comprised of  $C_{\rm ox}$ ,  $R_{\rm sub}$ , and  $C_{\rm sub}$  [11], [12].

- 2) Loss due to eddy current in the underlying substrate, induced by the penetration of the magnetic field into the conductive silicon. This is substantial when substrate resistivity is low (e.g., <1  $\Omega$ -cm). The case of less conductive substrate (e.g., >10  $\Omega$ -cm) can effectively reduce this loss to negligible values [13]. Therefore, in our SiGe BiCMOS process with substrate resistivity larger than  $10~\Omega$ -cm [14], we do not include this effect. For other technologies, substrate eddy loss can be modeled by mutual inductance between metal and substrate [1]. The loss in the substrate can be reduced by introducing a patterned ground shield [16], although this technique sacrifices the self-resonant frequency and only efficiently reduces the electrical loss [17].

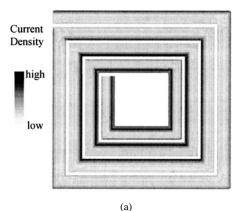

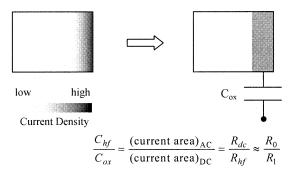

- 3) Energy loss inside the nonzero-resistivity metal lines, which is from current flowing through the spiral inductor itself and includes both ohmic and eddy-current loss. The eddy-current loss is generated by inductive coupling between turn-to-turn metal lines. As a result, line resistance and inductance show a clear dependence on frequency due to nonuniform current density in the conductor [8], [18]. Using ASITIC, Fig. 2(a) illustrates the current distribution in a spiral inductor at 3 GHz. As shown in Fig. 2(b), the metal resistance rises rapidly with increasing frequency while line inductance is less sensitive to the current-crowding effect.

The energy loss in the metal is one of the primary sources of energy dissipation and is intrinsic to the spiral structure. The lumped single- $\Pi$  model is not sufficient to model this effect and overly optimistic performance predictions have been seen in [9]. To accurately account for this effect, we introduce a new circuit structure. In our new approach, a ladder circuit is developed to replace the series R and L in the single- $\Pi$  model in order

Fig. 2. Current-crowding-caused frequency-dependent R(f) and L(f) characteristics. (a) Current distribution in a spiral inductor at 3 GHz (top view). Width =  $25\,\mu\mathrm{m}$ ; spacing =  $5\,\mu\mathrm{m}$ ; outer diameter =  $320\,\mu\mathrm{m}$ . (b) Normalized resistance and inductance. ( $R_{\mathrm{dc}}=0.19\,\Omega$ ,  $L_{\mathrm{dc}}=3.7\,\mathrm{nH}$ .

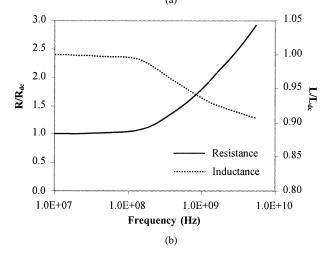

to capture the frequency-dependent resistance and inductance. Fig. 3 illustrates the physical phenomena related to each circuit element.

For a single metal line, the dc current is uniformly distributed inside the conductor. Therefore, it can be represented as a  $R_0$  and  $L_0$  in series (Fig. 3). As the frequency goes up, the depth of current penetrating into the metal (skin depth) becomes comparable to or even smaller than the cross-sectional dimensions of the line. For example, the skin depth of copper is 2  $\mu$ m at 1 GHz and decreases proportionally with the square root of frequency. The skin effect pushes the ac current toward the surface of the conductor. To capture the effect of different current densities in different conduction layers, additional RL branches can be introduced in parallel to  $R_0$  to represent each conduction layer in depth [19]. By adding more ladder branches, the skin effect can be accurately modeled up to an arbitrary maximum frequency. For model simplicity, we only bring in one  $R_1L_1$  branch, which models the surface layer resistance and inductance (Fig. 3) [20].

In addition to the skin effect, the magnetic field generated by neighboring lines further changes the current distribution and results in a higher current density at the edges of the metal lines [Fig. 2(a)]. This is described as the proximity effect and has a greater impact than the skin effect on the increase of resistance and degradation of Q in present-day spiral inductor designs [13]. Since the inductance  $L_0$  is induced by the magnetic field in the

Fig. 3. Frequency-independent ladder circuit representation to capture R(f) and L(f).

\* For symmetry,  $C_{mid}$ =2 $C_{side}$ ,  $R_{mid}$ = $R_{side}$ /2; the dependence of  $R_{sub}$  on the location of substrate contact can be captured by unsymmetrical branches.

Fig. 4. New 2- $\Pi$  model. R(f) and L(f), distributed characteristics, and substrate effects are well modeled.

adjacent space of the line, we model the magnetic interaction between the external field and internal current by adding the mutual inductance  $L_m$  between  $L_0$  and  $L_1$  (Fig. 3).

Based on the ladder circuit representation, a symmetrical 2- $\Pi$ equivalent circuit model is built to capture the distributed characteristics of an on-chip spiral inductor. Fig. 4 illustrates the final lumped model. First, the original ladder circuit ( $R_0$ ,  $L_0$ ,  $R_1$ , and  $L_1$ ) is evenly split into two parts. In order to properly capture the inductive coupling among metal lines, the mutual inductance  $\mathcal{L}_m$  is cross coupled between the two parts. Then, we add the substrate circuit ( $C_{ox}$ ,  $C_{sub}$ , and  $R_{sub}$ ) and feedthrough capacitance  $C_s$  similarly to [6]. In addition, we use  $C_c$  and  $R_{sc}$  to model the line-to-line coupling capacitance and direct turn-to-turn electric coupling through the dielectric materials  $(C_{ox})$  and the conductive substrate, respectively. For spiral inductors with symmetrical layout, their 2-Π subnetworks are identical; otherwise, the 2- $\Pi$  subnetworks are different only in their substrate circuits (e.g., the substrate branch closer to the input port has the values proportional to the metal length of the input turn). With all frequency-independent elements, the final 2-∏ ladder circuit accounts for all major physical phenomena occurring in spiral inductors.

TABLE I ANALYTICAL FORMULAS FOR CIRCUIT ELEMENTS

| Parameters | Analytical Equation         |  |

|------------|-----------------------------|--|

| $R_0$      | $(1+n_r^{-1})R_{dc}$        |  |

| $L_0$      | $(1-3.57k/n_r^{3/2})L_{dc}$ |  |

| $R_I$      | $n_r R_0$                   |  |

| $L_{I}$    | $L_0/(0.315n_r)$            |  |

| $L_m$      | $k\sqrt{L_0L_1}$            |  |

where  $n_r$  is the positive root of

$$(0.315R_{dc}^2)/(m\omega_{crit}^2L_{dc}^2) \cdot n_r^2 + (\varepsilon_{ox}length^2)/(6C_{ox}L_{dc}c^2) \cdot n_r - 1 = 0$$

$$k = \sqrt{\frac{0.315}{m}} \cdot (\frac{R_{dc}}{\omega_{crit}L_{dc}}) \cdot n_r, \qquad \omega_{crit} = \frac{3.1}{\mu_0} \cdot \frac{P}{w^2} \cdot R_{sheet}$$

and

$$m = \frac{240}{N^{1.23}}$$

(N is the number of turns)

w: metal width;  $R_{sheet}$ : metal sheet resistance;

P: metal pitch; length: total length of the metal line.

### III. ANALYTICAL RLC ELEMENT CALCULATIONS

The key to a compact inductor model is the capability to physically and accurately link the layout to performance through a set of analytical formulas. For this purpose, after setting up the circuit structure, the closed-form solution for each element is developed based on its physical origin. Table I lists the exact results. Extensive derivations are presented in this section.

# A. Substrate Network

The substrate resistance  $R_{\rm sub}$  and capacitance  $C_{\rm sub}$  model the ohmic loss in the conductive silicon substrate. Since the on-chip spiral inductor is implemented in the same layers as on-chip interconnects, we can calculate them as in [12] with the knowledge of inductor layout and process technology, assuming an uniformly doped substrate.  $R_{sc}$ , which represents the electric coupling between lines through the conductive substrate, is approximately proportional to the resistance of the substrate below the inductor and can be estimated by

$$R_{sc} = \frac{1.5 \cdot (\text{substrate resistivity}) \cdot N \cdot P}{(\text{metal length}) \cdot (\text{substrate thickness})}$$

(1)

where N is the number of turns and P is the metal line pitch (i.e., metal width plus the metal spacing from edge to edge).

### B. DC Inductor Resistance, Capacitance, and Inductance

There have been extensive investigations on inductor resistance and inductance calculations at low frequency ( $R_{\rm dc}$  and  $L_{\rm dc}$ ) [2], [3], [5], [6], [19]–[21].  $R_{\rm dc}$  is equal to the product of the metal sheet resistance and the aspect ratio of the metal line (total metal length/metal width). Instead of using a numerical methodology to calculate  $L_{\rm dc}$ , we apply the analytical equations from [22] and [23] for single-turn and multiple-turn spiral inductor  $L_{\rm dc}$  calculations, respectively. The accuracy of those

equations have been well verified for a wide range of inductor configurations. Furthermore, metal-to-metal and metal-to-substrate capacitances ( $C_s$ ,  $C_c$ , and  $C_{\rm ox}$ ) are calculated using analytical two-dimensional capacitance equations such as those in [24] and then scaled with their effective coupling lengths.

# C. Ladder Circuit Elements

The critical and unique circuit component in our 2- $\Pi$  model is the ladder circuit ( $R_0$ ,  $L_0$ ,  $R_1$ ,  $L_1$ , and  $L_m$ ), which accounts for the inductor resistance and inductance characteristics at high frequencies, i.e., both skin and proximity effects. Instead of resorting to numerical or purely empirical techniques to determine their values, we solve for them together with the following physical constraints.

1) Metal Layer Partition: The first constraint comes from the physical origin of the ladder branch  $(R_1 \text{ and } L_1)$  in parallel with  $R_0$ . Since  $R_1L_1$  models the metal surface layer and  $R_0L_0$  models the overall conductor, their relationship is uniquely defined upon selecting a partition ratio for the outer layer to the overall cross section. An empirically optimized condition from [20] can be expressed as

$$\frac{L_0}{L_1} = 0.315 \cdot \frac{R_1}{R_0}. (2)$$

2) Electromagnetic Analysis of R(f): The second constraint is generated by matching the physical analysis of R(f) with our ladder circuit prediction. In [13], an analytical equation for frequency dependence of the resistance of a multiturn spiral inductor is derived from fundamental electromagnetic principles

$$R(f) = R_{\rm dc} \cdot \left(1 + \frac{1}{10\omega_{\rm crit}^2} \cdot \omega^2\right) \tag{3}$$

where  $\omega_{\rm crit}$  can be calculated from geometrical size, as listed in Table I. A similar but more physical R(f) model is derived in [8] and can also be used for the purpose of prediction. On the other hand, from our ladder circuit and the PEEC-based circuit theory [25], we derive the approximate relationship

$$R(f) = R_{\rm dc} \cdot \left(1 + \frac{L_m^2}{R_0 R_1} \cdot \omega^2\right). \tag{4}$$

By matching the coefficients of  $\omega^2$  in (3) and (4), the physical constraint from R(f) is obtained

$$m\omega_{\rm crit}^2 L_m^2 = R_o R_1 \tag{5}$$

where m is a new parameter we introduce to model the dependence on the number of turns N [m=10 in (3)]. As increasing numbers of parallel lines leads to stronger proximity effect, metal resistance shows more significant frequency dependence when N is larger. Exact calculation of m is extrapolated from measurement data (Table I).

3) Relationship of LC at High Frequency: The third constraint accounts for the fundamental limitation of a LC system. From Maxwell's equations, the relationship between L and C in the metal—oxide—silicon system at extremely high frequencies is known to be

$$\frac{L_{\rm hf}C_{\rm hf}}{({\rm metal\ length})^2} = \frac{\varepsilon_{\rm ox}}{c^2} \tag{6}$$

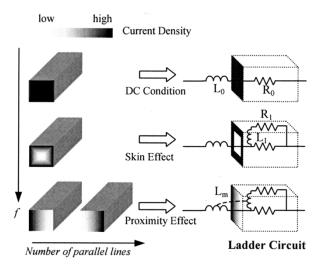

Fig. 5. Cross section of a metal line at high frequency.  $C_{\rm hf}$  scales with the current-conducting area, which decreases at high frequency. This effect leads to larger ac resistance.

where c is the speed of light in a vacuum and  $\varepsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub>. As the ladder circuit model shows

$$L_{\rm hf} = \left(1 - \frac{L_m^2}{L_0 L_1}\right) \cdot L_0. \tag{7}$$

For high-frequency capacitance  $C_{\rm hf}$  calculation, if we assume that  $C_{\rm ox}$ , which is similar as a parallel-plate capacitance, is proportional to the effective area occupied by the ac current in the inductor, then  $C_{\rm hf}$  scales with resistance when the current is pushed to the edge of the metal line due to proximity effect, as illustrated in Fig. 5. Therefore,  $C_{\rm hf}$  can be approximately calculated as

$$C_{\rm hf} = \frac{R_0}{R_1} \cdot C_{\rm ox}.\tag{8}$$

Using (7) and (8) in (6), we then have

$$C_{\rm ox} \cdot \left(\frac{R_0}{R_1}\right) \cdot \left(L_0 - \frac{L_m^2}{L_1}\right) = \varepsilon_{\rm ox} \cdot \frac{({\rm metal \ length})^2}{6c^2} \quad (9)$$

where the factor of 6 is a parameter fitted from measurement in order to improve the accuracy.

4) Resistance and Inductance at Low Frequency: The last two constraints ensure the correct inductor characteristics at dc condition. At low frequency, the ladder circuit should be equivalent to  $R_{\rm dc}$  and  $L_{\rm dc}$  in series. Thus, we obtain the following two conditions from circuit theory:

$$R_{\rm dc} = \frac{R_0 R_1}{R_0 + R_1} \tag{10}$$

$$L_{\rm dc} = L_0 + \left(\frac{R_0}{R_0 + R_1}\right)^2 \cdot L_1 \tag{11}$$

where  $R_{\rm dc}$  and  $L_{\rm dc}$  are solved as described in Section III-B.

Combining the five physical constraints in (2), (5), and (9)–(11), the ladder circuit elements  $(R_0, L_0, R_1, L_1, \text{ and } L_m)$  are solved in closed form as listed in Table I. They are scalable functions of the inductor dimensions and independent of frequency.

# IV. MODEL VERIFICATION

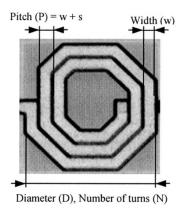

To verify the accuracy and scalability of the 2- $\Pi$  circuit model, test structures of octagonal spiral inductors with various geometrical configurations were fabricated using a 0.18- $\mu$ m eight-metal aluminum SiGe BiCMOS technology (substrate resistivity is larger than 10  $\Omega$  · cm). A microphotograph of

Fig. 6. Octagonal spiral inductor micrograph.

TABLE II

RANGE OF DIMENSIONS FOR TEST STRUCTURES

| w (μm) | s (µm) | D (μm)    | N     |

|--------|--------|-----------|-------|

| 5 – 25 | 5      | 220 - 420 | 1 - 9 |

one such structure, with layout variables defined, is shown in Fig. 6. The range of test structure dimensions is summarized in Table II, including different metal width, outer dimension, and number of turns. After de-embedded S parameter measurement, the equivalent R(f) and L(f) of spiral inductors are extracted from  $Y_{21}$

$$R + j\omega L = -\frac{1}{Y_{21} + j\omega C_s} \tag{12}$$

i.e., matching to the normal single- $\Pi$  structure. The 2- $\Pi$  model predicted Y parameters are produced using SPICE. Both the single-port quality factor

$$Q = -\frac{\text{Im}(Y_{11})}{\text{Re}(Y_{11})} \tag{13}$$

and differential quality factor (ports driven 180° out of phase)

$$Q_{\rm df} = -\frac{\operatorname{Im}(Z_{11} + Z_{22} - Z_{12} - Z_{21})}{\operatorname{Re}(Z_{11} + Z_{22} - Z_{12} - Z_{21})}$$

(14)

are evaluated. Although Q as defined in [26] provides more physical meaning, we keep the definitions as (13) and (14) to be consistent with other publications and provide fair comparisons.

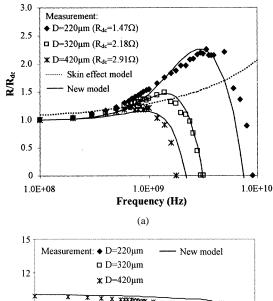

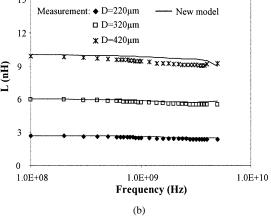

Fig. 7 shows the normalized R(f) and L(f) curves for three test structures, which differ only in outer diameter. As the measurement data illustrate, the ac resistance above 1 GHz can be more than two times larger than the dc resistance. The skin effect alone cannot describe such a rapid increase, especially for multiple-turn inductors where the inductive coupling among lines are strong, as shown in Fig. 7(a). The new model correctly captures the rapid increase in resistance due to current crowding effect for various dimensions, while the skin effect model in [6] significantly underestimates the rate of increase and lacks model scalability for different structures. Fig. 7(a) also illustrates that the equivalent R drops down at high frequency due to the distributed nature of the spiral inductors, which cannot be

Fig. 7. Verification of frequency dependence of R and L. ( $w=15\mu m, P=20\mu m, N=4$ ). (a) Resistance as a function of frequency and dimensions. (b) Inductance as a function of frequency and dimensions.

predicted by the single- $\Pi$  model [27]. A trend in RF IC design is to use copper technology and larger cross-section metal lines to reduce metal resistance and improve Q. However, it should be noted that this technique is less effective at high operating frequency because of severe current crowding and distributed effects. Accurate modeling of these high-frequency characteristics is crucial for correct inductor design and performance analysis. As shown in Fig. 7(b), the change in inductance as a function of spiral structure and frequency is also well captured by our model beyond the self-resonant frequency.

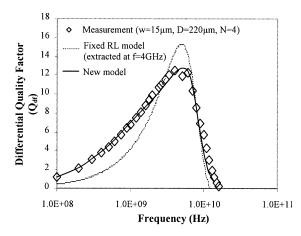

Because existing inductor models either cannot support transient analysis [6], [8] or neglect the frequency dependence of R(f) and L(f) [5], [7], a common compromise is to extract R and L at a specific frequency, e.g., the operating frequency, and use the fixed values for further circuit simulation. While this approach is suitable for single-frequency simulation, it is inaccurate over large frequency ranges and, therefore, introduces significant error in transient analysis [9]. This is demonstrated in Fig. 8. With a fixed R and L extracted at 4 GHz,  $Q_{\rm df}$  is underestimated by more than 50% at 1.5 GHz and the peak value is overestimated by 17%. Iterations between estimation of peak Q frequency and inductor layout are helpful to reduce this error, although it requires more computation time and designer's insight. The new model accurately and efficiently predicts  $Q_{\rm df}$  over the entire frequency range of interest.

Fig. 8. Usage of fixed R and L leads to large error in overall characteristics. New model matches measurement accurately.

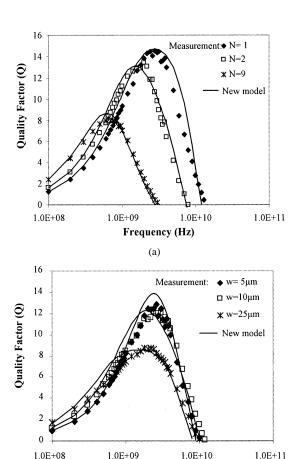

Fig. 9. New model has excellent scalability and predictability. (a) Structures with a different number of turns ( $w=15~\mu\mathrm{m},~P=420~\mu\mathrm{m}$ ).

Frequency (Hz)

Fig. 9 verifies Q for different inductor structures. In current design, the degradation of Q at high frequency is attributed to eddy-current loss in the metal, substrate loss and, finally, the self-resonance. The new 2- $\Pi$  equivalent circuit accurately models all of these phenomena and demonstrates excellent scalability for prediction of both the peak value and frequency response of the quality factor. Results from comprehensive model

TABLE III

COMPREHENSIVE MODEL EVALUATION

| w    | D    | N  | Q peak    | c / GHz   | Q <sub>df</sub> pea | k / GHz   |

|------|------|----|-----------|-----------|---------------------|-----------|

| (µm) | (µm) | IN | Meas.     | Model     | Meas.               | Model     |

| 5    | 220  | 4  | 12.9/2.6  | 13.8/2.5  | 16.2/3.0            | 19.8/3.0  |

| 10   | 220  | 4  | 12.1/2.4  | 12.2/2.2  | 15.7/3.4            | 14.9/3.2  |

| 15   | 420  | 1  | 14.7/2.8  | 14.7/2.8  | 19.7/3.8            | 19.5/4.0  |

| 15   | 420  | 2  | 13.4/2.0  | 13.1/1.8  | 19.1/2.6            | 17.0/2.6  |

| 15   | 320  | 4  | 11.1/1.4  | 10.7/1.4  | 15.1/2.2            | 14.2/2.4  |

| 15   | 220  | 4  | 10.2/3.4  | 9.1/3.4   | 12.5/3.6            | 11.9/3.8  |

| 15   | 420  | 4  | 11.5/1.2  | 11.6/1.0  | 15.8/1.6            | 14.2/1.4  |

| 15   | 320  | 6  | 9.2/1.2   | 10.0/1.0  | 11.9/1.8            | 11.8/1.6  |

| 15   | 420  | 9  | 8.0/0.7   | 8.7/0.7   | 10.0/0.95           | 10.1/0.90 |

| 20   | 420  | 4  | 10.9/0.85 | 11.3/0.85 | 15.3/1.8            | 14.2/1.6  |

| 25   | 320  | 4  | 8.5/1.6   | 8.5/1.6   | 11.0/2.8            | 10.2/3.0  |

evaluations are summarized in Table III. The root-mean-square error for the peak value (frequency) of Q and  $Q_{\rm df}$  are 5.6% (5.7%) and 8.6% (7.1%), respectively.

### V. CONCLUSION

A new 2- $\Pi$  equivalent-circuit model for on-chip spiral inductors has been developed. Verification with measurement data from various test structures demonstrates the validity of this model. Since all elements are frequency independent, it is fully compatible with transient analysis and wide-band design. The excellent scalability of this model is advantageous for spiral inductor design automation.

# ACKNOWLEDGMENT

The authors would like to thank Prof. A. Niknejad and Dr. X. Zhang for valuable suggestions.

## REFERENCES

- J. N. Burghartz et al., "RF circuit design aspects of spiral inductors on silicon," *IEEE J. Solid-State Circuits*, vol. 33, pp. 2028–2034, Dec. 1998

- [2] A. E. Ruehli, "Inductance calculations in a complex integrated circuit environment," *IBM J. Res. Develop.*, pp. 470–481, Sept. 1972.

- [3] A. Niknejad. ASITIC. Univ. California, Berkeley. [Online]. Available: http://formosa.eecs.berkeley.edu/~niknejad/asitic.html

- [4] P. R. Gray and R. G. Meyer, "Future directions in silicon ICs for RF personal communications," in *Proc. IEEE Custom Integrated Circuits Conf.*, June 1995, pp. 83–89.

- [5] J. R. Long and M. A. Copeland, "The modeling, characterization, and design of monolithic inductors for silicon RF ICs," *IEEE J. Solid-State Circuits*, vol. 32, pp. 357–369, Mar. 1997.

- [6] C. P. Yue and S. S. Wong, "Physical modeling of spiral inductors on silicon," *IEEE Trans. Electron Devices*, vol. 47, pp. 560–568, Mar. 2000.

- [7] A. Niknejad and R. Meyer, "Analysis, design, and optimization of spiral inductors and transformers for Si RF ICs," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1470–1481, Oct. 1998.

- [8] J. Sieiro et al., "A physical frequency-dependent compact model for RF integrated inductors," *IEEE Trans. Microwave Theory Tech.*, vol. 50, pp. 384–392, Jan. 2002.

- [9] D. Leenaerts, G. Gielen, and R. A. Rutenbar, "CAD solutions and outstanding challenges for mixed-signal and RF IC design," in *Proc. IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD)*, Nov. 2001, pp. 270–277.

- [10] Y. Cao et al., "Frequency-independent equivalent circuit model for on-chip spiral inductors," in Proc. IEEE Custom Integrated Circuits Conf., June 2002, pp. 217–220.

- [11] J. Jasegawa, M. Furukawa, and H. Yanai, "Properties of microstrip line on Si-SiO<sub>2</sub> system," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-19, pp. 869–881, Nov. 1971.

- [12] Y. Eo and W. R. Eisenstadt, "High-speed VLSI interconnect modeling based on S-parameter measurement," *IEEE Trans. Compon., Hybrids, Manufact. Tech.*, vol. 16, pp. 555–562, Aug. 1993.

- [13] W. B. Kuhn and N. M. Ibrahim, "Analysis of current crowding effects in multiturn spiral inductors," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 31–38, Jan. 2001.

- [14] R. Grovers, D. L. Harame, and D. Jadus, "Temperature dependence of Q and inductance in spiral inductors fabricated in a silicon–germanium/BiCMOS technology," *IEEE J. Solid-State Circuits*, vol. 32, pp. 1455–1459, Sept. 1997.

- [15] W. B. Kuhn and N. K. Yanduru, "Spiral inductor substrate loss modeling in silicon RF ICs," *Microwave J.*, pp. 66–81, Mar. 1999.

- [16] C. P. Yue and S. Simon, "On-chip spiral inductors with patterned ground shields for Si-based RF ICs," *IEEE J. Solid-State Circuits*, vol. 33, pp. 743–752, May 1998.

- [17] C.-M. Hung and K. K. O, "A 1.24-GHz monolithic CMOS VCO with phase noise of -137 dBc/Hz at a 3-MHz offset," *IEEE Microwave Guided Wave Lett.*, vol. 9, pp. 111–113, Mar. 1999.

- [18] H. Tsai et al., "Investigation of current crowding effect on spiral inductors," in *IEEE Microwave Theory and Techniques Symp. Dig.*, 1997, pp. 139–142.

- [19] H. A. Wheeler, "Formulas for the skin effects," Proc. IRE, pp. 412–424, 1942.

- [20] S. Kim and D. P. Neikirk, "Compact equivalent circuit model for the skin effect," in *IEEE Microwave Theory and Techniques Symp. Dig.*, 1996, pp. 1815–1818.

- [21] H. M. Greenhouse, "Design of planar rectangular microelectronic inductors," *IEEE Trans. Parts, Hybrids, Packag.*, vol. PHP-10, pp. 101–109, June 1974.

- [22] E. Pettenpaul et al., "CAD models of lumped elements on GaAs up to 18 GHz," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 294–304, Feb. 1988

- [23] S. S. Mohan et al., "Simple accurate expressions for planar spiral inductances," *IEEE J. Solid-State Circuits*, vol. 34, pp. 1419–1424, Oct. 1999.

- [24] S. Wong, G. Lee, and D. Ma, "Modeling of interconnect capacitance, delay, and crosstalk in VLSI," *IEEE Trans. Semiconduct. Manufact.*, vol. 13, pp. 108–111, Feb. 2000.

- [25] B. Young, Digital Signal Integrity. Englewood Cliffs, NJ: Prentice-Hall, 2001.

- [26] K. O, "Estimation methods for quality factors of inductors fabricated in silicon integrated circuit process technologies," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1249–1252, Aug. 1998.

- [27] S.-M. Yim, T. Chen, and K. O, "The effects of a ground shield on the characteristics and performance of spiral inductors," *IEEE J. Solid-State Circuits*, vol. 37, pp. 237–244, Feb. 2002.

**Yu Cao** (S'98) received the B.S. degree in physics from Peking University, Beijing, China, in 1996 and the M.A. degree in biophysics from the University of California, Berkeley, in 1999, where he is currently working toward the Ph.D. degree in electrical engineering.

In the summer of 2000, he was with Hewlett-Packard Labs, Palo Alto, CA, as a Research Intern, and in the summer of 2001, he was with IBM Microelectronics Division, East Fishkill, NY, working on RF spiral inductor modeling. From

2001 to 2002, he consulted with Celestry Design Technologies, Inc., San Jose, CA, on RF design tool development. He has one pending U.S. patent. His research interests include high-speed interconnect design and analysis, nanometer CMOS design solutions, and mixed-signal design.

Mr. Cao received the 2000 Beatrice Winner Award at the IEEE International Solid-State Circuits Conference.

**Robert A. Groves** (M'94) received the B.S.E.E. degree (*summa cum laude*) from the State University of New York in 1996.

He joined IBM Corporation, Microelectronics Division, East Fishkill, NY, in 1989 as a Development Lab Technician. Since 1994, he has worked on SiGe model development in the IBM Communications Research and Development Center, with an emphasis on high-frequency modeling and characterization. His current interest is in microwave passive devices on silicon (interconnect, capacitors, and inductors), particularly integrated spiral inductor optimization and modeling.

**Xuejue Huang** (S'97–M'03) received the B.E degree from Huazhong University of Science and Technology, Wuhan, China, in 1994, and the M.S. and Ph.D. degrees in electrical engineering and computer sciences from the University of California, Berkeley, in 1999 and 2002, respectively.

In the summer of 2000, she was with Hewlett-Packard Laboratories, Palo Alto, CA, as a Research Intern working on circuit design techniques to suppress on-chip power/ground noise. In the summer of 2001, she was with the IBM

T. J. Watson Research Center, Yorktown Heights, NY, working on interconnect modeling and optimization for multigigahertz clock network design. She joined Rambus Inc., Los Altos, CA, as a Member of Technical Staff in 2002. Her current research interests include high-speed IC design and signal integrity analysis.

**Noah D. Zamdmer** received the B.S. and M.S. degrees in 1994 and the Ph.D. degree in 1999 in electrical engineering, all from the Massachusetts Institute of Technology, Cambridge.

He joined IBM Microelectronics in 1999, where he is currently involved in SOI technology development, with emphasis on RF applications and the high-frequency characterization and modeling of FETs. He holds one U.S. patent.

Dr. Zamdmer is a Member of Phi Beta Kappa.

**Jean-Olivier Plouchart** (M'97) was born in Paris, France, in 1966. He received the M.S. and Ph.D. (Hon.) degrees in electrical engineering from Paris VI University in 1988 and 1994, respectively.

From 1988 to 1989, he was with Alcatel Telspace, involved in MESFET GaAs MMICs design for satellite telecommunications. From 1989 to 1990, he was a Scientist Consultant at the ETCA as part of his military service. In 1990, he joined the French Telecom Laboratory (CNET) to develop the MMIC GaAs HBT technological process and to design HBT MMICs for DCS1800 radiocommunications and high-bit-rate optical telecommunications. In 1994, he joined the University of Michigan, Ann Arbor, as a Research Fellow, where he designed high-speed circuits using a 100-GHz InP HBT process. In 1996, he joined the IBM T. J. Watson Research Center, East Fishkill, NY, as a Research Scientist, where his work involved the design of SiGe BiCMOS and CMOS RFIC circuits. He has published more than twenty papers on RF IC design. Currently, he leads the development of SOI technology for low-power SOC applications at the IBM Semiconductor and Research Design Center.

**Richard A. Wachnik** (M'82) received the B.S. degree in physics from the Massachusetts Institute of Technology, Cambridge, and the Ph.D. degree in materials science and engineering from the University of Pennsylvania, Philadelphia, where he synthesized and studied the electronic properties of graphite compounds.

He is currently Manager of Technology Integration with the IBM Microelectronics Semiconductor Research and Development Center, East Fishkill, NY. At the National Institute of Standards and Technology, he developed an early analytical model of charge pumping in MOSFETs. At IBM, he holds patented and has published in the areas of reliability and processing of high-performance IC technologies.

**Tsu-Jae King** (S'89–M'91–SM'96) received the B.S., M.S., and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, where her research involved the seminal study of polycrystalline silicon–germanium films and their applications in metal–oxide semiconductor technologies.

She joined the Xerox Palo Alto Research Center as a Member of the Research Staff in 1992, to research and develop polycrystalline-silicon thin-film transistor technologies for high-performance flat-panel

display and imaging applications. In August 1996, she joined the faculty of the University of California, Berkeley, where she is currently an Associate Professor of electrical engineering and computer sciences and the Director of the UC Berkeley Microfabrication Laboratory. She has served on committees for many technical conferences including the Device Research Conference, the International Conference on Solid State Devices and Materials, and the International Electron Devices Meeting. Her current research activities are in sub-50-nm Si devices and technology, thin-film materials and devices for integrated microsystems, and large-area electronics. She has authored or coauthored over 150 publications and holds six U.S. patents.

Dr. King is a Member of the Electrochemical Society, the Society for Information Display, and the Materials Research Society, and is currently a member of the IEEE Electron Device Society VLSI Technology and Circuits Technical Committee. Since 1999, she has served as an Editor for the IEEE ELECTRON DEVICE LETTERS.

**Chenming Hu** (S'71–M'76–SM'83–F'90) received the B.S. degree from the National Taiwan University, Taipei, Taiwan, R.O.C., and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Berkeley.

He is the CTO of the Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, Taiwan. He is currently on leave from UC Berkeley. He leads the development of the industry standard MOSFET model for IC simulation, BSIM. He has authored or coauthored five books and over 700 research papers.

He is a Member of the Editorial Boards of the *Journal of Semiconductor Science and Technology* and the *Journal of Microelectronics Reliability*.

He received the 1997 IEEE Jack A. Morton Award for contributions to the physics of MOSFET reliability and the 2002 IEEE Solid State Circuits Award for his work on BSIM. He is a Member of the U.S. National Academy of Engineering, a Fellow of the Institute of Physics, and a Life Honorary Professor of the Chinese Academy of Science. He has received the Monie A. Ferst Award of Sigma Xi, the W. Y. Pan Foundation Award, the DARPA Most Significant Technological Accomplishment Award for codeveloping the FinFET transistor structure, and UC Berkeley's highest honor for teaching—the Distinguished Teaching Award.