# Fully FPGA-based Sensorless Control for synchronous AC drive using an Extended Kalman Filter

Lahoucine Idkhajine

# ▶ To cite this version:

Lahoucine Idkhajine. Fully FPGA-based Sensorless Control for synchronous AC drive using an Extended Kalman Filter. Automatic. Université de Cergy-Pontoise, 2010. English. tel-01994860

# HAL Id: tel-01994860 https://hal.archives-ouvertes.fr/tel-01994860

Submitted on 8 Feb 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Année 2010

UNIVERSITE DE CERGY PONTOISE

# THESE

Présentée pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITE DE CERGY PONTOISE

Ecole doctorale: Sciences et Ingénierie Spécialité: Génie Electrique

Soutenue publiquement le 24 Novembre 2010

Par

Lahoucine IDKHAJINE

# Fully FPGA-based Sensorless Control for Synchronous AC Drive using an Extended Kalman Filter

#### JURY

| Président          | : | Prof. Benoît ROBYNS                            | HEI Lille                                                                                |

|--------------------|---|------------------------------------------------|------------------------------------------------------------------------------------------|

| Rapporteurs        | : | Dr. François AUGER<br>Prof. Serge PIERFEDERICI | Université de Nantes<br>ENSEM Nancy                                                      |

| Examinateurs       | • | Prof. Marcian CIRSTEA<br>Dr. Josep GUERRERO    | Anglia Ruskin University – Royaume Uni<br>Universitat Politècnica de Catalunya – Espagne |

| Directeur de thèse | : | Prof. Eric MONMASSON                           | Université de Cergy Pontoise                                                             |

Laboratoire SATIE - UCP/UMR 8029, 1 rue d'Eragny, 95031 Neuville sur Oise France

Je dédie ce travail à toute ma famille, à ma mère, à mon père, à ma sœur et à mon frère pour leur soutien et leur affection. Une pensée à mon grand père AGNTAF M'Barek, que Dieu ait son âme ! L'objectif du travail réalisé dans le cadre de cette thèse est de montrer l'intérêt d'utiliser les FPGAs (Field Programmable Gate Array) comme support pour l'implantation d'algorithmes complexes dédiés à la commande de machines électriques. Pour ce faire, une commande sans capteur mécanique utilisant un filtre de Kalman étendu et basée sur FPGA est réalisée. Cette commande est destinée à piloter une machine synchrone à pôles saillants. Le modèle d-q de la machine basé sur l'approximation d'inertie infinie est implanté. L'ordre du Filtre de Kalman est donc égal à 4 et la complexité totale de la boucle de régulation est évaluée à près de 700 opérations arithmétiques (dont plus de 53% de multiplications). Les apports des solutions FPGAs en termes de performances de contrôle et en termes de capacité d'intégration sont quantifiés.

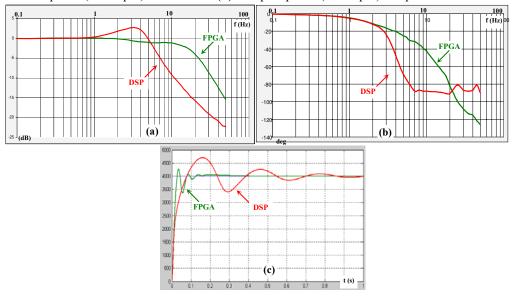

En termes de performances de contrôle, il a été démontré qu'en utilisant de telles solutions matérielles, le temps de calcul est très réduit (de l'ordre de 5µs, 5% de la période d'échantillonnage). Cette rapidité de calcul permet d'avoir un contrôle quasi-instantané ce qui améliore la bande passante de la boucle de régulation. A ce sujet, une comparaison avec les performances obtenues avec une solution logicielle telle que le DSP est effectuée. Dans les deux cas, le comportement dynamique de la boucle de régulation sans capteur est quantifié.

En termes de capacité d'intégration, il est possible de développer une architecture commune qui peut être adaptée à plusieurs systèmes. A titre d'exemple, il est possible de développer un filtre de Kalman sur un même FPGA capable d'estimer les grandeurs de plusieurs systèmes sans pour autant affecter les performances de contrôle.

En outre, une méthodologie de développement dédiée à de tels algorithmes complexes est proposée. Il s'agit là d'une adaptation des méthodologies proposées dans des travaux de thèse précédents, [62] et [63]. En effet, une étape de spécification préliminaire du système ainsi que des procédures d'optimisation supplémentaires y sont introduites. Ces dernières sont particulièrement nécessaires dans le cas de commandes complexes et permettent une adéquation entre l'algorithme développé et l'architecture FPGA correspondante. De plus, cette méthodologie a été organisée de façon à distinguer l'étape du développement de l'algorithme et l'étape du développement de l'architecture FPGA.

Un état de l'art sur les technologies FPGA est également proposé. La structure interne des FPGAs récents est décrite. Leur contribution dans le domaine de la commande des machines électriques est quantifiée. Les différentes étapes de la méthodologie de développement sont présentées.

Le développement d'une commande numérique (basée sur FPGA) d'une machine synchrone à aimants permanents associée à un capteur de position Resolver est par la suite traité. Cette application s'inscrit dans un contexte avionique où l'objectif était d'avoir une solution FPGA hautement intégrée. Pour cela, le FPGA Actel Fusion est utilisé. Ce composant intègre un convertisseur analogique numérique. La commande, le traitement des signaux Resolver ainsi que la conversion analogique numérique sont implantés sur le même composant.

En ce qui concerne la commande sans capteur basée sur le filtre de Kalman étendu, il a été décidé de structurer les chapitres correspondants à travers la méthodologie de développement proposée. Ainsi, la phase de spécification préliminaire du système, la phase du développement de l'algorithme, la phase du développement de l'architecture FPGA et la phase d'expérimentation sont séparément traitées. Durant la phase d'expérimentation, la procédure *«Hardware-In-the-Loop (HIL)»* est incluse afin de valider le fonctionnement de l'architecture développée une fois la phase d'implantation physique achevée.

- Réseaux de portes programmables Field Programmable Gate Array

- Méthodologie de développement

- Commande sans capteur mécanique

- Filtre de Kalman Etendu

- Machine synchrone à pôles saillants

- Machine synchrone à aimant permanent

- Capteur de position Resolver

- Traitement des signaux Resolver

The aim of this thesis is to present the interest of using Field Programmable Gate Array (FPGA) devices for the implementation of complex AC drive controllers. The case of a sensorless speed controller using the Extended Kalman Filter (EKF) has been chosen and applied to a Salient Synchronous Machine (SSM). The d-q model based on the infinite inertia hypothesis has been implemented. The corresponding EKF order is then equal to 4 and the complexity of the whole sensorless controller is equal to 700 arithmetic operations (more than 53% of multiplications). The contribution of FPGAs in this field has been quantified in terms of control performances and in terms of system integration.

In terms of control performances, the proposed FPGA-based solution ensures a short execution time which is around  $5\mu s$  (5% of the sampling period). This treatment fastness ensures a quasi-instantaneous control which improves the control bandwidth. To this purpose, a comparison with a software DSP-based solution is made. The dynamic behavior and the influence of the execution time, in both cases, on the control bandwidth have been quantified.

In terms of integration capacity, it is possible to implement a generic FPGA architecture that can be adapted to the control of several systems. Thus, it is possible to develop a common EKF architecture that is able to estimate variables from many systems without affecting the control performances.

In addition, a design methodology adapted to such complex controllers has been proposed. The particularity of this updated methodology, compared to the previous ones ([62], [63]), is to provide an enlarged set of steps starting from the preliminary system specification to the ultimate experimentation. Optimization procedures have also been introduced. These optimizations are necessary in case of complex controllers and lead to the adequation between the developed algorithm and the corresponding hardware FPGA architecture.

A state of the art FPGA technology is also presented. The internal structure of the recent devices and their corresponding technology are discussed. Their contribution in the field of AC drive applications is quantified. An in-depth presentation of the proposed design methodology is made.

Besides, the development of a fully integrated FPGA-based controller for a Permanent Magnet Synchronous Machine (PMSM) associated with a Resolver sensor is presented. This controller has been developed for an aircraft application where the main objective was to develop a fully integrated FPGA solution. The Actel Fusion FPGA device has been used. This device integrates an Analog to Digital Converter (ADC). The current controller, the Resolver Processing Unit (RPU) and the analog to digital conversion are implemented within the same device.

When it comes to the sensorless controller, the corresponding chapters have been structured according to the presented design methodology: the preliminary system specification, the algorithm development, the FPGA architecture development and finally the experimentation. The latter includes Hardware-In-the-Loop (HIL) tests and the final experimental validation.

- Field Programmable Gate Array

- Design methodology

- Sensorless controller

- Extended Kalman Filter

- Salient Synchronous Machine

- Permanent Magnet Synchronous Machine

- Resolver sensor

- Resolver Processing Unit

Les travaux de thèse présentés dans ce mémoire ont été réalisés au sein de l'équipe SETE (Systèmes d'Energies pour les Transports et l'Environnement) du laboratoire SATIE (Systèmes et Applications des Technologies de l'Information et de l'Energie), antenne de l'université de Cergy-Pontoise.

Ces quelques remerciements témoignent de la reconnaissance que je porte à toutes celles et tous ceux qui ont contribué de près ou de loin à la réussite de ce travail.

Je ne puis commencer sans remercier mon directeur de thèse Eric MONMASSON, Professeur des Universités à l'université de Cergy-Pontoise et directeur de recherche de l'antenne du laboratoire SATIE à Cergy-Pontoise. J'ai eu la grande chance d'avoir été sous sa direction depuis mon premier stage de Master. J'ai pu découvrir un homme aux grandes qualités humaines et scientifiques. Je ne lui exprimerai jamais assez ma profonde reconnaissance pour tous ses conseils, ses encouragements, sa confiance et les conditions de travail excellentes qu'il m'a procurées.

Je voudrais également exprimer mes sincères et inoubliables remerciements à Sandrine LEBALLOIS, Maître de Conférences à l'université de Cergy-Pontoise. En effet, elle a été à l'origine de mon parcours et ma réussite puisque c'est elle qui m'a conseillé, encouragé et soutenu pour continuer mes études et m'orienter vers le domaine de l'enseignement et la recherche.

Je tiens aussi à remercier Wissem NAOUAR, Enseignant Chercheur à l'ENIT (Ecole Nationale d'Ingénieurs de Tunis) pour son incomparable soutien, ses qualités humaines et ses précieux conseils qu'il m'a prodigués tout au long de cette période.

Mes remerciements s'adressent aussi à mes très chères collègues Amira MALOUF, Imene BAHRI et Herie PARK. J'ai eu le grand plaisir de travailler avec elles et j'ai particulièrement apprécié leur amitié, leur soutien et leur esprit d'équipe.

Je profite également de cette occasion pour exprimer ma profonde reconnaissance à Isabelle COLLET, Aude BREBANT, Don Abasse BOUKARI et Kamel BOUALLAGA pour leur amitié, leur contribution et leur soutien sans limite tout au long de cette période.

Mes vifs remerciements s'adressent également à Jean-Yves LEHUEROU, Bruno BUSSO, Lionel VIDO, Dejan VASIC ainsi que tout le corps professoral de l'Institut Universitaire Professionnalisé (IUP-GEII) de l'université de Cergy-Pontoise.

Je ne peux terminer sans avoir une pensée à mon grand père M'Barek (que Dieu ait son âme), mon grand père Lahcen, mes parents Mohamed et Yamina, mon frère Youssef, ma sœur Nadia et toute ma famille, pour leurs soutien et encouragements. Je voudrais souligner que ma réussite est d'abord et avant tout leur réussite. Je voudrais en outre témoigner mes sincères reconnaissances à la famille BIZOUNKAD et plus particulièrement à Lahcen BIZOUNKAD qui n'a cessé de m'assurer tous les moyens moraux et matériels pendant mes études en France.

#### **General Introduction**

| 1. | Thesis objectives and author contributions | 12 |

|----|--------------------------------------------|----|

|    | Outline                                    |    |

| 3. | Nomenclature                               | 14 |

### Chapter 2: State of the art FPGA technology

| 1. Introduction                                           |    |

|-----------------------------------------------------------|----|

| 2. Generic structure of an FPGA                           | 19 |

| 2.1. Logic Blocks                                         |    |

| 2.2. Interconnection network                              |    |

| 2.3. Clock manager blocks                                 |    |

| 2.4. I/O blocks                                           |    |

| 2.5. Arithmetic (DSP) blocks                              |    |

| 2.6. Memory blocks                                        |    |

| 2.7. Communication blocks                                 |    |

| 2.8. Embedded processor cores                             |    |

| 2.9. Configuration technology                             |    |

| 3. Case studies                                           |    |

| 3.1. SRAM based technology                                | 25 |

| 3.2. Antifuse based technology                            |    |

| 3.3. Flash based technology                               | 27 |

| 3.4. Feature summary                                      |    |

| 4. Design tools                                           |    |

| 5. Contribution of FPGAs in complex AC drive applications | 30 |

| 5.1. Evaluation in terms of control performances          |    |

| 5.2. Evaluation in terms of system integration            |    |

| 5.3. FPGA implementation constraints                      |    |

| 6. FPGA design methodology for control applications       | 35 |

| 6.1. Preliminary system specification                     |    |

| 6.2. Algorithm development                                |    |

| 6.3. FPGA-based architecture development                  |    |

| 6.4. Experimentation                                      |    |

| 7. Conclusion                                             | 43 |

# Chapter 3: Fully integrated FPGA-based controller for a PMSP associated with a resolver sensor

| 1. Introduction                                                                  | 45 |

|----------------------------------------------------------------------------------|----|

| 2. Description and implementation of the FPGA integrated ADC                     | 47 |

| 3. Resolver Processing Unit                                                      | 48 |

| 3.1. Resolver sensor description                                                 | 48 |

| 3.2. RPU principle                                                               |    |

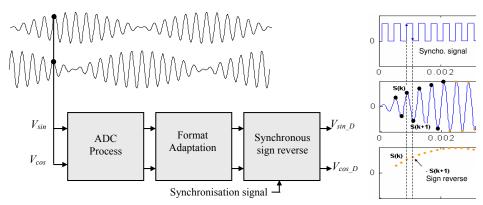

| 3.3. Synchronous demodulation                                                    |    |

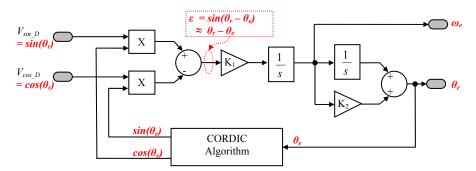

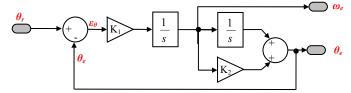

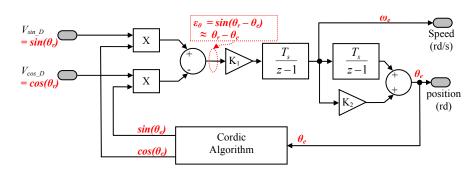

| 3.4. Angle Tracking Observer (ATO)                                               |    |

| 3.5. Compensation of the ADC Sampling Synchronization Error for resolver signals |    |

| 3.6. Evaluation of the noise rejection                                           |    |

| 3.7. Experimentation                                                             | 54 |

| 4. FPGA-based controller description                                             |    |

| 4.1. Controller timing diagram.                                                  |    |

| 4.2. Compensation of ADC Sampling Synchronization Error for PMSM currents        |    |

| 4.3. Experimental results                                   | 0 |

|-------------------------------------------------------------|---|

| 4.4. Time/Area performances                                 |   |

| 4.5. Influence of the execution time on the control quality |   |

| 5. Conclusion                                               |   |

# Chapter 4: FPGA-based sensorless control for synchronous AC drive - Preliminary system specification

| 1. Introduction                                                    | 61 |

|--------------------------------------------------------------------|----|

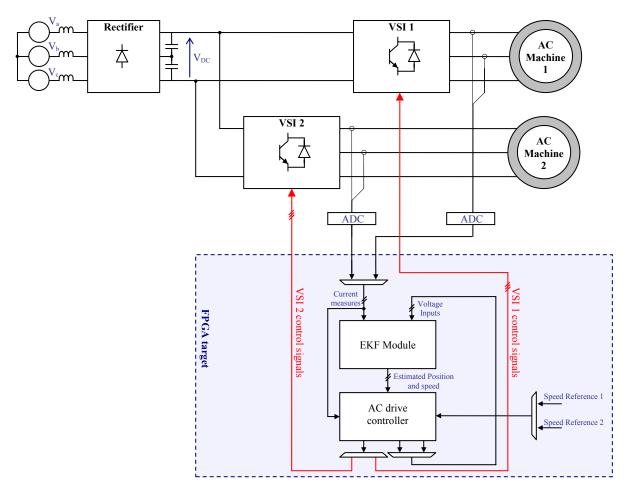

| 2. Sensorless control system - Hardware specification              | 62 |

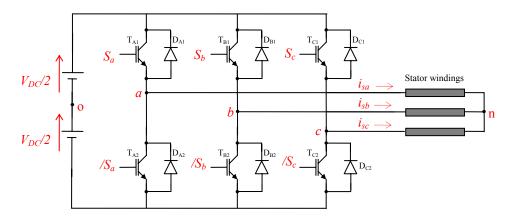

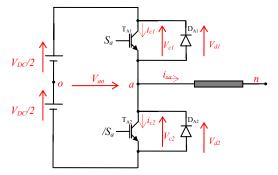

| 2.1. Power stage                                                   |    |

| 2.2. Electrical sensors, ADC and DAC boards                        |    |

| 2.3. FPGA-based digital control unit                               | 63 |

| 2.4. Host-PC interface                                             | 63 |

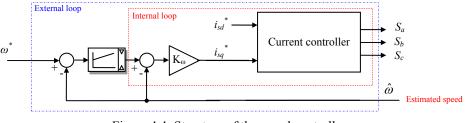

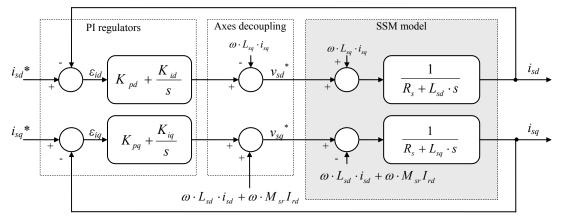

| 3. Stator current controller and speed controller                  |    |

| 3.1. Stator current controller                                     | 63 |

| 3.2. PWM specifications                                            | 64 |

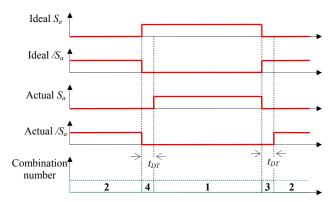

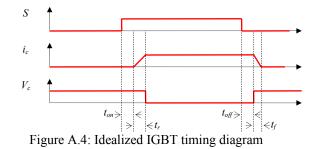

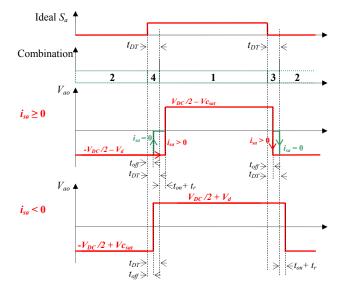

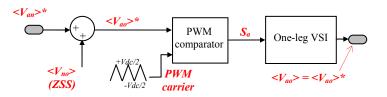

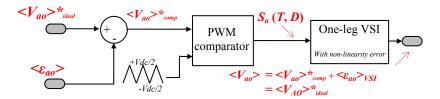

| 3.3. Compensation of VSI nonlinearities                            | 64 |

| 3.4. Speed controller                                              | 65 |

| 3.5. Voltage interface                                             | 65 |

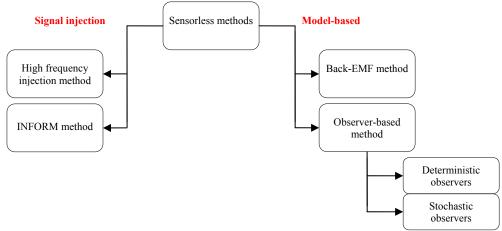

| 4. Estimation of the rotor position and speed - sensorless methods | 65 |

| 4.1. Sensorless methods based on signal injection                  | 66 |

| 4.2. Sensorless methods based on the motor model                   | 66 |

| 4.3. Choice of the sensorless method                               |    |

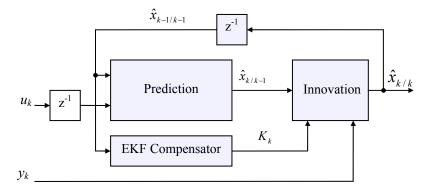

| 5. Extended Kalman Filter basics                                   | 67 |

| 6. System state space modeling                                     | 69 |

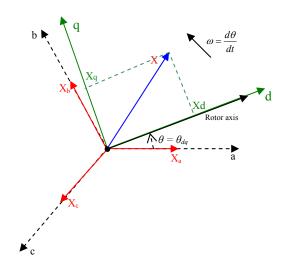

| 6.1. Modeling in (d-q) rotating frame                              | 69 |

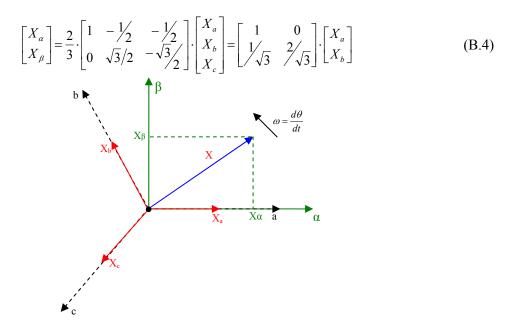

| 6.2. Modeling in $(\alpha - \beta)$ stationary frame               |    |

| 6.3. Choice of the model                                           |    |

| 7. Conclusion                                                      | 75 |

# Chapter 5: FPGA-based sensorless control for synchronous AC drive - Algorithm development

| 1. | Introduction                                                 | 77 |

|----|--------------------------------------------------------------|----|

| 2. | Modular partitioning                                         | 78 |

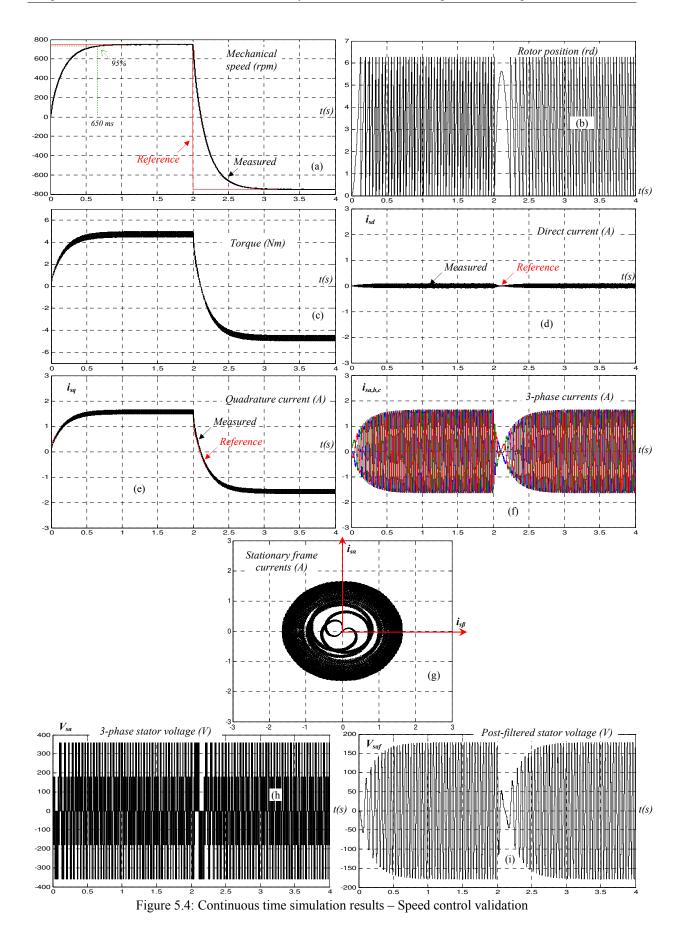

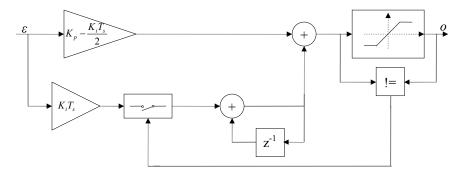

| 3. | Continuous-time functional simulation                        | 78 |

| 4. | Digital realization                                          | 82 |

|    | 4.1. Discretization and sampling period setting              | 82 |

|    | 4.2. Algorithm normalization                                 | 83 |

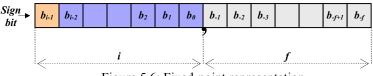

|    | 4.3. Fixed-point data setting                                | 84 |

| 5. | Algorithm optimization                                       |    |

|    | 5.1. EKF complexity pre-evaluation                           | 87 |

|    | 5.2. Optimization of the EKF algorithm                       |    |

|    | 5.3. Complexity post-evaluation                              |    |

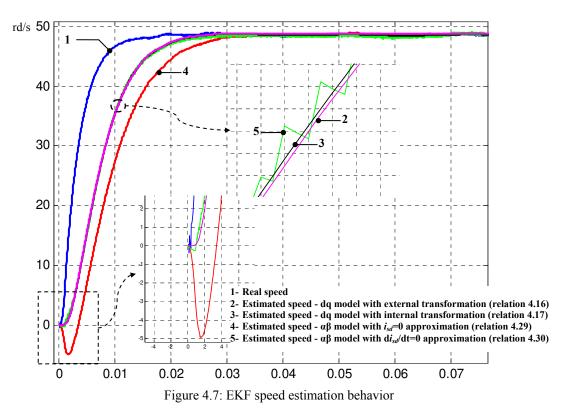

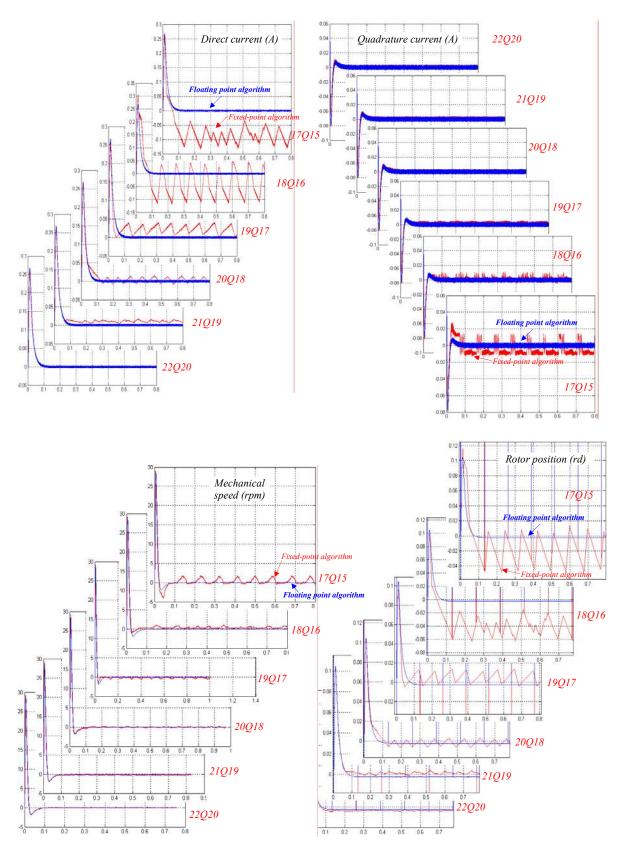

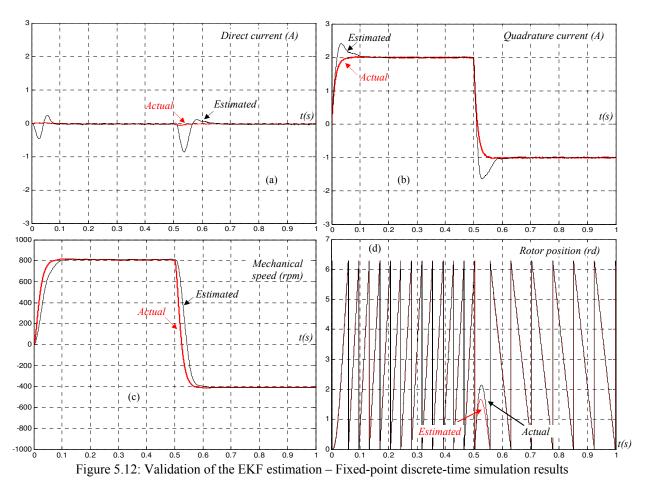

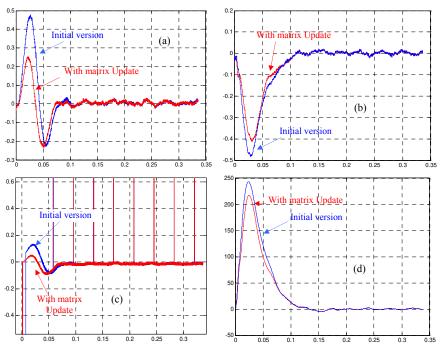

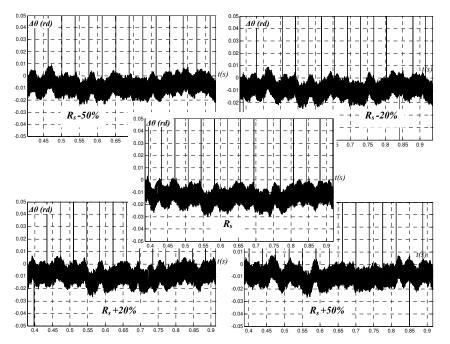

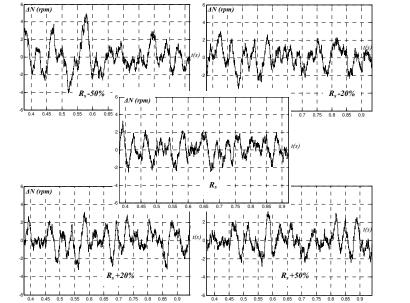

| 6. | Discrete-time, fixed-point simulation                        | 89 |

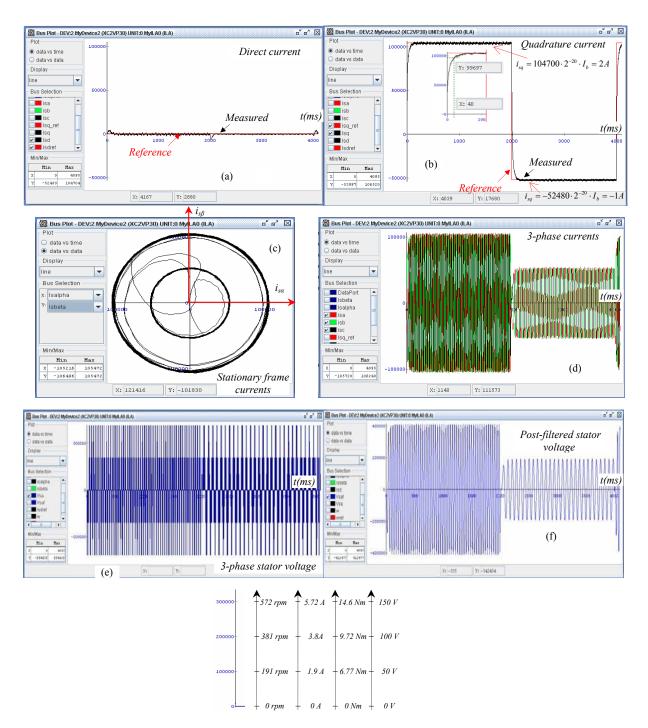

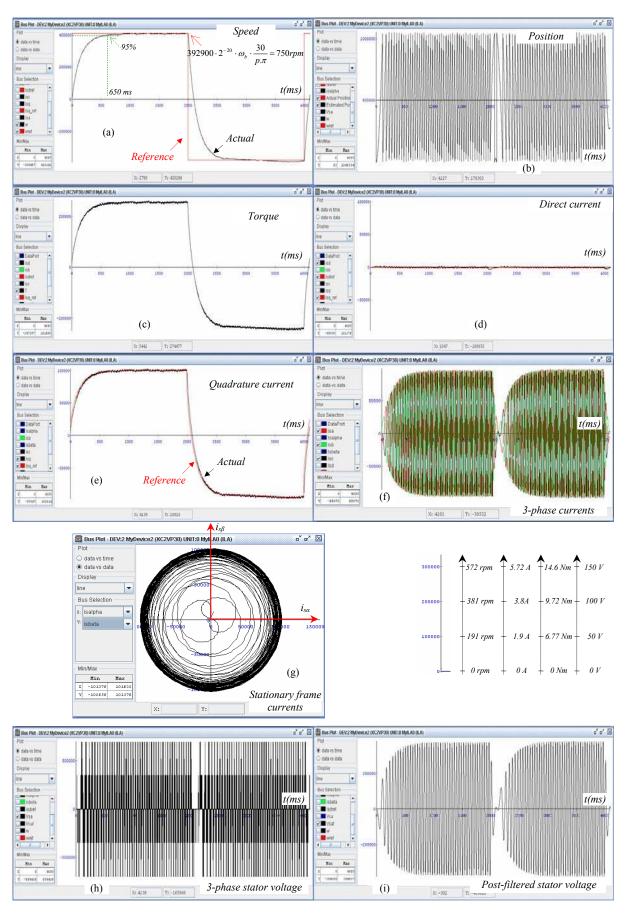

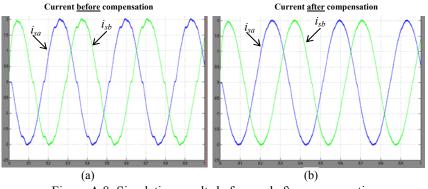

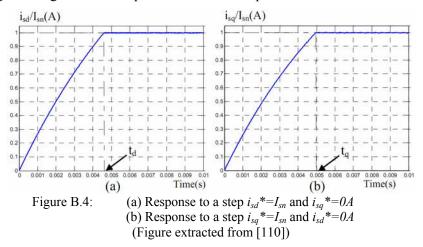

|    | 6.1. Validation of the stator current controller             | 89 |

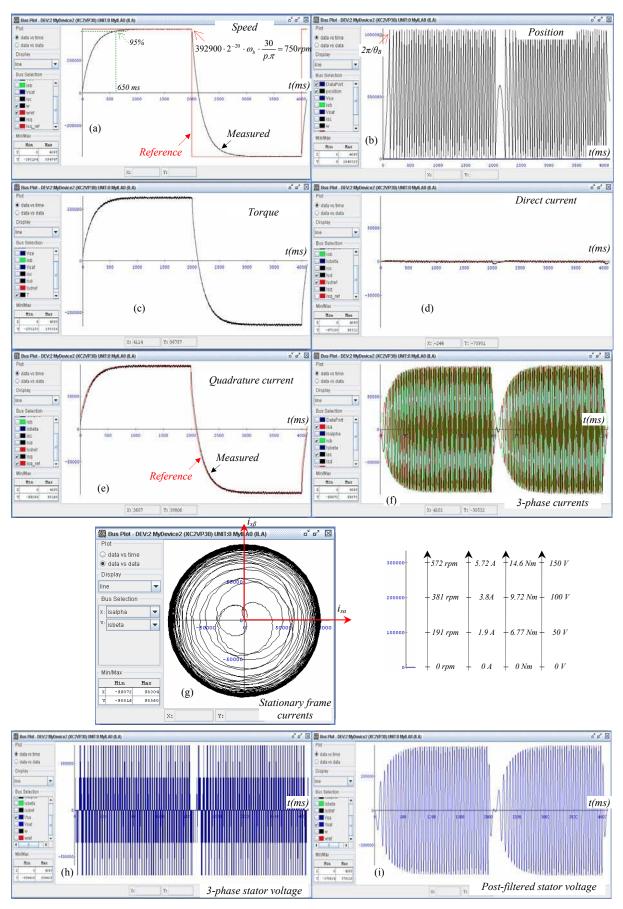

|    | 6.2. Validation of the speed controller                      | 90 |

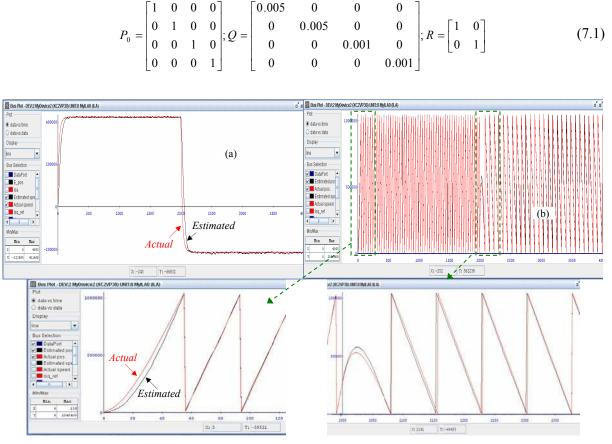

|    | 6.3. Validation of the EKF observer                          |    |

|    | 6.4. Validation of the EKF-based sensorless speed controller | 96 |

| 7. | Conclusion                                                   | 99 |

|    |                                                              |    |

# Chapter 6: FPGA-based sensorless control for synchronous AC drive - FPGA architecture development

| 1. Introduction                                         | 101 |

|---------------------------------------------------------|-----|

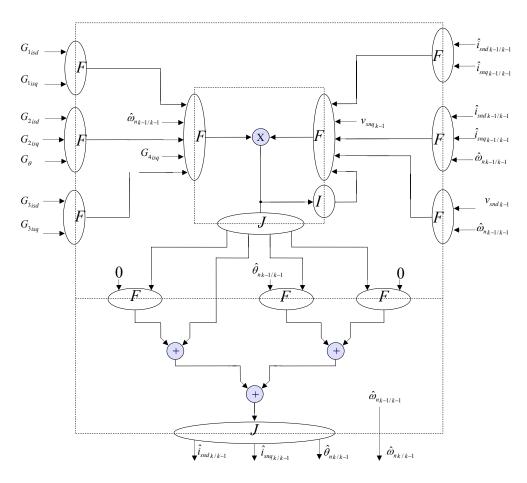

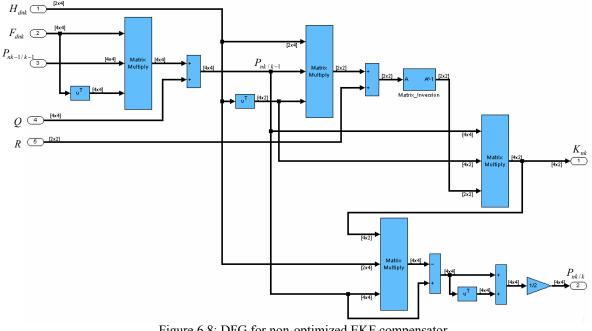

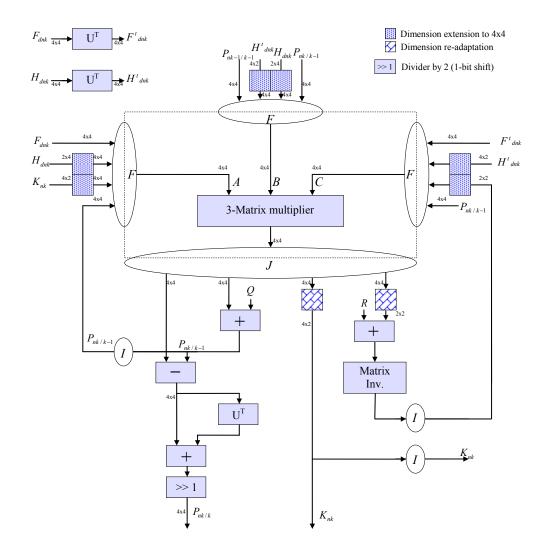

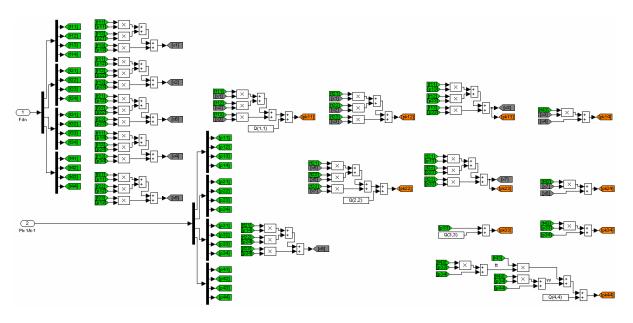

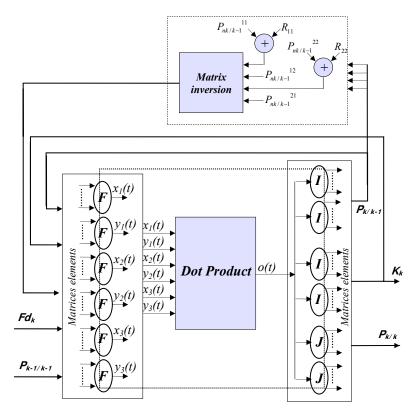

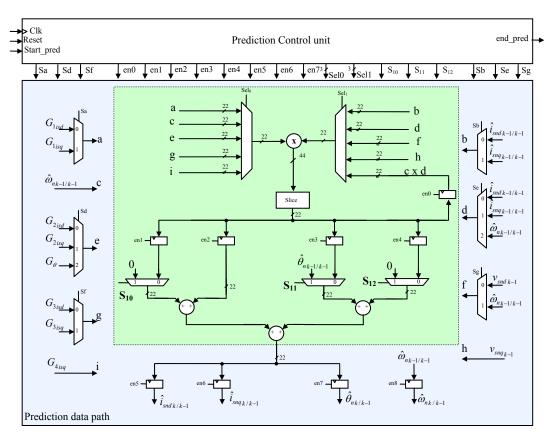

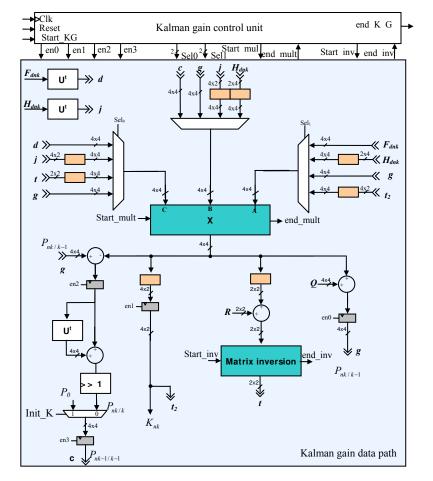

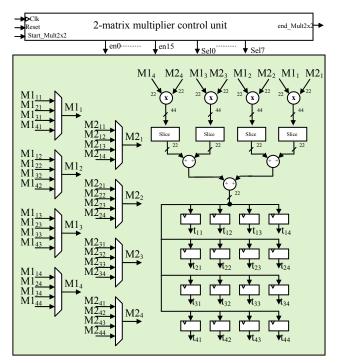

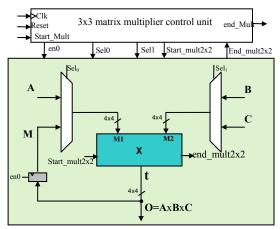

| 2. Architecture optimization                            | 102 |

| 2.1. Optimization strategy                              | 102 |

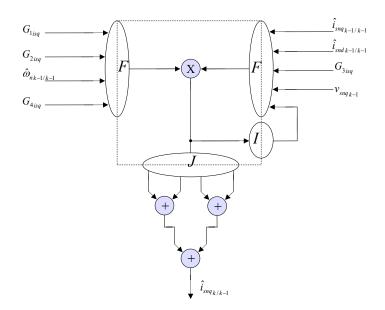

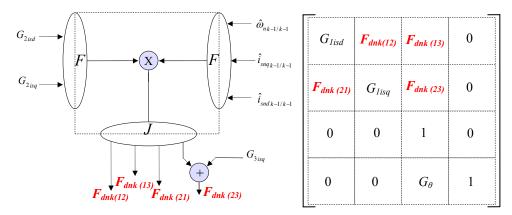

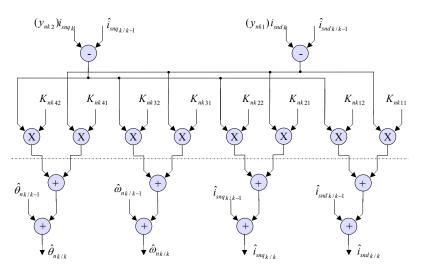

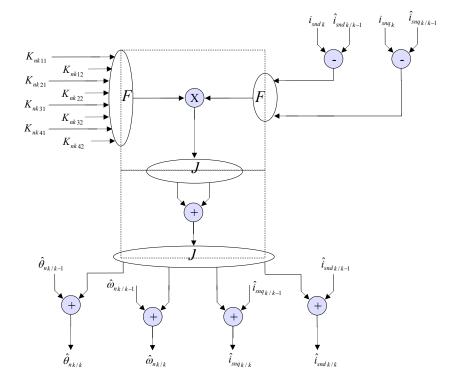

| 2.2. Optimization of the EKF prediction module          | 105 |

| 2.3. Optimization of the EKF compensator                | 107 |

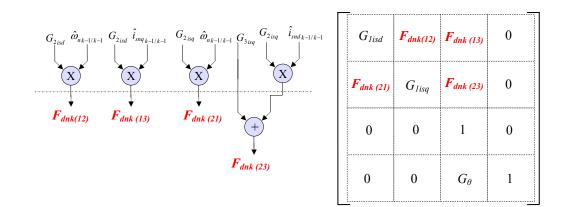

| 2.4. Optimization of the EKF innovation module          | 111 |

| 3. FPGA architecture design                             | 112 |

| 4. Architecture VHDL-coding                             |     |

| 5. Architecture functional simulation                   | 115 |

| 6. Design synthesis and time/area performances analysis | 116 |

| 7. Conclusion                                           | 119 |

# Chapter 7: FPGA-based sensorless control for synchronous AC drive - Experimentation

| Introduction                                             | 121                                                                 |

|----------------------------------------------------------|---------------------------------------------------------------------|

|                                                          |                                                                     |

|                                                          |                                                                     |

| Experimental validation                                  |                                                                     |

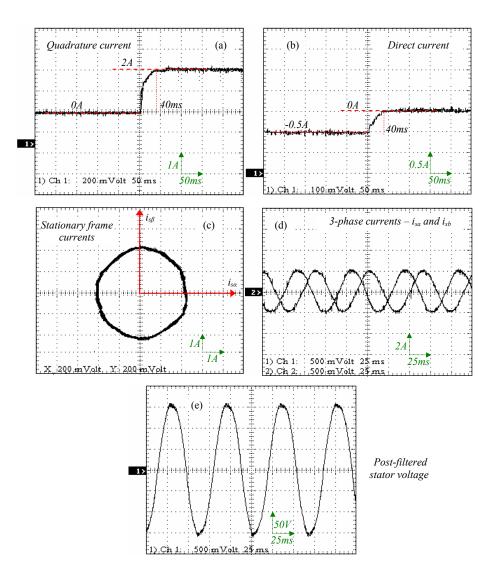

| 4.1. Validation of the stator current controller         | 130                                                                 |

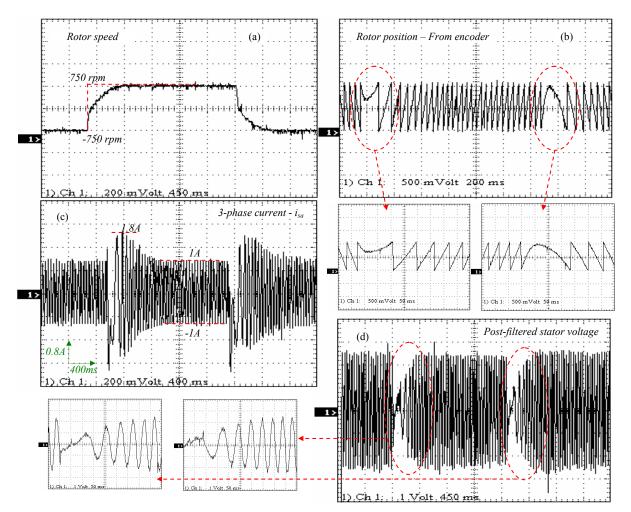

| 4.2. Validation of the sensor-based speed controller     | 131                                                                 |

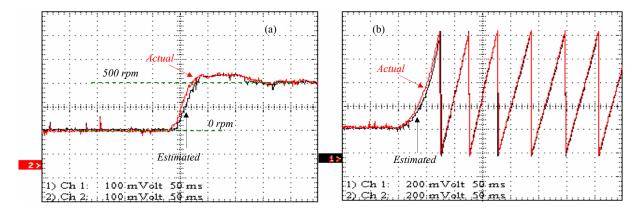

| 4.3. Validation of the EKF observer                      | 132                                                                 |

| 4.4. Validation of the whole sensorless speed controller | 132                                                                 |

| Conclusion                                               | 135                                                                 |

|                                                          | <ul> <li>4.1. Validation of the stator current controller</li></ul> |

### General conclusion and perspectives

| 1. General conclusion                                                                  | . 137 |

|----------------------------------------------------------------------------------------|-------|

| 2. Perspectives                                                                        | . 137 |

| 2.1. Algorithm perspectives                                                            |       |

| 2.2. FPGA development perspectives                                                     |       |

| Appendix A - Compensation of the VSI non-linearities                                   | 139   |

| Appendix B - Salient Synchronous Machine - Modeling and parameter identification       | 145   |

| Appendix C - Tuning of the current and speed regulators                                | .151  |

| Appendix D - EKF for AC drive applications - FPGA-Based solution or DSP-Based solution | 155   |

| Appendix E - FPGA-based matrix multiplication and inversion                            | 159   |

| Bibliography                                                                           | 161   |

# Chapter 1

# **General Introduction**

During these last years, the interest of power electronics and drive applications has been constantly rising. They have encountered a significant progress in terms of power management, by using high efficiency magnetic and power electronic materials, and in terms of control technology by implementing sophisticated control solutions.

When focusing on these control solutions, it is commonly accepted that digital-based controllers are the systematic option. A wide range of them are mostly carried out using software solutions such as microcontrollers and Digital Signal Processors (DSPs). The increasing interest to such solutions is due to their low cost, their design flexibility and their ability to implement complex control algorithms. However, their use remains limited in some industrial applications where high control performances are required. This is typically true for aircraft applications where high control reactivity and large bandwidth are key-issues. The latter are mainly related to the computing time of the used digital controller. The use of software solutions is then limited because of their fixed internal architecture which leads to fully serialize the treatment. The more complex the control algorithm, the longer the execution time. As a consequence, delays are introduced in the control closed loop which affects the control bandwidth.

To achieve high control performances, the use of fast digital solutions is then essential. Many researches and industrial applications have proved that Field Programmable Gate Array (FPGA) solutions are good candidates. Indeed, FPGAs are outperforming today's software solutions by exploiting the inherent algorithm parallelism. Consequently, implementing such hardware solution gives the possibility to develop an architecture that is fully dedicated to the control algorithm. Thus, allying today's FPGA high speed performances with parallelism, leads to a drastic reduction of the execution time. Consequently, in terms of control performances, a quasi-instantaneous control is ensured which enhances the control reactivity and bandwidth.

In addition to these control performances, the system integration is also another criterion that justifies the use of FPGAs. Indeed, their increasing integration density allows the implementation of several independent control algorithms within the same device. When exploiting the control rapidity, it

is also possible to implement a unique algorithm that can control quasi-simultaneously several systems. Along this integration way, recent FPGAs give as well the possibility to implement software treatment since they can integrate processor cores. This makes them true System on Chip (SoC) solutions. Furthermore, a novel SoC approach consists in integrating mixed signal elements such as Analog to Digital Converter (ADC) that has been encountered in niche FPGA devices.

With all these assets, the use of such hardware solutions has successfully allowed the implementation of advanced AC drive control algorithms, [24], [62]. In addition to the standard control strategies, advanced control strategies such as oversampling control, multi-level multi phase control, predictive control and re-configurable control have been proposed.

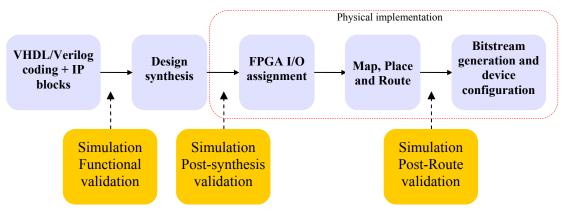

As far as the design process is concerned, FPGA solutions have been the focus of many researches. All these researches share the same objective which is to provide a design methodology that makes the design process more manageable and less intuitive, [33]-[37], [63].

#### 1. Thesis objectives and author contributions

The proposed thesis work is a prolongation of the previously discussed researches and applications. The objective is to evaluate how FPGAs can also be suitable for the implementation of complex AC drive controllers. The case of a sensorless controller for a synchronous AC drive has been chosen. The chosen sensorless method is based on the Extended Kalman Filter (EKF) which estimates the rotor position and speed from the current and voltage quantities. Due to the EKF complexity, such sensorless controller is systematically implemented in DSP solutions. With these solutions, the execution time is frequently evaluated to several tens or hundreds of microseconds.

The aim is then to evaluate how, with only a few microseconds of computing time (less than  $5\mu$ s), an FPGA solution can boost the control performances and how they can increase the system integration. In the following, more details about the thesis objectives and author's contributions are listed,

• Before starting the development of the sensorless controller, a first evaluation of the hardware FPGA solutions in terms of system integration is achieved. A sensor-based controller for a Permanent Magnet Synchronous Machine (PMSM) is developed. This PMSM is associated with a resolver position sensor. This first task belongs to an avionic research program and the objective was to develop a fully integrated FPGA-based controller. To reach this integration aim, the used target is the Actel Fusion FPGA. In addition to the digital features, this device integrates also an ADC. The PMSM controller, the resolver signal treatment and the analog to digital conversion are all ensured by the same device. This development has led to the following publications: [18]-[23].

The next points are related to the development of the FPGA-based sensorless controller using the EKF. This controller is applied to a Salient Synchronous Machine (SSM). Here again, the developed design is intended to be used in an aircraft application which aims to develop a sensorless controller for a Brushless Synchronous Starter Generator (BSSG) [38], [65], [92].

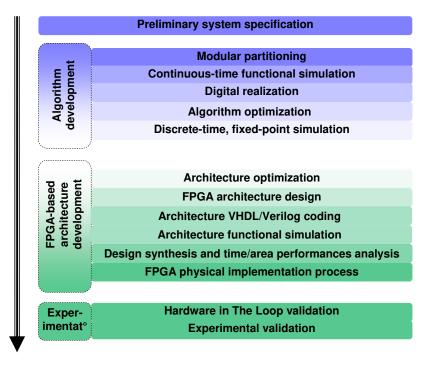

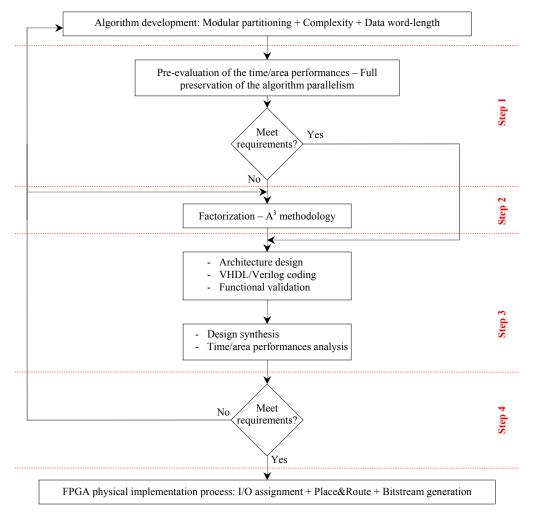

- Adaptation of the design methodology proposed in [63] to complex control applications. The proposed methodology is reorganized and is divided into four main phases: (i) the preliminary system specification, (ii) the development of the algorithm, (iii) the development of the FPGA architecture and (iv) the experimentation. This methodology is applied to the development of the EKF-based sensorless controller, [25].

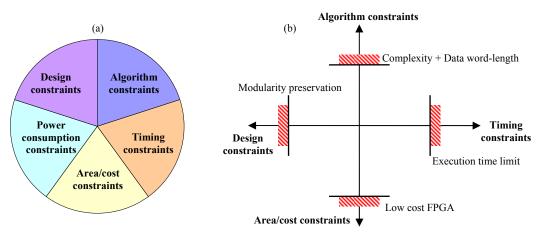

- Insertion of algorithm optimization procedures to the design methodology. The objective here is to optimize the complexity of the algorithm by reducing its computational cost. When applied to the developed sensorless controller, this optimization is to be balanced with the precision and the dynamic behavior, [69].

- Insertion of an FPGA architecture optimization procedure. The latter takes into account implementation constraints. The objective is to develop an FPGA architecture that is able to process the algorithm with the consideration of timing and area constraints, [67].

- Analysis and quantification of the control performances. To this aim, the control bandwidth of the developed FPGA-based sensorless controller has been quantified. The same analysis is done with a DSP-based sensorless controller. Both of these solutions have been developed and compared, [68].

- Analysis and quantification of the system integration. With the obtained time/area performances, author states the possibility to implement a common architecture that can be adapted and used quasi-simultaneously to drive many systems without downgrading their control performances.

- Hardware-In-the-Loop validation of the developed FPGA-based sensorless controller, [24], [66].

- Experimental validation of the developed FPGA-based sensorless controller, [24], [25], [65]-[69].

### 2. Outline

This thesis report is basically divided as follows.

In chapter 2, a state of the art FPGA technology is presented. In this chapter, author starts by presenting the evolution of FPGAs and their value-added to the nowadays industrial electronics. A generic structure of the recent devices is provided and then case studies are achieved. In the latter, the features of recent FPGAs from each technology are given. Their contribution in the field of power electronics and drive applications is presented. To this aim, we have focused on the case of complex AC drive control applications. A quantitative analysis in terms of control performances and system integration is achieved. Finally, the proposed design methodology is presented.

In chapter 3, author deals with the fully integrated FPGA-based controller for the PMSM associated with the Resolver sensor. The used digital control unit is based on the Actel Fusion FPGA. At first, the presentation and the implementation of the integrated Analog to Digital Converter (ADC) is achieved. Then the principle of the Resolver sensor is presented. The extraction of the rotor position and speed is ensured by the FPGA-based Resolver Processing Unit (RPU). This module is associated with a Hysteresis PMSM current controller. The introduced Sampling Synchronization Error (SSE) by the implemented ADC is also discussed and compensation procedures are proposed.

Now, the development of the FPGA-based sensorless speed controller is initiated. Chapters 4 to chapter 7 are organized according to the proposed design methodology.

In chapter 4, the preliminary system specification is discussed. The objective of this step is to make a hardware specification of the system in the one hand, and make an algorithm benchmarking in the other hand. For the first case and depending on the mechanical load conditions, the AC drive and the supply conditions are chosen. The algorithm benchmarking consists in choosing the control strategy, the sensorless method and the system state space model.

In chapter 5, the development of the whole sensorless algorithm is achieved. During this phase, the modular partitioning, the continuous-time simulation, the digital realization, the algorithm optimization and the necessary discrete-time and fixed-point simulations are achieved.

Chapter 6 treats the development of the corresponding FPGA architecture. Taking into account the defined implementation constraints, the optimization of this architecture is made with the help of the Algorithm Architecture Adequation methodology. Then the design of the architecture, its VHDL-coding and the time/area performances analysis are made.

Finally, chapter 7 presents the experimentation step. In order to make a first experimental operating guarantee, the Hardware-In-the-Loop (HIL) validation is performed. Then the ultimate experimental validation using the presented experimental platform is achieved.

# 3. Nomenclature

# 3.1. Symbols

| Cllr                                                                          | · Clash signal                                                                            |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Clk<br>Basat                                                                  | : Clock signal                                                                            |

| Reset                                                                         | : Reset signal                                                                            |

| En<br>Luit deur                                                               | : Enable signal                                                                           |

| Init_done                                                                     | : ADC configuration flag – Fusion FPGA                                                    |

| Start                                                                         | : Start signal                                                                            |

| DATAVALID                                                                     | : ADC result ready – Fusion FPGA                                                          |

| CALIBRATE                                                                     | 6                                                                                         |

| $V_{in}$                                                                      | : ADC analog voltage input – Fusion FPGA                                                  |

| CHNumber                                                                      | : Analog multiplexed selection input – Fusion FPGA                                        |

| xxx_RDY                                                                       | : ADC conversion flag – Fusion FPGA<br>: ADC Conversion time – Fusion FPGA                |

| t <sub>conv</sub>                                                             | : ADC conversion time – Fusion FPGA<br>: ADC sampling synchronization error – Fusion FPGA |

| $\mathcal{E}_{SSE}$                                                           | : Electrical angular position and speed estimated from the Resolver Processing Unit       |

| $egin{array}{lll} 	heta_e, \ \omega_e \ 	heta_r, \ \omega_r \end{array}$      | : Actual position and speed, from Resolver sensor                                         |

|                                                                               | : Position offset                                                                         |

| $	heta_{offset} \ V_{cos}, \ V_{sin}$                                         | : Amplitude modulated Resolver sensor outputs                                             |

| V <sub>cos</sub> , V <sub>sin</sub><br>V <sub>cos</sub> D, V <sub>sin</sub> D | : Demodulated Resolver signals                                                            |

| E                                                                             | : Resolver Excitation signal                                                              |

| $\omega_{ex}$                                                                 | : Resolver Excitation signal                                                              |

| m                                                                             | : Resolver transformation ratio                                                           |

| $\mathcal{E}_{\theta}$                                                        | : RPU angular position error                                                              |

| $H_{	heta}$                                                                   | : RPU position-position transfer function                                                 |

| $H_{\omega}$                                                                  | : RPU speed-position transfer function                                                    |

| $K_1^{\omega}$                                                                | : RPU closed-loop coefficient                                                             |

| $K_2$                                                                         | : RPU closed-loop coefficient                                                             |

| $T_s$                                                                         | : Sampling period                                                                         |

| Bw                                                                            | : Hysteresis bandwidth                                                                    |

| $i_{sa}, i_{sb}, i_{sc}, I_{rd}$                                              | : 3-phase stator currents and the rotor currents                                          |

| E <sub>isa</sub> , E <sub>isb</sub> , E <sub>isc</sub> ,                      | : 3-phase stator current errors                                                           |

| $i_{sd}, i_{sq}$                                                              | : d-q stator currents                                                                     |

| $\mathcal{E}_{id}, \mathcal{E}_{iq}$                                          | : d-q current errors                                                                      |

| $i_{s\alpha}, i_{s\beta}$                                                     | : $\alpha$ - $\beta$ stator currents                                                      |

| θ, ω                                                                          | : Electrical angular position and speed                                                   |

| $V_{DC}, V_{ZSS}$                                                             | : DC link voltage, Zero Sequence voltage                                                  |

| $V_{sa}$ , $V_{sb}$ , $V_{sc}$                                                | : 3-phase stator voltages                                                                 |

| $v_{sd}, v_{sq}$                                                              | : d-q stator voltages                                                                     |

| $V_{s\alpha}, V_{s\beta}$                                                     | : $\alpha$ - $\beta$ stator currents                                                      |

| $S_a, S_b, S_c$                                                               | : VSI switching signals                                                                   |

| $V_a, V_b, V_c$                                                               | : 3-phase power supply voltages                                                           |

| $V_{ao}, V_{bo}, V_{co}$                                                      | : 3-phase voltages – VSI voltages                                                         |

| $T_e, T_L$                                                                    | : Electromagnetic torque, Load torque                                                     |

| $R_s, R_r$                                                                    | : Stator, rotor Resistances                                                               |

| $L_{sd}, L_{sq}$                                                              | : d-q stator inductances<br>: Stator-rotor mutual inductance                              |

| $M_{sr}$                                                                      |                                                                                           |

| $f_L, J$                                                                      | : Viscous friction coefficient, Rotor inertia<br>: Pole pairs number                      |

| $p \\ N$                                                                      | : Mechanical speed                                                                        |

| $\Omega$                                                                      | : Angular mechanical speed                                                                |

| $\theta_m$                                                                    | : Mechanical rotor position                                                               |

| $V_{bmf}$                                                                     | : Back-EMF voltage                                                                        |

| $\Psi$                                                                        | : Flux                                                                                    |

| -                                                                             |                                                                                           |

| х, и, у             | : State space vector, System input and output vectors                  |

|---------------------|------------------------------------------------------------------------|

| <i>w, v</i>         | : System disturbances                                                  |

| <i>f</i> , <i>h</i> | : continuous-time state space matrix, System output matrix             |

| $f_d, h_d$          | : Discrete-time State space matrix, Discrete-time System output matrix |

| $F_d, H_d$          | : Jacobian matrices for linearization                                  |

| Κ                   | : Kalman gain matrix                                                   |

| $P, P_0$            | : State error covariance matrix, Initial covariance matrix             |

| <i>Q</i> , <i>R</i> | : Model noise and measurement noise covariance matrices                |

| $K_p$               | : PI-regulator proportional gain                                       |

| $K_i$               | : PI-regulator integral gain                                           |

| $V_{nom}$           | : Nominal voltage                                                      |

| Inom                | : Nominal current                                                      |

| $N_{nom}$           | : Nominal speed (rpm)                                                  |

| $V_{Bcc}$           | : Voltage base value for current controller                            |

| $V_{Bekf}$          | : Voltage base value for the EKF                                       |

| $I_B$               | : Current base value                                                   |

| $\omega_B$          | : Angular speed base value                                             |

| $	heta_B$           | : Angular position base value                                          |

| $G_{vsensor}$       | : Gain introduced by the voltage sensor                                |

| Gisensor            | : Gain introduced by the current sensor                                |

| $G_{ADC}$           | : Gain introduced by the ADC                                           |

|                     |                                                                        |

# 3.2. Indexes

| s, r                | : Stator and rotor index                                     |

|---------------------|--------------------------------------------------------------|

| d, q                | : Rotating reference frame indexes                           |

| α, β                | : Stationary reference frame indexes                         |

| *, ^                | : Reference quantity, Estimated quantity                     |

| k                   | : Sampling index                                             |

| <i>B</i> , <i>n</i> | : Base quantity for normalization, Normalization index       |

| a, b, c             | : 3-phase reference frame index                              |

| k/k-1, k/k          | : Predicted quantity, Estimated optimal quantity             |

| k-1/k-1             | : Estimated optimal quantity at the previous sampling period |

### 3.3. Abbreviations

| $A^3$      | : | Algorithm Architecture Adequation           |

|------------|---|---------------------------------------------|

| ADC        | : | Analog to Digital Converter                 |

| ASIC       | : | Application Specific Integrated Circuit     |

| ATO        | : | Angle Tracking Observer                     |

| CAD        | : | Computer Aided Design                       |

| CAM        | : | Computer Aided Manufacture                  |

| CAN        | : | Control Area Network                        |

| CAT        | : | Computer Aided Test                         |

| CB_PWM     | : | Carrier Based PWM                           |

| CB_SPWM    | : | Carrier Based Sinusoidal PWM                |

| CB_ZSS_PWM | : | Carrier Based PWM with Zero Sequence Signal |

| CCC        | : | Clock Conditioning Circuit                  |

| CLB        | : | Configurable Logic Block                    |

| CMT        | : | Clock Management Tile                       |

| CORDIC     | : | COordinate Rotation Digital Computer        |

| CPLD       | : | Complex Programmable Logic Device           |

| DAC        | : | Digital to Analog Converter                 |

| DCM        | : | Digital Clock Manager                       |

| DFG        | : | Data Flow Graph                             |

| DSP        | : | Digital Signal Processor                    |

| EDA        | : | Electronic Design Automation                |

| EDK        | : | Embedded Development Kit                    |

|            |   | -                                           |

| EDG          |                                                          |

|--------------|----------------------------------------------------------|

| EDS :        | Embedded Design Suite                                    |

| EEPROM :     | Electrically Erasable Programmable Read Only Memory      |

| EKF :        | Extended Kalman Filter                                   |

| EMF :        | Electromotive Force                                      |

| EPROM :      | Erasable Programmable Read Only Memory                   |

| FDFG :       | Factorized DFG                                           |

| FIFO :       | First In First Out                                       |

| FPGA :       | Field Programmable Gate Array                            |

| HIL :        | Hardware In the Loop                                     |

| I/O :        | Input / Output                                           |

| I2C :        | Inter Integrated Circuit                                 |

| IC :         | Integrated Circuit                                       |

| ICON :       | Integrated CONtroller                                    |

| IGBT :       | Insulated Gate Bipolar Transistors                       |

| ILA :        | Integrated Logic Analyzer                                |

| IOE :        | I/O Element                                              |

| IP :         | Intellectual Property                                    |

| LAB :        | Logic Array Block                                        |

| LB :         | Logic Block                                              |

| LC :         | Logic Cell                                               |

| LE :         | Logic Element                                            |

| LL :<br>LM : | Logic Module                                             |

| LUT :        | Look Up table                                            |

| MMCM :       | Mixed Mode Clock Manager                                 |

|              |                                                          |

| OTP :        | One Time Programmable                                    |

| P_PI :       | Proportional – Proportional – Integral                   |

| PCI :        | Peripheral Component Interconnect                        |

| PI :         | Proportional – Integral                                  |

| PLL :        | Phase Locked Loop                                        |

| PMSM :       | Permanent Magnet Synchronous Machine                     |

| PWM :        | Pulse Width Modulation                                   |

| RAM :        | Random Access Memory                                     |

| RDC :        | Resolver to Digital Converter                            |

| ROM :        | Read Only Memory                                         |

| RPU :        | Resolver Processing Unit                                 |

| SAR :        | Successive Approximation Register                        |

| SEU :        | Single Event Upset                                       |

| SIA :        | Satellite Industry Association                           |

| SMO :        | Sliding Mode Observer                                    |

| SoC :        | System on Chip                                           |

| SPI :        | Serial Peripheral Interface                              |

| SR :         | Shift Register                                           |

| SRAM :       | Static Random Access Memory                              |

| SSE :        | Sampling Synchronization Error                           |

| SSM :        | Salient Synchronous Machine                              |

| SVPWM :      | Space Vector PWM                                         |

| THD :        | Total Harmonic Distortion                                |

| USB :        | Universal Serial Bus                                     |

| VCO :        | Voltage Controlled Oscillator                            |

| VHDL :       | Very high speed integrated Hardware Description Language |

| VIO :        | Virtual Input/Output                                     |

| VSI :        | Voltage Source Inverter                                  |

| VT :         | VersaTile                                                |

| , I .        | , 0150 1 HO                                              |

# Chapter 2

# State of the art FPGA technology

#### **1. Introduction**

A few decades ago, digital electronic designs were mainly based on basic Integrated Circuits (ICs). Each of them was fully specified by the manufacturer and has a specific function. The end-user had to make a collection of the necessary ICs to develop a digital circuit that performs the desired function. Generally, digital systems were easier to develop, smaller in terms of complexity, heavier in terms of board size and ran at low speed performances. No Design tools existed which made the design processes more intuitive.

The increasing success of these digital systems and their value-added to the early everyday's life made customers starting to ask for more sophisticated device solutions. Device solutions that are manufactured and specified to the developed application and that are smaller, faster, more complex, low cost and low power consuming. All these challenges made designers to compete and propose many solutions that led to the expansion of today's electronic industry.

Driven by these demands, new materials, new fabrication processes, new design tools and device technologies have been proposed and new markets for digital circuits have evolved. Indeed, with the increasing resort to informatics and their associated computing resources, a set of efficient software tools are proposed [8]. Therefore, Electronic Design Automation (EDA) and Computer Aided Design (CAD) tools are provided for the design process. For the fabrication process, Computer Aided Manufacture (CAM) and Computer Aided Test (CAT) tools are proposed.

When it comes to device technologies, many solutions are nowadays available and an additional benchmarking effort has to be made by the end-user so as to choose the best one that suits the desired performances and also the expected level of flexibility, re-programmability, cost and power consumption. This leads to many start-up questions that are asked during system specification: do we have to use a set of standard ICs, a rapid-prototyping reprogrammable solution (Semi-Custom Application Specific Integrated Circuit-ASIC) or a fully custom solution (Full custom ASIC)? Do we have to use fully software devices (Digital Signal Processor-DSP, µProcessor, µController ...), fully

hardware devices (Complex Programmable Logic Device-CPLD, Field Programmable Gate Array-FPGA ...) or mixed software/hardware devices (FPGA System on Chip-SoC)?

Among this diversity of digital solutions and since their first introduction to the market in 1985 by the Xilinx Company, FPGA hardware technologies have attracted an always increasing interest. Indeed, FPGAs belong to the semi-custom ASIC family. The latter low cost devices consist of predesigned (by the manufacturer) elementary cells and interconnections that can be programmed and interconnected by the user in order to realize a specific function for a specific application. In addition to their low manufacturing cost, these devices distinguish themselves by a high integration density, a notable computation rapidity, a high level of flexibility and a rapid prototyping.

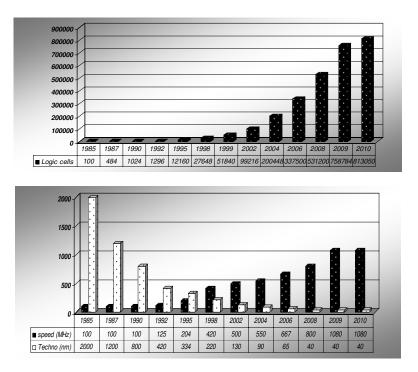

Nowadays, the always increasing integration density, speed and the low power consumption make FPGA solutions suitable for complex applications in different domains such as, digital signal processing, power electronics and drive applications, communication, aerospace, defense, etc. This is also made possible with the considerable progress in terms of process technology which has reached down to 40nm (28nm has been recently announced by Xilinx and Altera vendors) [2], [3]. To give a visual evolution of FPGA capacities, Figure 2.1 overviews the evolution of FPGAs in terms of density (logic cells), speed, and process technology. It is worth noticing that these waveforms have been obtained by comparing the available commercial FPGAs. Also the measurement of speed is based on the maximum available clock frequency that can be reached within the FPGA.

Figure 2.1: Evolution of FPGA performances

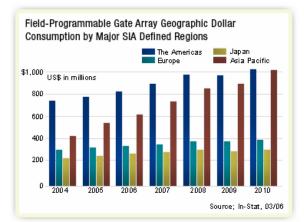

From a more financial point of view, many market analyses have been achieved and the conclusions in each case gave promising financial value-added of FPGAs. For example, according to an *In-Stat market analyst* documentation article (published in 2006) where an estimation of the FPGA market evolution was made [1], the value of worldwide FPGA market would increase from \$1.9 billion in 2005 to \$2.75 billion by 2010. Another precise example of FPGA market is given in Figure 2.2 where the evolution of Dollar consumption by Major (Satellite Industry Association) SIA defined regions is stressed.

Figure 2.2: FPGA market evolution in SIA regions (source: In-Stat market analyst)

The goal and the challenge of this chapter are to introduce a large part of FPGA facets. Thus, the next part introduces the generic structure of an FPGA where the most important and relevant FPGA elements are presented. The case studies provided in part 3 aim to make a quantitative description of FPGAs by focusing on precise FPGA devices from each technology. Part 4 is devoted to the contribution and the application of FPGAs in the field of power electronics and drive applications especially in the case of complex control algorithms. Advantages of using FPGAs in this field and also implementation constraints to manage are both focused on. Finally, an FPGA design methodology dedicated to power electronics and drive applications is discussed.

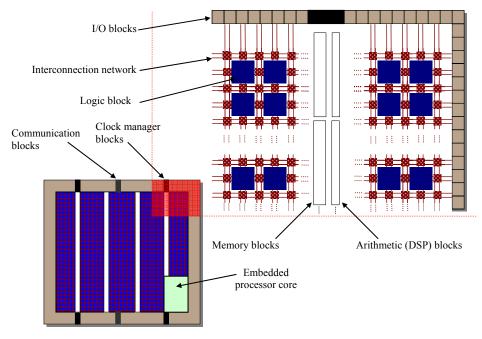

### 2. Generic structure of an FPGA

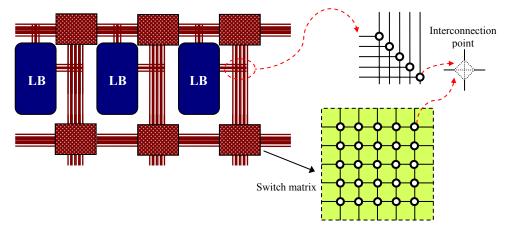

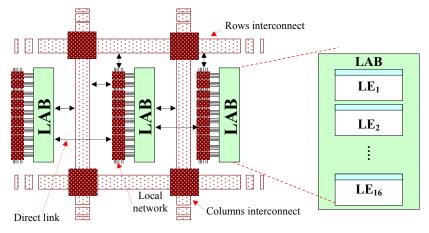

As presented in Figure 2.3, the basic structure of an FPGA consists of a matrix of logic blocks, an interconnection network and configurable I/O blocks [2]-[17]. To ensure high level of integration, today's FPGA devices also include coarse-grain hardwired elements such as memory blocks, arithmetic (DSP) blocks, clock manager blocks and communication blocks. Furthermore, FPGA solutions give the possibility to implement embedded processor cores which makes them true System on Chip (SoC) solutions [26]-[29]. Also, a novel SoC approach consists in integrating mixed signal elements such as Analog to Digital Converters (ADCs) that has been encountered in the Actel Fusion FPGA [10].

Figure 2.3: Generic structure of an FPGA (Island topology)

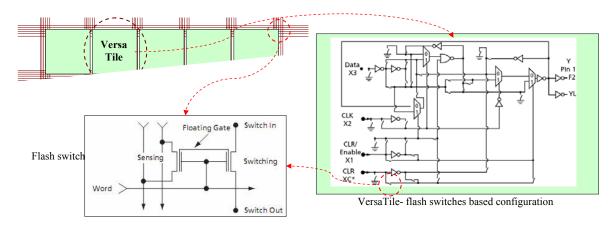

#### 2.1. Logic Blocks

First of all, it is worth noticing that the naming of Logic Blocks (LBs) has been intentionally chosen so as to keep the generic structure as independent on FPGA families as possible. In fact, to anticipate the discussion made in the case studies (part 3); different appellations are adopted by FPGA vendors with different levels of granularity. For instance, Slice and Configurable Logic Block (CLB) appellations are used by Xilinx vendor, [2]. Logic Element (LE) and Logic Array Block (LAB) are used by Altera Vendor, [3] and VersaTile is used by Actel, [4].

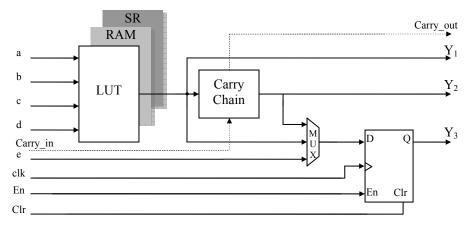

Depending on the expected function to implement, each LB is configured to perform combinatorial and/or sequential operations. An LB is generally composed of a set of Look-Up-Tables (LUTs) dedicated to combinatorial operations and a set of D-Flip-Flops for sequential operations. In addition to this basic operating mode, an LB is also able to perform a local storage function (distributed RAM memory), shift register (SR), multiplexer, and adder/subtractor operations.

Although the internal structure of LBs differs from an FPGA family to another, a normalized FPGA density metric has been accepted. Indeed, a common Logic Cell (LC) has been defined which is composed of a 4-bit LUT, a D-Flip-Flop, a carry chain (for arithmetic operations) and a multiplexer. Roughly speaking, Altera FPGAs include LEs, each of them is equivalent to one LC [3]. A Xilinx Spartan-6 FPGA CLB is equivalent to 12.8 LCs [12] and a Virtex FPGA CLB is equivalent to 4.5 LCs [13]. Figure 2.4 highlights the internal structure of an elementary LC.

Figure 2.4: Internal structure of an elementary LC

#### **2.2. Interconnection network**

The programmable interconnection network is the backbone of the FPGA logic resources. Where the FPGA fabric performs arithmetic and logical computations, the programmable interconnection network makes the necessary connections between the necessary elements so as to develop the architecture that performs the expected user function.

In many today's FPGAs, three typical interconnection techniques can be encountered: the nearest-neighbor technique, the segmented technique and the hierarchical technique [6]. By considering the distance between the FPGA elements to be interconnected and the complexity of the developed architecture, a combination of these techniques is made so as to optimize signal propagation delays.

#### 2.2.1. Nearest-neighbor technique

This technique consists in directly routing each logic block with each of its immediate neighbors using local interconnection [6]. Although, this technique has the credit to be simple, it has a lack severe propagation delay and connectivity issues. This is especially true when the distance and the complexity increase. This is the reason why this technique is combined with segmented and hierarchical techniques.

#### 2.2.2. Segmented technique

The routing is, in this case, made using specific switch matrices. As described in Figure 2.5, the interconnection between logic blocks is segmented and the switch matrices ensure the connectivity between these segments, allowing long distance routing to be accomplished and then ensuring optimized propagation delays [6]. As an example, this topology is realized in Xilinx and Altera FPGAs.

Figure 2.5: Segmented interconnection technique

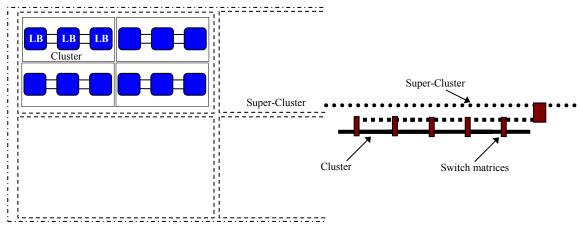

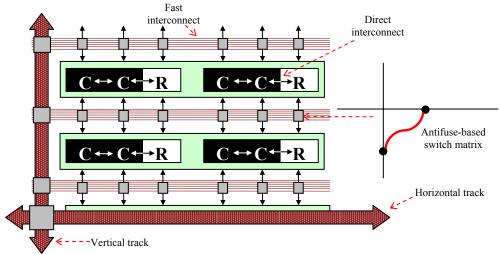

#### 2.2.3. Hierarchical technique

This is a slightly different approach to reducing propagation delays of long wires. In fact, as depicted in Figure 2.6, at the lower level of hierarchy, local neighbor logic blocks are grouped together as a single cluster. Within each cluster, local nearest-neighbor routing is made. Then, at the immediate higher level of hierarchy, adjacent clusters are grouped and form another cluster in the higher level of grouping [6]. This is repeated at higher levels of hierarchy, with larger clusters (super-clusters) and longer wires. As in the segmented technique, the connection points that connect one level of routing hierarchy to another are ensured by switch matrices. This interconnection technique is typically used by Actel Antifuse FPGAs where 3 levels of hierarchy are available, [4].

Figure 2.6: Hierarchical interconnection technique

#### 2.3. Clock manager blocks

The integrated clock manager blocks allow the management of the clocking resources within the FPGA. They are commonly based on high frequency Phase-Locked-Loops (PLLs) that support several features for general purpose clock management such as frequency multiplication/division, phase shifting, propagation delay compensation and duty cycle correction. For instance, Xilinx Virtex-6 FPGA includes up to 18 clock manager blocks (called Mixed Mode Clock Manager MMCM, [14]) and Altera Stratix-4 FPGA provides up to 12 PLLs, [16].

As far as clock distribution is concerned, a dedicated global clock network is available so as to wire clock signals to the FPGA elements. In addition, specific FPGA pins and buffers are provided so as to ensure a high speed clock signal transmission.

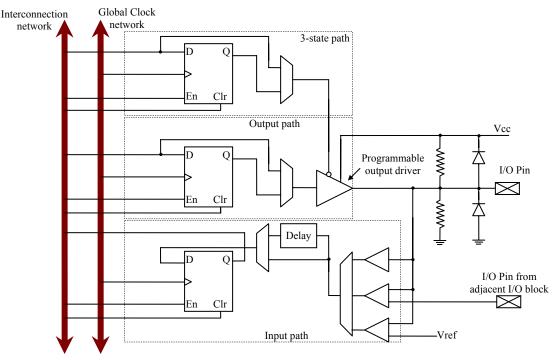

#### 2.4. I/O blocks

The Input/Output blocks provide a programmable bidirectional interface between the internal FPGA fabric and the external environment. They are usually organized as banks and can reach up to 1200 I/O blocks (Xilinx Virtex-6 FPGA). Each bank can be dedicated to different I/O standards including single-ended I/Os, differential I/Os, voltage referenced I/Os and high speed interfaces (PCI and memory interfaces). A simplified diagram of an I/O block internal structure is presented in Figure 2.7. There are three main signal paths, the output path, the input path and the 3-state path. For synchronization purpose, each path contains a set of storage elements that act as registers or latches.

Figure 2.7: General structure of an I/O block

#### 2.4.1. Input path

This path carries data from the external FPGA pin to the internal logic. A programmable delay and storage elements are introduced in order to control the synchronization of data with the clock signal. The input path can be configured to ensure standard input, differential input with another input path from an adjacent I/O block or voltage referenced input.

#### 2.4.2. Output path

This path carries data from the internal logic to the external FPGA pin. Storage elements can also be used to synchronize the data transfer with the clock signal.

#### 2.4.3. Three-state path

This path sets the FPGA pin in a high impedance state. A programmable output driver is used to select either the output path (output mode) or the 3-state path (high impedance mode).

#### 2.5. Arithmetic (DSP) blocks

In order to suit the high demand of resources for complex applications, recent FPGAs give the possibility to implement arithmetic operations using hardwired arithmetic blocks. In most of the cases, the latter consist of a large amount of hardwired multipliers, e.g. up to 2000 multipliers (25x18 bits) are included in Virtex-6 SX Xilinx FPGA series. In addition, these arithmetic blocks are pipelined using a set of registers in order to enhance speed performances.

Furthermore, in the advanced recent FPGAs, more complex arithmetic blocks are provided: DSP blocks. Indeed, these pipelined blocks consist of a combination of a multiplier, an adder/subtractor and an accumulator. Implementing such blocks allows more complex arithmetic operations in high computational and high frequency demanding applications such as filtering, image processing, video treatment, signal transmission ... Examples of FPGAs that provide DSP blocks are: Xilinx Virtex-6, Xilinx Spartan-6 and Altera Stratix-4.

#### 2.6. Memory blocks

In addition to logic blocks and hardwired arithmetic blocks, FPGA devices support a large amount of embedded memory blocks to increase hardware resource availability and speed performance. Indeed, in large systems that often require data storage, implementing on-chip memories has a value-added especially by increasing the system integration density and allowing faster read/write operations.

In nowadays FPGAs, most of these on-chip data storage blocks consist of configurable blocks which allow the implementation of various memory structures including RAMs, ROMs, FIFOs and shift registers. As an example, the Xilinx Virtex 6 FPGA provides up to 1064 RAM blocks that correspond to up to 38 Mb RAM capacity and the Altera Stratix-4 FPGA provides up to 33 Mb embedded RAM memories.

In addition to these dedicated blocks, distributed RAM memories are also available. This is especially true when talking about SRAM-based FPGAs where the integrated logic blocks can run as distributed RAM and/or shift registers.

For the same purpose and in order to provide a nonvolatile memory feature, niche FPGA families such as Flash-based FPGAs support also Flash memory blocks. For example, Actel Fusion FPGA supports up to 8 Mb flash memory resources, 1 Kb FlashROMs and up to 270 Kb RAMs, [10].

#### 2.7. Communication blocks

The current FPGA devices include also communication blocks that consist generally of transmission and reception buffers. Various communication protocols (standard or user-defined) are supported, including among others USB, Ethernet, CAN, PCI, SPI and I2C protocols. For this aim, dedicated transceivers are provided so as to support many of these protocols and ensure high data transmission rates, e.g. up to 11 Gbps with Stratix-4 and Virtex-6 FPGA.

#### 2.8. Embedded processor cores

Besides the evolution of the discussed FPGA elements and in order to meet more flexibility and higher integration capability, the recent FPGA devices give the possibility to implement an increasing diversity of processor cores. They are then considered as System-On-Chips (SoCs) or System-on-Programmable-Chips (SoPCs) solutions [26]-[29].

In such SoPC approach, two categories of processor cores can be encountered, the "non-synthesizable" cores and the "synthesizable" cores.

The non-synthesizable (also called hard processor) cores are hardwired within the FPGA, in addition to the previously discussed FPGA elements. As a general rule, a hard processor core offers higher clock speeds with less flexibility. For example, Altera provides an ARM9 processor core embedded in its EPXA10 series that is marketed as an Excalibur<sup>™</sup> device [3]. The Xilinx Virtex-5

integrates also a hardwired PowerPC 440 processor cores on-chip [2]. Recently, Actel has provided the first hardwired Cortex-M3 processor core integrated into its Fusion FPGA family [10].

The synthesizable (Soft cores), such as Altera Nios II, Xilinx MicroBlaze processors and Actel ARM7 or Cortex-M1, use existing FPGA configurable elements to implement the processor core, [2]-[4]. The particularity of such approach is the flexibility that allows the designer to configure and specify the number, the types of peripherals, the memory width... However, these cores have slower clock rates.

#### 2.9. Configuration technology

The internal structure, the operating mode and the configuration of the discussed FPGA elements differ depending on the device family and technology. There are various configuration methods and technologies including, SRAM, EPROM, EEPROM, Fuse, Antifuse and Flash technologies. Because of their popularity, only the SRAM, the Antifuse and the Flash technologies have been here investigated.

#### 2.9.1. SRAM technology

The most widely used method for storing configuration data in available FPGAs is volatile static RAM, or SRAM. The configuration is entirely made using a set of dedicated SRAM blocks. These blocks are organized as a specific configuration layer. The most popular SRAM-based FPGA families are Xilinx and Altera families. The popularity of this technology is manly due to their fast and infinite reconfiguration cycles [6]. Drawbacks of such technology are power consumption and data volatility. Indeed, compared to the other technologies, an SRAM-based connection point is based on high number of transistors (6 transistors) and dissipates significant static power because of leakage current. Another significant drawback is that SRAM does not maintain its contents after power is off, which means that at power-up the FPGA is not configured and must be programmed using off-chip logic and storage, [6].

#### 2.9.2. Antifuse technology

The Antifuse technology is based on the so-called Antifuse connections that are based on metal link. The latter behaves in the opposite of a Fuse. In other words, an Antifuse link is normally unconnected and a specific programming procedure is required to make the connection (i.e short circuit between Antifuse endpoints). This procedure consists in injecting a high current or a Laser that heats and then melts the silicon layer between endpoints so as to make the connection [6]. The main drawback of such technology is that FPGAs in this case are One-Time-Programmable (OTP) which limits significantly their flexibility and make them useless for prototyping environments.

#### 2.9.3. Flash technology

This technology is definitely an interesting gap between SRAM technology and Antifuse technology since the configuration is based on flash connections that keep the configuration state when the power is off. Furthermore, a flash-based connection point uses less number of transistors than its SRAM counterpart (2 transistors sharing a floating gate) [4]. Consequently, this yields to lower current leakage and then to lower static power consumption. Also this technology is useful in aircraft and space systems since it guaranties the configuration against the Single Event Upset (SEU) radiations. In contrast, the main drawbacks of such technology are slow configuration rate and a limited number of reconfiguration cycles.

### 3. Case studies

In order to move from an abstract presentation of FPGAs and see how exactly they look like, single examples have been chosen from the available and most recent FPGAs. The selection is based on configuration technology criterion. Then, a deeper investigation of each example for each configuration technology is made.

#### 3.1. SRAM based technology

The most popular SRAM-based FPGA families are Xilinx and Altera families. Among the commercialized FPGA devices, one can stress the high performance VIRTEX (Xilinx) and STRATIX (Altera) FPGAs and the low cost SPARTAN (Xilinx) and CYCLONE (Altera) FPGAs. As it will be discussed afterwards, in the field of power electronics and drive applications, cost is a key-issue. As a consequence, it has been chosen to present only the low cost FPGA families. As examples of illustration, the latest Xilinx SPARTAN-6 and Altera Cyclone-4 FPGA families will be investigated.

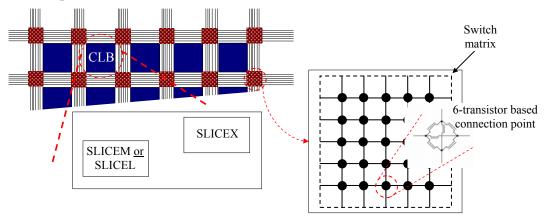

#### 3.1.1. Xilinx Spartan-6 FPGA

A Spartan-6 SRAM-based FPGA incorporates a combination of the previously discussed FPGA elements and is based on 45-nm process technology. There are up to 11519 CLBs (equivalent to 147443 LCs) and, as seen in Figure 2.8, each single CLB contains a pair of slices: SliceX and SliceL/SliceM (globally, a Spartan-6 contains 50% of SliceX, 25% of SliceM and 25% of SliceL). Each slice can be configured to perform combinatorial functions using four 6-bit LUTs and sequential functions using eight D-Flip-Flops. Furthermore, the SliceM can operate as a distributed RAM block, as a shift register, as a multiplexer or as a carry chain that performs arithmetic additions and subtractions. A SliceL supports all the SliceM features except the memory and shift register functions. To have a deeper idea about the structure of each slice, refer to [12]

Figure 2.8: SRAM-based SPARTAN-6 FPGA fabric

The interconnection network is composed of wires and a sea of switch matrices (with 6transistor based connection points). The interconnection of FPGA elements in this case is based on segmented technique and the routing resources are physically located in horizontal and vertical routing channels. Various types of routing are ensured depending on the distance between elements to interconnect (Fast interconnect, Single interconnect, Double interconnect and Quad interconnect).

As for the hardwired arithmetic blocks, Spartan-6 FPGA includes up to 180 DSP blocks named DSP48A1 slices. Each one supports many independent functions, including 18-bit multiplier, 48-bit accumulator, 18-bit adder/subtractor, a wide bus multiplexer, magnitude comparator and a wide counter.

The number of I/O blocks varies from 102 to 576 depending on the series and device size. All of them operate as bidirectional interfaces. They are organized as banks and can support a large number of single-ended, differential and voltage referenced standards.

Spartan-6 FPGAs contain a set of clocking resources and Clock Management Tiles (CMTs). The provided clocking resources consist of dedicated clock inputs, buffers and routings. There are 8 dedicated clock inputs, 32 global clock inputs that can operate as general purpose I/Os and 16 clock buffers. There are up to 6 CMTs, each single one contains 2 Digital Clock Managers (DCMs) and one PLL. The role of a DCM is primarily to eliminate clock skew and distribution delays. It can also ensure phase shifting and clock multiplication and division. A PLL is based on voltage controlled oscillator (VCO) that operates from 400 MHz to 1080 MHz.

As far as memory blocks are concerned, every Spartan-6 FPGA supports between 12 and 268 dual port RAM blocks in addition to the distributed RAM within CLBs. This corresponds to a total of 6179 Kb memory capacity.

#### 3.1.2. Altera Cyclone-4 FPGA

A Cyclone-4 FPGA is based on 60nm process technology and integrates up to 150000 LEs [15]. As seen in Figure 2.9, these latter are gathered in 16-group blocks called Logic Array Blocks (LABs). Each LE consists of a 4-bit LUT that can perform either combinatorial or arithmetic operations and a D-Flip-Flop for sequential operations. Also, an LE can operate in arithmetic mode and perform a 2-bit full adder and also a basic carry chain.

The interconnection network is organized in 2 levels (Figure 2.9); *local interconnect* and *global interconnect* [15]. The first one is used to transfer signals between LEs in the same LAB. The global interconnect is organized in column and row lines that drive signals between LABs and also between the other FPGA elements. Direct link interconnect is also provided to connect adjacent elements so as to minimize the use of columns and rows, providing higher flexibility and higher speed performances.

Figure 2.9: SRAM-based CYCLONE-4 FPGA fabric

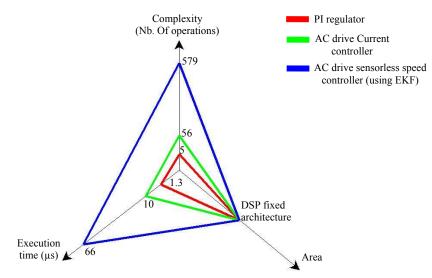

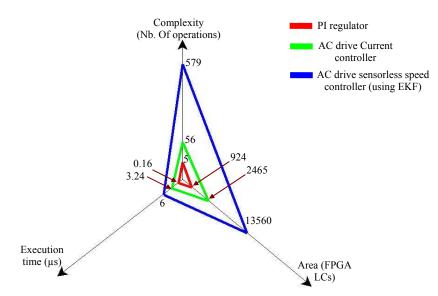

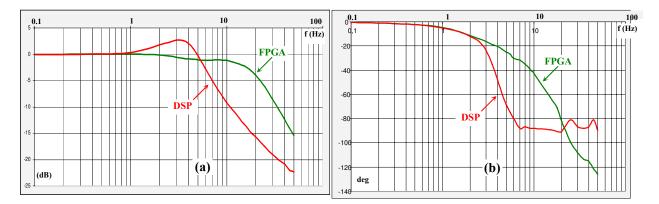

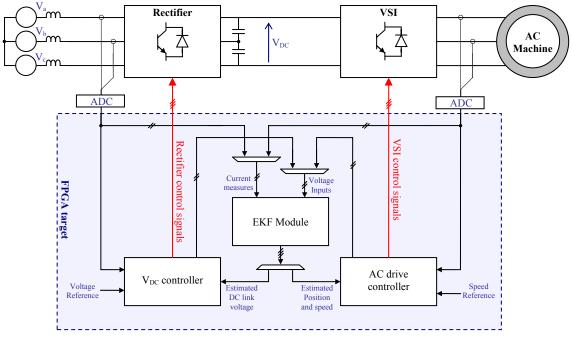

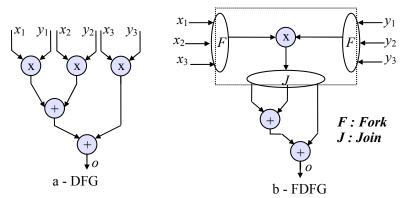

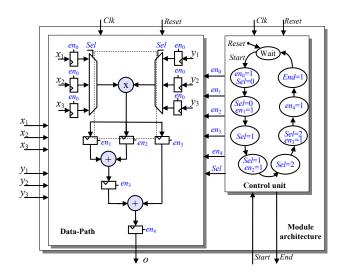

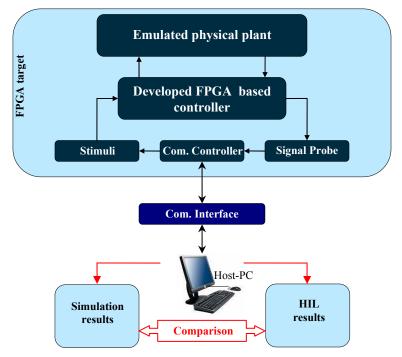

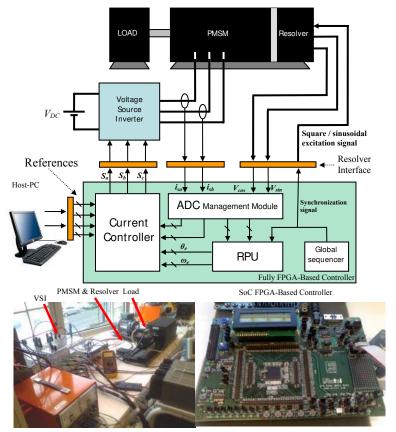

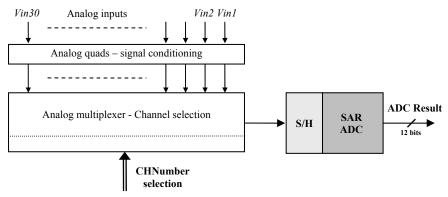

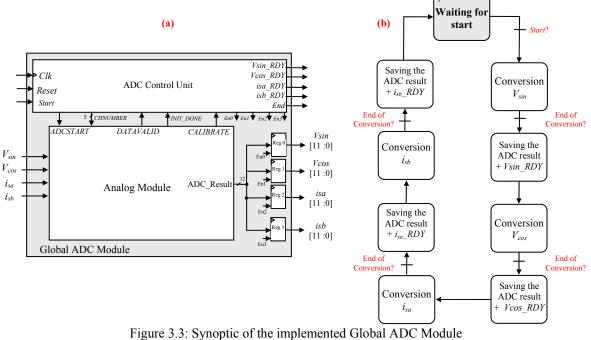

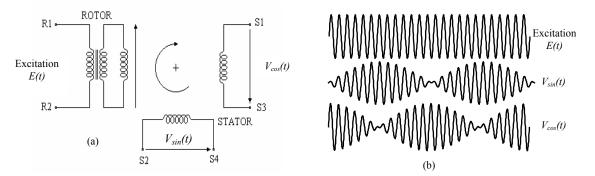

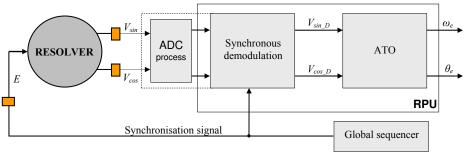

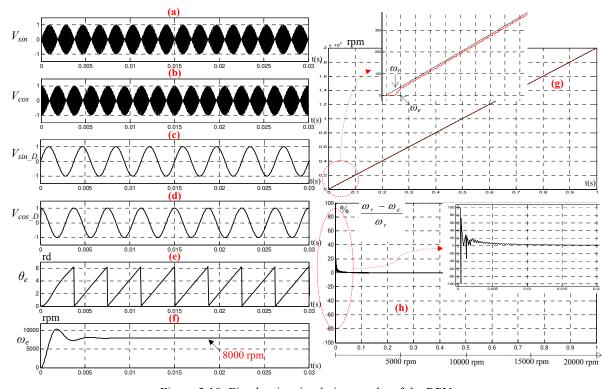

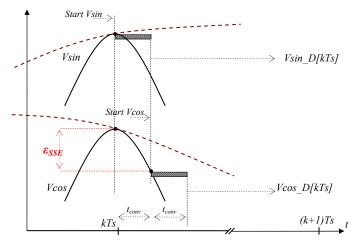

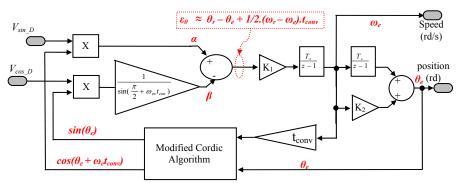

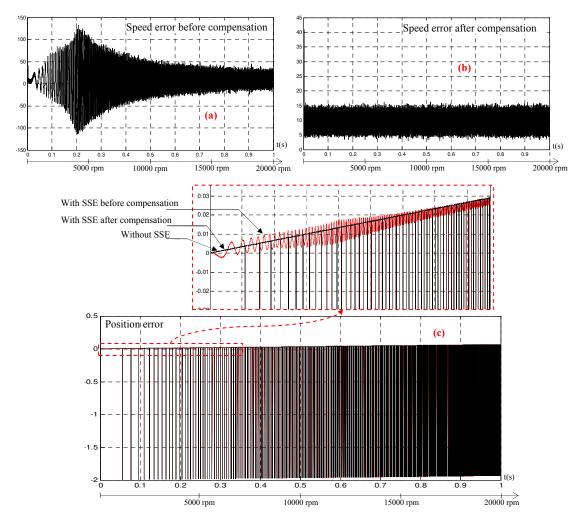

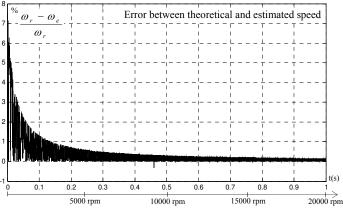

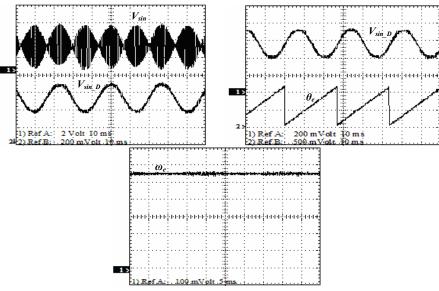

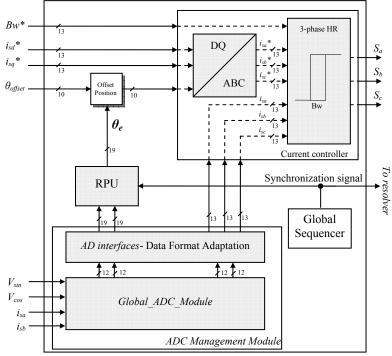

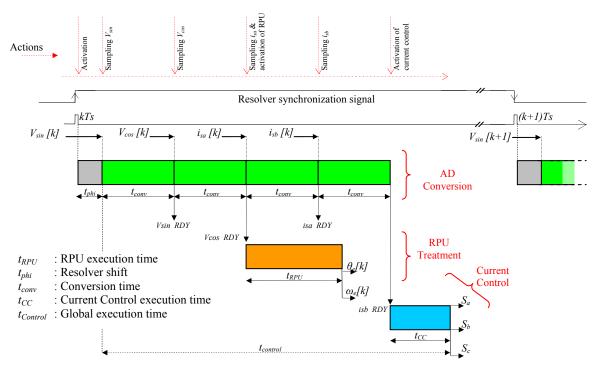

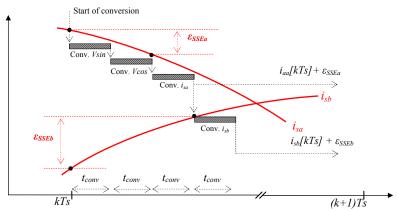

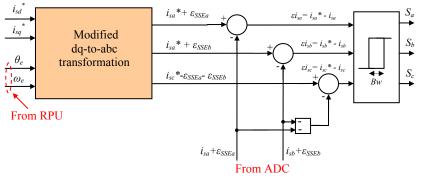

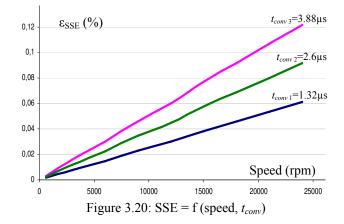

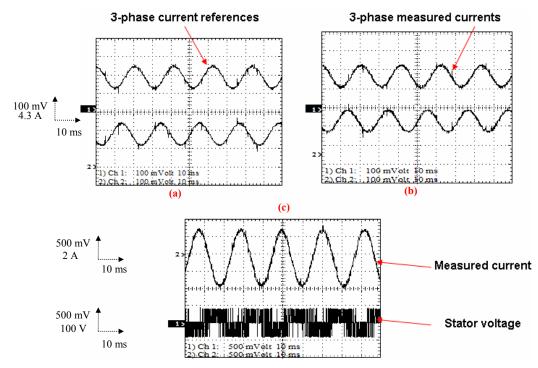

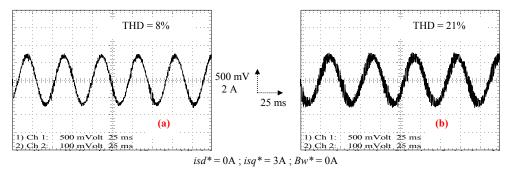

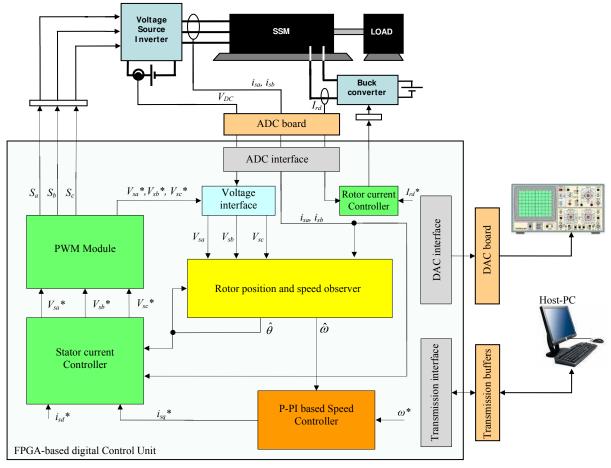

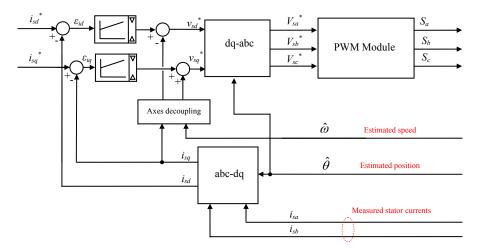

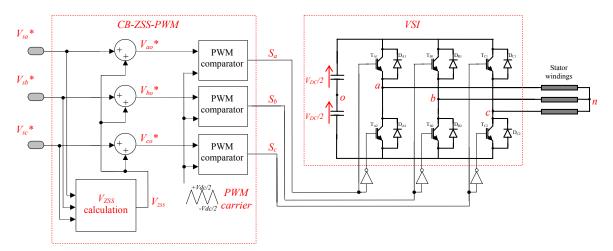

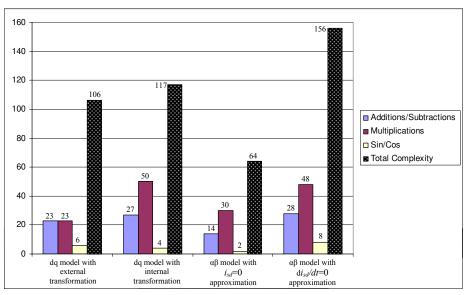

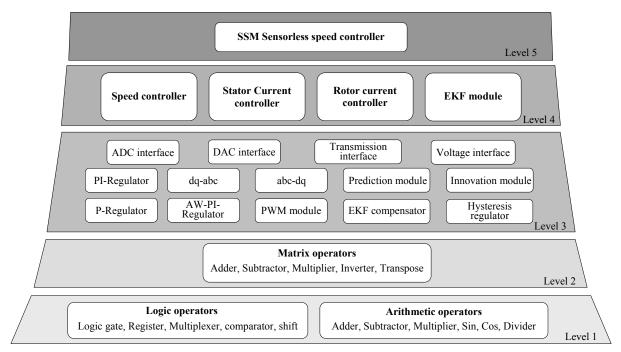

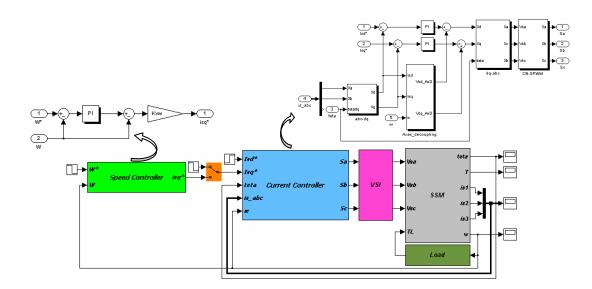

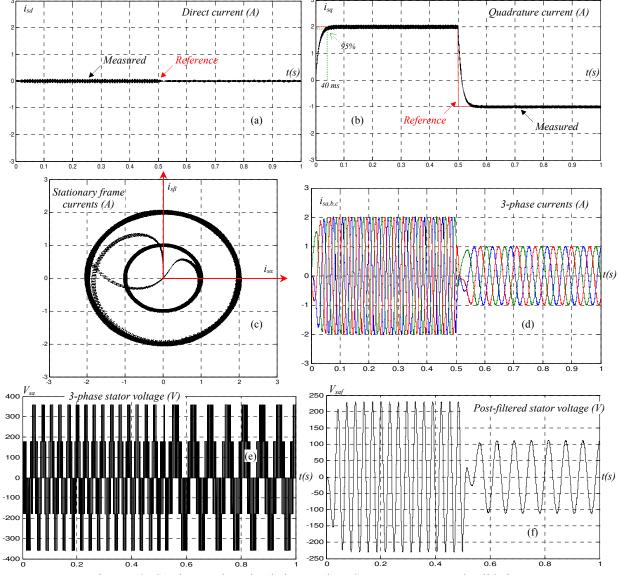

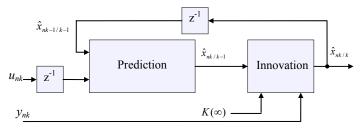

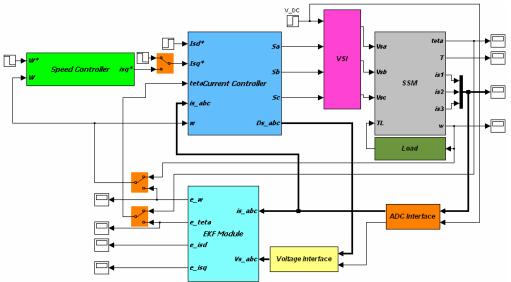

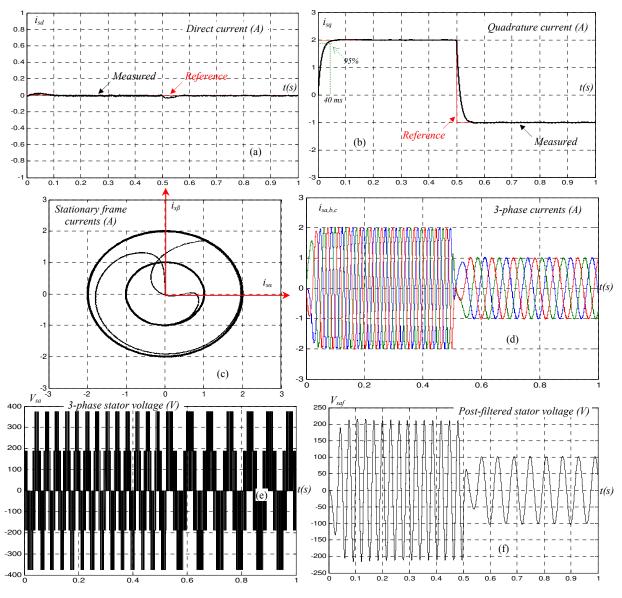

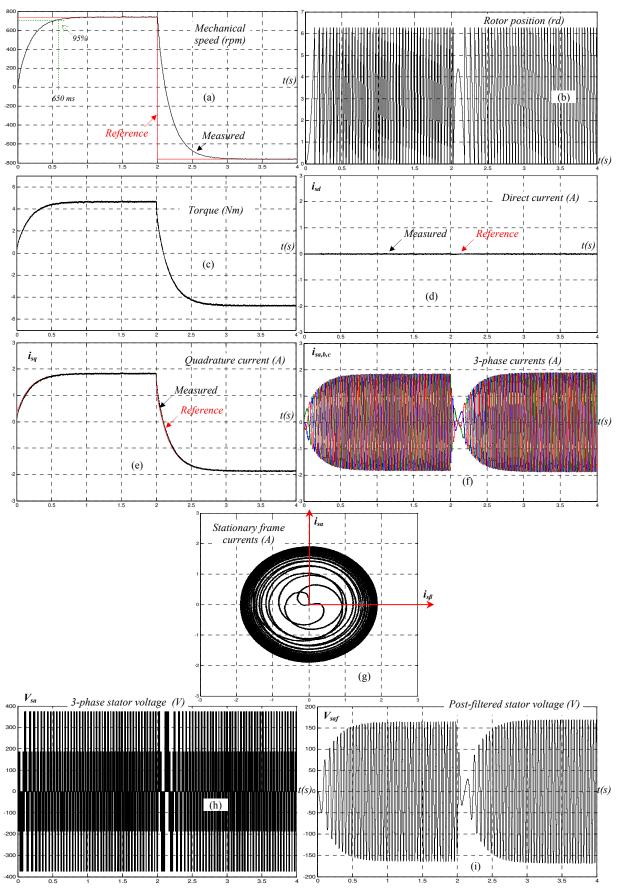

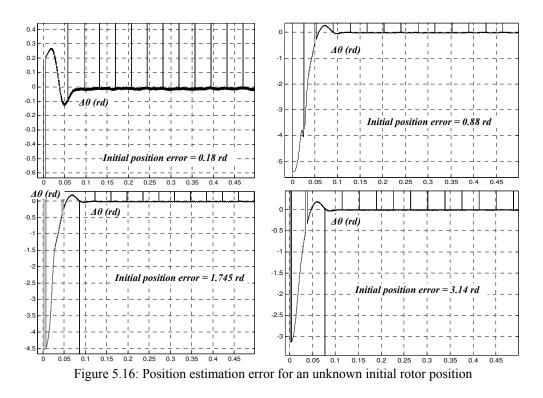

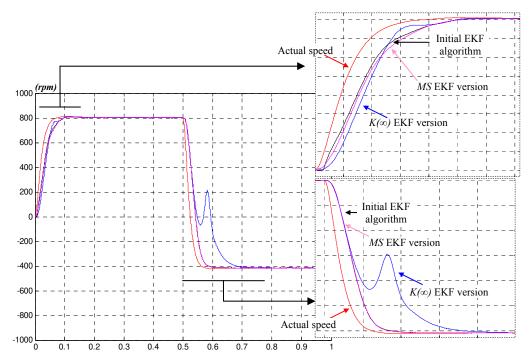

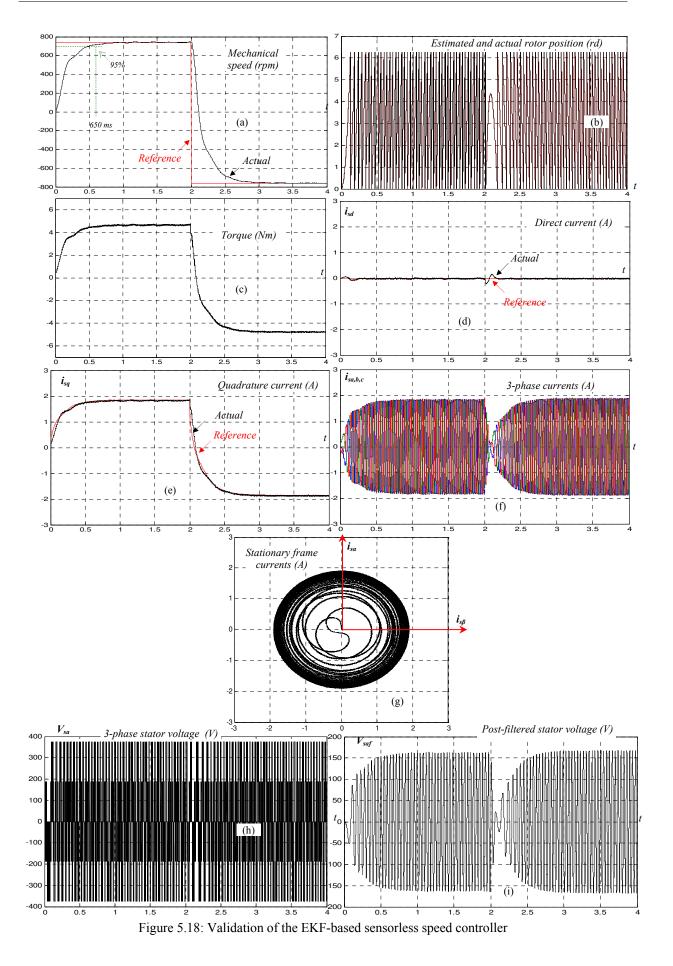

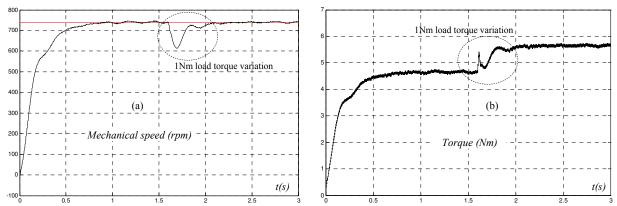

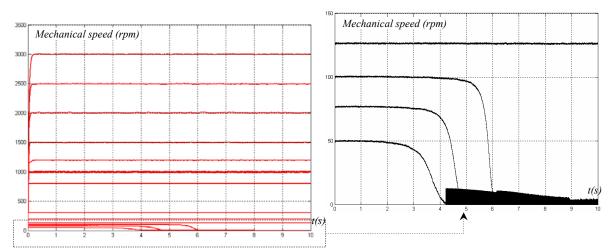

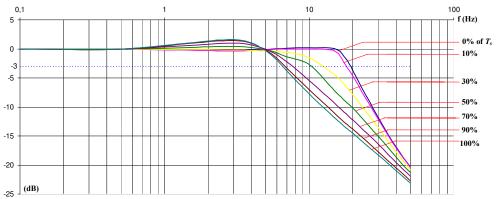

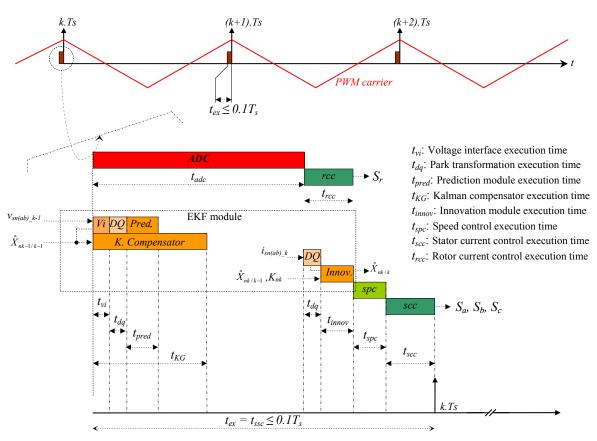

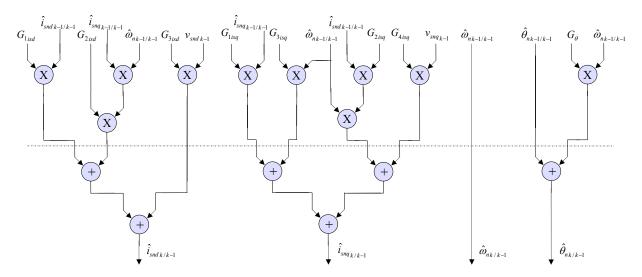

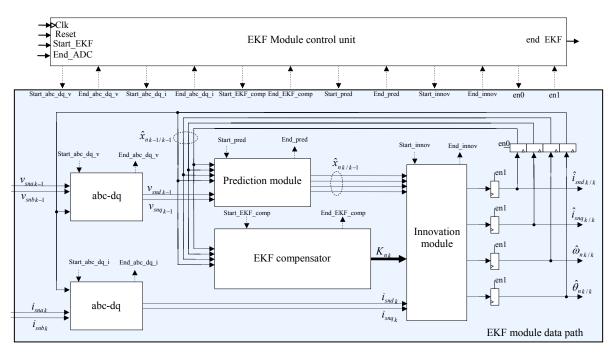

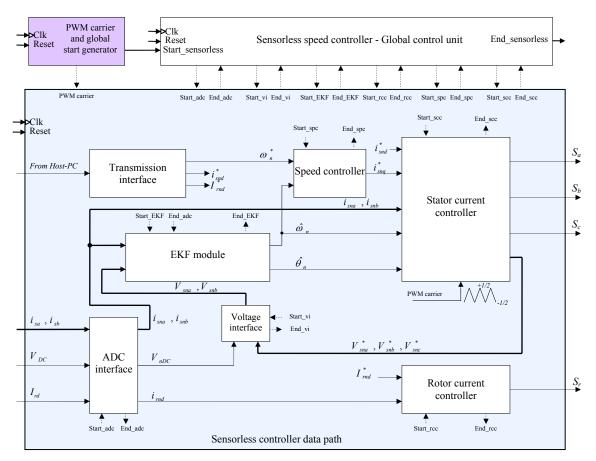

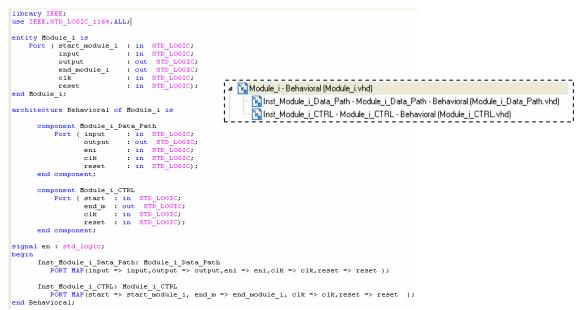

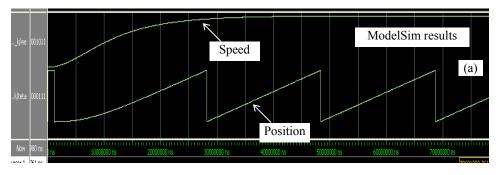

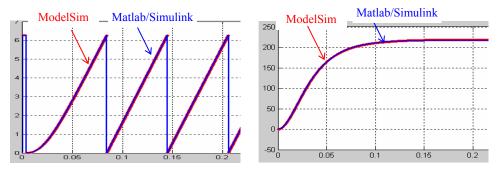

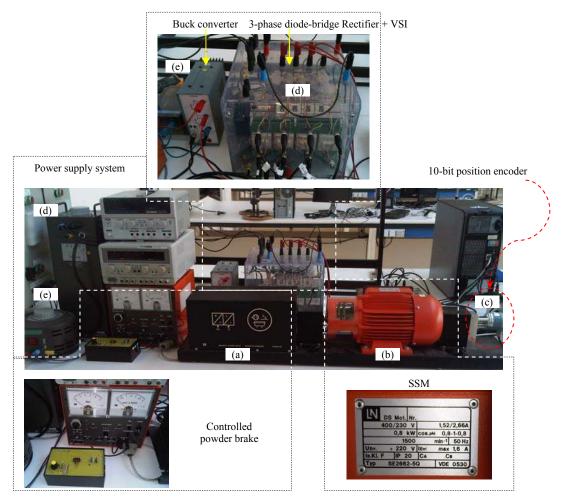

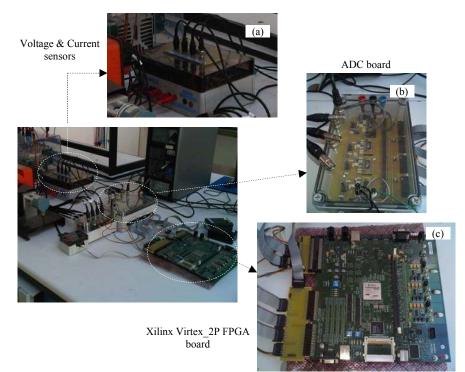

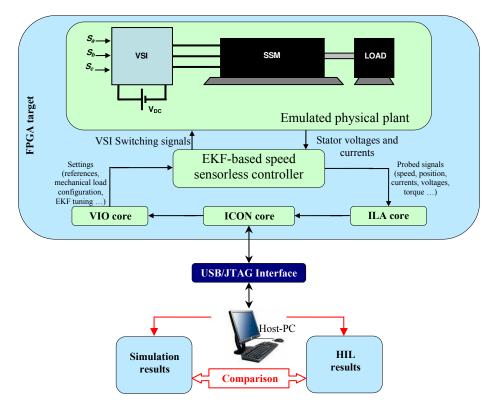

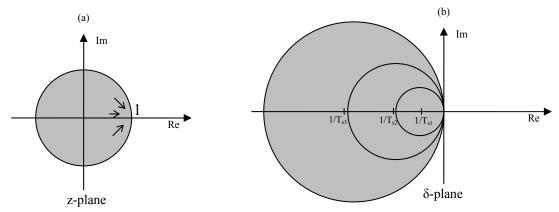

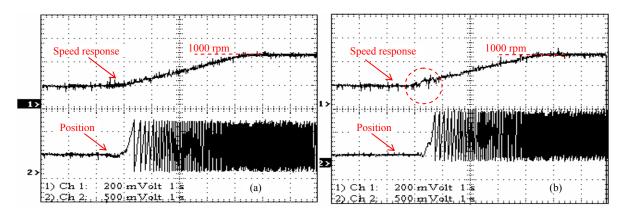

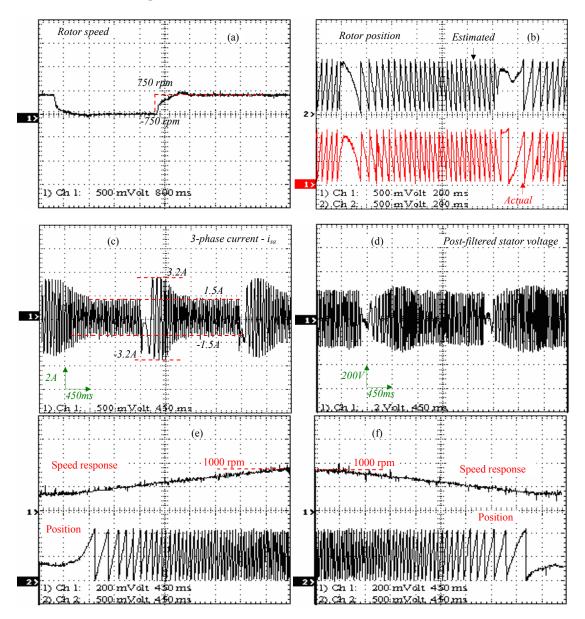

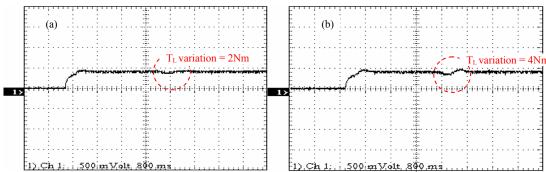

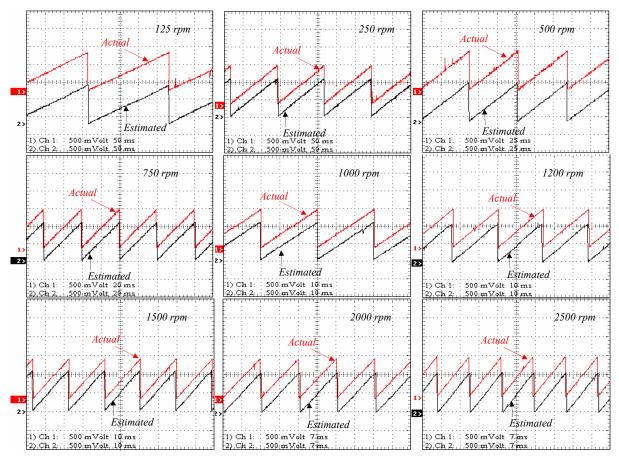

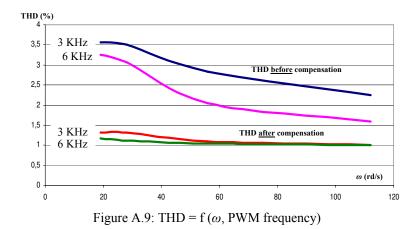

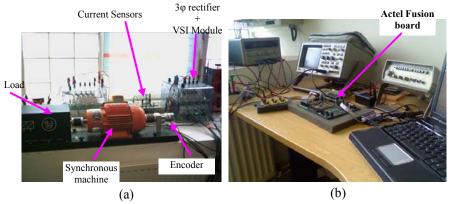

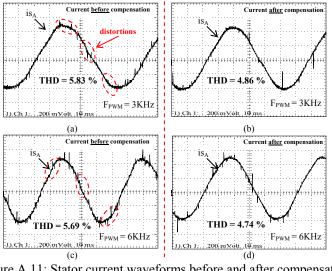

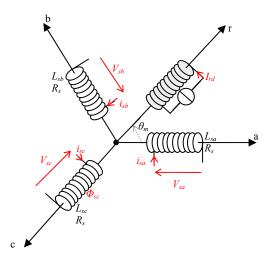

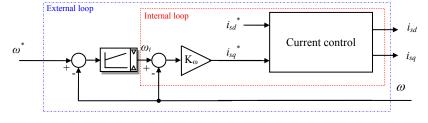

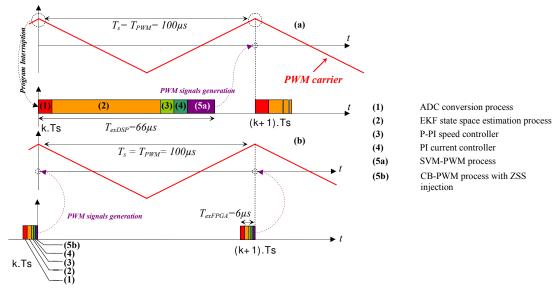

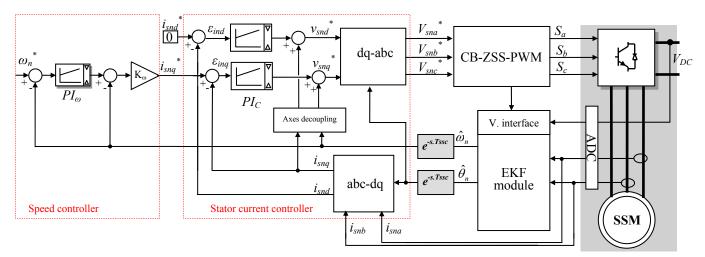

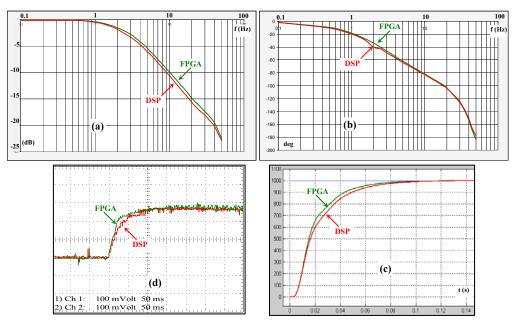

Cyclone-4 FPGAs include up to 360 embedded multipliers organized as columns. Each one can be configured to perform as one 18x18-bit multiplier or two 9x9-bit multipliers. In order to reach high speed performances, each multiplier is pipelined and associated with input/output registers.