## MSc THESIS

# Fully Integrated Analog Front-end for a 2-electrode ECG device

Rachit Mohan Advisor: dr.ir. Wouter A. Serdijn Advisor: ir. Senad Hiseni

FACULTY OF ELECTRICAL ENGINEERING, MATHEMATICS AND COMPUTER SCIENCE

# Fully Integrated Analog Front-end for a 2-electrode ECG device

## THESIS

submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

$\mathrm{in}$

#### Microelectronics

by

Rachit Mohan born in Dhandbad, India

Microelectronics Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Fully Integrated Analog Front-end for a 2-electrode ECG device

#### by Rachit Mohan

#### Abstract

**Ardiovascular** diseases are leading cause of deaths worldwide. With increasing graying population and limited health infrastructure there is a need for portable and implantable ECG devices to diagnose these diseases early on. In general an ECG device requires three or more electrodes, which need to be applied to the body via a gel, to obtain a satisfactory reading. This puts a constraint on the portability of the device. This thesis deals with designing a fully-integrated 10 bit analog front-end i.e. an instrumentation amplifier and an ADC, specifically, for a two-electrode ECG device. Integrated ECG read-out circuits have to deal with two challenges mainly viz. obtaining a high common-mode rejection ratio (CMRR) and integrating large time-constants on the chip.

Firstly, all sources of interference which affect an ECG reading is studied. It is shown that for a portable and integrated read-out circuit, a high CMRR is obtained from the fact that the device will be floating and hence the circuit itself need not have a high CMRR.

Existing techniques for integrating large time-constants are presented and compared. It is shown that these techniques either give rise to unpredictable time-constants and are non-linear near the required cut-off frequency or consume a lot of power from a system perspective. A novel mixed-signal feedback technique using a sigma-delta ADC has been proposed wherein the digital signal is scaled, integrated and fed back to the previous analog stage. The advantages of such a method are more control over the position of the cut-off frequency and higher linearity. The power consumption needed to implement such a technique is negligible.

The circuit is designed in CMOS  $0.35\mu$ m I3T25 technology. The designed instrumentation amplifier reports the best SNR and  $3^{rd}$  highest Noise-Efficienty Factor (NEF). The linearity at the cut-off frequency is shown to be of 10 bits which is an improvement of 3 bits over existing techniques. The total static power consumption for the system is  $66\mu$ W. The implementation of the time-constant consumes only 40nW of static power.

| Laboratory<br>Committee Members | : | ELCA |                          |

|---------------------------------|---|------|--------------------------|

| Advisor:                        |   |      | dr.ir. Wouter A. Serdijn |

| Advisor:                        |   |      | ir. Senad Hiseni         |

| Member:                         |   |      | ir. Thijmen Hamoen       |

| Member:                         |   |      | dr.ir. Michiel Pertijs   |

It's a magical world, let's go exploring - Calvin's last words (of Calvin and Hobbes fame)

TO MY PARENTS

## Contents

| List of Figures  | ix   |

|------------------|------|

| List of Tables   | xi   |

| Acknowledgements | xiii |

| 1        | EC   | G signa | al and device characteristics                         | 3         |

|----------|------|---------|-------------------------------------------------------|-----------|

|          | 1.1  | Struct  | ure of the heart                                      | 3         |

|          | 1.2  | ECG v   | vave                                                  | 5         |

|          | 1.3  | ECG s   | signal characteristics                                | 7         |

|          | 1.4  | Descri  | ption of device                                       | 8         |

|          | 1.5  | Literat | ture study and contribution                           | 10        |

| <b>2</b> | Inte | erferen | ce sources                                            | 13        |

|          | 2.1  | Skin-E  | Electrode Interface                                   | 13        |

|          | 2.2  | Interfe | rence sources                                         | 16        |

|          | 2.3  | Capac   | itively-coupled common-mode interference              | 18        |

| 3        | Sys  | tem-Le  | evel Design                                           | <b>25</b> |

|          | 3.1  | Analog  | g techniques for implementing high-valued resistances | 27        |

|          | 3.2  | Mixed   | -Signal Feedback                                      | 31        |

|          |      | 3.2.1   | Theory                                                | 31        |

|          |      | 3.2.2   | Small signal stability analysis                       | 35        |

|          |      | 3.2.3   | Comparison with alternative architectures             | 37        |

|          |      | 3.2.4   | Block-level Implementation                            | 39        |

| 4        | Cire | cuit-Le | vel Design                                            | 43        |

|          | 4.1  | Design  | of Instrumentation Amplifier                          | 43        |

|          |      | 4.1.1   | Design of feedback                                    | 43        |

|          |      | 4.1.2   | Design for noise                                      | 44        |

|          |      | 4.1.3   | Design for low-pass cut-off frequency                 | 48        |

|          |      | 4.1.4   | Distortion                                            | 51        |

|          | 4.2  | Design  | of the comparator                                     | 52        |

|          | 4.3  | Design  | of the DAC                                            | 55        |

|          |      | 4.3.1   | Selection of DAC pulse waveform                       | 56        |

|          | 4.4  | Design  | of input $g_{\rm m}$ -C stage                         | 56        |

|          | 4.5  | Design  | of charge pump                                        | 58        |

| <b>5</b> | $\mathbf{Sim}$ | ulation Results                                       | 61 |

|----------|----------------|-------------------------------------------------------|----|

|          | 5.1            | High-pass cut-off frequency                           | 61 |

|          | 5.2            | ENOB                                                  | 61 |

|          | 5.3            | Power Consumption and Efficiency                      | 62 |

|          | 5.4            | Effect of Mismatch, Process Variation and Temperature | 65 |

|          | 5.5            | System Area                                           | 69 |

| 6        | Con            | clusion and Recommendation for Future Work            | 75 |

|          | 6.1            | Conclusion and original scientific contribution       | 75 |

|          | 6.2            | Recommendation for Future Work                        | 76 |

| Bi       | bliog          | raphy                                                 | 83 |

## List of Figures

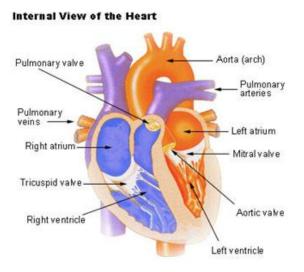

| 1.1  | Internal view of the heart $[1]$                                                                                                            | 3   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

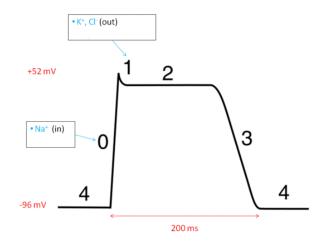

| 1.2  | Cardiac Action Potential [2]                                                                                                                | 5   |

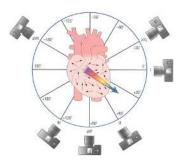

| 1.3  | ECG signal is a vector quantity [3]                                                                                                         | 6   |

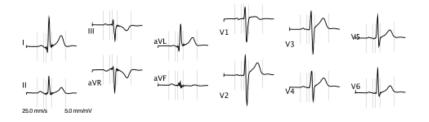

| 1.4  | ECG signals from different leads [4]                                                                                                        | 6   |

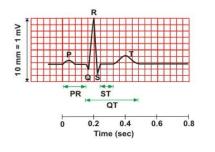

| 1.5  | $ECG \text{ signal } [5] \dots \dots$ | 7   |

| 1.6  | Standard 3-electrode position [6]                                                                                                           | 9   |

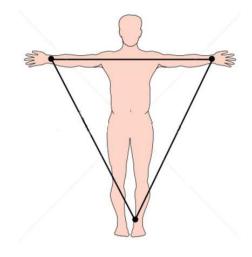

| 1.7  | Proposed ECG device                                                                                                                         | 9   |

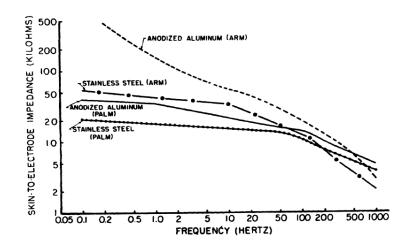

| 2.1  | Skin-electrode impedance vs frequency for two different materials [7]                                                                       | 14  |

| 2.2  | Skin-electrode impedance of stainless-steel vs time for 10 subjects                                                                         | 15  |

| 2.3  | Passive models for skin-electrode interface                                                                                                 | 16  |

| 2.4  | Main sources of interference in an ECG read-out                                                                                             | 17  |

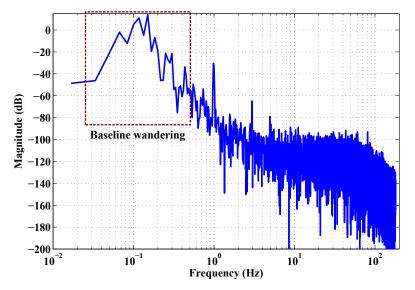

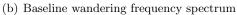

| 2.5  | Sample ECG signal and its frequency Spectrum                                                                                                | 19  |

| 2.6  | Effect of Baseline wandering and muscle artefact on ECG signal                                                                              | 20  |

| 2.7  | 2-electrode power-line interference model and its equivalent circuit $\ldots$                                                               | 22  |

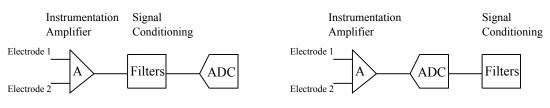

| 3.1  | Analog Implementation of front-end of readout                                                                                               | 25  |

| 3.2  | Digital Implementation of front-end of readout                                                                                              | 25  |

| 3.3  | Conventional analog front-end signal flow                                                                                                   | 26  |

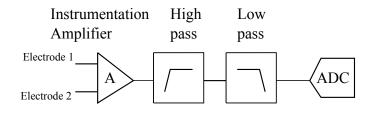

| 3.4  | T-network impedance scaler                                                                                                                  | 28  |

| 3.5  | Analog Implementation of front-end of readout                                                                                               | 28  |

| 3.6  | MOS-BIPOLAR view of a pseudo-resistor                                                                                                       | 28  |

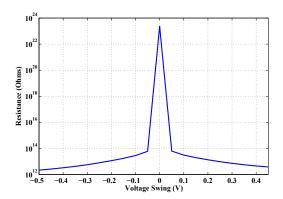

| 3.7  | Incremental resistance vs voltage swing across pseudo-resistor                                                                              | 29  |

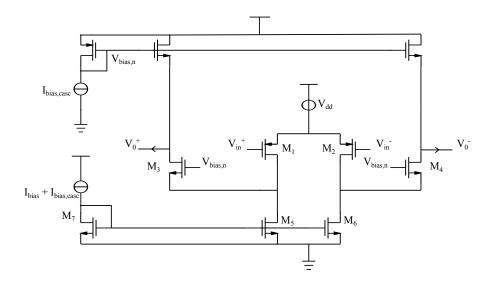

| 3.8  | RC circuit using pseudo-resistor                                                                                                            | 29  |

| 3.9  | Distortion due to pseudo-resistor for 50mHz, 100mV signal swing, for                                                                        |     |

|      | $f_{\rm hpf,pseudo} = 50 {\rm mHz}$                                                                                                         | 30  |

| 3.10 | Distortion due to pseudo-resistor for 1Hz, 100mV signal swing for                                                                           |     |

| 0.11 | $f_{\rm hpf,pseudo} = 50 \mathrm{mHz}$                                                                                                      | 30  |

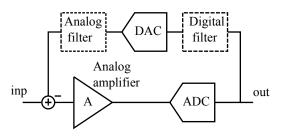

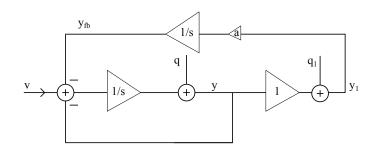

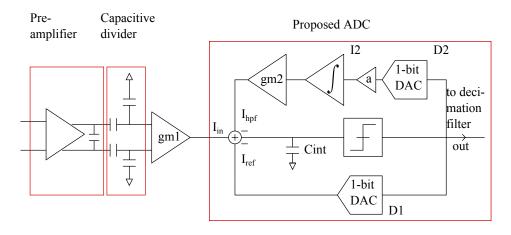

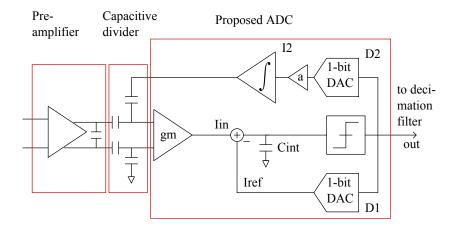

|      | Generalized block diagram of the mixed-signal feedback technique                                                                            | 31  |

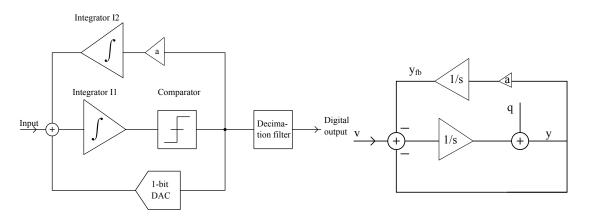

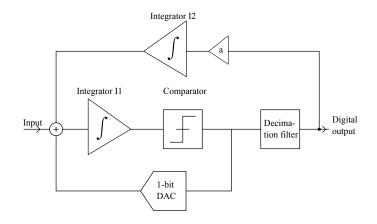

|      | Block Diagram of First order Sigma-Delta Modulator                                                                                          | 32  |

|      | Linearized model of Sigma-Delta Modulator                                                                                                   | 32  |

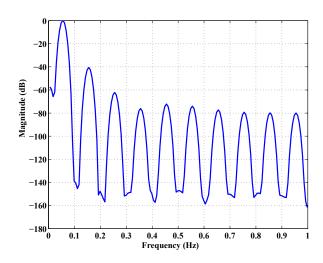

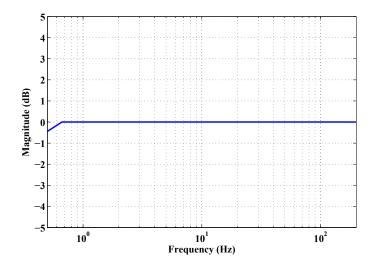

|      | Signal Transfer Function of a conventional Sigma Delta Modulator                                                                            | 33  |

|      | Noise Transfer Function of a conventional Sigma Delta Modulator                                                                             | 33  |

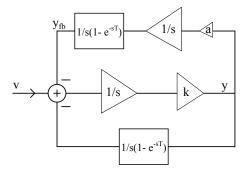

|      | Sigma Delta ADC with second feedback loop                                                                                                   | 35  |

|      | s-domain equivalent block diagram                                                                                                           | 35  |

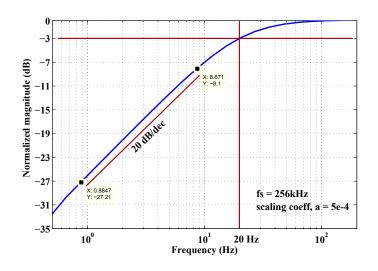

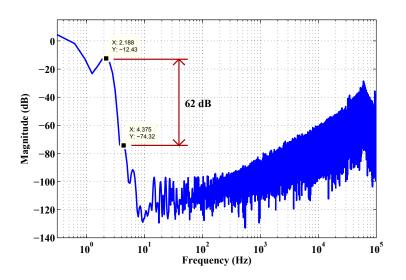

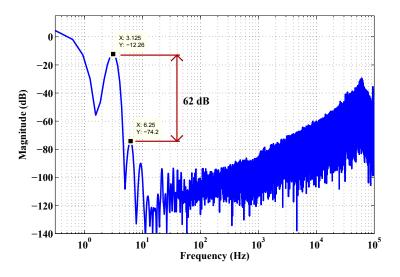

|      | Signal Transfer Function for the proposed block diagram at $f_s = 256$ kHz .                                                                | 36  |

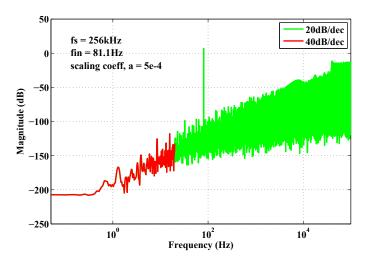

|      | Noise Transfer Function for the proposed block diagram at $f_s = 256 \text{kHz}$ .                                                          | 36  |

|      | Model for analysing the stability of the sigma-delta loop                                                                                   | 36  |

| 3.21 | Alternative architecture wherein the feedback is taken after the decimation                                                                 | 0.5 |

| 9.00 | filter                                                                                                                                      | 37  |

|      | Equivalent s-domain model                                                                                                                   | 38  |

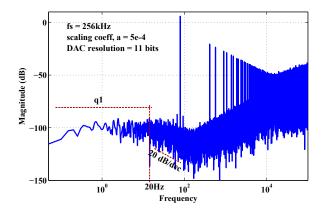

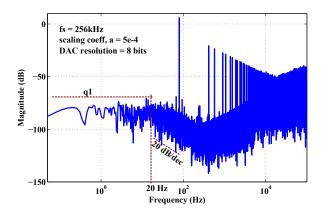

| 3.23 | 12 bit ADC followed by a 11-bit DAC in the feedback                                                                                         | 38  |

| 3.24 | 12 bit ADC followed by a 8-bit DAC in the feedback                                                                                                                                           | 38 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.25 | Scaling and Integration performed in two stages                                                                                                                                              | 41 |

| 3.26 | Scaling and Integration performed in a single-stage with a charge-pump .                                                                                                                     | 41 |

| 3.27 | System-level diagram with two transconductance stage                                                                                                                                         | 42 |

| 3.28 | System-level diagram with just one transconductance stage                                                                                                                                    | 42 |

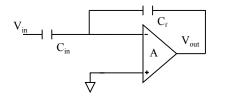

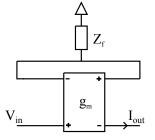

| 4.1  | Transimpedance amplifier configuration                                                                                                                                                       | 44 |

| 4.2  | Voltage amplifier configuration                                                                                                                                                              | 44 |

| 4.3  | Transconductance Amplifier configuration                                                                                                                                                     | 44 |

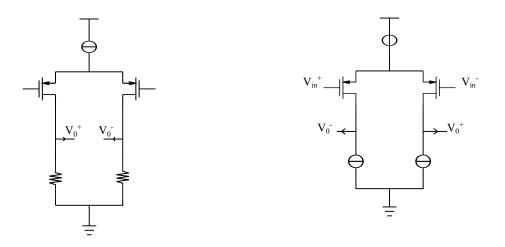

| 4.4  | Conventional Differential Amplifier                                                                                                                                                          | 45 |

| 4.5  | Proposed Differential Amplifier                                                                                                                                                              | 45 |

| 4.6  | Single-sided Input, Single-sided Output Amplifier                                                                                                                                            | 45 |

| 4.7  | Biasing of the proposed differential amplifier                                                                                                                                               | 45 |

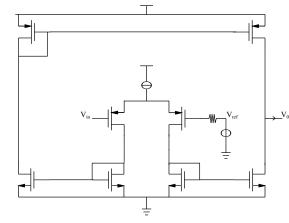

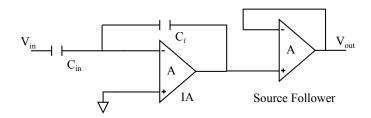

| 4.8  | Instrumentation Amplifier schematic                                                                                                                                                          | 47 |

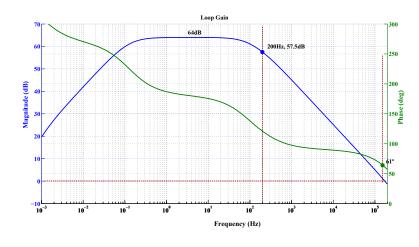

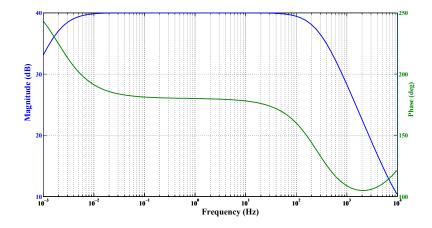

| 4.9  | Loop Gain                                                                                                                                                                                    | 49 |

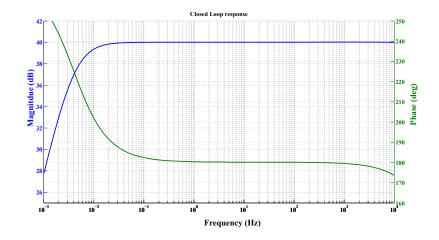

| 4.10 |                                                                                                                                                                                              | 49 |

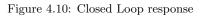

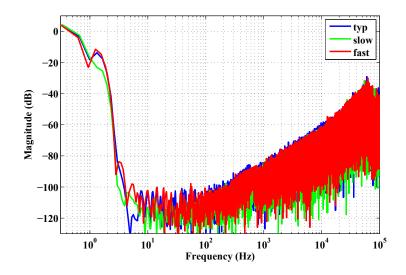

|      | Input-referred noise of the instrumentation amplifier                                                                                                                                        | 49 |

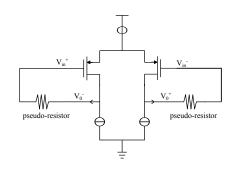

|      | Indirect Feedback                                                                                                                                                                            | 50 |

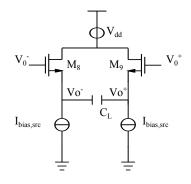

|      | Schematic of the source follower                                                                                                                                                             | 51 |

| 4.14 | Magnitude and Phase response of the amplifier followed by the source follower                                                                                                                | 51 |

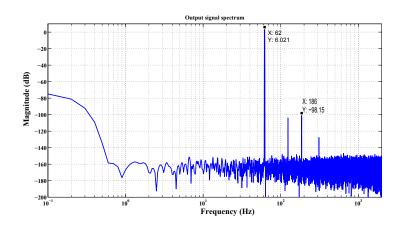

| 4.15 | Frequency spectrum of the output of the amplifier for input frequency =                                                                                                                      |    |

|      | 62Hz                                                                                                                                                                                         | 52 |

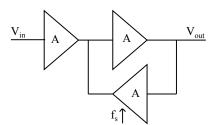

| 4.16 | Chain of large-gain amplifiers                                                                                                                                                               | 52 |

| 4.17 | Amplifier with hysterisis                                                                                                                                                                    | 52 |

| 4.18 | Latched amplifier                                                                                                                                                                            | 53 |

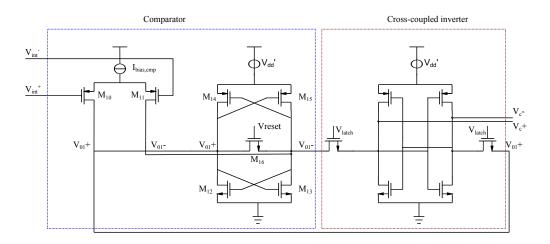

| 4.19 | Schematic of a latched comparator                                                                                                                                                            | 54 |

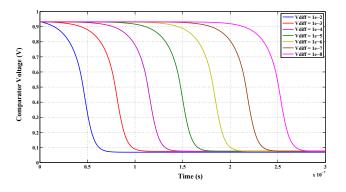

| 4.20 | Response time variation of comparator to different input voltage differences                                                                                                                 | 54 |

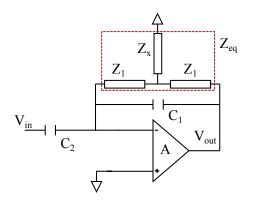

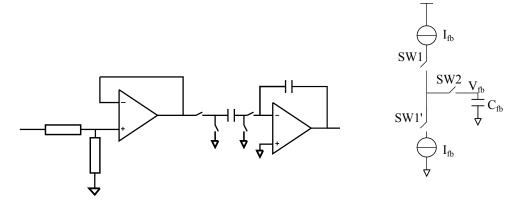

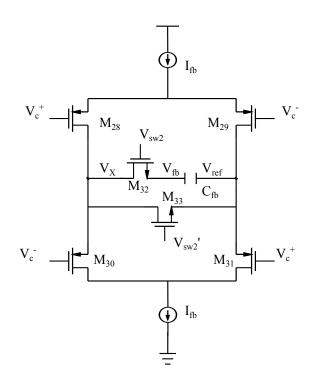

| 4.21 | Schematic of the differential DAC implementation                                                                                                                                             | 55 |

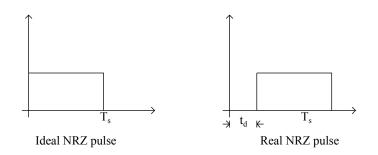

| 4.22 | NRZ pulse response                                                                                                                                                                           | 56 |

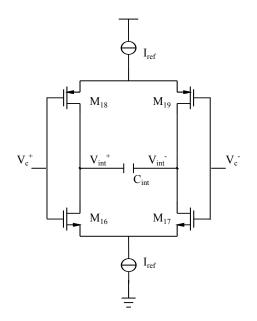

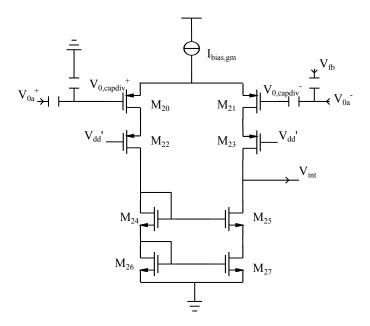

| 4.23 | Schematic of the cascoded gm-stage implementation                                                                                                                                            | 57 |

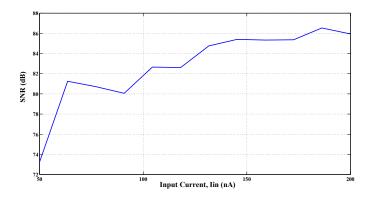

| 4.24 | SNR vs the Input current to the modulator                                                                                                                                                    | 58 |

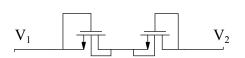

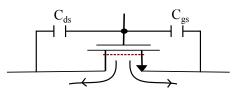

| 4.25 | Charge Injection from MOS switch                                                                                                                                                             | 59 |

| 4.26 | Charge Pump schematic                                                                                                                                                                        | 60 |

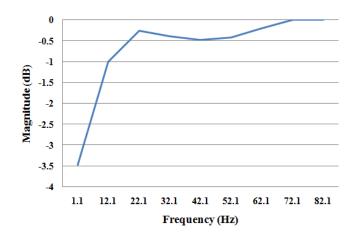

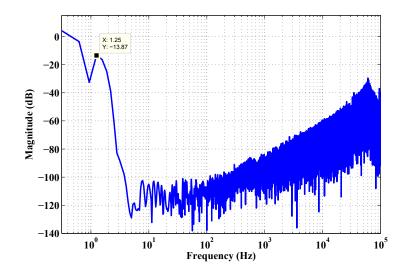

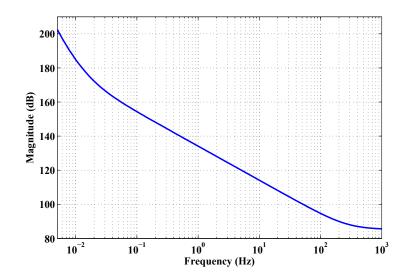

| 5.1  | STF of the designed modulator                                                                                                                                                                | 61 |

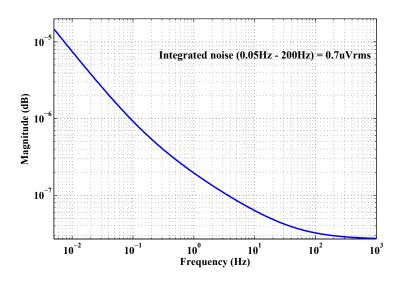

| 5.2  | Input-referred noise of the whole system                                                                                                                                                     | 62 |

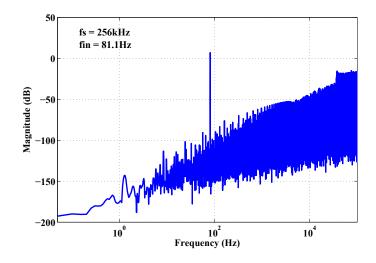

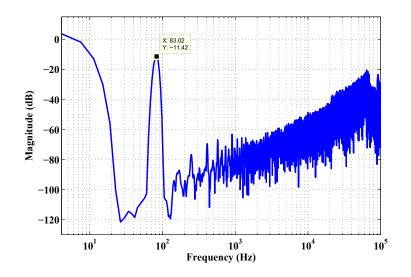

| 5.3  | Modulator output for $f_{\rm in} = 82.1$ Hz                                                                                                                                                  | 63 |

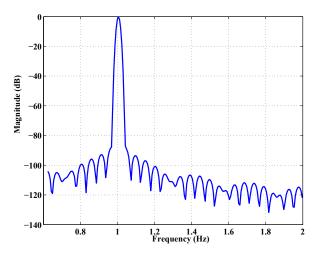

| 5.4  | Modulator output for $f_{\rm in} = 1.1 \text{Hz}$                                                                                                                                            | 63 |

| 5.5  | Modulator output for $f_{\rm in} = 2.1 \text{Hz} \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                      | 64 |

| 5.6  | Modulator output for $f_{\rm in} = 3.1 \text{Hz} \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                      | 64 |

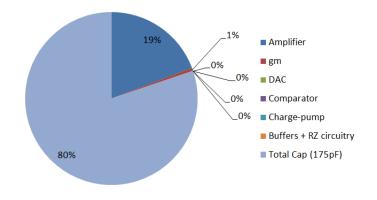

| 5.7  | Block-wise break-up of power consumption                                                                                                                                                     | 65 |

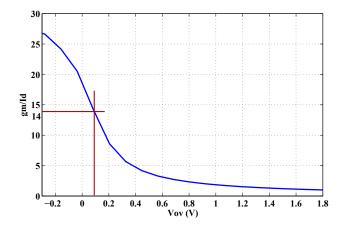

| 5.8  | $\frac{g_{\rm m}}{I_{\rm d}}$ of the input transistor $\ldots \ldots \ldots$ | 66 |

| 5.9  | PSRR vs frequency of the amplifier                                                                                                                                                           | 67 |

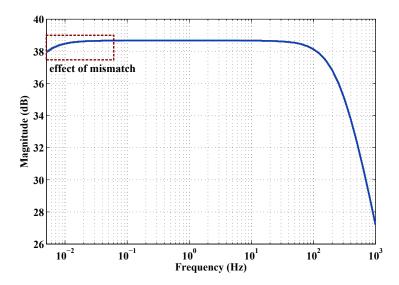

| 5.10 | Effect of mismatch between components on the amplifier transfer function                                                                                                                     | 67 |

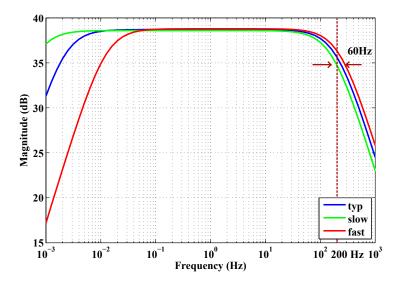

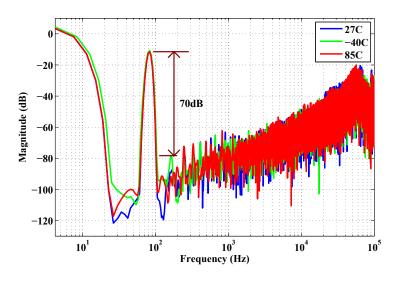

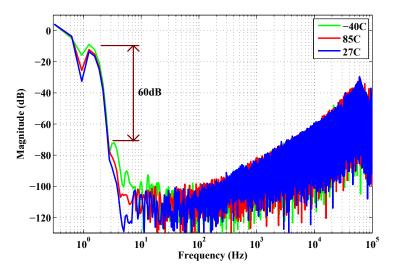

| Effect of process variations on the amplifier transfer function                         | 68                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

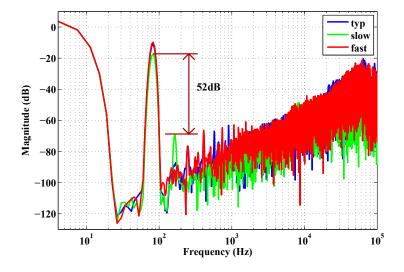

| Effect of process variation on the Modulator for $f_{\rm in} = 82.1 \text{Hz}$          | 68                                                                                                                                                                                                                                                                                                                       |

| Effect of process variation on the Modulator for $f_{in} = 1.1$ Hz                      | 69                                                                                                                                                                                                                                                                                                                       |

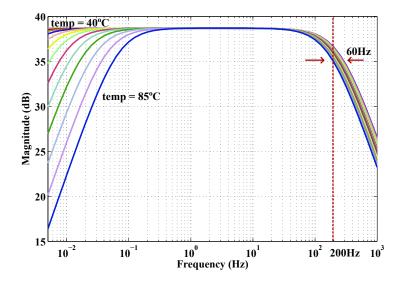

| Effect of temperature on the amplifier transfer function                                | 70                                                                                                                                                                                                                                                                                                                       |

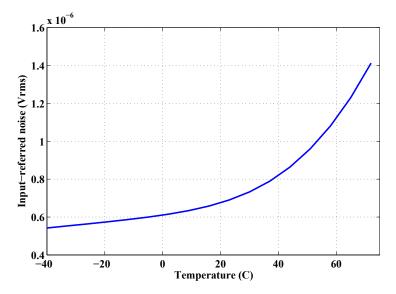

| Effect of temperature on the integrated input-referred noise                            | 70                                                                                                                                                                                                                                                                                                                       |

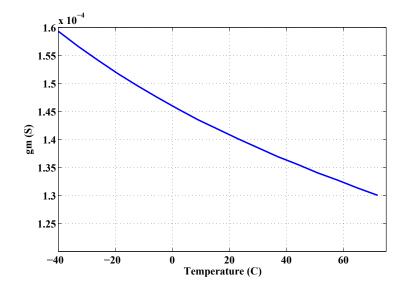

| Effect of temperature on $g_{m1,2}$                                                     | 71                                                                                                                                                                                                                                                                                                                       |

| Effect of temperature on modulator output for $f_{\rm in} = 82.1 \text{Hz} \dots \dots$ | 72                                                                                                                                                                                                                                                                                                                       |

| Effect of temperature on modulator output for $f_{\rm in} = 1.1 {\rm Hz}$               | 72                                                                                                                                                                                                                                                                                                                       |

| Block-wise break-up of area                                                             | 73                                                                                                                                                                                                                                                                                                                       |

|                                                                                         | Effect of process variation on the Modulator for $f_{\rm in} = 82.1 {\rm Hz}$ Effect of process variation on the Modulator for $f_{\rm in} = 1.1 {\rm Hz}$ Effect of temperature on the amplifier transfer function Effect of temperature on the integrated input-referred noise Effect of temperature on $g_{\rm m1,2}$ |

## List of Tables

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | A few ECG applications along with the required frequency bandwidth<br>System specifications                                                                                                                               | 8<br>11              |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $2.1 \\ 2.2$                              | Impedance values for stainless steel dry electrode                                                                                                                                                                        | $\frac{15}{21}$      |

| 3.1<br>3.2<br>3.3<br>3.4                  | Fully Analog Implementation vs Fully Digital ImplementationSheet resistance of a few polysilicon resistors in I3T25 technologySummary of choice of ADCComparison between continuous-time and discrete-time implementation | 26<br>27<br>32       |

| 3.5<br>3.6                                | of loop filter                                                                                                                                                                                                            | 34<br>39<br>40       |

| $4.1 \\ 4.2 \\ 4.3 \\ 4.4$                | Operating points of components in the Instrumentation Amplifier<br>Operating points of components in the Source follower                                                                                                  | 48<br>51<br>55<br>58 |

| $5.1 \\ 5.2 \\ 5.3$                       | Block-wise break-up of power consumption                                                                                                                                                                                  | 65<br>66<br>70       |

| 6.1                                       | Resulting specification of the designed system                                                                                                                                                                            | 76                   |

## Acknowledgements

This report would not have been possible without the support and counseling of several people who helped, directly or indirectly, me in completing it.

First, I would like to thank my thesis supervisor Wouter Serdijn. The fact that he guided me by helping me ask the right questions has moulded me and even made me confident to face the challenges that lie ahead in both professional and personal life. Senad Hiseni, officially my mentor but unofficially a friend who provided the much necessary kick whenever I started slouching. I would like to take this opportunity to express my gratitude to both Senad and Wouter for supporting me throughout the year even when it was easier not to do so.

I would also like to thank Applied Biomedical Systems BV (ABS) for providing me an opportunity to work on this topic. I would especially like to thank Vincent Larik, Ryan Blei and Jerry for the meetings that were held. They helped me provide a direction to my thesis.

I am thankful for the awesome work-fun environment of the 18<sup>th</sup> floor. I had a great time at the football match, ELCA festival, day-out at the beach, dinner get-together, barbeque. The culture of cake-for-any-reason-and-any-season is something that I absolutely loved and hopefully will try to spread. I would especially like to thank Vincent, Wu and Marion for diligently lending me their coffee cards and thus increasing my productivity. Without you I would have had blood instead of coffee running in my veins. I would also like to thank Antoon Frehe for helping me out with never-ending server issues.

There are not many things which are more enjoyable than hanging out aimlessly with close-friends. I would like to specially thank my friends Apurva, Shishir and Rahul for providing me with these times. They helped me get through a roller-coaster year smoothly.

Last and definitely not the least, I would like to thank my parents for trusting and believing in me. A big thanks to my mother for her constant nagging to keep me focused on my work.

Looking back, this report is not just the culmination my master thesis but of my whole journey of master programme at TU Delft. When Pooh was once asked what was his best moment, he couldn't answer it because although he enjoyed eating honey, the moment just before he ate it, which had no name, was the best. These two years have been 'that' moment.

Rachit Mohan Delft, The Netherlands November 22, 2011 Use of electricity in medical diagnosis has undergone rapid progress since the time Lugi Galvani, an Italian anatomist in the 18th century, demonstrated the existence of 'animal electricity' in frogs [8]. From then to nowadays, wherein electrical currents generated by the various parts of the body such as the heart, the brain, the muscles to name a few, are used for medical diagnosis, the understanding and usage of this discovery has advanced a great deal.

ECG(electrocardiogram) is by far the most common usage of electrical activity reading for medical diagnosis [9]. It is a recording of the electrical activity generated by the heart over a period of time. By interpreting this activity, one can diagnose the condition of the heart. The first ECG device was invented in 1902 by Willem Einthoven, a Dutch scientist [10]. Generally, the ECG is monitored by placing a number (3-12) of electrodes (also known as leads) on the human body. To obtain a satisfactory reading, the skin needs to be chafed and a special (Ag-AgCl) gel needs to be applied before connecting the electrodes [11].

Traditionally, the ECG devices have been quite bulky and costly and thus are present only in select hospitals and health centers. The increasing graying population, especially in the western world, has spawned a need for the overhaul of the present limited health infrastructure and enablement of personal, cheap and immediate healthcare to people. Thus there is a great deal of interest in portable, hand-held devices and implantable solutions which would enable in the read-out of these electrical signals.

This thesis concentrates on developing an integrated analog front-end circuit for a portable 2-electrode ECG device which uses 'dry' electrodes i.e. no gel needs to be applied. By using such electrodes not only certified technicians are not needed to operate the ECG device but also ensures that the skin need not be prepared every time an ECG is to be read and thus increases patient comfort. By reducing the number of electrodes, the size of the device can be made smaller and thus more portable. A fully integrated front-end solution also helps in this respect. Currently, integrated solutions manage to achieve a maximum of 8 bits of resolution. There is a need for High-resolution ECGs (> 10 bit) which aid in diagnosing conditions such as AMI (Acute Myocardial Infarction) [12].

This thesis will examine the feasibility i.e. the advantages and challenges of using a 2-electrode device from a circuit-level perspective. This thesis will also investigate the challenges in increasing the resolution of an integrated front-end. The main objectives of the thesis can be broadly stated as:

1. Identify all the interference sources which would affect the performance of the above described device.

- 2. Identify the bottleneck for resolution in an integrated design and suggest possible solutions.

- 3. Develop a circuit-level schematic of the system based on the study done in the above points.

- 4. Design the whole system for low-power operation.

This report is divided into six chapters. Chapter 1 provides pre-requisite knowledge for designing an ECG read-out device. It discusses the principle of generation of an ECG signal and ECG device characteristics. It also discusses the existing work in literature in this area and original contributions of this thesis in brief. Chapter 2 studies the interference sources that affect an ECG reading. This will be followed by discussing the system-level design in Chapter 3. Chapter 4 concentrates on circuit-level design and the challenges encountered for each of the blocks identified in Chapter 3. In Chapter 5, system simulation results are presented. Chapter 6 provides a summary of this report and concludes with possible improvements in the design.

# 1

To understand the specifications of the read-out device, it is first necessary to understand the characterisctics of the input signal i.e. the ECG. Section 1.1 describes the working of the heart and explains how the ECG is generated. Section 1.2 and Section 1.3 present the nomenclature and the characteristics of the ECG signal. Section 1.4 describes the physical characteristics of the read-out device. This knowledge is important as it will be used in later chapters to make a few decisions regarding the design of the circuit. The chapter concludes by a brief discussion on the existing work in literature in this area, the challenges specific to the design of read-out circuit for this particular application and original contribution of this thesis.

## 1.1 Structure of the heart

The heart is an inverted conical shaped, hollow muscular organ, about the size of a human fist. It is divided into right and left sides by a vertical wall made of muscle called the septum. Both the sides are further divided into two with the top chambers called the atria and the bottom chambers called the ventricles. The left and right atria and their corresponding ventricles are separated from each other by one-way valves called mitral valve and tricuspid valve respectively.

The left and right sides of the heart can be imagined as self-contained pumping

Figure 1.1: Internal view of the heart [1]

stations which are connected in series. The left side drives oxygen-rich blood, which it receives from the lungs, to all the cells of the body. The oxygen-rich blood enters into the left atrium from the lungs through a valve called the pulmonary valve. The atrium contracts and sends the blood into the left ventricle through the mitral valve which closes once this operation is over to prevent it from flowing back into the atrium. The left ventricle then contracts and sends it for circulation into the body. The working of the right atrium and the right ventricle is similar to that of its left counterparts. After circulation, the oxygen-poor blood returns to the right atrium. The right atrium then contracts and transfers it to the right ventricle through the tricuspid valve. Like the mitral valve, this also closes after the blood is transferred to prevent the blood from flowing back. The right ventricle then contracts and sends this blood to the lungs for replenishment, completing one full cycle.

The contraction of the chambers is triggered through application of electrical impulses or stimuli. These impulses are generated at regular intervals by the SA node (SinoAtrial node) present in the right atrium. Each impulse travels throughout the walls of the atrium, causing it to contract. There is a node present between the atrium and ventricles called the AV node (AtrioVentricular node) which adds a delay to the impulse traveling from the atrium to the ventricle. This ensures that the atria contract before the ventricles do. Electrical impulses travel in the heart (as a matter of fact in the whole human body) by a phenomenon called depolarization and re-polarization which will now be discussed as it is crucial in understanding how an ECG wave is generated.

All the cells maintain an electrical charge difference across their membranes, known as the resting potential of the cell. This electrical polarization is present due to complex protein structures embedded into the cell membrane. The potential difference across the cell membrane is around 70mV-80mV for atrial cells and 90mV for ventricular cells. By convention, the potential outside the cell membrane is taken as reference.

In the resting phase, i.e., when there is no electrical stimulus applied to the cell, positive  $Na^+$  and  $Ca^{2+}$  ions are present outside the cell membrane and negative  $Cl^-$  ions within it. If a potential below a certain threshold value is applied outside the cell (stimulus given by pacemaker cells), channels within the membrane open and positive ions rush inside the cell to achieve equilibrium. The influx of positive ions increases the potential of the cell and thus opening more channels in the membrane. This continues to happen until all the channels are open. The equilibrium is reached when the cell potential reaches around +10mV w.r.t its surroundings. This causes a breakdown in the membrane of the adjacent cell and so on, leading to a wave called the depolarization wave.

After depolarization of the cell, the concentration of  $Ca^{2+}$  ion within it increases by almost an order of magnitude. This leads to hydrolysis of ATP (a type of protein) present within the cell, causing the cell membrane to close and the cell to contract. The whole cycle of depolarization and re-polarization keeps on repeating till an electrical stimulus is applied. One cycle of polarization is known as an action potential. Fig. 1.2 depicts a cardiac action potential i.e. one cycle of depolarization and repolarization of the cell. It has 5 phases (numbered 0-4). Phase 4 is the resting potential of the cell, when no stimulus is applied. The Phase 0 depicts the depolarization stage of the cycle. The maximum rate of depolarization can be calculated by the slope (dV/dt)in this region. In Phases 1 and 2, the influx and outflow of positive ions is balanced out and hence the potential of the cell is maintained. The re-polarization of the cell can be seen in Phase 3.

As the heart cells undergo the depolarization and re-polarization cycle, this

Figure 1.2: Cardiac Action Potential [2]

electrical activity is not confined not only to the heart but is also spread throughout the body through body fluids and tissues by a similar mechanism. The sum of all action potentials generated by all the cells gives a net voltage difference which is known as the ECG wave which is used for diagnosis. The next section discusses the generation of the ECG signal and its various segments vis-a-vis the mechanism described above.

#### 1.2 ECG wave

As discussed in the previous section, the ECG wave is the net total of action potentials of all the cells. Thus the shape of the ECG wave will depend on the direction in which we view the heart and hence the position of the electrodes. In technical terms, the ECG signal is essentially a vector whose value depends on the position of the electrodes (Fig. 1.3).

Fig. 1.4 depicts the ECG wave from various electrode positions. The names of ECG waves signify the position of the electrodes. Their nomenclature standard is outside the scope of discussion for this thesis.

Although there is no fixed shape, each ECG signal can be divided into 5 main

Figure 1.3: ECG signal is a vector quantity [3]

Figure 1.4: ECG signals from different leads [4]

segments viz. P, Q, R, S and T. To gain a better understanding, Fig. 1.5 shows an idealized representation of the ECG signal when the electrodes are positioned on the wrists of the person (position I in Fig. 1.4).

Each segment carries information about the functioning of a specific region of the heart. The P-wave occurs when the atria cells undergo depolarization. The electrical impulse travels from the right atrium to the left atrium. In normal working of the heart, the P-wave would be around 80ms - 100ms duration. The QRS-wave occurs when the ventricular cells undergo depolarization. It is larger in magnitude than the P-wave as the ventricular cells are thicker and larger in mass as compared to those of the atria (as can be seen from Fig. 1.1. The T-wave represents the re-polarization of ventricles. The re-polarization of atria cells coincides with the depolarization of ventricles and hence is masked by the QRS wave.

The duration of each wave and that of the connecting segments gives an insight into the working of the heart, enabling diagnosis. The amplitude and timing characteristics of the ECG signal can be seen in Fig. 1.5. The nominal amplitude of an ECG wave is 1mV, although it can be as high 5mV or as low as 0.1mV in some cases [13], [14].

In the next section, specifications for the design of the read-out system will be discussed.

$\begin{array}{ll} \mbox{P wave } (0.08 - 0.10 \mbox{ s}) & \mbox{QRS } (0.06 - 0.10 \mbox{ s}) \\ \mbox{P-R interval } (0.12 - 0.20 \mbox{ s}) & \mbox{Q-T}_{C} \mbox{ interval } (\leq 0.44 \mbox{ s})^{*} \\ & \mbox{*}\mbox{QT}_{C} = \mbox{QT}_{\sqrt{\text{RR}}} \end{array}$

Figure 1.5: ECG signal [5]

## **1.3 ECG signal characteristics**

Fig. 1.5, lists the nominal time durations of each of the segments of the ECG wave. Medical professionals or computer programs interpret the ECG by studying the deviations from these nominal values. Therefore it is of utmost importance that the ECG read-out system faithfully reproduces the signal. The amount of distortion that can be tolerated depends on two criterion viz. application of the ECG device and the end user of the device.

Usually all the segments of an ECG wave are not of interest. Different applications require interpretation of different segments (Table 1.1). For example, to measure the heart rate, only the R-R timing interval is required. The timing of PQ-segment and ST-segment is not of particular interest in this case. To diagnose arrhythmia, the shape and time duration of the S-wave and ST-segment is important [15]. Thus while designing the read-out system, we have to make sure that the signal content in the frequency band of interest is not affected.

The end user of the ECG readout system determines the amount of noise or distortion that the application can tolerate. For example, the human eye can distinguish distortion smaller than 1%-5% (7-bits of resolution) [16]. Thus if a human person was to interpret an ECG, a read-out system with Total Harmonic Distortion (THD) around 1% would be sufficient whereas in the case of automated signal processing, the specification would be decided by the tolerance of the DSP algorithms that would follow and in general would be much lower. Since the distortion specification is not very clear, in our system, a distortion specification which meets the resolution requirements of the ADC is considered sufficient.

Also, since the requirements of the ECG read-out are heavily application dependent there are no specific standards that an ECG reading device has to adhere to. Although there are a few standards in the IEC (*International Electrotechnical Commission*) and AHA (*American Heart Association*) which are not strictly required to be

| Processing            | Bandwidth (Hz) |

|-----------------------|----------------|

| Display               | 0.5 - 40       |

| QRS detection         | 0.5-40         |

| Arrhythmia detection  | 0.05-60        |

| ST segment monitoring | 0.05-60        |

Table 1.1: A few ECG applications along with the required frequency bandwidth

followed but are used as guidelines by device manufacturers.

AHA recommends that the bandwidth of an ECG device used for standard clinical applications should have a bandwidth of 0.5Hz to 100Hz. IEC 60601 standard states that the input referred noise of any ambulatory ECG device should not be greater than  $30\mu V_{\rm rms}$  [17]. Assuming an input signal of  $1mV_{\rm rms}$ , as per the previous section, the target SNR for most applications is therefore 40dB or 8 bits of resolution.

Other design parameters that are important for any medical device are its input impedance and CMRR. These will be discussed in detail later chapters.

The next section will discuss in detail the device and the application and thus the specifications for the design of the read-out.

#### **1.4** Description of device

Technically, an ECG device requires only two electrodes to read the electrical activity. However, three electrodes are the most common ones because a third electrode is required as a reference electrode, which provides a reference common-mode voltage for the ECG device. It is usually needed to improve the CMRR of the device or reduce the common-mode noise, which is the bottleneck in almost all front-end designs for an ECG device.

As stated in the previous section, the placement of these electrodes will decide the shape of the ECG wave. The more number of electrodes, the more the number of voltage differences, the more elaborate the information and hence better the diagnosis.

Fig. 1.6 shows one of the popular ECG electrode position. Here, the ECG signal is read out as a voltage difference between the electrodes on the left and the right arm and the electrode on the right leg providing the reference. This position is also known as the Einthoven's Triangle, named after the inventor of the first ECG reading device.

Before the electrodes are attached to the body, the skin is prepared by scraping it with sandpaper. This is done to remove the upper dry skin and hence reduce the impedance of the skin. A gel (Ag-AgCl gel) is then applied to facilitate a low impedance

Figure 1.6: Standard 3-electrode position [6]

Figure 1.7: Proposed ECG device

contact with the electrode. This, although helps in obtaining a proper reading of the ECG signal, requires trained clinicians to operate it and also increases patient discomfort.

Hence, there is a need for a recording device using 'dry' electrodes which do not require any skin preparation or trained people to operate the device.

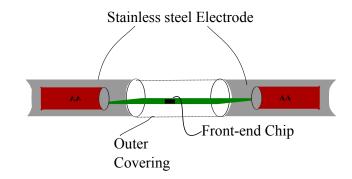

Fig. 1.7 shows a rough diagram of the proposed ECG device. The grip-style 'dry' electrodes shown are made of stainless steel. The basic idea is that the user grips the device with both the hands for the ECG signal to be measured. The device would be powered by 3V (2 AA batteries) each of which would be housed below the electrodes. The integrated front-end chip would be in the middle of the device and would be covered. There is no reference electrode in this device and thus would have different response to interference as compared to conventional ECG devices and thus would require a different front-end design.

## 1.5 Literature study and contribution

A lot of work in literature has been dedicated to designing front-end circuits for ECG devices. Historically, the research work mainly dealt with solving just one problem viz. increasing the CMRR of the instrumentation amplifier. [18], [19], [20] have studied the effects of all possible interferences on an ECG reading and have shown that common-mode interference is the most important of them all. Consequently many techniques and instrumentation amplifiers have been proposed to increase the CMRR of the devices [21], [22], [23], [24]. However, these designs and implementations are for ECG devices in general and no work has been done on the design of hand-held 2-electrode ECG devices specifically.

In this thesis, the effect of all possible interference sources such as power-line noise, baseline wandering, muscle artefacts for the proposed device will be studied. It will be shown that under certain conditions viz. the device is a hand-held portable one, the interference susceptibility of a 2-electrode system is comparable to or might be even superior to that of a traditional ECG device with a reference electrode.

One of the main bottlenecks in the design of an integrated bio-potential read-out front-end, apart from CMRR, is the integration of large time-constants on chip. Implementing a sub-Hz cut-off frequency, to obtain a proper high-pass characteristic, requires time-constants in the order of few seconds. Till now this has been implemented off-chip using resistors and capacitors of a few M $\Omega$ s and  $\mu$ Fs respectively.

Unfortunately, using such resistors and capacitors is not possible when designing an integrated circuit as it would take up an impractical amount of area. One of the most popular techniques for obtaining a large time-constant is by implementing an extremely high resistance by biasing transistors in sub-threshold region [25], [26]. However, their resistance is unpredictable and non-linear [27].

A new technique called mixed-signal feedback feeds back the digital signal to the previous analog stage. [28], [29], [30] use this concept to implement a sub-Hz cut-off frequency. The advantage of such architecture is that since now the cut-off frequency is implemented in the digital domain, a greater degree of control can be obtained over its value and linearity as opposed to pseudo-resistors.

Unfortunately, the mixed-signal feedback techniques presented by these authors are limited to 8 bits of resolution. In this thesis, a mixed-signal feedback technique using a sigma-delta ADC is proposed to increase the resolution to 10 bits.

This circuit will act as a prototype, since we are interested in the feasibility of using a 2-electrode ECG read-out for various applications. Hence, it would be nice if the technical specifications such as frequency and resolution are programmable. However, this thesis deals with possible solutions to the aforementioned challenges. Introducing programmability is trivial and is not presented in this thesis. Table 1.2 summarizes the technical specifications which the read-out circuit has to meet.

| Parameters           | Specification                                 |

|----------------------|-----------------------------------------------|

|                      |                                               |

| Input Amplitude      | $1 \mathrm{m} V_{\mathrm{rms}}$               |

| Bandwidth            | 1Hz-200Hz                                     |

| $\operatorname{SNR}$ | 60dB                                          |

| Distortion           | $\sim 60 \text{dB} (10 \text{ bit accuracy})$ |

| Supply Voltage       | 3V                                            |

| Power consumption    | less than $50\mu W$                           |

| Input Impedance      | $>5M\Omega$                                   |

| CMRR                 | greater than 60dB                             |

| Process Technology   | $0.35 \mu \mathrm{m}$ AMIS I3T25 technology   |

Table 1.2: System specifications

The objective of any sensing or readout system is faithful reproduction of the signal to be measured which is ECG signal in our case (henceforth mentioned only as signal). To achieve this objective, it is necessary that the signal is not modified by the read-out circuitry. Any read-out is generally affected by the following

- Source loading : Considerable signal attenuation will take place at the input of the system, if its input impedance is comparable to or smaller than the impedance of the source (body tissues and electrode). Thus it is important to properly characterize the source impedance and account for it in the design.

- Interference and noise sources: Any undesired signal can be termed as noise. The function of the read-out system is to differentiate between the signal of interest and other signals viz. noise and interference. It is important to understand the type and behaviour of all the interference sources so that they can be eliminated by proper design. Usually, in an ECG read-out, the main sources of interference and noise are coupling of the power-line source, baseline wandering, muscle artefact, instrumentation noise and electrode-skin interface offset. The behaviour of noise sources is affected by the impedance of the body and electrodes too, and hence emphasizing the need to characterize it properly.

- Distortion: Any circuit consisting of non-linear devices such as transistors will add distortion to the input signal. To meet the required resolution, it is important that the distortion components be <60dB than the main signal component.

Section 2.1 discusses the modeling of electrode and body impedances. Section 2.2 studies the effect of existing interference sources and it will be seen that power-line interference is a major concern in traditional ECG systems. It is shown in Section 2.3 that for a hand-held two electrode system, power-line interference can be completely neglected. Reduction of distortion is dependent on the design of the read-out circuit. Techniques to reduce it will be discussed in Chapter 4.

## 2.1 Skin-Electrode Interface

The total source impedance comprises the impedance of body tissues, electrode and the skin-electrode interface. However, the impedance of the skin-electrode interface plays the main role in deciding the total source impedance as the impedance of the metal electrode and that of the body tissues is usually much smaller relatively [31].

The linear relationship between current and voltage as stated by Ohm's law does

Figure 2.1: Skin-electrode impedance vs frequency for two different materials [7]

not hold true at junctions of different materials such as p-n junctions or electrode-skin interfaces. In the metal electrode, electrons are the carrier of electrical current whereas it is ions in the skin/body tissues. Complex chemical reactions decide the current-voltage relationship at the interface. Due to this, the electrode impedance not only varies with the type of metal used and frequency of the signal, but also with time. A by-product of this chemical reaction is presence of a constant DC offset potential of maximally 300mV at the interface [32].

Fig. 2.1 compares the spectral impedance of the dry electrodes made up of different materials [7]. As can be seen the impedance of the electrode can vary upto 20 times depending on the material of the electrode and frequency of operation. Passage of time also leads to change in impedance of the electrodes due to perspiration as can be seen in Fig. 2.2 [33]. The impedance of stainless steel electrodes was monitored for 20 minutes on 10 subjects. It can be seen in most cases, but cannot be generalized, that the impedance decreases as time increases. This is attributed to the fact that sweat accumulates between the electrode and skin interface which leads to increase in concentration of salts and hence increases the conductivity.

Table 2.1 [33], lists the worst-case and average initial impedances of the skinelectrode interface for stainless steel.

Numerous attempts have been made to model the skin-electrode interface. These can be broadly categorized into two categories -

- By obtaining a complex passive-element model of the interface which accurately characterizes the above impedance curves over our desired frequency range.

- Simplify the above model by using only the worst case impedance value.

Figure 2.2: Skin-electrode impedance of stainless-steel vs time for 10 subjects

|                           | Impedance $(k\Omega)$ |

|---------------------------|-----------------------|

| Average Initial Impedance | 381                   |

| Maximum                   | 1000                  |

| Minimum                   | 29                    |

| After 20 mins             |                       |

| Average Impedance         | 85                    |

| Maximum                   | 230                   |

| Minimum                   | 27                    |

Table 2.1: Impedance values for stainless steel dry electrode

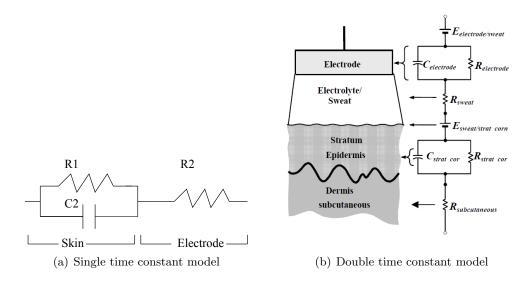

Fig. 2.3(a) depicts a single time-constant model proposed by [34]. The drawback of this model is that it is valid over very small range of frequencies. A double time-constant model proposed by [35], as shown in Fig. 2.3(b), is more accurate. But, this model is not only quite complex but also the resistance and capacitive values will vary from person to person and thus would be inaccurate.

No single model can completely and accurately model the impedance of the interface [7] and might even be futile in our case. This is evident from Fig. 2.1 and Fig. 2.2. The impedance of stainless steel electrodes is almost an order of magnitude different in both the cases. If we consider only the worst-case impedance for our design,

Figure 2.3: Passive models for skin-electrode interface

the only error that it would introduce is that we would be over-designing. This would be a smaller price to pay for than for developing an accurate model. If the input impedance of the system is much greater than the worst-case impedance of interface, the actual impedance value of the interface will not matter and thus can also be modeled as a simple resistor.

For our case, we will also assume that the device will be used for less than one minute and thus the impedance of the interface can be assumed to be constant over this period of time. From Table 2.1, the worst case initial impedance of a stainless-steel dry electrode is 300k $\Omega$ . Assuming an input impedance of at least 10 times than the worst-case impedance i.e. an input impedance of  $\approx 5M\Omega$  will be needed. This is also in-line with the guidelines published by AHA which requires any ECG device to have an input impedance of at least  $2M\Omega$  [36].

## 2.2 Interference sources

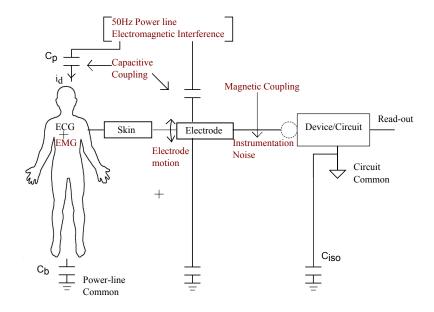

Fig. 2.4 depicts the possible sources of interference and noise that usually affect a conventional ECG read-out [37]. They are discussed below in brief

• Coupling: Power-line noise and electromagnetic interference can be coupled to the device input terminals in three ways [18] viz. capacitive coupling, magnetic coupling and resistive ground coupling.

Resistive ground coupling refers to coupling of the noise signals in the ground leads caused by ground loops, causing a change in the ground potential. This is not applicable in our case as ours is a 2-electrode device and there is no ground lead present. The other 2 leads will be shielded by the electrodes and hence the coupling of noise signals can be neglected. Moreover, their length would be very

Figure 2.4: Main sources of interference in an ECG read-out

small (most probably they would be implemented as PCB traces) as opposed to long leads in traditional ECG systems. For these reasons, effect of resistive ground coupling can be neglected.

Magnetic coupling refers to mutual coupling caused by current flowing in the electrode leads. The amount of coupling depends on the area covered by this loop and shielding. This effect can also be neglected as, once again, the leads would be small and shielded.

Due to capacitive coupling, power-line noise current flowing through the body is usually around  $0.2\mu$ A- $0.5\mu$ A [18], [38]. Other electromagnetic interferences such as tubelight (1kHz), television video signals [18] have known to lead to incorrect signal reproducibility. Capacitive coupling of interferences from the environment into the body increases the common-mode signal amplitude at the input terminals of the device. It will be shown in the next section that for a hand-held device, common-mode current does not flow through the leads and hence does not lead to any common-mode signal. Here too, capacitive coupling of the power-line interference to the leads and the device can be neglected for the same reasons as stated as above.

• Electrode Contact noise and Motion artefact: Motion artefact stems from change in relative position of the heart from the electrodes or in other words, from movement of the electrodes. Since the device is a hand-held one, the user can be in motion. The user may also tighten or loosen his/her grip during the period of the readout. This causes changes in the skin-electrode interface properties and thus its impedance which leads to sudden changes in the DC offset potential or known as electrode contact noise or baseline wandering. These occur at very low frequency, usually < 0.5Hz and can be filtered out.

• EMG noise: EMG noise results from generation of action potentials from muscles other than that of the heart. Tightening and loosening of muscles leads to generation of EMG. Its amplitude can usually be modeled as a Gaussian distribution curve [39] whose standard deviation is generally 10% of ECG signal amplitude. Although there can be cases where contraction of muscles would lead to transient peak voltage greater than the ECG amplitude. The bandwidth of EMG signals ranges from 30Hz-500Hz [39] which means a significant portion of the EMG energy lies in-band within the ECG signal band. Filtering will not help in this case and we will need to resort to digital techniques such as averaging. Implementation of an EMG digital filter is outside the scope of this thesis.

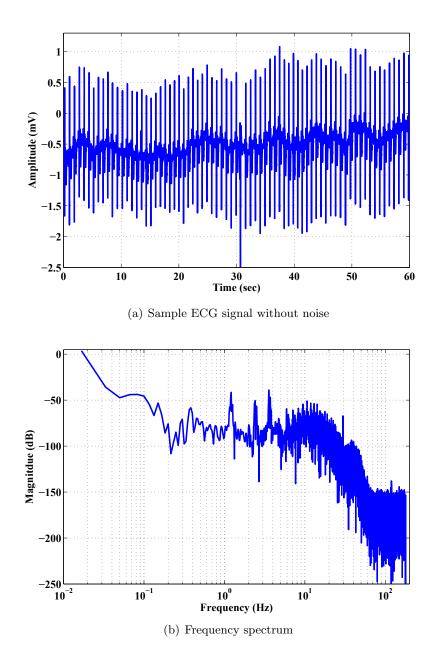

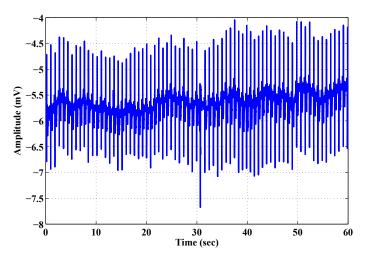

Fig. 2.5(a) and Fig. 2.5(b) plot a sample 'noise-less' ECG signal and its frequency spectrum. Fig. 2.6(b) and Fig. 2.6(c) show the effect of baseline wandering and EMG noise separately on the frequency spectrum. The corresponding timedomain 'noisy' ECG signal is shown in Fig. 2.6(a). As can be seen in Fig. 2.6(b), energy of the signal has increased significantly around 0.1Hz frequency range due to baseline wandering. In Fig. 2.6(c), the energy around 30Hz-50Hz has visibly increased due to EMG noise. All the above signals were obtained from the ECG database available at [40].

• Instrumentation noise: Noise due to the read-out circuitry is termed as instrumentation noise. The device needs to be designed such that it can meet the 10-bit resolution requirement.

In summary, 3 main interference sources need to be accounted for in the design viz. common-mode interference due to capacitive coupling, baseline wandering and instrumentation noise. Baseline wandering can be filtered out by high-pass filtering. The design of the high-pass filter will be discussed in Chapter 3. Design for low instrumentation noise will be discussed in Chapter 4. Response of a 2-electrode system to common-mode noise due to capacitive coupling is discussed in more detail in the next section. Effect of rest of the interference sources can be neglected.

## 2.3 Capacitively-coupled common-mode interference

Fig. 2.4 shows coupling capacitances of the human body to power-line source  $(C_{\rm p})$  and power-line common  $(C_{\rm b})$ . The power-line common is usually referred to as earth ground in literature. In this thesis too, it has been referred to as earth ground.  $i_{\rm d}$  is the current that is capacitively coupled to the body through the power-line source. It is called the displacement current. For our analysis, only capacitive coupling due to power-line source will be considered as it lies within the band of interest. However, the analysis will hold true for any electromagnetic interference and the results derived can be applied to any capacitively coupled interference.

Evaluating the value of  $C_{\rm p}$  and  $C_{\rm b}$  is not trivial as it depends on a variety of

Figure 2.5: Sample ECG signal and its frequency Spectrum

factors such as environment and surroundings, skin properties, distance from power-line source or metallic objects.

Table 2.2 [38] lists the nominal and worst-case values of coupling capacitances and surroundings in which can they be encountered. The corresponding values of the displacement current have been specified in the last column. The experiments carried out by the author is by no means exhaustive. However, the results provide a good

(a) ECG signal with baseline wandering and muscle arterfact

(c) Muscle arterfact frequency spectrum

Figure 2.6: Effect of Baseline wandering and muscle artefact on ECG signal

insight into the nominal coupling capacitance values that one can expect.

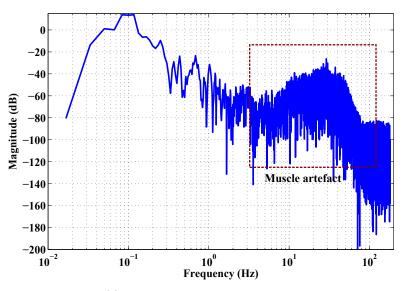

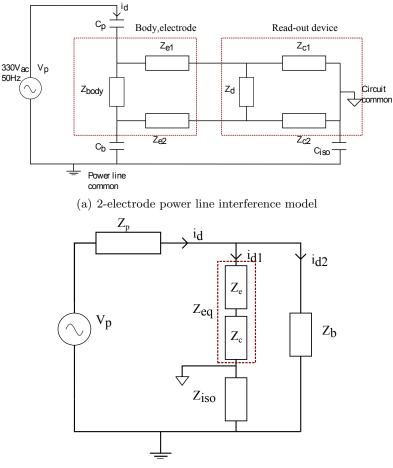

Fig. 2.7(a) depicts an interference model of a 2-electrode hand-held battery oper-

| Location                        | $C_{\mathrm{p}}~(\mathbf{pF})$ | $C_{\mathrm{b}}~(\mathbf{pF})$ | $i_{\rm d}$ (nA) |

|---------------------------------|--------------------------------|--------------------------------|------------------|

| Living room(near metallic lamp) | 2.2                            | 1000                           | 424              |

| Kitchen                         | 1.2                            | 735                            | 229              |

| Bathroom                        | 1                              | 3905                           | 198              |

| Library                         | 0.7                            | 111                            | 127              |

| Far from plugged oscilloscope   | 2                              | 225                            | 565              |

| Touching power cord             | 14                             | 260                            | 2715             |

| Nominal values                  | 2                              | 500                            | 200              |

Table 2.2: Measured values of coupling capacitances in various locations

ated system as presented by [18], [19], [20].  $Z_{\rm d}$  is the differential input impedance of the device and  $Z_{\rm c1}$  and  $Z_{\rm c2}$  are the impedances between the input terminals of the device and the circuit common.  $Z_{\rm e1}$  and  $Z_{\rm e2}$  are the impedances of the skin-electrode interface.

$C_{\rm iso}$ , again, varies from the type of design of the device, its size and the surroundings. Coupling to the electrode leads is neglected once again.

$Z_{body}$  in Fig. 2.7(a) can be neglected by assuming that  $i_d$  is equally distributed across the body and therefore the whole body is at the same potential [19], [18]. It is not possible to estimate the value of  $i_d$  at each point on the body as, like coupling capacitances, it too would be a function of the environment, surrounding, orientation, skin impedance and time duration. There have been no reported cases in literature wherein this assumption is proven to be false. The impact that the failure of this assumption will have on our design is discussed briefly in the last part of this section.

Fig. 2.7(b) shows the equivalent impedance diagram for calculating the commonmode voltage at the input terminals of the device. In this figure both the electrodes and common-mode impedance of both the terminals have been assumed to be equal. That is, the following assumptions have been made

$$Z_{e1} = Z_{e2} = Z_{e}$$

$$Z_{c1} = Z_{c2} = Z_{c}$$

$$Z_{eq} = \frac{Z_e + Z_c}{2}$$

$$Z_{iso} = \frac{1}{s \cdot C_{iso}}$$

$$Z_b = \frac{1}{s \cdot C_b}$$

$$Z_p = \frac{1}{s \cdot C_p}$$

(b) Equivalent impedance for calculating common-mode voltage

Figure 2.7: 2-electrode power-line interference model and its equivalent circuit

Referring to Fig. 2.7(a), the differential input impedance of the device,  $Z_{\text{idiff}}$ , and the common-mode input impedance of the device,  $Z_{\text{icm}}$  are given by

$$Z_{\rm idiff} = Z_{\rm d} / / 2Z_{\rm c} \tag{2.1}$$

$$Z_{\rm icm} = Z_{\rm iso} + \frac{Z_{\rm c}}{2} \tag{2.2}$$

To avoid source-loading,

$$Z_{\text{idiff}} >> Z_{\text{e}}$$

(2.3)

$$Z_{\rm d}, Z_{\rm c} >= 5 {\rm M}\Omega \tag{2.4}$$

$Z_{\text{idiff}}$  is taken to be at least 10 times greater than the worst-case electrode impedance that can be expected. From Fig. 2.7(b), the common-mode voltage due to power-line interference,  $V_{\text{cm}}$ , is

$$V_{\rm cm} \approx \frac{1}{2} \cdot \frac{Z_{\rm c}}{Z_{\rm eq}} \cdot \frac{Z_{\rm eq}}{Z_{\rm eq} + Z_{\rm iso}} \cdot \frac{Z_{\rm b}}{Z_{\rm p} + Z_{\rm b}} \cdot V_{\rm p}$$

$$V_{\rm cm} \approx \frac{1}{500} \frac{Z_{\rm c}}{Z_{\rm eq} + Z_{\rm iso}} \tag{2.5}$$

The term  $\frac{1}{500}$  is obtained by substituting nominal values of  $Z_{\rm p}$  and  $Z_{\rm b}$  from Table 2.2. In the case of a hand-held device and especially in the case wherein the circuit would be an integrated chip (as opposed to a PCB implementation), the coupling of the circuit common to the earth ground will be much smaller than that of the human body and it can be assumed  $C_{\rm iso} \approx 0$  and therefore  $V_{\rm cm} = 0$ .

This can also be understood from (2.2) wherein infinite  $Z_{iso}$  will lead to infinite common-mode impedance and thus no common-mode signal transfer will take place. This result can be compared to the tail current impedance required for a differential amplifier stage. Infinite impedance of the tail current source would lead to infinite CMRR.

(2.5) shows that irrespective of the value of coupling capacitances,  $C_{\rm p}$  and  $C_{\rm b}$ ,  $V_{\rm cm}$  will always be 0 as long as  $Z_{\rm iso} >> Z_{\rm eq}$ . Mismatch between electrode impedances, common-mode impedances of the input terminals of the device will also not matter as long as  $C_{\rm iso}$  is 0.

A brief quantitative calculation is carried out to determine the value of  $C_{\rm iso}$  that can be tolerated for a 10-bit resolution. To obtain the specified resolution,  $V_{\rm cm}$  should be <60dB than the differential signal. For a  $1 \text{m} V_{\rm rms}$  input signal,  $V_{\rm cm} < 1 \mu V_{\rm rms}$ . By substituting these values in (2.5), we get that  $C_{\rm iso} <\approx 1 \text{fF}$ . Given that the nominal coupling capacitance of the human body is 500pF (Table 2.2), we can safely assume that the coupling capacitance of a shielded IC would easily meet this criterion.

To understand why CMRR of the instrumentation amplifier needs to be high for traditional ECG systems, the CMRR of the system can be written as

$$CMRR = \frac{Z_{eq} + Z_{iso}}{500 \cdot Z_c}$$

(2.6)

It is assumed here that  $Z_{\text{idiff}}$  is much greater than the source impedance. To increase the CMRR, one has to either increase  $Z_{\text{iso}}$  or decrease  $Z_{\text{c}}$ . Decreasing  $Z_{\text{c}}$  will also decrease  $Z_{\text{idiff}}$ , which is undesirable and increasing  $Z_{\text{iso}}$  is also a challenge as ECG equipments have been quite large. Hence a third electrode is used as a reference electrode to increase the CMRR. By using the third electrode, CMRR and  $Z_{\text{idiff}}$  both do not depend on  $Z_{\text{c}}$  and the two parameters are essentially decoupled. The CMRR of such systems is then limited by the mismatch between the electrodes.

The only way the common-mode noise will be able to affect our device considerably is if the assumption that the displacement current,  $i_d$ , is symmetric in nature is not valid i.e. different parts of the body have different coupling capacitances. In this case, the common-mode current would flow through the body impedance and manifest itself as a differential voltage. Since this current is at 50Hz frequency, it will be indistinguishable from the signal of interest. A notch filter at 50Hz would be needed to reject it completely, which is better implemented in the digital domain. Thus for designing, we will assume that the coupling capacitances are symmetric and therefore the displacement current in the body too, which will be the case in the majority of scenarios. If it fails for certain cases, a digital notch filter can later be added. Two possible scenarios for the design of the front-end architecture are depicted in Fig. 3.1 and Fig. 3.2. In Fig. 3.1 the signal conditioning is carried out fully in the analog domain whereas in Fig. 3.2 it is carried out completely in the digital domain. The instrumentation

Figure 3.1: Analog Implementation of front-end of readout

Figure 3.2: Digital Implementation of front-end of readout

amplifier is the first block in both the cases as it performs two important functions viz

- Provide a sufficiently high input impedance

- Provide a sufficiently high CMRR

To compare both approaches, Table 3.1 compares the ADCs required in each of the cases in terms of resolution, power, area and cost as ADCs are generally the most power-consuming block in a signal chain.

As only one set of input is needed, as opposed to an array of inputs, area is not a concern for this application. Hence an analog implementation is chosen. Fig 3.3 depicts a standard signal chain of a full analog implementation of a read-out circuit. The main challenge in such an implementation is obtaining the required frequency transfer.

Time-constant,  $\tau$  of a cut-off frequency in general, is given by

$$\tau = \frac{2 \cdot \pi}{f_{\rm c}} = R \cdot C \tag{3.1}$$

where  $f_c = \text{cut-off}$  frequency and R, C are the resistance and capacitance respectively. The high-pass cut-off frequency is much lower than the low-pass one and therefore much more challenging to design for. In this chapter, implementation of the high-pass cut-off frequency will be considered. Implementation of the low-pass cut-off frequency will be discussed in the next chapter.

On-chip capacitors are generally less than few tens of pFs due to area considerations. To obtain the required time-constant of 6.28s (Table 1.2) corresponding

|                     | Full-analog implementa-<br>tion                                                                                                                                       | Full-digital Implementa-<br>tion                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution Required | Assuming that to achieve a 60dB SNR, dynamic range of 10-bits would be required and thus a 12-bit ADC is required taking into account practical implementation issues | Since the input signal to the ADC comes directly from the instrumentation amplifier, the $300 \text{mV}$ DC offset would also be present. Thus a resolution $\approx 22$ -bits will be required to achieve a target SNR of 60dB. |

| Power consumed      | Few tens of microwatts                                                                                                                                                | Much greater than its analog counterpart                                                                                                                                                                                         |

| Area                | Large because huge capaci-<br>tors and resistors would be re-<br>quired to obtain the required<br>bandwidth at such low fre-<br>quencies                              | Much smaller as compared to<br>a full-analog implementation                                                                                                                                                                      |