# Fundamental Frequency Switching Strategies of a Seven-Level Hybrid Cascaded H-Bridge Multilevel Inverter

Zhong Du, Member, IEEE, Leon M. Tolbert, Senior Member, IEEE, Burak Ozpineci, Senior Member, IEEE, and John N. Chiasson, Senior Member, IEEE

Abstract—This paper presents a cascaded H-bridge multilevel inverter that can be implemented using only a single dc power source and capacitors. Standard cascaded multilevel inverters require n dc sources for 2n + 1 levels. Without requiring transformers, the scheme proposed here allows the use of a single dc power source (e.g., a battery or a fuel cell stack) with the remaining n-1 dc sources being capacitors, which is referred to as hybrid cascaded H-bridge multilevel inverter (HCMLI) in this paper. It is shown that the inverter can simultaneously maintain the dc voltage level of the capacitors and choose a fundamental frequency switching pattern to produce a nearly sinusoidal output. HCMLI using only a single dc source for each phase is promising for high-power motor drive applications as it significantly decreases the number of required dc power supplies, provides high-quality output power due to its high number of output levels, and results in high conversion efficiency and low thermal stress as it uses a fundamental frequency switching scheme. This paper mainly discusses control of seven-level HCMLI with fundamental frequency switching control and how its modulation index range can be extended using triplen harmonic compensation.

*Index Terms*—Fundamental frequency modulation control, hybrid cascaded H-bridge multilevel inverter (HCMLI), triplen harmonic compensation.

### I. INTRODUCTION

THE MULTILEVEL inverter is a promising power electronics topology for high-power applications because of its low electromagnetic interference (EMI) and high efficiency with low-switching-frequency control method [1]–[6].

Traditionally, each phase of a cascaded multilevel inverter requires n dc sources for 2n + 1 levels. For many applications, obtaining so many separate dc sources may preclude the use of

Manuscript received December 4, 2007; revised April 8, 2008; accepted August 19, 2008. Current version published February 6, 2009. This work was supported by the University of Tennessee (UT)-Battelle, LLC, under Contract DE-AC05-000R22725 with the U.S. Department of Energy. This paper was presented in part at the Applied Power Electronics Conference and Exposition 2005, Busan, Korea, and in part at the Power Electronics Specialists Conference 2007, Orlando, FL. Recommended for publication by Associate Editor A. Rufer.

Z. Du is with Parker Hannifin Corporation, Olive Branch, MS 38654 USA (e-mail: zhong.du@parker.com).

L. M. Tolbert and B. Ozpineci are with the Power Electronics and Electric Machinery Research Center, National Transportation Research Center, Oak Ridge National Laboratory, Knoxville, TN 37932 USA (e-mail: tolbertlm@ornl.gov; ozpinecib@ornl.gov).

J. N. Chiasson is with the Department of Electrical and Computer Engineering (ECE), Boise State University, Boise, ID 83725 USA (e-mail: johnchiasson@ boisestate.edu).

Digital Object Identifier 10.1109/TPEL.2008.2006678

such an inverter. To reduce the number of dc sources required when the cascaded H-bridge multilevel inverter is applied to a motor drive, a scheme is proposed in this paper that allows the use of a single dc source (such as battery or fuel cell) as the first dc source with the remaining n - 1 dc sources being capacitors in the cascaded H-bridges multilevel inverter, which is referred to as the hybrid cascaded H-bridge multilevel inverter (HCMLI) [7]–[9]. Previous work has shown that pulsewidth modulation (PWM) control can be used on HCMLI [10]. Compared to the traditional cascaded H-bridge multilevel inverter, the proposed HCMLI has a low number of dc sources and retains the lowswitching-frequency advantage.

The authors have been working on the multilevel inverter harmonic elimination control technologies based on harmonic elimination mathematics theory, and present several findings, such as complete switching angle solution technology and active harmonic elimination technology. The seven-level multilevel inverter fundamental frequency harmonic elimination method and triplen harmonic injection for modulation index extension method have been published in previous papers. All the technologies published in the previous papers can be applied to normal multilevel inverters to satisfy different application requirements.

However, the published technologies cannot be directly applied to HCMLI as the capacitors are not dc sources. The control goal of the HCMLI needs to maintain the balance of the dc voltage level of the capacitors while producing a nearly sinusoidal three-phase output voltage using a low-switchingfrequency harmonic elimination method. This paper focuses on how to apply the seven-level fundamental frequency harmonic elimination method to HCMLI and extend its modulation index range, and presents new findings on HCLMI control other than normal cascaded H-bridge multilevel inverters.

#### II. WORKING PRINCIPLE OF HCLMI

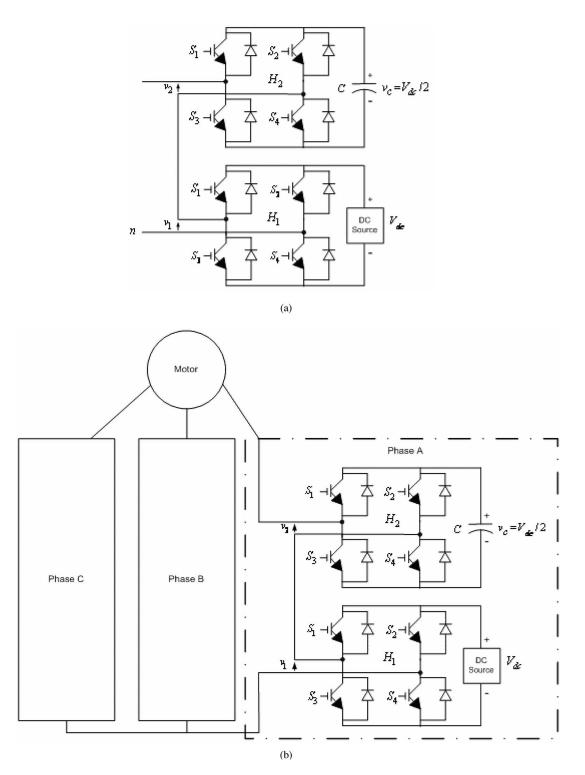

To operate a cascaded multilevel inverter using a single dc source, capacitors are used as the dc sources for all but the first source. To explain, consider a cascaded multilevel inverter with two H-bridges as shown in Fig. 1. The dc source for the first H-bridge (H<sub>1</sub>) is a battery or fuel cell with an output voltage of  $V_{dc}$ , while the dc source for the second H-bridge (H<sub>2</sub>) is a capacitor whose voltage is to be held at  $V_c$ . The output voltage of the first H-bridge is denoted by  $v_1$  and the output of the second H-bridge is denoted by  $v_2$  so that the output voltage of

Fig. 1. Topology of the proposed multilevel inverter with a single dc source for first level and capacitors for other levels. (a) Single-phase topology. (b) Three-phase topology.

the cascaded multilevel inverter is

$$v(t) = v_1(t) + v_2(t).$$

(1)

By opening and closing the switches of H<sub>1</sub> appropriately, the output voltage  $v_1$  can be made equal to  $-V_{dc}$ , 0, or  $V_{dc}$ , while similarly the output voltage of H<sub>2</sub> can be made equal to  $-V_c$ , 0, or  $V_c$  by opening and closing its switches appropriately. Therefore, the output voltage of the inverter can have the values  $-(V_{dc} + V_c), -V_{dc}, -(V_{dc} - V_c), -V_c, 0, V_c, (V_{dc} - V_c), V_{dc},$  and  $(V_{dc} + V_c)$ , which constitute nine possible output levels.

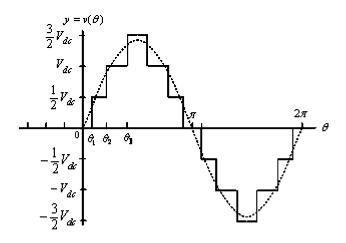

To balance the capacitor's voltage, not all the possible voltage levels must be used in a cycle. A simple seven-level output voltage case  $-3V_{\rm dc}/2$ ,  $-V_{\rm dc}$ ,  $-V_{\rm dc}/2$ , 0,  $V_{\rm dc}/2$ ,  $V_{\rm dc}$ ,  $3V_{\rm dc}/2$  can be designed, as shown in Fig. 2, when the capacitor's voltage

Fig. 2. Seven-level equal step output-voltage waveform.

TABLE I

OUTPUT VOLTAGES FOR A SEVEN-LEVEL INVERTER

| θ                                 | $v_1$           | <i>v</i> <sub>2</sub> | $v = v_1 + v_2$     |

|-----------------------------------|-----------------|-----------------------|---------------------|

| $0 \le \theta < \theta_1$         | 0               | 0                     | 0                   |

| $\theta_1 \leq \theta < \theta_2$ | 0               | $V_{dc}/2$            | V <sub>dc</sub> /2  |

| $\theta_1 \leq \theta < \theta_2$ | V <sub>dc</sub> | -V <sub>dc</sub> /2   | V <sub>dc</sub> /2  |

| $\theta_2 \leq \theta < \theta_3$ | V <sub>dc</sub> | 0                     | $V_{dc}$            |

| $\theta_3 \leq \theta < \pi/2$    | V <sub>dc</sub> | V <sub>dc</sub> /2    | 3V <sub>dc</sub> /2 |

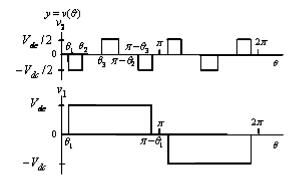

Fig. 3. H-bridge voltages  $v_1$  and  $v_2$  control for  $\theta_1 \leq \theta < \theta_2$ ,  $v_1 = V_{dc}$  and  $v_2 = -V_{dc}/2$ .

$V_c$  is chosen as  $V_{dc}/2$ . Table I shows how a waveform can be generated using the topology of Fig. 1.

Fig. 3 shows how the waveform of Fig. 2 is generated if for  $\theta_1 \leq \theta < \theta_2$ ,  $v_1 = V_{dc}$  and  $v_2 = -V_{dc}/2$  are chosen. Similarly, Fig. 4 shows how the waveform of Fig. 2 is generated if for  $\theta_1 \leq \theta < \theta_2$ ,  $v_1 = 0$  and  $v_2 = V_{dc}/2$  is chosen. The fact that the output-voltage level  $V_{dc}/2$  can be achieved in two different ways is exploited to keep the capacitor voltage regulated. Specifically, one measures the capacitor voltage  $v_c$  and the inverter current *i*. Then, if  $v_c < V_{dc}/2$  and i > 0, one sets  $v_1 = V_{dc}$  and  $v_2 = -V_{dc}/2$ , and the capacitor is being charged. Table II summarizes this case along with the discharge case  $v_c > V_{dc}/2$ .

By choosing the nominal value of the capacitor voltage to be one-half that of the dc source, the values of the levels are equal; however, this is not strictly required. The criteria for this capacitor balancing scheme is that: 1) the capacitance value is

Fig. 4. H-bridge voltages  $v_1$  and  $v_2$  control for  $\theta_1 \leq \theta < \theta_2$ ,  $v_1 = 0$  and  $v_2 = V_{dc}/2$ .

TABLE II Controller for Capacitor Voltage Level

| System State              | $v_1$    | <i>v</i> <sub>2</sub> | $v = v_1 + v_2$    | Capacitor State |

|---------------------------|----------|-----------------------|--------------------|-----------------|

| $v_c < V_{dc}/2, i > 0$   | $V_{dc}$ | -V <sub>dc</sub> /2   | V <sub>dc</sub> /2 | Charging        |

| $v_{c} < V_{dc}/2, i < 0$ | 0        | $V_{dc}/2$            | V <sub>dc</sub> /2 | Charging        |

| $v_c > V_{dc}/2, i > 0$   | 0        | $V_{dc}/2$            | V <sub>dc</sub> /2 | Discharging     |

| $v_c > V_{dc}/2, i < 0$   | $V_{dc}$ | -V <sub>dc</sub> /2   | $V_{dc}/2$         | Discharging     |

chosen large enough so that the variation of its voltage around its nominal value is small (generally speaking, one can choose the capacitor–load time constant to be ten times than that of the fundamental period); and 2) the capacitor charging energy is greater than or equal to the capacitor discharge energy in a cycle.

#### III. MODULATION CONTROL

Generally, traditional PWM control methods and space vector PWM methods are applied to multilevel-inverter modulation control [15]–[27]. These methods will cause extra losses due to high switching frequencies. For this reason, low-switchingfrequency control methods, such as selective harmonic elimination method [11]–[14], [28]–[34], fundamental frequency switching method [11], [14], or active harmonic elimination method, can be used for the HCMLI control [13]. Here, fundamental frequency method is used.

The Fourier series expansion of the seven-level equal step output voltage waveform shown in Fig. 2 is

$$V(\omega t) = \sum_{n=1,3,5...}^{\infty} \frac{2V_{\rm dc}}{n\pi} (\cos(n\theta_1) + \cos(n\theta_2) + \cos(n\theta_3)) \sin(n\omega t)$$

(2)

where *n* is the harmonic number of the output voltage of the multilevel inverter. Ideally, given a desired fundamental voltage  $V_1$ , one wants to determine the switching angles  $\theta_1, \theta_2$ , and  $\theta_3$  so that  $V(\omega t) = V_1 \sin(\omega t)$ , and specific higher harmonics of  $V(n\omega t)$  are eliminated. For three-phase inverter applications, the triplen harmonics in each phase need not be canceled as they automatically cancel in the line-to-line voltages. In this paper, the goal is to achieve the fundamental and eliminate the fifth and seventh harmonics. Using (2), this can be formulated

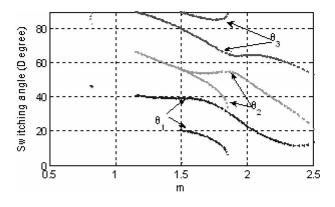

Fig. 5. Solution of switching angles for seven-level multilevel converter.

as the solution to the following equations:

$$\cos(\theta_1) + \cos(\theta_2) + \cos(\theta_3) = m$$

$$\cos(5\theta_1) + \cos(5\theta_2) + \cos(5\theta_3) = 0$$

$$\cos(7\theta_1) + \cos(7\theta_2) + \cos(7\theta_3) = 0.$$

(3)

This is a system of three transcendental equations in the three unknowns  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$ . There are many ways one can solve for the angles. Here, the resultant method [31], [32] is used to find all the switching angles that are shown in Fig. 5 [31], and the modulation index m is defined in this paper as

$$m = \frac{V_1}{(4/\pi_1)(V_{\rm dc}/2)}.$$

(4)

#### IV. CONDITIONS OF CAPACITOR VOLTAGE BALANCE CONTROL

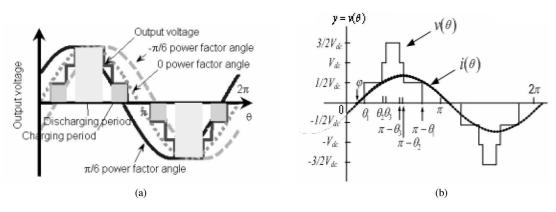

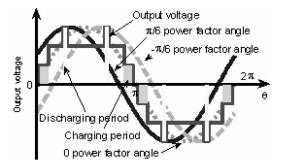

We now show the ability to balance the capacitor voltage, which is related to the modulation index and the load power factor angle. To explain, Fig. 6 shows the voltage waveform and three current waveforms corresponding power factor angles  $-\pi/6$ , 0, and  $\pi/6$ .

To analyze the voltage balance situation due to capacitor charging and discharging in detail, a power factor angle  $\varphi$  shown in Fig. 6(b) is used. Here, charging amount is defined as

$$Q_{\rm charging} = \int_0^{2\pi} I_{\rm charging} \, d\theta \tag{5}$$

and discharging amount is defined as

$$Q_{\rm discharging} = \int_0^{2\pi} I_{\rm discharging} \ d\theta. \tag{6}$$

Then, in a whole cycle, the net accumulation charge amount is

$$Q_{\rm accumulation} = Q_{\rm charging} - Q_{\rm discharging}.$$

(7)

Therefore, to achieve capacitor voltage regulation, the net accumulation amount must be greater than zero in a whole cycle. As the capacitor charging is restricted by the switching angles and time periods of the output voltage waveform, the key control issue is to charge the capacitor as much as possible. Applying fundamental frequency switching angles to (5)–(7), and assuming the power factor angle is  $\varphi$ , as shown in Fig. 6(b), and the load current is

$$i_{\text{load}} = I \sin{(\theta - \varphi)}.$$

(8)

The capacitors' voltage balance condition is

$$Q_{\text{accumulation}} = \int_{\theta_1}^{\theta_2} |I\sin(\theta - \varphi)| d\theta + \int_{\pi - \theta_2}^{\pi - \theta_1} |I\sin(\theta - \varphi)| d\theta$$

$$- \int_{\theta_3}^{\pi - \theta_3} |I\sin(\theta - \varphi)| d\theta \ge 0.$$

(9)

To implement (9), a current sensor is needed to detect the current direction and use it for the switching control. For practical applications, a current sensor is not desired. Therefore, the capacitors' voltage balance condition becomes

$$Q_{\text{accumulation}} = \int_{\theta_1}^{\theta_2} I \sin(\theta - \varphi) d\theta + \int_{\pi - \theta_2}^{\pi - \theta_1} I \sin(\theta - \varphi) d\theta - \int_{\theta_3}^{\pi - \theta_3} I \sin(\theta - \varphi) d\theta \ge 0.$$

(10)

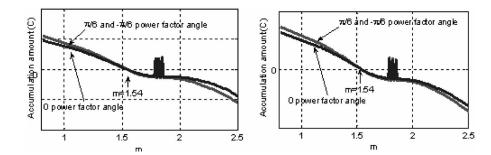

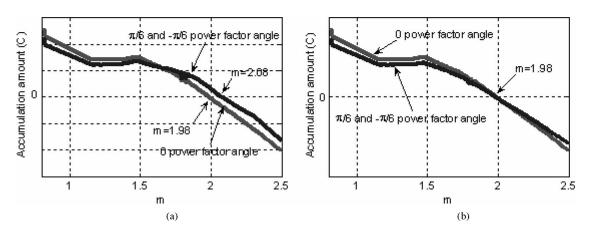

Based on the aforementioned analysis, numerical computation was performed by using switching angles shown in Fig. 5. The net accumulation amounts of power factor angles 0 and  $\pm \pi/6$  are calculated for the seven-level output voltage case, and the accumulation curves with and without current direction control are shown in Fig. 7(a) and (b). From (9) and (10), it can be expected that the amount of accumulation is proportional to the load current, but the accumulation curve shape is unique for any load current. For this reason, Fig. 7 shows the curve shape for all the load current (y-axis does not mark any value). For both cases, the highest modulation index that can balance the capacitor's voltage is around 1.54. It means that for high modulation indexes above 1.54, the discharging amount is greater than the charging amount, which results in the inability to regulate the capacitor's voltage. For practical applications, this modulation index range is somewhat narrow. An improved method is needed to extend the modulation index range.

Fig. 7(a) and (b) shows cases for power factor angle cases  $-\pi/6$ , 0, and  $\pi/6$ . All of their balance points are m = 1.54, and  $\pm \pi/6$  curves are overlapped. If the absolute value of the power factor angle is between 0 and  $\pi/6$ , the curve lies between 0 and  $\pm \pi/6$  curves. It can also be seen that there are some spikes in the curves. This is because the switching angles shown in Fig. 5 are not continuous for these points. The accumulation amount is decreasing when the modulation index is increasing; this is because the charging period is decreasing and discharging period is increasing.

## V. MODULATION INDEX EXTENSION CONTROL BY INJECTING TRIPLEN HARMONICS

The key point of the capacitor voltage balance control at high modulation index is to increase the charging time and decrease the discharging time. To do this, triplen harmonic voltage injection method is proposed. The triplen harmonic voltage is a

Fig. 6. (a) Capacitor charging and discharging time with different power factor angles. (b) Load current with power factor  $\varphi$ .

Fig. 7. Accumulation curve without triplen harmonic voltage compensation. (a) With current direction detection. (b) Without current direction detection.

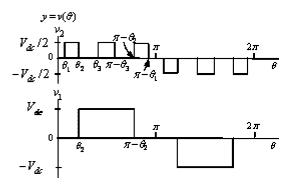

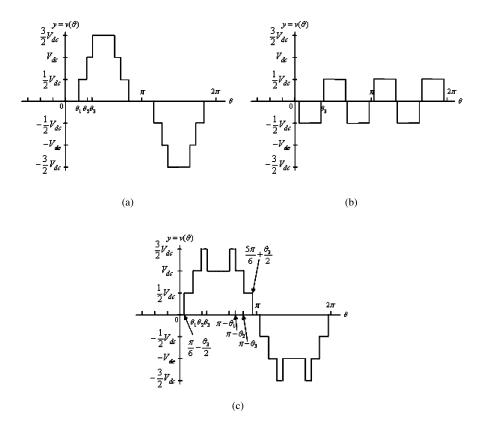

square wave with a frequency equal to three times the fundamental frequency with amplitude of  $V_{\rm dc}/2$ . The triplen harmonic shown in Fig. 8(b) can be represented by

$$V_{\rm tri}(\omega t) = \sum_{n=1,3,5\dots}^{\infty} \frac{2V_{\rm dc}}{n\pi} \cos(n\theta_3) \sin(3n\omega t) \tag{11}$$

and is injected into the original seven-level output voltage shown in Fig. 8(a) to obtain an output voltage waveform shown in Fig. 8(c). The triplen harmonic voltages will automatically cancel in the line–line voltages of three-phase systems, and will not change the fundamental frequency contents [9]. The only effect is to change the charging period and discharging period. The charging and discharging times with triplen harmonic injection are shown in Fig. 9. From Fig. 9, it can be seen that the original long discharging period has been changed into two short discharging periods.

The capacitor's voltage balance conditions with and without current direction detection are now (12) and (13), respectively

$$Q_{\text{accumulation}} = \int_{\frac{\pi}{6} - \frac{\theta_3}{2}}^{\theta_1} |I \sin(\theta - \varphi)| d\theta$$

$$+ \int_{\pi - \theta_1}^{\frac{5\pi}{6} + \frac{\theta_3}{2}} |I \sin(\theta - \varphi)| d\theta$$

$$- \int_{\theta_2}^{\theta_3} |I \sin(\theta - \varphi)| d\theta$$

$$- \int_{\pi - \theta_3}^{\pi - \theta_2} |I \sin(\theta - \varphi)| d\theta \ge 0 \quad (12)$$

$$Q_{\text{accumulation}} = \int_{\frac{\pi}{6} - \frac{\theta_3}{2}}^{\theta_1} I \sin(\theta - \varphi) d\theta + \int_{\pi - \theta_1}^{\frac{5\pi}{6} + \frac{\theta_3}{2}} I \sin(\theta - \varphi) d\theta - \int_{\theta_2}^{\theta_3} I \sin(\theta - \varphi) d\theta - \int_{\pi - \theta_3}^{\pi - \theta_2} I \sin(\theta - \varphi) d\theta \ge 0.$$

(13)

If triplen harmonic voltage compensation method is used, the accumulation curve, using switching angles shown in Fig. 5 based on (12) and (13), is shown in Fig. 10. If current direction control is used, the highest possible modulation index while still balancing the capacitor's voltage is 1.98 for a power factor angle 0 and 2.08 for power factor angles  $\pm \pi/6$ , which are shown in Fig. 10(a). If current direction detection is not used, the highest possible modulation index while still balancing the capacitor's voltage is 1.98 for power factor angles 0 and  $\pm \pi/6$ , which are shown in Fig. 10(a). If current direction detection is not used, the highest possible modulation index while still balancing the capacitor's voltage is 1.98 for power factor angles 0 and  $\pm \pi/6$ , which are shown in Fig. 10(b). If the absolute value of the power factor angle is between 0 and  $\pi/6$ , the curve will lie between the two curves of 0 and  $\pm \pi/6$ .

Similar to the seven-level without triplen harmonic case, from (12) and (13), it can be expected that the amount of accumulation is proportional to the load current, but the accumulation curve shape is unique for any load current. For this reason, Fig. 10 shows the curve shape for all the load current (*y*-axis does not mark any value). Comparing the accumulation curves of

Fig. 8. Output voltage waveform with triplen harmonic compensation. (a) Original seven-level output waveform. (b) Injected triplen square wave. (c) Final output waveform.

Fig. 9. Capacitor charging and discharging time with different power factor angles with triplen harmonic voltage compensation.

Fig. 10(a) and (b), it is observed that the current direction control does not affect the modulation index range too much.

Comparing Fig. 10 to Fig. 7, it is observed that a modulation index of at least 1.98 can be achieved using triplen harmonic compensation while also keeping the capacitor regulated. Compared to 1.54 without triplen harmonic compensation, this is a 33% extension.

# VI. EXPERIMENTAL RESULTS

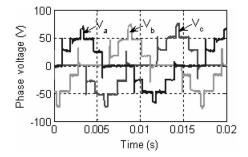

To experimentally validate the proposed HCMLI with sevenlevel equal-step output-voltage-modulation control scheme, a prototype three-phase-cascaded H-bridge multilevel inverter has been built using MOSFETs as the switching devices. Three dc power supplies (one for each phase) feed the inverter. A real-time variable output voltage, variable-frequency three-phase inverter controller based on Altera FLEX 10K field-programmable gate array (FPGA) is used to implement the control algorithm.

To maintain the capacitor's voltage balance, a comparator using an operational amplifier is used to detect the capacitor's voltage and feed the voltage signal into the FPGA controller. A 1-hp induction motor is connected to the motor drive as its load. In the experimental implementation, the capacitors' voltages are regulated to  $V_{\rm dc}/2 = 24$  V. As discussed previously, the current direction control will not affect the modulation index range too much. Current direction signal is not used for the capacitor's voltage balance control in the experiments.

## A. Fundamental Frequency Modulation Control Without Triplen Harmonic Compensation

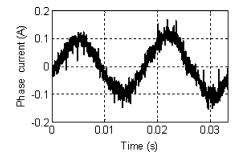

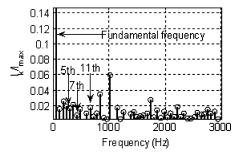

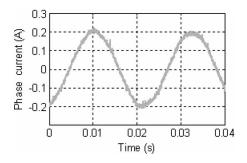

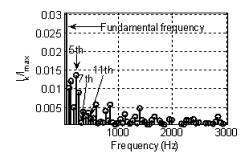

For voltage balance control without triplen harmonic compensation method, the modulation index m = 1.32 and stator frequency f = 60 Hz are chosen for the experiment. Fig. 11 shows the output phase voltage waveform, and Fig. 12 shows the corresponding normalized fast Fourier transform (FFT) spectrum of the line–line voltage. The phase current waveform is shown in Fig. 13, and Fig. 14 shows the corresponding normalized FFT spectrum of the phase current. The current harmonics are less than the corresponding voltage harmonics as the stator inductance of the induction motor acts as a low-pass filter.

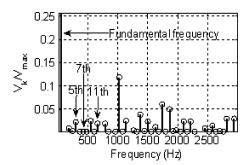

From the voltage spectrum distribution in Fig. 12, it is seen that the fifth and seventh harmonic voltages are nearly zero, and the triplen harmonic voltages (such as the third, ninth, etc.) are

Fig. 10. Accumulation curve with triplen harmonic voltage compensation. (a) With current direction control. (b) Without current direction control.

Fig. 11. Output phase voltage waveform for m = 1.32, f = 60 Hz.

Fig. 12. Normalized FFT analysis of line–line voltage for m = 1.32, f = 60 Hz.

also very low. From the current spectrum distribution shown in Fig. 14, it is seen that it has very low fifth or seventh current harmonics, and very low triplen current harmonics. Also, the simulation shows that the 11th harmonic is 1.68%, and the experimental 11th harmonic shown in Fig. 12 is 2%. The simulation result matches the experimental result very well.

## B. Fundamental Frequency Modulation Control With Triplen Harmonic Compensation

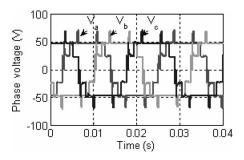

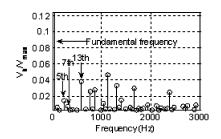

For voltage balance control using the triplen harmonic compensation method, the modulation index m = 1.97 and stator frequency f = 45 Hz are chosen for the experiment. Fig. 15 shows the output phase voltage waveform, while Fig. 16 shows the corresponding normalized FFT spectrum of the line–line voltage. The phase current waveform is shown in Fig. 17, and

Fig. 13. Output current waveform for m = 1.32, f = 60 Hz.

Fig. 14. Normalized FFT analysis of phase current for m = 1.32, f = 60 Hz.

Fig. 15. Output phase voltage waveform for m = 1.97, f = 45 Hz.

Fig. 18 shows the corresponding normalized FFT spectrum of the phase current.

It can be observed that the capacitor's voltage is regulated at 24 V, which is half of the dc source voltage.

Fig. 16. Normalized FFT analysis of line–line voltage for m = 1.97, f = 45 Hz.

Fig. 17. Output current waveform for m = 1.97, f = 45 Hz.

Fig. 18. Normalized FFT analysis of phase current for m = 1.97, f = 45 Hz.

From the voltage spectrum distribution in Fig. 16, it is seen that the fifth and seventh harmonic voltages are nearly zero, and the triplen harmonic voltages (such as the third, ninth, etc.) are also very low. From the current spectrum distribution shown in Fig. 18, it is seen that it has low fifth or seventh current harmonics, as well as low triplen current harmonics. Again the current harmonics are less than the corresponding voltage harmonics as the stator inductance of the induction motor acts as a low-pass filter. Also, the simulation shows that the 13th harmonic is 3.4%, and the experimental 13th harmonic shown in Fig. 16 is 3.8%. The simulation result matches the experimental result very well.

It is also observed that for modulation index in the range 1.54– 1.97, the seven-level output voltage waveform with triplen harmonic compensation can balance the capacitors' voltages. However, the seven-level output voltage waveform without triplen harmonic compensation is unable to balance the capacitors' voltages.

In theory, the capacitor voltage balance can reach modulation index m = 1.98. However, in the actual experiments, due to the switching loss, conduction loss of the switching devices, and the wire copper loss of the circuit, the modulation index for capacitor's voltage balance is seen to be slightly less than 1.98. This is observed through experiments that the capacitor's voltage is maintained at a lower voltage than the desired  $V_{\rm dc}/2$  if the modulation index is 1.98.

## VII. CONCLUSION

This paper proposed an HCMLI that uses only one power source for each phase while producing desired multilevel voltage waveforms. A fundamental frequency switching control algorithm was developed, and a triplen harmonic compensation method was also developed to extend the modulation index range for which the capacitor voltage can be regulated. Simulation and experiments were performed to show the proposed method work in practice.

#### REFERENCES

- L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," *IEEE Trans. Ind. Appl.*, vol. 35, no. 1, pp. 36–44, Jan./Feb. 1999.

- [2] J. S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, May/Jun. 1996.

- [3] J. Rodríguez, J. Lai, and F. Peng, "Multilevel inverters: A survey of topologies, controls and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [4] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [5] P. Hammond, "A new approach to enhance power quality for medium voltage ac drives," *IEEE Trans. Ind. Appl.*, vol. 33, no. 1, pp. 202–208, Jan./Feb. 1997.

- [6] W. A. Hill and C. D. Harbourt, "Performance of medium voltage multilevel inverters," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting*, Phoenix, AZ, Oct. 1999, pp. 1186–1192.

- [7] Z. Du, L. M. Tolbert, J. N. Chiasson, B. Ozpineci, H. Li, and A. Q. Huang, "Hybrid cascaded H-bridges multilevel motor drive control for electric vehicles," in *Proc. IEEE Power Electron. Spec. Conf.*, Jeju, Korea, Jun. 18–22, 2006, pp. 1–6.

- [8] Z. Du, L. M. Tolbert, and J. N. Chiasson, "A cascade multilevel inverter using a single fuel cell DC source," in *Proc. IEEE Appl. Power Electron. Conf.*, Dallas, TX, Mar. 19–23, 2006, vol. 1, pp. 419–423.

- [9] Z. Du, B. Ozpineci, and L. M. Tolbert, "Modulation extension control of hybrid cascaded H-bridge multilevel converters with 7-level fundamental frequency switching scheme," in *Proc. IEEE Power Electron. Spec. Conf.*, Tampa, FL, Jun. 17–21, 2007, pp. 2361–2366.

- [10] K. A. Corzine, F. A. Hardrick, and Y. L. Familiant, "A cascaded multi-level H-bridge inverter utilizing capacitor voltages sources," in *Proc. IASTED Int. Conf. Power Energy Syst.*, Palm Springs, CA, Feb. 24–26, 2003, pp. 290–295.

- [11] J. N. Chiasson, L. M. Tolbert, K. J. McKenzie, and Z. Du, "Control of a multilevel converter using resultant theory," *IEEE Trans. Control Syst. Technol.*, vol. 11, no. 3, pp. 345–354, May 2003.

- [12] J. N. Chiasson, L. M. Tolbert, K. J. McKenzie, and Z. Du, "A new approach to solving the harmonic elimination equations for a multilevel converter," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting*, Salt Lake City, UT, Oct. 12–16, 2003, pp. 640–645.

- [13] Z. Du, L. M. Tolbert, and J. N. Chiasson, "Active harmonic elimination for multilevel converters," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 459–469, Mar. 2006.

- [14] Z. Du, L. M. Tolbert, and J. N. Chiasson, "Modulation extension control for multilevel converters using triplen harmonic injection with low switching frequency," in *Proc. IEEE Appl. Power Electron. Conf.*, Austin, TX, Mar. 6–10, 2004, pp. 419–423.

- [15] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel PWM methods at low modulation indices," *IEEE Trans. Power Electron.*, vol. 15, no. 4, pp. 719–725, Jul. 2000.

- [16] A. Shukla, A. Ghosh, and A. Joshi, "Improved multilevel hysteresis current regulation and capacitor voltage balancing schemes for flying capacitor multilevel inverter," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 518– 529, Mar. 2008.

- [17] B. P. McGrath and D. G. Holmes, "Analytical modelling of voltage balance dynamics for a flying capacitor multilevel converter," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 543–550, Mar. 2008.

- [18] L. M. Tolbert and T. G. Habetler, "Novel multilevel inverter carrier-based PWM method," *IEEE Trans. Ind. Appl.*, vol. 35, no. 5, pp. 1098–1107, Sep./Oct. 1999.

- [19] J. Vassallo, J. C. Clare, and P. W. Wheeler, "A power-equalized harmonicelimination scheme for utility-connected cascaded *H*-bridge multilevel converters," in *Proc. IEEE Ind. Electron. Soc. Annu. Conf.*, Nov. 2–6, 2003, pp. 1185–1190.

- [20] S. Sirisukprasert, J.-S. Lai, and T.-H. Liu, "Optimum harmonic reduction with a wide range of modulation indexes for multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 875–881, Aug. 2002.

- [21] P. C. Loh, D. G. Holmes, and T. A. Lipo, "Implementation and control of distributed PWM cascaded multilevel inverters with minimum harmonic distortion and common-mode voltages," *IEEE Trans. Power Electron.*, vol. 20, no. 1, pp. 90–99, Jan. 2005.

- [22] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 178–185, Jan. 2007.

- [23] W. Yao, H. Hu, and Z. Lu, "Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 45–51, Jan. 2008.

- [24] S. Kouro, P. Lezana, M. Angulo, and J. Rodriguez, "Multicarrier PWM with DC-link ripple feedforward compensation for multilevel inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 52–59, Jan. 2008.

- [25] A. K. Gupta and A. M. Khambadkone, "A space vector modulation scheme to reduce common mode voltage for cascaded multilevel inverters," *IEEE Trans. Power Electron.*, vol. 22, no. 5, pp. 1672–1681, Sep. 2007.

- [26] S. Lu and K. A. Corzine, "Advanced control and analysis of cascaded multilevel converters based on *P–Q* compensation," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1242–1252, Jul. 2007.

- [27] S. Khomfoi and L. M. Tolbert, "Fault diagnostic system for a multilevel inverter using a neural network," *IEEE Trans. Power Electron.*, vol. 22, no. 3, pp. 1062–1069, May 2007.

- [28] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thyristor inverters: Part I—Harmonic elimination," *IEEE Trans. Ind. Appl.*, vol. IA-9, no. 3, pp. 310–317, May/Jun. 1973.

- [29] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thyristor inverters: Part II—Voltage control technique," *IEEE Trans. Ind. Appl.*, vol. IA-10, no. 5, pp. 666–673, Sep./Oct. 1974.

- [30] P. N. Enjeti, P. D. Ziogas, and J. F. Lindsay, "Programmed PWM techniques to eliminate harmonics: A critical evaluation," *IEEE Trans. Ind. Appl.*, vol. 26, no. 2, pp. 302–316, Mar./Apr. 1990.

- [31] T. Kato, "Sequential homotopy-based computation of multiple solutions for selected harmonic elimination in PWM inverters," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 46, no. 5, pp. 586–593, May 1999.

- [32] V. Blasko, "A novel method for selective harmonic elimination in power electronic equipment," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 223–228, Jan. 2007.

- [33] J. R. Wells, X. Geng, P. L. Chapman, P. T. Krein, and B. M. Nee, "Modulation-based harmonic elimination," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 336–340, Jan. 2007.

- [34] V. G. Agelidis, A. I. Balouktsis, and M. S. A. Dahidah, "A five-level symmetrically defined selective harmonic elimination PWM strategy: Analysis and experimental validation," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 19–26, Jan. 2008.

**Zhong Du** (S'01–M'05) received the B.S. degree in process automation instrumentation and the M.S. degree in power machinery and engineering from Tsinghua University, Bejing, China, in 1996 and 1999, respectively, and the Ph.D. degree in electrical engineering from the University of Tennessee, Knoxville, in 2005.

Since 2007, he has been with Parker Hannifin Corporation, Olive Branch, MS, where he works on hybrid diesel trucks. He was a Research Associate with the National Transportation Research Center,

Oak Ridge National Laboratory, Oak Ridge, TN, and a Research Assistant Professor at North Carolina State University, Raleigh. His current research interests include hybrid vehicles, utility power electronics systems, and distributed energy systems.

Leon M. Tolbert (S'89–M'91–SM'98) received the B.E.E., M.S., and Ph.D. degrees in electrical engineering from Georgia Institute of Technology, Atlanta, in 1989, 1991, and 1999, respectively.

In 1991, he joined the Engineering Division, Lockheed Martin Energy Systems, where worked on several electrical distribution projects at the three U.S. Department of Energy Plants, Oak Ridge, TN. In 1997, he became a Research Engineer in the Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory (ORNL), Oak Ridge,

where he is also an Adjunct Participant and conducts joint research at the National Transportation Research Center (NTRC). Since 1999, he has been an Associate Professor in the Department of Electrical and Computer Engineering, University of Tennessee, Knoxville. His current research interests include the areas of electric power conversion for distributed energy sources, motor drives, multilevel converters, hybrid electric vehicles, and application of SiC power electronics.

Prof. Tolbert is a Registered Professional Engineer in the State of Tennessee. From 2003 to 2006, he was the Coordinator of special activities for the Industrial Power Converter Committee of the Industry Applications Society (IAS). He was the recipient of the 2001 IAS Outstanding Young Member Award. From 2003 to 2007, he was the Chair of the Education Activities Committee of the IEEE Power Electronics Society. From 2003 to 2006, he was an Associate Editor of the IEEE POWER ELECTRONICS LETTERS. He is an Associate Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS.

**Burak Ozpineci** (S'92–M'02–SM'05) received the B.S. degree in electrical engineering from Middle East Technical University, Ankara, Turkey, in 1994, and the M.S. and Ph.D. degrees in electrical engineering from the University of Tennessee (UT), Knoxville, in 1998 and 2002, respectively.

In 2001, he joined the Postmasters Program in the Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory (ORNL), Knoxville, TN, and became a Full-Time Research and Development Staff Member in 2002 and the Group

Leader of the Power and Energy Systems Group in 2008. He also has an Adjunct Faculty appointment with the University of Arkansas, Fayetteville. His current research interests include the system-level impact of SiC power devices, multilevel inverters, power converters for distributed energy resources and hybrid electric vehicles, and intelligent control applications for power converters.

Dr. Ozpineci was the Chair of the IEEE Power Electronics Society (PELS) Rectifiers and Inverters Technical Committee and Transactions Review Chairman of the IEEE Industry Applications Society Industrial Power Converter Committee. He was the recipient of the 2006 IEEE Industry Applications Society Outstanding Young Member Award, the 2001 IEEE International Conference on Systems, Man, and Cybernetics Best Student Paper Award, and 2005 UT-Battelle (ORNL) Early Career Award for Engineering Accomplishment.

John N. Chiasson (S'82–M'84–SM'03) received the Bachelor's degree in mathematics from the University of Arizona, Tucson, the Master's degree in electrical engineering from Washington State University, Pullman, and the Ph.D. degree in Controls from the University of Minnesota, Minneapolis.

He was with the industry at Boeing Aerospace, Control Data, and Asea Brown Boveri Limited (ABB) Daimler-Benz Transportation. He is currently an Associate Professor of electrical and computer engineering at Boise State University, Boise. He is the author

of the recent textbook *Modeling and High-Performance Control of Electric Machines* (Wiley, 2005). His current research interests include the control of ac electric drives and multilevel converters.