## Gate-bias stress in amorphous oxide semiconductors thin-film transistors

M. E. Lopes, H. L. Gomes, M. C. R. Medeiros, P. Barquinha, L. Pereira, E. Fortunato, R. Martins, and I. Ferreira

<sup>1</sup>Centre of Electronic Optoelectronics and Telecommunications (CEOT), Universidade do Algarve, Campus de Gambelas, 8005-139 Faro, Portugal

(Received 12 March 2009; accepted 7 July 2009; published online 10 August 2009)

A quantitative study of the dynamics of threshold-voltage shifts with time in gallium-indium zinc oxide amorphous thin-film transistors is presented using standard analysis based on the stretched exponential relaxation. For devices using thermal silicon oxide as gate dielectric, the relaxation time is  $3 \times 10^5$  s at room temperature with activation energy of 0.68 eV. These transistors approach the stability of the amorphous silicon transistors. The threshold voltage shift is faster after water vapor exposure suggesting that the origin of this instability is charge trapping at residual-water-related trap sites. © 2009 American Institute of Physics. [DOI: 10.1063/1.3187532]

Amorphous gallium-indium zinc oxide (GIZO) thin-film transistors (TFTs) have attracted attention for their possible applications to flat, flexible, and transparent displays, 1-4 especially when processed at low temperatures. However, like the other TFTs' technologies, they also suffer from a stability phenomena known as gate-bias stress.<sup>5,6</sup> This effect manifests itself as a continuous increase in threshold voltage  $(V_{th})$ when the gate bias is kept constant over time. This limits the application of these TFTs in demanding applications, such as active matrix organic light emitting displays. The increase in  $V_{\rm th}$  lowers the luminance of individual pixels over time, causing display nonuniformity. As an example, using current technologies several driving transistors per pixel are necessary to compensate for the  $V_{\rm th}$  shift. Hence, a proper understanding of the stressing mechanism is of paramount importance.

Gate-bias stress effects are commonly reported in the literature for a variety of transistors, a-Si TFTs, organic transistors, 9-11 and recently also in amorphous oxide semiconductors TFTs. 12-15 The effect has been explained as a slow trapping of charge carriers in defects of unknown origin located at the semiconductor/dielectric interface. 13 It is known that the current degradation is faster when the devices are exposed to atmosphere 15,16 and that the stability improves after annealing. Also, it has been reported that the effects can be reduced by the insertion of a passivation layer, either between the dielectric and the semiconductor <sup>17</sup> or on top of the semiconductor in bottom-gate structures. <sup>16</sup>

This work provides a quantitative study of the gate-bias stress instability as a function of temperature and environment conditions. The results allow a comparison with competing TFTs technologies. Furthermore, it also provides evidences that water vapor contamination enhances this instability. Therefore, there is no conceptual limitation for the stability of GIZO based TFTs. This is in contrast to hydrogenated amorphous silicon TFTs where the instability is caused by the creation of intrinsic defects, unsaturated valence states into which electrons are trapped.

The device fabrication process has been described in detail elsewhere. 18 Briefly, the TFTs were produced with a staggered bottom gate configuration on silicon wafers, which acted as the gate electrode. 100 nm thick SiO<sub>2</sub> produced

either by (a) thermal oxidation or by (b) plasma enhanced

chemical vapor deposition (PECVD) was used as the dielec-

tric. A 40 nm thick GIZO (1:2:2 mol of Ga<sub>2</sub>O<sub>3</sub>: In<sub>2</sub>O<sub>3</sub>: ZnO)

film was deposited at room temperature by rf magnetron

sputtering, serving as the active channel layer. Finally, Ti/Au

source/drain electrodes were e-beam evaporated with typical

channel width and length of 50 and 25  $\mu$ m, respectively.

The GIZO active layer and the source/drain electrodes were

patterned using the lift-off technique. The effect of annealing

was studied by measuring both as-grown and annealed de-

vices, being the annealing performed in a tubular furnace for

1 h, in air, at 200 °C. Wet-atmosphere exposure was carried

out by bubbling dry N2 through distilled water poured into a

sealed flask. After this, the sample chamber was pumped to

high vacuum for one hour prior to any electrical measure-

thley 487 picoammeter/voltage source. Measurements were

carried out in dark conditions, in air as well as in high

vacuum. Before stressing, the devices have a  $V_{\rm th}$  in the range

ture. As a typical example linear transfer curves are pre-

sented in the inset of Fig. 1 as a function of stress time. The

device was fabricated using thermal SiO2 as gate dielectric

and it was annealed at 200 °C, being all the measurements done in vacuum. The applied gate bias during stress was

10 V and the transfer curves were measured in the linear

Assuming that the threshold-voltage shift  $(\Delta V_{th})$  is due

charges create an electric field that has to be compensated by

the gate bias before an accumulation layer can be formed.

The rate at which the charges are trapped depends on the free

of 1–3 V. All the transistors work in accumulation mode.

Electrical measurements were carried out using a Kei-

Stress was measured as a function of time and tempera-

$<sup>^2</sup>$ Department of Materials Science/CENIMAT/13N and CEMOP-UNINOVA, Faculty of Sciences and Technology, New University of Lisbon, Campus da Caparica, 2829-516 Caparica, Portugal

region at a drain bias of 0.5 V. The gate-bias induced stress does not affect significantly the  $\mu_{FE}$ , which is readily confirmed by the observation that the transistor transfer curves shift in a parallel fashion. However, it can be noticed that the curves were not perfectly linear over the entire voltage range. to trapped charges with surface density  $N_{\rm tr}$ ,  $\Delta V_{\rm th}$  is then given  $\Delta V_{\rm th} = e N_{\rm tr} / C_{\rm ox}$ , where  $C_{\rm ox}$  is the capacitance of the gate dielectric and e is the elementary charge. These trapped

carrier concentration  $N_f$ . For an exponential distribution of trap states characterized by a temperature  $T_0$ ,  $\Delta V_{\rm th}$  at infinite

a)Electronic mail: hgomes@ualg.pt.

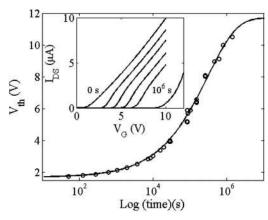

FIG. 1.  $V_{th}$  as function of time on a logarithmic scale. The continuous curve is a fit with stretched-exponential time dependence. The inset shows the drain current in the linear region ( $V_{DS}$ =0.5 V) as a function of the applied gate bias for increasing stress time. The gate bias during stress was 10 V and the temperature 20 °C.

stress time is equal to the applied gate bias, yielding a stretched exponential decay for  $V_{th}$  with time,

$$\Delta V_{\text{th}}(t) = V_0 \left\{ 1 - \exp \left[ -\left(\frac{t}{\tau}\right)^{\beta} \right] \right\},\,$$

where  $\tau$  is a characteristic time constant, the dispersion parameter  $\beta$  equals  $T/T_0$ , and  $V_0 = V_G - V_{th0}$ , where  $V_{th0}$  is the threshold voltage at the start of the experiment. The relaxation time is thermally activated as

$$\tau = v^{-1} \exp\left(\frac{E_a}{k_B T}\right),\,$$

where  $E_a$  is the mean activation energy for trapping and v is the frequency prefactor. This formalism allows the quantification of the device stability and is irrespective of the microscopic details of the process involved.<sup>19</sup>

The  $V_{\rm th}$  is presented as a function of time on a logarithmic scale in Fig. 1.  $V_{\rm th}$  saturates with time being the maximum shift equal to the applied gate bias. The continuous line is a fit to a stretched exponential. Perfect agreement is obtained for  $\tau$ =3×10<sup>5</sup> s and  $\beta$ =0.5 yielding a characteristic temperature of the trap states ( $T_0$ ) of 600 K. A similar agreement was found for stress measurements at other temperatures (see Table I).

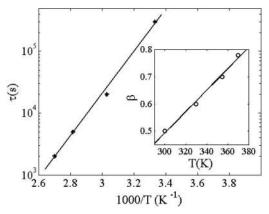

FIG. 2.  $\tau$  as a function of reciprocal temperature. The line shows that  $\tau$  is thermally activated with  $E_a$ =0.68 eV. The inset shows the corresponding  $\beta$  as a function of temperature.

To further investigate the trapping dynamics, stress measurements were performed at various temperatures, in vacuum, using annealed TFTs with thermal SiO<sub>2</sub>. The characteristic relaxation times are presented as a function of reciprocal temperature in Fig. 2. A straight line is obtained showing that the relaxation time is thermally activated, with  $E_a$ =0.68 eV and v=10<sup>6</sup> s<sup>-1</sup>. The inset of Fig. 2 shows the values of  $\beta$  as a function of temperature.  $E_a$  can be related to the microscopic nature of the trap site.

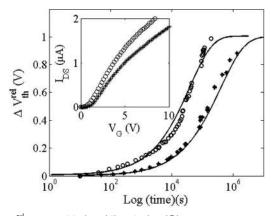

In spite of being recently observed that the gate-bias stress effect in TFTs can be reduced by protecting the transistors against environmental humidity, either with an encapsulation layer or by operating the transistor in vacuum,  $^{15-17}$  a correlation between stability and contamination by water has never been established. In order to study this relation we measured and compare the stability of the annealed sample before and after water vapor exposure for 24 h. Figure 3 shows the relative threshold voltage shift  $[V_{\text{th}}^{\text{rel}}=(V_{\text{th}})]$  $-V_{\text{th0}}/(V_g-V_{\text{th0}})$ ]. After water contamination,  $V_{\text{th}}$  increases with time much faster than before water vapor exposure. The continuous lines in Fig. 3 are fits to a stretched exponential. From these fits we obtain for  $\tau$  a value that decreases one order of magnitude from  $\tau=3\times10^5$  to  $3.9\times10^4$  s, while  $\beta$ remains approximately constant ( $\sim$ 0.5). The fitting parameters are shown in Table I.

Water vapor exposure also causes a small change in the initial  $V_{\rm th}$  (unstressed device), changing from 1.1 to 0.8 V. Therefore, the curves cross each other if  $V_{\rm th}$  is represented in

TABLE I. Activation energy  $E_a$ , relaxation time  $\tau$ , and dispersion parameter,  $\beta$ , at room temperature for investigated transistors, as well as for organic and silicon transistors. The table contains both our data as well as literature data. Values are presented for gate-bias stress in accumulation and recovery.

|                                                                    |         | au @RT              |         | $E_a$ (eV) | Ref.      |

|--------------------------------------------------------------------|---------|---------------------|---------|------------|-----------|

| Semiconductor dielectric/processing                                |         | (s)                 | $\beta$ |            |           |

| GIZO annealed @ 200 °C thermal SiO <sub>2</sub> , stress in vacuum |         | $3.0 \times 10^{5}$ | 0.5     | 0.68       | This work |

| GIZO annealed @ 200 °C PECVD SiO <sub>2</sub> (measured in air)    | Stress  | $1.2 \times 10^{5}$ | 0.5     |            | This work |

|                                                                    | Recover | $4 \times 10^{2}$   | 0.12    |            |           |

| GIZO as-grown PECVD $SiO_2$ (measured in air)                      | Stress  | $1.4 \times 10^{3}$ | 0.5     |            | This work |

|                                                                    | Recover | $4 \times 10^4$     | 0.4     |            |           |

| GIZO, thermal SiO <sub>2</sub> annealed @ 300 °C                   | Stress  | $2 \times 10^{4}$   | 0.42    | 0.53       | 13        |

| GIZO, thermal SiO <sub>2</sub> annealed @ 300 °C                   | Stress  | $2 \times 10^{4}$   |         |            | 14        |

|                                                                    | Recover | $3 \times 10^{5}$   |         |            |           |

| Organic semiconductor (in vacuum)                                  |         | $1 \times 10^{7}$   | 0.44    | 0.6        | 10        |

| Organic semiconductor (in air)                                     |         | $1 \times 10^{4}$   | 0.5     |            | 11        |

| Amorphous silicon                                                  | Stress  | $8 \times 10^{7}$   |         | 0.98       | 19        |

|                                                                    | Recover | $5 \times 10^{9}$   |         | 1.1        |           |

| Microcrystalline silicon                                           |         | $10^{12}$           |         | 1.07       | 6         |

FIG. 3.  $V_{\rm th}^{\rm rel}$  measured before (\*) and after ( $\bigcirc$ ) water vapor exposure. The continuous curves are a fit with stretched-exponential time dependence. Fitting parameters are in Table I. The inset shows the corresponding changes in the linear transfer curves measured for  $V_{\rm DS}{=}0.5$  V. The results were obtained in a device using thermal SiO<sub>2</sub> as gate dielectric and previously annealed at 200 °C.

absolute values. To avoid this crossing effect we chose to represent in Fig. 3 the relative threshold voltage shift  $(V_{\rm th}^{\rm rel})$ .

The linear transfer curves before and after the exposures to humidity are shown in the inset of Fig. 3. After water vapor contamination  $V_{\rm th}$  decreases from 1.1 to 0.8 V and the  $\mu_{\rm FET}$  improves slightly from 5 to 6 cm²/V s. These small changes, corresponding to a slight improvement on the device performance, can be the result of surface adsorbed water which still remains after pumping in vacuum. This water causes the formation of a surface accumulation layer of electrons. <sup>15</sup> However, water which diffuses toward the interface SiO<sub>2</sub>/GIZO may act as a deep carrier trap leading to  $V_{\rm th}$  degradation as observed in our experimental results. In contrast, it has been reported that the presence of water during annealing improves the transistor parameters. <sup>20</sup> In this case, the combined effect of water and oxygen at high temperatures passivates unstable bonds or carrier defects. <sup>20</sup>

Gate-bias stress experiments were also carried out on devices fabricated using  $SiO_2$  grown by PECVD as a gate dielectric. Thermal annealed devices showed a significant higher stability than the as-grown devices (see Table I). In view of the previous results, the improvement of the device stability is possibly caused by the out-diffusion of water from the device.

To benchmark the stability of GIZO based transistors we have included in Table I the parameters  $\tau$ ,  $\beta$ , and  $E_a$  for other TFTs' technologies. The relaxation time of an annealed transistor is approaching the a-Si transistors. Also, since a-Si and  $\mu c$ -Si TFTs have activation energy higher than GIZO based TFTs, the difference in stability becomes less pronounced at high temperatures. Our data also shows a relaxation time of  $3 \times 10^5$  s, which is one order of magnitude higher than the best value reported in the literature  $(2 \times 10^4 \text{ s})$  for a GIZO based transistor produced using thermal SiO<sub>2</sub> as a gate dielectric  $^{13,14}$  (see Table I).

In applications such as active matrix displays, the transistor is only temporarily switched on. The generated  $\Delta V_{th}$  relaxes in the off-state. Recovery of stress is, therefore, as important as stress. The  $\Delta V_{th}$  recover was studied by keeping the drain and the gate terminals grounded between the measurements of the transfer curves. Measurements were done on devices using PECVD SiO2 as a gate dielectric. The  $\Delta V_{th}$

is completely reversible and follows stretched-exponential time decay. Table I shows that for the as-grown device, the relaxation time for stress is slightly smaller than for recovery. However, recovering is much faster in the annealed device. This behavior is different from the previous reported for GIZO based transistor where  $V_{\rm th}$  recovering is observed to be slower than stressing, <sup>14</sup> as well as on *a*-Si transistors where stress is orders of magnitude faster than recovery (see Table I).

In summary, we have investigated the stability of amorphous oxide TFTs using GIZO as the semiconductor channel layer. The Vth with time according to a stretched exponential. The relaxation times are thermally activated with activation energy of 0.68 eV for thermal  $\mathrm{SiO}_2$ . Differences in stability are due to differences in the relaxation time that varies between  $10^2$  and  $10^5$  s. The gate-bias stress is completely reversible. Experiments after water vapor exposure clarifies previously reported results, demonstrating that water contamination increases significantly the gate-bias stress instability.

The authors wish to thank the Portuguese Foundation for Science and Technology for financial support of this work to the research units CEOT CENIMAT/I3N and to projs. PTDC/EEA-ELC/64975/2006 and PTDC/CTM/73943/2006.

<sup>1</sup>P. Barquinha, L. Pereira, G. Goncalves, R. Martins, and E. Fortunato, J. Electrochem. Soc. **156**, H161 (2009).

<sup>2</sup>J. Y. Kwon, K. S. Son, J. S. Jung, T. S. Kim, M. K. Ryu, K. B. Park, B. W. Yoo, J. W. Kim, Y. G. Lee, K. C. Park, S. Y. Lee, and J. M. Kim, IEEE Electron Device Lett. **29**, 1309 (2008).

<sup>3</sup>J. Park, S. Kim, C. Kim, S. Kim, I. Song, H. Yin, K.K. Kim, S. Lee, K. Hong, J. Lee, J. Jung, E. Lee, K.W. Kwon, and Y. Park, Appl. Phys. Lett. **93** 053505 (2008).

<sup>4</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London) **432**, 488 (2004).

<sup>5</sup>J. M. Lee, I. Y. Cho, J. H. Lee, and H. I. Kwon, Appl. Phys. Lett. **93**, 093504 (2008).

<sup>6</sup>R. Wehrspohn, S. Deane, I. French, and M. Powell, Thin Solid Films 383, 117 (2001).

<sup>7</sup>Y. He, R. Hattori, and J. Kanicki, IEEE Electron Device Lett. **21**, 233 (2000).

<sup>8</sup>A. Nathan, G. R. Chaji, and S. J. Ashtiani, J. Disp. Technol. **1**, 267 (2005)

<sup>9</sup>H. L. Gomes, P. Stallinga, F. Dinelli, M. Murgia, F. Biscanini, D. M. Leeuw, T. Muck, J. Geurts, L. W. Molenkamp, and V. Wagner, Appl. Phys. Lett. 84, 3184 (2004).

<sup>10</sup>S. G. J. Mathijssen, M. Cölle, H. Gomes, E. C. P. Smits, B. de Boer, I. McCulloch, P. A. Bobbert, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) 19, 2785 (2007).

<sup>11</sup>S. G. J. Mathijssen, M. Kemerink, A. Sharma, M. Cölle, P. A. Bobbert, R. A. J. Janssen, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) 20, 975 (2008).

<sup>12</sup>P. Görrn, P. Hölzer, T. Riedl, W. Kowalsky, J. Wang, T. Weimann, P. Hinze, and S. Kipp, Appl. Phys. Lett. 90, 063502 (2007).

<sup>13</sup>A. Suresh and J. F. Muth, Appl. Phys. Lett. **92**, 033502 (2008).

<sup>14</sup>I. T. Cho, J. M. Lee, J. H. Lee, and H. I. Kwon, Semicond. Sci. Technol. 24, 015013 (2009).

<sup>15</sup>J. S. Park, J. K. Jeong, H. J. Chung, Y. G. Mo, and H. D. Kim, Appl. Phys. Lett. **92**, 072104 (2008).

<sup>16</sup>J. K. Jeong, H. W. Yang, J. H. Jeong, Y. G. Mo, and H. D. Kim, Appl. Phys. Lett. **93**, 123508 (2008).

Phys. Lett. 93, 123308 (2008).

S. Chang, Y. W. Song, S. Lee, S. Y. Lee, and B. K. Ju, Appl. Phys. Lett. 92, 192104 (2008).

<sup>18</sup>P. Barquinha, L. Pereira, G. Goncalves, R. Martins, and E. Fortunato, Electrochem. Solid-State Lett. 11, H248 (2008).

<sup>19</sup>S. C. Deane, R. B. Wehrspohn, and M. J. Powell, Phys. Rev. B **58**, 12625 (1998)

<sup>20</sup>K. Nomura, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, Appl. Phys. Lett. **93**, 192107 (2008).