IEEE-TPEL

IEEE Transactions on Power Electronics **<b>**IEEE

## Gate-emitter Pre-threshold Voltage as a Health Sensitive Parameter for IGBT Chip Failure Monitoring in High Voltage Multichip IGBT Power Modules

| Journal:                      | D TPEL-Reg-2018-05-1038.R1                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Manuscript ID                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Manuscript Type:              |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Date Submitted by the Author: | 28-Sep-2018                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Complete List of Authors:     | Mandeya, Richard; Newcastle University, School of Engineering<br>Chen, Cuili; Newcastle University, School of Electrical and Electronic<br>Engineering<br>Pickert, Volker; Newcastle University, School of Electrical, Electronic and<br>Computer Engineering<br>Naayagi, R.T.; Newcastle University, School of Electrical and Electronic<br>Engineering<br>Ji, Bing; University of Leicester, Department of Engineering |  |  |  |

| Keywords:                     | Multichip modules, High-voltage techniques, Insulated gate bipolar transistors, Failure analysis, Reliability, Monitoring                                                                                                                                                                                                                                                                                                |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

#### IEEE-TPEL

# Gate-emitter Pre-threshold Voltage as a Health Sensitive Parameter for IGBT Chip Failure Monitoring in High Voltage Multichip IGBT Power Modules

Richard Mandeya<sup>1</sup>, Cuili Chen<sup>1</sup>, Volker Pickert<sup>1</sup>, Member, IEEE, R.T. Naayagi<sup>2</sup>, Senior Member, IEEE, Bing Ji<sup>3</sup>,

Member, IEEE.

<sup>1</sup>School of Engineering, Newcastle University, NE1 7RU, Newcastle upon Tyne, UK, England.

<sup>2</sup>School of Electrical and Electronic Engineering, Newcastle University International Singapore, 567739, Singapore. <sup>3</sup>Department of Engineering, University of Leicester, LE1 7RH, Leicester, UK, England.

m.a.r.mandeya@ncl.ac.uk, c.chen22@ncl.ac.uk, volker.pickert@ncl.ac.uk, naayagi.ramasamy@ncl.ac.uk,

bing.ji@le.ac.uk.

Authors confirm none of the material in this paper has been published or is under consideration for

publication elsewhere.

*Abstract* - This paper proposes a novel health sensitive parameter, called the gate-emitter prethreshold voltage  $V_{GE(pre-th)}$ , for detecting IGBT chip failures in multichip IGBT power modules. The proposed method has been applied in an IGBT gate driver and measures the  $V_{GE}$  at a fixed time instant of the  $V_{GE}$  transient before the threshold voltage occurs. To validate the proposed method, theoretical analysis and practical results for a 16-chip IGBT power module are presented in the paper. The results show a 500 mV average shift in the measured  $V_{GE(pre-th)}$  for each IGBT chip failure.

*Keywords* – High voltage multichip Insulated Gate Bipolar Transistor (IGBT) module, IGBT chip failure, health monitoring, threshold voltage.

#### I. INTRODUCTION

> IGBT power modules are widely used in high power converter applications [1, 2]. They dominate the market due to their superior overall performance which results from the IGBT structure incorporating the gating of Metal Oxide Semiconductor Field-Effect Transistors (MOSFETs) for fast switching speed, and the body region of Bipolar Junction Transistors (BJTs) for low conduction losses [3, 4]. Recently, there has been a growing interest in the application of health monitoring techniques to improve the operational reliability of the IGBT power modules. In general, there are mainly three points which are of interest in IGBT health monitoring: i) virtual junction temperature  $(T_{vj})$  [5-28], ii) solder degradation [29-32], and iii) bond wire failure [29, 33-39]. Some of the health monitoring techniques proposed are in-situ, meaning health monitoring is achieved via a test circuit exclusively developed for detecting degradation and implemented onboard power converters. In-situ health monitoring avoids the fallout of a disrupted field service due to power converter teardown prior to inspection.

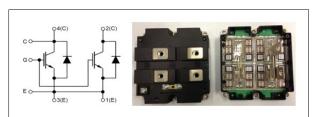

> This paper proposes an online detection technique for IGBT chip failures in High Voltage (HV) multichip IGBT power modules as their applications are mostly critical [41-43]. A typical multichip module is depicted in Fig.1 which shows a 3.3 kV, 800 A single switch IGBT power module (DIM800NSM33-F) from Dynex Semiconductor Limited that was used for experimentation. The DIM800NSM33-F has 16 IGBT chips and 8 anti-parallel diodes. This work focusses only on the health monitoring of the IGBT chips and not the diode chips. This is because IGBTs have a more complex semiconductor structure and due to the gate a more complex chip surface structure which makes IGBT chip less reliable compared to diodes. Also, IGBTs experience higher turn-on and turn-off losses compared to diodes and are therefore more stressed. Finally, in large power modules, it is common to have more IGBT chips than diode chips due to the different current density for each device type.

Fig. 1. Dynex 3.3 kV, 800 A IGBT Power Module (DIM800NSM33-F): Electrical Configuration [44], External and Interior View.

Bond wire failure is one of the primary failure mechanisms of the IGBT module. For an IGBT chip, since several bond wires are employed for the chip connection, it remains functional upon the initial occurrence of one bond wire lift-off. However, an IGBT chip eventually ceases to function when all of its bond wires fail. Likewise, upon the initial chip failure, a multichip IGBT module still remains functional due to several IGBT chips being in parallel [33, 45]. Nevertheless, an IGBT power module's robustness is in line with its health conditions which depends on each of the constituent chips. Eventually, the power module fails outright. In this regard, this paper proposes the IGBT chip failure as a health monitoring precursor for multichip IGBT power modules.

A new method for detecting the IGBT chip failures in multichip HV IGBT power modules is presented in this paper by monitoring the pre-threshold voltage ( $V_{GE(pre-th)}$ ) which takes place during the turn-on transient of  $V_{GE}$ . A distinct advantage of  $V_{GE(pre-th)}$  is that it is measured before the conduction of the IGBT collector current ( $I_C$ ), and hence does not suffer from changes in the load current or the noise caused by the switching on of the device after the threshold point. Furthermore,  $V_{GE(pre-th)}$  does not require HV isolation and HV insulation as all of the measurement circuitry is on the gate side rather than the HV collector side. For HV isolation, we refer to the electric circuitry employed for isolation between the HV and gate-emitter circuits. For HV insulation, we mean the insulation of the cables and the components. Unlike current sensor based methods,  $V_{GE(pre-th)}$  uses a simple low cost and lightweight voltage sensor which can be easily embedded into any gate driver.

This paper discusses the theoretical analysis and hardware implementation of  $V_{GE(pre-th)}$  on the gate driver of the 16-chip DIM800NSM33-F, where  $V_{GE(pre-th)}$  is monitored at a fixed time instant from the IGBT turn-on command. It is shown that the sensitivity is 500 mV per IGBT chip failure and the

IEEE-TPEL

results are consistent under different operational and environmental conditions. As it is measured before the IGBT's turn-on threshold,  $V_{GE(pre-th)}$  can be embedded within a standard PWM controller.

## II. COMPARISON OF EXISTING HEALTH MONITORING METHODS

Over the last two decades, many efforts have been dedicated to online bond wire failure detection of IGBT power devices. Most of the research focuses on the IGBT health sensitive parameters (HSPs) which can be measured externally through the main terminals – collector, gate and emitter (as well as Kelvin connectors where appropriate) – of an IGBT module. A selection of these methods is presented in Table I.

Table I. Examples of bond wire and chip failure detection techniques.

| HSP                       | IGBT<br>Type | <b>Relative Sensitivity</b> |                          | Immunity to T <sub>vj</sub> | Reference    |

|---------------------------|--------------|-----------------------------|--------------------------|-----------------------------|--------------|

|                           |              | Bond wire/chip failure (A)  | <b>T</b> vj ( <b>B</b> ) | A/B                         | Kelerence    |

| $V_{\text{CE(on)}}^{[1]}$ | 1-chip       | 1% (bond wire)              | 0.01%                    | 100 (weak)                  | [29, 33, 34] |

| $V_{\text{CE(on)}}^{[2]}$ | 1-chip       | 14.6 % (bond wire)          | 0.01%                    | 1460 (strong)               | [37]         |

| R <sub>CE(on)</sub>       | 2-chip       | 1.9% (bond wire)            | 0.44%                    | 4 (weak)                    | [36]         |

| I <sub>G(peak)</sub>      | 2-chip       | 36% (chip)                  | 0.05%                    | 720 (medium)                | [46-48]      |

| dV <sub>CE</sub> /dt      | 2-chip       | 25% (bond wire)             | 0.17%                    | 147 (weak)                  | [38]         |

<sup>[1]</sup>  $V_{CE(on)}$  is the on-state voltage drop under load current.

<sup>[2]</sup>  $V_{CE(on)}$  is the on-state voltage drop at the inflexion point.

Table I shows five HSPs to determine bond wire failure ( $V_{CE(on)}$ ,  $R_{CE(on)}$ ,  $dV_{CE}/dt$ ) and chip failure ( $I_{G(peak)}$ ). A chip failure means the loss of all bond wires connected to one chip. It is well known that the temperature dependency of a HSP can conceal their failure signature or depreciate their ability to detect a bond wire/chip failure. In order to determine the impact that  $T_{vj}$  has on the reading of bond wire failure and chip failure the relative sensitivity for bond wire/chip failures and the relative sensitivity for bond wire/chip failures and the relative sensitivity for  $T_{vj}$  is shown in Table I. The quotient of both indicates how immune each HSP is from  $T_{vj}$  changes. As HSPs are measured in different units -  $V_{CE(on)}$  is measured in V,  $dV_{CE}/dt$  in V/s,  $I_{G(peak)}$  in A and  $R_{CE(on)}$  in  $\Omega$  - a direct comparison of their sensitivity to temperature changes or to changes in the number of bond wire failure or chip failure is difficult. As such the sensitivity of each HSP must be normalised for comparison. Relative sensitivity is a normalised parameter and shown in Eq.

#### IEEE-TPEL

(1). In Eq. (1) 'Variation' is either the  $T_{vj}$  reading of HSP for a given temperature above room temperature or the reading of HSP for a given number of bond wire or chip failures. 'Baseline value' is either the  $T_{vj}$  reading of HSP at room temperature or the reading of HSP where all bond wires or chips are healthy.

Relative Sensitivity =

$$\frac{|Variation|}{Baseline value_{room temperature}} \times 100\%$$

(1)

In Table I,  $R_{CE(on)}$  and  $dV_{CE}/dt$  have weak immunity. That is because both have the highest temperature-dependent HSPs with 0.44% and 0.17% respectively which causes challenges in reading bond wire lift-offs. According to the references stated in the table, both techniques are not able to detect the first bond wire lift-off.  $R_{CE(on)}$  is effective in determining the second bond wire lift-off whereas  $dV_{CE}/dt$  is only capable of detecting the fourth bond wire lift-off, and hence they can not be regarded as good HSPs for single bond wire lift-off.  $V_{CE(on)}$  measured at load current also has a weak immunity. However,  $V_{CE(on)}$  measured at the inflexion point shows the strongest resistance to  $T_{vj}$  variation. Measurement of  $V_{CE(on)}$  requires regrettably HV isolation, and the measurement circuit must deal with large  $V_{CE}$  voltage swings ranging from kilovolts during the blocking stage to a few volts during the on-state stage.  $I_{G(peak)}$  has a medium immunity to  $T_{vj}$  changes but detecting a peak gate current value is difficult to implement practically. As gate currents are relatively small and measurements are taken close to the IGBT module the detection circuit must also deal with EMI challenges.

So far the techniques in Table I have only been applied to IGBT switches with only one or two chips. HSP will become more challenging when there are more IGBT chips in parallel, which are typical in multichip IGBT power modules. The main challenge is the increase in the complexity in the physics of failure as well as their characteristic formation, owing to the inhomogeneous power semiconductor chips combined with the heterogeneous construction of power modules. This can lead to an accelerate chip failure subject to operational stresses, which can depreciate the HSPs or conceal their failure signature. Multichip IGBT power modules are designed for large current ratings, and the number of chips connected in parallel depends on the chip current rating and the load current rating.

The proposed method for detecting the IGBT chip failures in multichip HV IGBT power modules is presented next.

## III. PRE-THRESHOLD VOLTAGE AS HSP

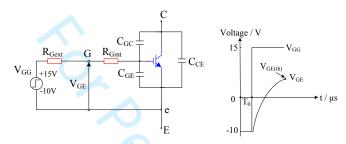

The gate-emitter circuitry comprises  $R_{G(ext)}$ ,  $R_{G(int)}$ ,  $C_{GE}$  and  $C_{GC}$  which form an *RC* circuit with  $V_{GG}$  as shown in Fig. 2.  $R_{G(int)}$  and  $R_{G(ext)}$  are the internal and the external gate resistors respectively.  $C_{GE}$  and  $C_{GC}$  are the gate-emitter and gate-collector capacitors of the IGBT.  $V_{GG}$  is the gate voltage supply.

Fig. 2. RC circuit forming the waveform of  $V_{\text{GE}}$  from the PWM trigger event  $T_0$  to  $V_{\text{GE(th)}}$  during turn-on.

Eq. (2) describes the exponential rising of  $V_{GE}$  at turn-on before threshold point which is reflected in Fig. 2 [36]. In Fig. 2, the off-state gate voltage supply,  $V_{GG(off)}$ , is -10 V whereas the on-state gate voltage supply,  $V_{GG(on)}$ , is +15 V. Thus the exponential rising of  $V_{GE}$  is due to the charging of the capacitive IGBT gate structure which is necessary prior to the IGBT module switching on.

$$V_{GE(pre-th)} = \left(V_{GE(th)} - V_{GG(off)}\right) \left(1 - e^{-\left[\frac{t}{R_G C_{ies}}\right]}\right) + V_{GG(off)}$$

(2)

Where  $V_{GE(th)}$  is the gate-emitter threshold voltage; *t* is the time;  $R_G$  is the total gate resistance which includes  $R_{G(int)}$  and  $R_{G(ext)}$ .  $C_{ies}$  is the gate input capacitance:

$$C_{\rm ies} = C_{\rm GE} + C_{\rm GC} \tag{3}$$

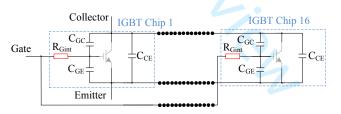

In multichip IGBT power modules, each of the paralleled IGBT chips exhibits an inherent gate input capacitance and an internal gate resistance as shown in Fig. 3. Thus a healthy IGBT power module has an overall internal gate resistance,  $R_{G(int),total}$  ( $R_{G(int),total} = R_{G(int)} / n$ ), and gate input capacitance,  $C_{ies,total}$  ( $C_{ies,total} = (C_{GE} + C_{GC}) \cdot n$ ), with  $R_{G(int),total}$  and  $C_{ies,total}$  being the lumped resistances and capacitances by taking each parallel connected chip *n* into account. DIM800NSM33-

#### IEEE-TPEL

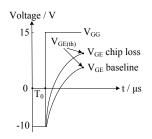

F IGBT modules have a typical  $C_{\text{ies,total}}$  of 144 nF and  $R_{G(\text{int}),\text{total}}$  of 135  $\mu\Omega$  [44]. In the case of the total loss of bond wire connections to an IGBT chip, the effective inter-chip connection will be altered resulting in a corresponding decline in  $C_{\text{ies,total}}$  and a rise in  $R_{G(\text{int}),\text{total}}$ . This partial open-circuit fault within the multichip module may not necessarily lead to an outright module breakdown, but will cause changes to its gate dynamic performance due to the  $R_{G(\text{int}),\text{total}}$  and  $C_{\text{ies,total}}$  changes with every chip failure and therefore the  $V_{\text{GE}}$  trajectory will be altered and the baseline value of  $V_{\text{GE}(\text{pre-th})}$  as defined in Eq. (2) and Fig. 2 will be shifted as shown in Fig. 4. A limitation of the proposed  $V_{\text{GE}(\text{pre-th})}$  method is that single bond wire lift-offs cannot be detected. This is because singular bond wire failures prior to outright chip failure will not cause changes to  $R_{G(\text{int}),\text{total}}$  and  $C_{\text{ies,total}}$  because the chip is still connected and functional through the remaining bond wires. For this reason; it is the loss of all emitter bond wires connected to a chip which results in an outright chip failure that  $V_{\text{GE}(\text{pre-th})}$  can detect. Considering multichip power modules such as the DIM800NSM33-F IGBT power module which has 16 IGBT chips and each chip has 8 emitter bond wires resulting in 128 emitter bond wires in total, the loss of a single or few bond wires will not affect the operation at the rated current of the power module.

Fig. 3. Representation of IGBT chip capacitances and internal resistances in multichip IGBTs.

Fig. 4. Changes on  $V_{GE}$  with IGBT chip failures.

Fig. 4 shows that  $V_{GE}$  always starts from a fixed voltage level and as  $V_{GE(th)}$  changes with chip failures, the trajectory of the  $V_{GE}$  will also change. Consequently, when measuring at a fixed point of time before  $V_{GE(th)}$ , the voltage level changes with the number of chips and this effect can be used as

a HSP for IGBT chip failures. The HSP is therefore called the pre-threshold voltage  $V_{GE(pre-th)}$ . This knowledge allows the use of a simple counter that determines the point of measurement slightly before  $V_{GE(th)}$  is reached. The counter will be triggered by the PWM signal to synchronise the measurement of  $V_{GE(pre-th)}$ .

Although IGBT power modules would continue to operate after the initial chip failures due to the paralleling of the chips, when more chips continue to fail, a warning status is reached that can be determined as critical. This means that beyond the loss of a certain amount of chips the power module will fail. The number of acceptable loss of chips depends on the application, and this decision lies with the customer. Generally, the loss of 10% of the silicon chips can be regarded as acceptable. Therefore, for the DIM800NSM33-F module, the detection of two chip failures out of sixteen has been set as the safety margin. Consequently, the experimentations discussed next are for the initial two chip failures of the DIM800NSM33-F.

## IV. EXPERIMENTAL SET-UP

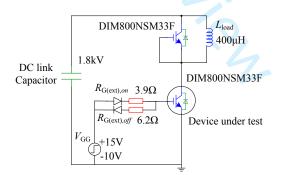

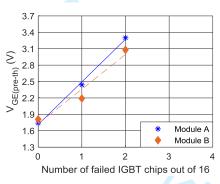

A purpose-built high voltage high current IGBT test rig was set up based on the schematic in Fig. 5 to investigate the proposed  $V_{GE(pre-th)}$  method for detecting the IGBT chip failure.

Fig. 5. Schematic for the  $V_{GE(pre-th)}$ -IGBT chip failure tests.

In Fig. 5, a 400  $\mu$ H inductive load was utilised, and the DC-link supply voltage and current were set to 1800 V DC and 800 A DC respectively. The IGBT at the top is off at all times and is employed as an anti-parallel diode. The 16-chip IGBT module under test was pulsed from a gate driver with a voltage supply ranging from -10 V to +15 V. The gate driver used is the 2SC0535T2A1-33 from CONCEPT [49]. 3.9  $\Omega$  gate resistors for turn-on ( $R_{G(ext),on}$ ) and 6.2  $\Omega$  gate resistors for turn-off

#### IEEE-TPEL

$(R_{G(ext),off})$  were used between the ideal pulsed voltage supply and the IGBT gate terminal. The gate resistors used are thick film surface mount resistors 1206 which are recommended in the gate driver datasheet, application note and manual [49-51]. The film surface mount resistors 1206 are typically used in gate driver circuits for real applications due to their low resistance tolerance of 1% and high-power proofing to minimize the gate-loop inductances (typical with wire wound resistors which could alter the switching performance of the IGBT [52]).

A liquid temperature controlled heatsink was used to alter the IGBT power module's baseplate temperature  $T_{\rm C}$  which in turn varies  $T_{\rm vj}$  according to Eq. 4.

$$T_{vj} = T_{C} + P_{D} \bullet Z_{Th(jc)}$$

(4)

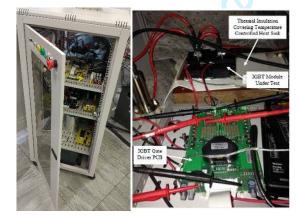

Where  $P_D$  and  $Z_{Th(jc)}$  are the IGBT power dissipation and the thermal impedance between the IGBT junction and case, respectively. A settling time is required to fulfil  $T_{vj}=T_C$ . The IGBT baseplate temperature ( $T_C$ ) was measured with thermocouples. The thermocouples used are Type K stainless steel washer probes with a tolerance of +/-1.5 °C [53]. In order to average out the thermocouple errors, six thermocouples were placed around the IGBT module mounting holes on the baseplate. For characterization, the IGBT  $V_{GE}$  waveform was measured by the oscilloscope to determine the best point of  $V_{GE(pre-th)}$  measurement just before  $V_{GE(th)}$ . A photograph of the test rig is shown in Fig. 6.

Fig. 6. Photograph of the experimental set-up: complete test rig and IGBT close-up.

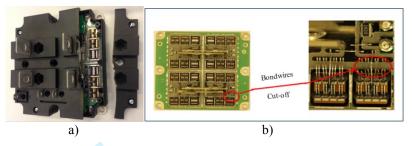

IGBT chip failure has been emulated by cutting off all the emitter bond wires of the IGBT chip. Consequently, the loss of 8 emitter bond wires connected to one chip which results in an outright chip failure is referred to as '1 chip loss' in the context. The loss of 16 emitter bond wires connected

#### IEEE-TPEL

to two chips leads to the loss of two IGBT chips, which is referred to as '2 chip loss', and the healthy state before chip failure is referred to as the 'baseline' in the experiments. An access hatch shown in Fig. 7a was developed in order to access the IGBT chips and cut off the emitter bond wires of one or two IGBT chips as shown in Fig. 7b.

Fig. 7. Cutting off bond wires to impose IGBT chip failures: a) chip access hatch, b) Close-up of bond wires cut off.

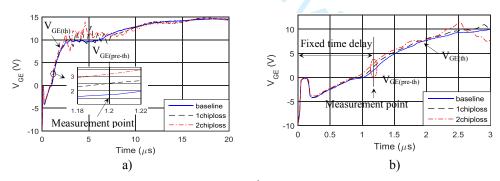

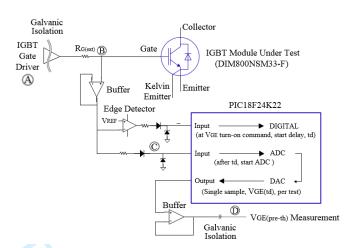

## V. CHARACTERISATION OF $V_{GE(PRE-TH)}$

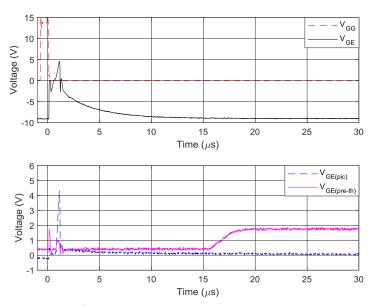

Fig. 8a shows the experimental results of  $V_{GE(pre-th)}$  for initial two chip failures on DIM800NSM33-F power module at  $T_{vj}$  of 20 °C. Fig. 8b illustrates the measurement point of  $V_{GE(pre-th)}$  using a fixed time delay of 1.2 µs after  $V_{GE}$  starts rising from -10 V. The results show that two successive IGBT chip failures of the sixteen-chip DIM800NSM33-F revealed a consistent trend on  $V_{GE(pre-th)}$  that the voltage level  $V_{GE(pre-th)}$  rises with every chip failure.

Fig. 8. a) Changes in  $V_{\text{GE}(\text{pre-th})}$  with IGBT chip failures at 20 °C, b) Use of fixed time delay for  $V_{\text{GE}(\text{pre-th})}$  measurement at 20 °C.

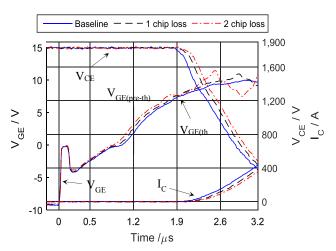

Fig. 9 shows that  $V_{\text{GE}(\text{pre-th})}$  is not affected by the switching transients of  $V_{\text{CE}}$  and  $I_{\text{C}}$  as the distortion of the uniform trend on  $V_{\text{GE}}$  occurs after  $V_{\text{GE}(\text{th})}$  when  $V_{\text{CE}}$  transient begins to fall and  $I_{\text{C}}$  begins to conduct/rise. Hence  $V_{\text{GE}(\text{pre-th})}$  has an advantage that it is not affected by the switching transients of  $V_{\text{CE}}$  and  $I_{\text{C}}$  or changes in the load size.

Fig. 9. Clearance of  $V_{GE(pre-th)}$  from  $I_C$  and  $V_{CE}$  switching noise at different IGBT health states.

In practice, the DC-link supply voltage ( $V_{DC-link}$ ) is regulated to a 5% fluctuation [54]. Variations in the DC-link voltage levels impact on  $V_{GE}(t)$  as shown in Eq. (5). However, the term  $dV_{CE}/dt$  in (5) remains zero 0 until  $V_{GE}(t)$  reaches  $V_{GE(th)}$ . At  $V_{GE(th)}$  current starts flowing in the IGBT and  $dV_{CE}/dt$ becomes  $dV_{CE}/dt\neq 0$  impacting on the voltage  $V_{GE}(t)$ . Therefore the proposed measurement is independent of DC-link supply voltage changes.

$$V_{GE}(t) = R_{G(int)} \left[ C_{GE} \frac{dV_{GE}}{dt} + C_{GC} \frac{d[V_{CE} - V_{GE}]}{dt} \right]$$

(5)

## A. Performance with respect to temperature changes

Eq (2) shows that  $V_{GE(pre-th)}$  is directly related to  $V_{GE(th)}$ .  $V_{GE(th)}$  is temperature dependent and can be expressed [55, 56] as,

$$V_{GE(th)} = V_{FB} + 2\phi_F + \gamma \sqrt{2\phi_F}$$

(6)

Where  $V_{\text{FB}}$  is the flat band voltage,  $\gamma$  is the body effect parameter and  $\mathcal{O}_{\text{F}}$  is the Fermi energy which is given by:

$$\phi_{\rm F} = \phi_{\rm T} \ln \frac{{\rm N}_{\rm A}}{{\rm n}_{\rm i}} \tag{7}$$

with  $n_i$  as the intrinsic density,  $N_A$  as the substrate concentration, and  $\mathcal{O}_T$  as the thermal voltage:

$$\phi_{\rm T} = \frac{{\rm kT}}{{\rm q}} \tag{8}$$

Where *k* is the Boltzmann's constant, *q* is the charge of an electron and *T* is the temperature. The intrinsic density  $n_i$  in (6) can be written as,

$$n_i = N_A e^{-\frac{E_g}{2kT}}$$

(9)

Where  $E_{g}$  is the energy gap.

Eqs. (8) and (9) show that the thermal voltage  $\mathcal{O}_{T}$  (8) and the intrinsic carrier concentration  $n_{i}$  (9) are temperature dependent parameters which account for the temperature dependency of  $V_{GE(th)}$ . The flat band voltage in Eq. (6) has also been reported as temperature dependent [28]. Consequently, in Eq. (2),  $V_{GE(th)}$  varies with temperature and it varies the gradient of the  $V_{GE}$  waveform which can influence  $V_{GE(pre-th)}$ . Eq. (2) also shows that  $V_{GE(pre-th)}$  is related to  $R_{G(int)}$  which is also temperature dependent [11, 12]. Hence  $R_{G(int)}$  can also vary the gradient of the  $V_{GE}$  waveform when the IGBT chip temperature changes.

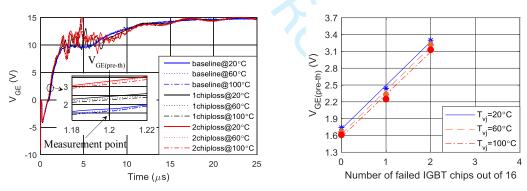

Therefore, it is essential to investigate how  $V_{GE(pre-th)}$  is influenced by the temperature and by the loss of chips. For this investigation, the temperature of the IGBT module has been varied through the heat plate. Tests at different temperatures are carried out before and after the chip failures. Fig. 10 shows the results of  $T_{vj}$  changes and the chip failures.

Fig. 10. Variation of  $V_{GE(pre-th)}$  with IGBT chip failures at different temperatures.

The results in Fig. 10 show linear relationships between  $V_{GE(pre-th)}$  and chip failures at each of the three temperatures. The results indicate that temperature variations do not affect the chip failure signature in  $V_{GE(pre-th)}$ . The reason is that gate-emitter voltage waveforms are very close with a small negative sensitivity of -2.5 mV / °C when  $T_{vj}$  changes from 20 °C to 100 °C before the chip failure. The same observation is made when the power module lost one or two chips. Fig. 10 shows clearly that once the first chip has failed, there is a jump in the  $V_{GE(pre-th)}$  level compared to the healthy module, with a positive sensitivity of 500 mV/chip failure which is a significantly bigger change in

#### IEEE-TPEL

voltage compared to the voltage change generated by the temperature as the  $T_{vj}$  sensitivity is only -2.5 mV / °C. Another +500 mV jump in  $V_{GE(pre-th)}$  is detected when the second chip becomes disconnected with the bond wires. Consequently, it can be concluded that  $V_{GE(pre-th)}$  is immune to  $T_{vj}$ changes as the change in  $V_{GE(pre-th)}$  due to changes in  $T_{vj}$  is always lower compared to the voltage change caused by the disconnected chips. Based on Fig 10, a warning system for the power module tested can be easily implemented with a simple lookup table that holds the following information:  $V_{GE(pre-th)} < 2.0$  V - power module is healthy (baseline); 2.0 V  $< V_{GE(pre-th)} < 2.8$  V - one IGBT chip has failed;  $V_{GE(pre-th)} > 2.8$  V - two IGBT chips have failed.

In Table I,  $I_{G(peak)}$  is the only HSP for IGBT chip failure detection which can be compared with  $V_{GE(pre-th)}$ . Using Eq. (1), the relative sensitivity of  $V_{GE(pre-th)}$  is 0.11 % for  $T_{vj}$  and 28.7 % for chip failures. This compares well with  $I_{G(peak)}$  which has a strong immunity to  $T_{vj}$  with a  $T_{vj}$  relative sensitivity of 0.05 % and the chip failure sensitivity of 36 %. The main advantage of  $V_{GE(pre-th)}$  over  $I_{G(peak)}$  is that  $V_{GE(pre-th)}$  employs a voltage sensor while  $I_{G(peak)}$  utilises a current sensor. In general, voltage sensors are cheaper, simpler and lightweight compared to current sensors hence voltage-based HSPs are preferred from a practical perspective [57].

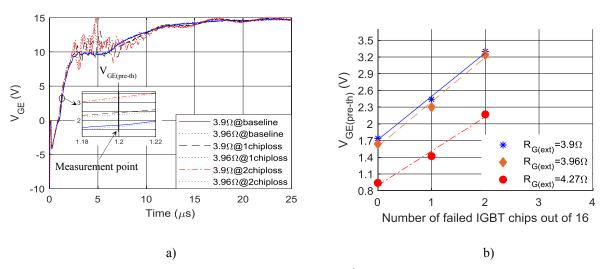

## B. Changes in $R_{G(ext)}$

$R_{G(ext)}$  is one of the most influential components on  $V_{GE(pre-th)}$  according to Eq. (2).  $R_{G(ext)}$  is located on the IGBT power module's external circuitry and is temperature sensitive. For this reason, the impact of changes in  $R_{G(ext)}$  has been investigated.

The gate resistors employed for  $R_{G(ext)}$  have a temperature coefficient of resistance (TCR) of 100ppm/K and thus the overall turn-on resistance changes from 3.9  $\Omega$  to 3.93  $\Omega$  for an 80 °C rise in temperature rise of the 3.9  $\Omega$   $R_{G(ext),on}$  utilised [52]. This effect was examined with the next available  $R_{G(ext),on}$  of 3.96  $\Omega$ . The results in Fig. 11a depict a negligible impact on the chip failure signature of  $V_{GE(pre-th)}$ .

Fig. 11.  $V_{GE}$  behaviour with changes in  $R_{G(ext)}$  and chip failures at 20 °C.

Fig. 11b shows six  $V_{\text{GE}(\text{pre-th})}$  measurements with  $R_{\text{G}(\text{ext}),on}$  of 3.9  $\Omega$  and  $R_{\text{G}(\text{ext}),on}$  of 3.96  $\Omega$  in the baseline, 1 chip failure and 2 chip failure conditions. The maximum error in the 3.9  $\Omega$  and 3.96  $\Omega$  measurements is only 4.5 % and does not have an impact on the chip failure signature of  $V_{\text{GE}(\text{pre-th})}$ .

The sizing of  $R_{G(ext)}$  depends on the application. Fig. 11b includes three  $V_{GE(pre-th)}$  measurements for 5 % increase in  $R_{G(ext),on}$  when it is physically changed to 4.27  $\Omega$ . The results show that only two chip failures can be detected as a  $V_{GE(pre-th)}$  reading of 1.42 V for the first chip failure falls within the baseline threshold and only the 2.2 V reading for two chip failures exceeded the baseline threshold. However, the  $V_{GE(pre-th)}$  reading of 2.2 V for two chip failures with  $R_{G(ext),on}$  of 4.27  $\Omega$  is within the one chip failure threshold of 2.0 V <  $V_{GE(pre-th)}$  < 2.8 for this power module. Hence the chip failure alarm is true, but the prediction is one chip failure rather than two chip failures which is false.

Consequently, it has been concluded that  $V_{GE(pre-th)}$  is highly dependent on  $R_{G(ext)}$ . When the same  $R_{G(ext)}$  is utilised, the impact of temperature changes on  $R_{G(ext)}$  can be ignored. Whereas when  $R_{G(ext)}$  is physically changed, different  $R_{G(ext)}$  values will lead to different results, but the fundamental  $V_{GE(pre-th)}$  principle remains. Therefore any physical change of  $R_{G(ext),on}$  by more than 1 % requires a recalibration of  $V_{GE(pre-th)}$ .

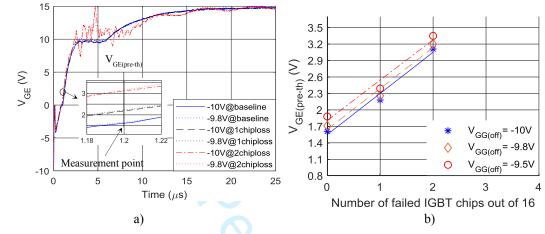

## C. Changes in V<sub>GG</sub>

The impact of changes in the gate driver supply voltage,  $V_{GG}$ , has been investigated due to the relation with  $V_{GE(pre-th)}$  in Eq. (2). The gate driver used includes voltage regulation for a reliable  $V_{GG(on)}$

to +15 V for IGBT turn-on, and -10 V ( $V_{GG(off)}$ ) for IGBT turn-off is not regulated as it provides the compensation when  $V_{GG(on)}$  fluctuates [51]. Eq. (2) shows a direct relation of  $V_{GE(pre-th)}$  with  $V_{GG(off)}$ . Consequently if  $V_{GG(off)}$  varies,  $V_{GE(pre-th)}$  varies too. Given  $V_{GG}$  fluctuation, component tolerances and temperature dependence of the gate driver components, the impact of 2 % and 5 % error on -10 V  $V_{GG(off)}$  resulting in -9.8 V and -9.5 V has been investigated.

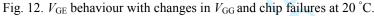

Fig. 12a. shows the voltage waveform for a 2 % change in  $V_{GG(off)}$  and Fig. 12b shows a comparison between 2 % and 5 % error compared to -10V in  $V_{GG(off)}$ . Fig. 12b shows that there is enough margin in  $V_{GE(pre-th)}$  between every chip failure to allow signalling the detection of chip failures. Fig. 12b also shows repeatability in the context of changes in  $V_{GG(off)}$  during two measurements. For example, if voltage fluctuations cause an error of 5 % in  $V_{GG(off)}$  during baseline condition,  $V_{GE(pre-th)}$  is in the order of 1.9 V following Fig. 12b. This is 100 mV under the threshold margin that flags up 1 chip failure as described in section B. If the voltage fluctuation disappears so that  $V_{GG(off)}$  stabilises back to -10 V and a chip has failed during that period then the second  $V_{GE(pre-th)}$  is in the look-up table (2.0 V to 2.8 V). Consequently, the proposed circuit is immune to  $V_{GG(off)}$  fluctuations up to 5 %. If, however, a higher error is expected then a voltage sensor should be added to measure  $V_{GG(off)}$ . This information can then be processed to correct the value of  $V_{GE(pre-th)}$ .

## D. Repeatability

The previous sections have so far demonstrated the impact of  $V_{\text{DC-link}}$ ,  $T_{\text{vj}}$ ,  $R_{\text{G(ext)}}$ ,  $V_{\text{GG(off)}}$  on the  $V_{\text{GE}(\text{pre-th})}$  measurement for one power module to determine chip failures. A second DIM800NSM33-F IGBT power module has been used to show if the proposed method produces the same results in terms of chip failure detection. Fig. 13 shows the measurement results conducted on two DIM800NSM33-F IGBT power modules (Modules A and B). Results at  $T_{\text{vj}}$ =20 °C are portrayed in Fig. 13 where, for the same fixed time delay (1.2µs), the recorded errors are: 4.0 % at baseline, 10.3 % with 1 chip failure and 6.7 % with 2 chip failures. The small differences in errors show that  $V_{\text{GE}(\text{pre-th})} \le 2.8 \text{ V} - 1$  chip failure; and  $V_{\text{GE}(\text{pre-th})} \ge 2.8 \text{ V} - 2$  chip failures.

Fig. 13. Experimental Results of V<sub>GE(pre-th)</sub> on a Different DIM800NSM33-F Power Modules at 20 °C.

VI. VGE(PRE-TH) PRACTICAL IMPLEMENTATION

On the premise of a known baseline value, two methods can normally be carried out for signal acquisition of the  $V_{\text{GE}(\text{pre-th})}$  profile. Firstly, a snapshot measurement of  $V_{\text{GE}(\text{pre-th})}$  can be taken at a fixed time instant corresponding to a pre-defined threshold value during the  $V_{\text{GE}}$  ramping-up. Alternatively, a fixed  $V_{\text{GE}(\text{pre-th})}$  can be related to the lapse in time taken to reach  $V_{\text{GE}(\text{pre-th})}$ . The results obtained in this paper are based on the former method where the time is fixed and  $V_{\text{GE}(\text{pre-th})}$  is measured.

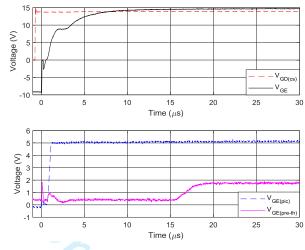

IGBT gate turn-on transients are in the order of hundreds of nanoseconds thus precise measurements necessitate a fast-respond triggering function and high bandwidth Sample-and-Hold (S/H) amplifiers to track the signal. Fig. 14 shows a simplified schematic of the hardware

implementation for  $V_{GE(pre-th)}$  measurement, which was embedded in the DIM800NSM33-F gate driver.

Fig. 14. Schematic of V<sub>GE(pre-th)</sub> measurement circuit for IGBT chip failure monitoring.

Fig. 14 shows the measurement points marked A, B, C and D where  $V_{GD(cs)}$  (gate driver control signal),  $V_{GE}$ ,  $V_{GE(pic)}$  ( $V_{GE}$  analogue input to a programmable interrupt controller (PIC) for  $V_{GE(pre-th)}$  measurement) and D  $V_{GE(pre-th)}$  signals are measured from respectively. The input buffer uses an operational amplifier (op-amp) to ameliorate the source impedance as the first stage in collecting  $V_{GE(pre-th)}$ . The buffer also prevents the  $V_{GE(pre-th)}$  measurement circuit from loading the gate driver. In this way, the gate's normal operation is not affected, and thus the proposed  $V_{GE(pre-th)}$  monitoring interface is suitable for online applications.

An edge detector is also shown in Fig. 14. The gate driver applies -10 V to maintain the off-state of the IGBT. Following a turn-on command, the gate input capacitance is charged by a +15 V gate voltage supply and  $V_{GE}$  starts to rise from -10 V. The edge detector is used to monitor the  $V_{GE}$  rising process and when it reaches -8 V, the edge detector sets off a delay counter in the PIC via a general purpose input-output (GPIO) on the PIC. The PIC utilized is the PIC18F24K22 with a clock speed of 64 MHz. A delay of 1.2 µs has been predetermined to trigger the S/H circuit. After a 1.2 µs delay, an Analogue-to-Digital Converter (ADC) in the PIC measures  $V_{GE(pre-th)}$ . To allow the precise acquisition of  $V_{GE(pre-th)}$  the PIC code enables the ADC module at the same time when the time delay counter is started by the edge detector and configures it ready to measure  $V_{GE(pre-th)}$ . When the 1.2 µs time delay is reached, the  $V_{GE(pre-th)}$  sample is acquired immediately by the ADC. The  $V_{GE(pre-th)}$

#### IEEE-TPEL

technique only requires a single sample at a time. Hence the fast-rising  $V_{GE}$  does not need to be tracked. If assurance is required, the proposed single  $V_{GE(pre-th)}$  measurement process can be repeated. A lookup table is included in the PIC using a simple code with the  $V_{GE(pre-th)}$  threshold values for different IGBT chip failure count. Thus the measured  $V_{GE(pre-th)}$  value, as well as the on-going chip failure count of the IGBT, are provided.

$V_{\text{GE}(\text{pre-th})}$  is more pronounced in the  $V_{\text{GE}}$  region between the zero-crossing and 5 V which are within the voltage rating of the PIC pins. Thus a diode and Zener diode combination has been utilised as shown in Fig. 14 to allow only the  $V_{\text{GE}}$  portion between zero and 5 V to progress through to the PIC. This protects the PIC from overvoltage and negative voltage. Fig. 14 also shows galvanic isolation of the gate driver input as well as the  $V_{\text{GE}(\text{pre-th})}$  output. These isolation barriers are necessary to protect users as well as the associated low voltage components and equipment from the high voltage environment on the IGBT power module's collector-emitter circuit.

# A. $V_{GE(pre-th)}$ measuring techniques

As the proposed  $V_{GE}$  measurement is before the threshold  $V_{GE(th)}$ , at which the IGBT switches on,  $V_{GE(pre-th)}$  measurements can be conducted in two modes: Mode 1 is during the turn-on period that is signalled by the PWM controller, and Mode 2 during the off-state of the IGBT which is determined by the PWM signal. In both cases, the same information about the chip failure(s) can be detected.

1) *Mode 1*

This is when  $V_{\text{GE}(\text{pre-th})}$  measurements are collected online during the normal IGBT switching operation. The IGBT is thus driven normally and  $V_{\text{GE}}$  continues to its full gate voltage of 15 V of the normal duty cycle.

In Fig. 15  $V_{\text{GE}(\text{pre-th})}$  of 1.8 V is successfully measured online in a typical PWM at 20 °C for a healthy power module. The frequency of the PWM is 1 kHz which is typically used in high voltage applications [58]. In each pulse,  $V_{\text{GE}(\text{pre-th})}$  is measured at the required time instant of 1.2 µs after  $V_{\text{GE}}$  starts rising from -10 V. The measured  $V_{\text{GE}(\text{pre-th})}$  is then available approximately 10 µs later after the measurement event which is caused by the processing time of the ADC employed. A faster ADC

may be utilised, but this is not necessary because in health monitoring, wear out failures are gradual and slow compared to switching frequencies thus time can be afforded for processing and transfer of data to a host computer.

Fig. 15. Mode 1 waveforms of  $V_{GE(pre-th)}$  applied during the on-state of the IGBT (duty cycle: 35%).

## 2) *Mode 2*

In this mode the PWM signal is low, and the IGBT is in the off-state. An interrupt routine which determines the health measurement override the off-status of the PWM signal and triggers the gate driver with a duty cycle that allows only enough time to produce the required  $V_{GE}$  transient at which  $V_{GE(pre-th)}$  is measured, and then turning off the IGBT. In this way, the status of  $V_{CE}$  and  $I_C$  is not affected:  $V_{CE}$  remains in the blocking state, thus the switch never turns-on. This mode can be extended to test IGBTs during stand-by where for a longer period of time the devices are off. Fig. 16 shows such a pre-mature  $V_{GE}$  pulse for testing  $V_{GE(pre-th)}$  during the off-time of the IGBT. The pulse lasts only 2µs. Activation of this pre-mature pulse must be considered in the controller. Hence the test is only possible when the IGBT is in the off-state at the end of the pre-mature pulse and before the next PWM pulse. Fig. 16 shows the successful  $V_{GE(pre-th)}$  measurement of 1.8 V at 20 °C for a healthy power module similar to Mode 1 above.

Fig. 16. Mode 2 waveforms of  $V_{GE(pre-th)}$  applied during the off-state of the IGBT (duty cycle: 0.07%).

Table II shows the results using the  $V_{GE(pre-th)}$  measurement circuit in Fig.14. The measurements are conducted on different DIM800NSM33-F IGBT power modules from the same manufacturing batch as the modules tested in section IV. The lookup table is derived from the characterization of the IGBT modules presented in section IV. The results show successful implementation as the correct information about the chip failure count is obtained according to the lookup table.

Table II. IGBT measurements with  $V_{\text{GE}(\text{pre-th})}$  circuit.

|                 |                                  | VGE(pre-th) circuit |            |                         |  |

|-----------------|----------------------------------|---------------------|------------|-------------------------|--|

| Loo             | $V_{\rm GE(pre-th)}({f V})$      |                     | Prediction |                         |  |

|                 |                                  | 20 °C               | 100 °C     | IGBT chip failure count |  |

| Baseline        | $V_{\text{GE(pre-th)}} < 2.0$    | 1.86                | 1.71       | 0                       |  |

| 1 Chip failure  | $2.0 < V_{\rm GE(pre-th)} < 2.8$ | 2.25                | 2.12       | 1                       |  |

| 2 Chip failures | $2.8 < V_{\text{GE(pre-th)}}$    | 3.03                | 2.88       | 2                       |  |

VII. CONCLUSION

A new health sensitive parameter for IGBT chip failure monitoring in multichip IGBT modules was proposed. The method is  $V_{GE(pre-th)}$  which takes place during the  $V_{GE}$  transient for turning on the IGBT.  $V_{GE(pre-th)}$  is measured at a defined time instant between  $V_{GE}$  zero-crossing and the threshold voltage.  $V_{GE(pre-th)}$  thus requires less hardware with only a voltage sensor and a counter. Practical

#### **IEEE-TPEL**

results reveal a good  $V_{\text{GE}(\text{pre-th})}$  performance with IGBT chip failures with an average sensitivity of 500 mV per chip failure.

The hardware implementation of  $V_{GE(pre-th)}$  has been described. Two techniques have been illustrated where an IGBT can be tested during IGBT turn-on as well as during the off-state. In both cases, the same information about number of chip failure(s) can be detected which makes  $V_{GE(pre-th)}$ more versatile than any other health sensitive parameter. The proposed circuit has been successfully implemented on the IGBT gate driver and the correct information about the chip failure count has been obtained. A limitation of the method is that detection of singular bond wires failures are not possible. However, for multichip power modules, the loss of a single or few bond wires will not affect the normal operation or the capability of the power module.

Since it is based on the low voltage gate side rather than the high voltage collector side of the IGBT,  $V_{GE(pre-th)}$  does not require high voltage isolation nor high voltage insulation.  $V_{GE(pre-th)}$  shows a good temperature immunity and high sensitivity to chip failures. However,  $V_{GE(pre-th)}$  is highly dependent on  $R_{G(ext)}$ . While the impact of temperature changes on  $R_{G(ext)}$  can be ignored, the physical alteration of  $R_{G(ext)}$  in excess of 1% requires a re-calibration of  $V_{GE(pre-th)}$ . Other influences like gate driver voltage fluctuations have also been investigated. The method performs well with a 5% fluctuation in  $V_{GG(off)}$ .

$V_{\text{GE}(\text{pre-th})}$  is applicable to standard multichip IGBT power modules such as 3.3 kV, 4.5 kV and 6.5 kV IGBT modules as they have similar structures. Future work will aim to demonstrate the performance of  $V_{\text{GE}(\text{pre-th})}$  in an operative converter configuration.

#### References

- [1] N. Y. A. Shammas, M. P. Rodriguez, A. T. Plumpton, and D. Newcombe, "Finite element modelling of thermal fatigue effects in IGBT modules," *IEE Proceedings-Circuits, Devices and Systems,* vol. 148, pp. 95-100, 2001.

- [2] J. Azemar, "IGBT technology, market overview & Wide band gap prospects," *Yole Développement,* 2013.

[3] M. Rahimo and S. Klaka, "High voltage semiconductor technologies," in *Power Electronics and Applications, 2009. EPE'09. 13th European Conference on, 2009, pp. 1-10.*

[4] M. A. Rodriguez, A. Claudio, D. Theilliol, and L. G. Vela, "A new fault detection technique for IGBT based on gate voltage monitoring," in *Power Electronics Specialists Conference*, 2007. *PESC 2007. IEEE*, 2007, pp. 1001-1005.

- [5] P. Ghimire, A. de Vega, S. Beczkowski, B. Rannestad, S. Munk-Nielsen, and P. Thogersen, "Improving Power Converter Reliability: Online Monitoring of High-Power IGBT Modules," *Industrial Electronics Magazine, IEEE*, vol. 8, pp. 40-50, 2014.

- [6] Y.-S. Kim and S.-K. Sul, "On-line estimation of IGBT junction temperature using on-state voltage drop," in *Industry Applications Conference, 1998. Thirty-Third IAS Annual Meeting. The 1998 IEEE*, 1998, pp. 853-859.

- [7] P. Ghimire, A. R. de Vega, S. Beczkowski, S. Munk-Nielsen, B. Rannested, and P. B. Thogersen, "An online V ce measurement and temperature estimation method for high power IGBT module in normal PWM operation," in *Power Electronics Conference (IPEC-Hiroshima 2014-ECCE-ASIA), 2014 International*, 2014, pp. 2850-2855.

- [8] B. Strauss and A. Lindemann, "Indirect measurement of junction temperature for condition monitoring of power semiconductor devices during operation," in *PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of*, 2015, pp. 1-6.

- [9] I. Bahun, N. Čobanov, and Ž. Jakopović, "Real-Time Measurement of IGBT's Operating Temperature," *AUTOMATIKA: časopis za automatiku, mjerenje, elektroniku, računarstvo i komunikacije,* vol. 52, pp. 295-305, 2012.

- [10] D. Barlini, M. Ciappa, A. Castellazzi, M. Mermet-Guyennet, and W. Fichtner, "New technique for the measurement of the static and of the transient junction temperature in IGBT devices under operating conditions," *Microelectronics Reliability*, vol. 46, pp. 1772-1777, 2006.

- [11] H. Kuhn and A. Mertens, "On-line junction temperature measurement of IGBTs based on temperature sensitive electrical parameters," in *Power Electronics and Applications, 2009. EPE'09. 13th European Conference on*, 2009, pp. 1-10.

- [12] W. Brekel, T. Duetemeyer, G. Puk, and O. Schilling, "Time resolved in situ Tvj measurements of 6.5 kV IGBTs during inverter operation," *Proc. PCIM Europe 2009*, 2009.

- [13] E. Hoene, T. Baumann, and O. Zeiter, "Device for measuring a temperature of a power semiconductor," ed: Google Patents, 2013.

- [14] M. Denk and M.-M. Bakran, "An IGBT Driver Concept with Integrated Real-Time Junction Temperature Measurement," in *PCIM Europe 2014; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of*, 2014, pp. 1-8.

- [15] C. Felgemacher, B. Dombert, C. Noeding, and P. Zacharias, "IGBT Online-Temperature Monitoring using Turn-Off Delay as a Temperature Sensitive Electrical Parameter," in *CIPS 2016; 9th International Conference on Integrated Power Electronics Systems; Proceedings of*, 2016, pp. 1-6.

- [16] D. Bergogne, B. Allard, and H. Morel, "An estimation method of the channel temperature of power MOS devices," in *Power Electronics Specialists Conference*, 2000. PESC 00. 2000 IEEE 31st Annual, 2000, pp. 1594-1599.

- [17] V. K. Sundaramoorthy, E. Bianda, R. Bloch, and F. Zurfluh, "Simultaneous online estimation of junction temperature and current of IGBTs using emitter-auxiliary emitter parasitic inductance," in *PCIM Europe 2014; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of*, 2014, pp. 1-8.

- [18] D. Xu, H. Lu, L. Huang, S. Azuma, M. Kimata, and R. Uchida, "Power loss and junction temperature analysis of power semiconductor devices," *Industry Applications, IEEE Transactions on,* vol. 38, pp. 1426-1431, 2002.

- [19] M. Musallam, C. Buttay, M. Whitehead, and C. M. Johnson, "Real-time compact electronic thermal modelling for health monitoring," in *Power Electronics and Applications, 2007 European Conference on*, 2007, pp. 1-10.

- [20] B. Tian, W. Qiao, Z. Wang, T. Gachovska, and J. L. Hudgins, "Monitoring IGBT's health condition via junction temperature variations," in *Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE*, 2014, pp. 2550-2555.

- [21] M. A. Eleffendi and C. M. Johnson, "Application of Kalman filter to estimate junction temperature in IGBT power modules," *Power Electronics, IEEE Transactions on*, vol. 31, pp. 1576-1587, 2016.

- [22] E. Farjah and R. Perret, "Application and analysis of thermosensitive parameters in the case of hybrid power modules," in *Industry Applications Society Annual Meeting, 1994., Conference Record of the 1994 IEEE*, 1994, pp. 1284-1289.

- [23] V. K. Sundaramoorthy, E. Bianda, M. Kamel, G. J. Riedel, and I. Nistor, "Online junction temperature estimation for IGBT modules with paralleled semiconductor chips," in *Power Electronics, Machines and Drives (PEMD 2014), 7th IET International Conference on*, 2014, pp. 1-5.

- [24] R. Moeini, P. Tricoli, H. Hemida, and C. Baniotopoulos, "Increasing the reliability of wind turbines using condition monitoring of semiconductor devices: a review," *IET Renewable Power Generation*, vol. 12, pp. 182-189, 2018.

- [25] M. Denk and M. M. Bakran, "Comparison of UCE and RGi based junction temperature measurement of multichip IGBT power modules," in *Power Electronics and Applications (EPE'15 ECCE-Europe)*, 2015 17th European Conference on, 2015, pp. 1-11.

- [26] M. Denk and M. M. Bakran, "IGBT Gate Driver with Accurate Measurement of Junction Temperature and Inverter Output Current," in *PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, 2017, pp. 1-8.

- [27] H. Luo, W. Li, F. Iannuzzo, X. He, and F. Blaabjerg, "Enabling Junction Temperature Estimation via Collector-Side Thermo-Sensitive Electrical Parameters Through Emitter Stray Inductance in High-Power IGBT Modules," *IEEE Transactions on Industrial Electronics*, vol. 65, pp. 4724-4738, 2018.

- [28] N. Baker and F. Iannuzzo, "The Temperature Dependence of the Flatband Voltage in High Power IGBTs," *IEEE Transactions on Industrial Electronics*, pp. 1-1, 2018.

- [29] Y. Xiong, X. Cheng, Z. J. Shen, C. Mi, H. Wu, and V. K. Garg, "Prognostic and warning system for power-electronic modules in electric, hybrid electric, and fuel-cell vehicles," *Industrial Electronics, IEEE Transactions on*, vol. 55, pp. 2268-2276, 2008.

- [30] P. L. Evans, A. Castellazzi, and C. M. Johnson, "Design Tools for Rapid Multidomain Virtual Prototyping of Power Electronic Systems," *IEEE Transactions on Power Electronics*, vol. 31, pp. 2443-2455, 2016.

- [31] N. Patil, J. Celaya, D. Das, K. Goebel, and M. Pecht, "Precursor parameter identification for insulated gate bipolar transistor (IGBT) prognostics," *IEEE Transactions on Reliability*, vol. 58, pp. 271-276, 2009.

- [32] D. W. Brown, M. Abbas, A. Ginart, I. N. Ali, P. W. Kalgren, and G. J. Vachtsevanos, "Turn-off time as an early indicator of insulated gate bipolar transistor latch-up," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 479-489, 2012.

- [33] B. Ji, V. Pickert, W. Cao, and B. Zahawi, "In situ diagnostics and prognostics of wire bonding faults in IGBT modules for electric vehicle drives," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 5568-5577, 2013.

- [34] V. Smet, F. Forest, J.-J. Huselstein, A. Rashed, and F. Richardeau, "Evaluation of Vce Monitoring as a Real-Time Method to Estimate Aging of Bond Wire-IGBT Modules Stressed by Power Cycling," *IEEE Transactions on Industrial Electronics*, vol. 60, pp. 2760-2770, 2013.

- [35] Y. Avenas, L. Dupont, N. Baker, H. Zara, and F. Barruel, "Condition Monitoring: A Decade of Proposed Techniques," *IEEE Industrial Electronics Magazine*, vol. 9, pp. 22-36, 2015.

- [36] M. A. Eleffendi and C. M. Johnson, "In-Service Diagnostics for Wire-Bond Lift-off and Solder Fatigue of Power Semiconductor Packages," *IEEE Transactions on Power Electronics*, vol. 32, pp. 7187-7198, 2017.

- [37] A. Singh, A. Anurag, and S. Anand, "Evaluation of Vce at Inflection Point for Monitoring Bond Wire Degradation in Discrete Packaged IGBTs," *IEEE Transactions on Power Electronics*, vol. 32, pp. 2481-2484, 2017.

- [38] W. Kexin, D. Mingxing, X. Linlin, and L. Jian, "Study of Bonding Wire Failure Effects on External Measurable Signals of IGBT Module," *IEEE Transactions on Device and Materials Reliability*, vol. 14, pp. 83-89, 2014.

- [39] M. Dbeiss, Y. Avenas, H. Zara, and L. Dupont, "In-situ condition monitoring system to study the ageing of power semi-conductor devices in photovoltaic inverters," in CIPS 2018; 10th International Conference on Integrated Power Electronics Systems, 2018, pp. 1-6.

- [40] !!! INVALID CITATION !!! [33-40].

- [41] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An industry-based survey of reliability in power electronic converters," *Industry Applications, IEEE Transactions on*, vol. 47, pp. 1441-1451, 2011.

- [42] H. Oh, B. Han, P. McCluskey, C. Han, and B. D. Youn, "Physics-of-Failure, Condition Monitoring and Prognostics of Insulated Gate Bipolar Transistor Modules: A Review," 2015.

- [43] G. Lefranc, T. Licht, H. J. Schultz, R. Beinert, and G. Mitic, "Reliability testing of high-power multichip IGBT modules," *Microelectronics reliability*, vol. 40, pp. 1659-1663, 2000.

IEEE-TPEL

- [44] "Dynex 3.3kV, 800A IGBT Module DIM800NSM33-F000," Dynex Datasheet, 2014.

- [45] S. Zhou, L. Zhou, and P. Sun, "Monitoring potential defects in an IGBT module based on dynamic changes of the gate current," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 1479-1487, 2013.

- [46] S. Zhou, L. Zhou, and P. Sun, "Monitoring Potential Defects in an IGBT Module Based on Dynamic Changes of the Gate Current," *IEEE Transactions on Power Electronics*, vol. 28, pp. 1479-1487, 2013.

- [47] N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, and M. Liserre, "IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current," *IEEE Transactions on Power Electronics*, vol. 32, pp. 3099-3111, 2017.

- [48] N. Baker, S. Munk-Nielsen, F. Iannuzzo, and M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," *Power Electronics, IEEE Transactions on*, vol. 31, pp. 3784-3793, 2016.

- [49] "2SC0535T2A1-33 Gate Driver Core Description and Application manual, Version 2," *Concept Technologies*, 2014.

- [50] IGBT Gate Driver 2BB0535T Application Manual [Online]. Available: https://www.power.com/sites/default/files/product\_document/application\_manual/2BB0535T\_Manu al.pdf Accessed 1 June 2016

- [51] C. P. Integrations, "IGBT Gate Driver Application Note AN-1101," *Power Integrations*, June 2018 2018.

- [52] "Standard Thick Film Chip Resistors Datasheet, Vishay, Document Number 20035 " 2012.

- [53] "Thermocouple Datasheet, Type K Washer," 2017.

- [54] D. D. J. Carr, J. Li, J. Pan, S. Ebner, and O. Apeldoorn, "Modular multilevel converter for direct MVDC connection of offshore wind farms," *Proc. 2015 IEEE Energy Convers. Congr. Expo. (ECCE)*, pp. 976-982, 20-24 Sept. 2015.

- [55] B. Wang, Y. Tang, and M. Chen, "Study on Electric Characteristic of IGBT at Different Junction Temperature," in *Power and Energy Engineering Conference (APPEEC), 2011 Asia-Pacific*, 2011, pp. 1-4.

- [56] S. M. Sze, Semiconductor devices: physics and technology: John Wiley & Sons, 2008.

- [57] R. Mandeya, C. Chen, V. Pickert, and R. T. Naayagi, "Pre-threshold Voltage as a Low Component Count Temperature Sensitive Electrical Parameter without Self-Heating," *IEEE Transactions on Power Electronics*, 2017.

- [58] K. Kondo, "Recent energy saving technologies on railway traction systems," *IEEJ Transactions on Electrical and Electronic Engineering*, vol. 5, pp. 298-303, 2010.

ien

##

# Reviewer 1

We like to say thank you to Reviewer 1 in reading our manuscript and in providing us with helpful information to improve the paper. We have in-cooperated all of your comments.

Recommendation: Revision – The paper is not accepted, but authors are given one chance to respond to reviewers' comments with a revision in 6 weeks or less.

# Comments:

The paper deals with a very hot topic and presents a new method to estimate the degradation of high power IGBT modules. This method seems to be very attractive because it is very simple to implement. The sensitivity is good allowing for simple measurements. However, I think that lots of improvements must be made prior to publish it in this journal.

Introduction:

- for me it is too long.

We have shortened the introduction section.

- I don't understand why the authors present lots of papers on junction temperature measurements because the paper is not focused on this topic.

We agree that we added too many references for TSEPs. We, therefore, reduced the TSEP references.

- On the contrary, Table I seems to be poor and very few references on health monitoring methods are given.

We have added more references on health monitoring methods and improved the table. The table now compares the techniques proposed for bond wire failure and chip failure detection which are common in IGBT health monitoring.

-p3, line 56: "Collector" instead of "collector"

We thank the Reviewer for picking this up and have changed it accordingly.

Section II:

-I don't see the interest of Fig. 2,

Originally, we wanted to illustrate the general operation procedure of the health monitoring technique. We agree that this is confusing and consequently deleted the figure.

-you don' speak about diodes but they are present in the module. Could you explain why?

The work focusses only on health monitoring of IGBT chips. We now highlighted this in the title and added a sentence in the abstract, the introduction and section IV. We have also explained why we focus on IGBT chips rather diode chips. The main reason is that IGBT chips experience higher thermal stresses compared to diodes hence IGBT chips are more susceptible to failures compared to diode chips.

-you have a A. paragraph but not a B.

Thank you for spotting this. We deleted A. paragraph.

-you dont speak about the temperature dependency of all these parameters which is, for me, a real issue.

We agree with the Reviewer that the temperature dependency of all the existing techniques is an important factor and it should be considered when assessing performance of the methods. Therefore, additional features are added in Table I to show the temperature dependency of the techniques and the impact of the temperature dependency on their ability to detect bond wires or chip failures. In addition, we also compared the immunity to  $T_{vj}$  variation of all these techniques. An additional illustration is also included.

-a table could be interesting to compare all these parameters with yours.

We agree with the Reviewer that a table is necessary to compare the techniques. As the methods are measured in different units, we have added a technique to normalise their sensitivities to relative sensitivities and then compared them using Table I. The existing techniques which are  $V_{CE(on)}$ ,  $I_{G(peak)}$ ,  $R_{CE(on)}$  and  $dV_{CE}/dt$  are then analysed according to the following aspects: the number of IGBT chips of the device under test, relative sensitivity of the HSP for bond wire failure, relative sensitivity the HSP for  $T_{ij}$  as well as their immunity to  $T_{ij}$  variation in section. We then made a comparison with  $I_{Clpeak}$ ) which detect chips and is comparable with the proposed technique in section IV. We concluded that both methods have has a strong immunity to  $T_{ij}$  and the main advantage of the proposed method,  $V_{CE(pre-th)}$ , over  $I_{Clpeak}$  is that  $V_{GE(pre-th)}$  employs a voltage sensor while  $I_{Clpeak}$  utilises a current sensor. And in general,

IEEE-TPEL

voltage sensors are cheaper, simpler and lightweight compared to current sensors hence voltage-based HSPs are preferred from a practical perspective.

Section III. -Fig. 6 is unreadable,

We agree that the quality of the figure is not good. The result presented is from a Saber simulation. The simulation work has been taken out in the revised manuscript. Thus the figure has been deleted.

- p9 line 23: why do you speak about a new TSEP?

Thank you for spotting this. We mean HSP instead of TSEP. Thus TSEP has changed to HSP.

-what is the interest of eq. 2 in this paper?

The equation is used to illustrate the relationship between the virtual junction temperature, Tvj, and the baseplate temperature, Tc. We want to show that the virtual junction temperature can be varied from the baseplate as they are related in Eq. 2. Assuming power loss of a single switching transient is minimal. Hence Pd is small, we assume that Tvj=Tc. Therefore, in the tests, a temperature controlled heat plate was utilised to alter Tvj.

-is the Rgint variation with the temperature implemented in Saber? Why have you not the same temperature dependency here compared with the experiments?

The simulation has been taken out in the revised manuscript. We have added some experimental results on the impact of temperature changes.

- Are simulations necessary? The use of eq. 1 is not sufficient to demonstrate the main results?

We agree that simulations are not essential hence simulations have been taken out. We have added more theoretical analysis to explain the main results.

-finally, I don't understand the interest of the simulation section because you don't compare the results with the experimental ones.

We agree that simulations are not essential and consequently are taken out in the revised manuscript.

Section IV: -generally, the quality of the figures has to be largely improved

## We have improved the quality of the figures.

-p12, line 32, could you be more specific about the "low temperature tolerance"? Are these resistances classically used to drive power modules?

We thank the reviewer for picking this up. It is a terminology error, which should have been resistance tolerance. This is now corrected and the wording has been improved.

Yes, and we have improved the statement by stating that the film surface resistors 1206 are recommended in gate driver datasheets and are common in gate driver circuits due to attractive features such as low resistance tolerance.

-p13: you give voltage variations due to IGBT loss. Could you compare these variations with theoretical ones? Why this voltage variation is not the same for the first and the second losses?

The equal voltages for one or two chip losses scenarios align with theoretical analysis since we have improved the discussions of results with more analysis linking results with theory. We have included more tests results which show that the variation of the first and second chip losses are generally the same.

-p14: you write that voltage drop due to temperature variation is negligible. I don't agree: the variation is 0.2V after the second loss which is not far away from the temperature drop due to the loss itself (0.5V)! Maybe if you would have used another power module, the result could be completely different.

Initially, we want to illustrate the immunity of  $V_{GE(pre-th)}$  to temperature. We mean that the change of  $V_{GE(pre-th)}$  over 80°C temperature variation is about 0.2V. The change of  $V_{GE(pre-th)}$  at one chip loss is more than 0.2V, about 0.5V on average. This means that the temperature variation will not affect the chip failure detection. Now we have largely improved the temperature analysis to make the temperature dependence clear as it is crucial. We included more test results and demonstrated that the proposed method performs well even when there are temperature changes in the IGBT module.

IEEE-TPEL

- About this variation with temperature: why do you have this variation, what is the physical explanation? Why do you have different simulation results?

In general, the HSPs are temperature dependent which means temperature variation will lead to change in HSP. As we know, bond wire and chip failures also lead to changes in HSP. Therefore, we want to include the discussion about the temperature dependency of the HSP and to verify that the temperature dependency of the proposed  $V_{GE(pre-th)}$  approach will not influence the bond wire and chip failure detection. We have shown more results and explained their link to the theory, to make the temperature dependence discussion clear.

The simulation results do not coincide with the experimental results which can be accounted to inaccurate simulation model of the real device tested. We have taken out the simulation and added more experimental results, and demonstrated that the proposed methods performs well even when there is temperature changes in the IGBT module.

-Fig. 11: could you explain the shape of the waveform: they are completely different from the shapes obtained in simulation?

We admit that the simulation results do not coincide with the experimental results. The simulation results displayed in the original paper are only part of the switching waveform. The overall switching waveform shows the same tendency as the experimental results. As simulation results have been taken out, we added more explanation about why the  $V_{GE}$  trajectory changes when there are bond wire failure and junction temperature change in section IV and section V. We have also added more experimental results and linked them with the theory.

-Fig. 15 and 16: are they experimental or simulation results? In the case of experimental results, give the measurement points.

Fig. 15 and 16 are simulation results. We have replaced them since simulation have been taken out. We added Fig.9 to illustrate the immunity of  $V_{GE(pre-th)}$  to the DC-link voltage. More analysis has been included in the revised manuscript. Fig.16 is replaced with experimental results shown in Fig.12. The measurement points have also been highlighted in the results.

- Why do you test the influence of  $V_{DC}$ ? Please explain the physical impact of this voltage.

The relationship between  $V_{DC}$  and the waveform of  $V_{GE(pre-th)}$  is explained in section V. The analysis shows that  $V_{GE(pre-th)}$  has good immunity to the DC-link voltage.

-why do you not study the influence of Rgext?

We thank the reviewer for noticing this. As we know, the change of the gate resistor will vary the switching speed of the IGBT module. Hence, the measurement point of the  $V_{\text{GE}(\text{pre-th})}$  will change, which makes the voltage at fixed time instant incomparable when the external resistor is not the same. However, it is important to investigate the influence of the  $R_{\text{G}(\text{ext})}$ . Now, we have highlighted the need to examine the influence of changes in  $R_{\text{G}(\text{ext})}$  as the equation of the method shows a relation with  $R_{\text{G}(\text{ext})}$ . We have included a section with the study and experimental results of the impact of  $R_{\text{G}(\text{ext})}$  impact. We have concluded that  $V_{\text{GE}(\text{pre-th})}$  is highly dependent on  $R_{\text{G}(\text{ext})}$ . However, when the same  $R_{\text{G}(\text{ext})}$  is utilised, the impact of temperature changes on  $R_{\text{G}(\text{ext})}$  can be ignored. Whereas when  $R_{\text{G}(\text{ext})}$  is physically changed, different  $R_{\text{G}(\text{ext})}$  values will lead to different results, but the fundamental  $V_{\text{GE}(\text{pre-th})}$  principal remains. Therefore we recommended that any physical change of  $R_{\text{G}(\text{ext})}$  of more than 1% require recalibration of  $V_{\text{GE}(\text{pre-th})}$ .

-some information about repeatability should be interesting.

We have included a section about the repeatability of the proposed method and defined the repeatability in the revised manuscript. Practical results and analysis have also been presented which show that the proposed method is repeatable.

Section V. -I don't understand the interest of Fig. 18 and 19,

We agree and have removed both figures as the information has already been shown in other figures.

- The scales of Fig. 20 and 22 are not adapted

We have improved the figures and shown results for both figures on better scales. Now they are Fig.15 and Fig.16.

- Some information about repeatability? What is the difference between two consecutive measurements? Is an averaging necessary or not?

We have included a section on repeatability of the proposed method and defined repeatability in the revised manuscript. We have included practical results and analysis to exhibit that the proposed method is repeatable. We have demonstrated the application procedure of the proposed approach in section VI.

-p21: I don't understand your comments about the 5% measurement error. I understood that you worked with a 5V ADC 10 bits --> resolution 5mV very far from 5%.

We thank the reviewers for picking this up. It should be 0.1%. In the revised manuscript we have taken a different approach to discuss the results as the 10-bit ADC had no impact on the results. We have demonstrated the application and measuring procedure of the proposed approach in section VI. We have added section on repeatability and shown that the proposed method is repeatable.

-the implementation is not complete --> you have to explain how you find a chip loss in online conditions.

The implementation section has been improved to show how the lookup tables, the PIC and the ADC were utilised. We have shown successful implementation of the online chip loss monitoring circuit in a commercially available IGBT gate driver.

## Reviewer 2

We like to say thank you to Reviewer 2 in reading our manuscript and in providing us with helpful information to improve the paper. We have in-cooperated all of your comments.

Major comments

\_\_\_\_\_

Please, include in Table I some more relevant references as below:

Y. Avenas et al., "Condition Monitoring: A Decade of Proposed Techniques," in IEEE Industrial Electronics Magazine, vol. 9, no. 4, pp. 22-36, Dec. 2015.

M. Dbeiss et al., "In-situ condition monitoring system to study the ageing of power semiconductor devices in photovoltaic inverters," CIPS 2018; 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 2018, pp. 1-6.

Moreover, among temperature monitoring techniques (Refs [15-36]) also include:

H. Luo et al., "Enabling Junction Temperature Estimation via Collector-Side Thermo-Sensitive Electrical Parameters Through Emitter Stray Inductance in High-Power IGBT Modules," in IEEE Transactions on Industrial Electronics, vol. 65, no. 6, pp. 4724-4738, June 2018.

N. Baker et al., "The Temperature Dependence of the Flatband Voltage in High Power IGBTs," in IEEE Transactions on Industrial Electronics. doi: 10.1109/TIE.2018.2854568 Peak gate current measurements:

N. Baker et al., "IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol. 32, no. 4, pp. 3099-3111, April 2017.

N. Baker et al., "IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol. 31, no. 5, pp. 3784-3793, May 2016.

Delay time on the gate side:

H. Luo et al., "Enabling Junction Temperature Estimation via Collector-Side Thermo-Sensitive Electrical Parameters Through Emitter Stray Inductance in High-Power IGBT Modules," in IEEE Transactions on Industrial Electronics, vol. 65, no. 6, pp. 4724-4738, June 2018.

We thank the Reviewer for providing the useful references. We have added the references accordingly.

Equation (1) is wrong. The asymptotic value of the first phase of a turn on is VGG(on), which means that VGE(th) must be replaced with VGG(on) in that equation.

The equation is to illustrate the waveform of the gate-emitter voltage before the threshold voltage. Therefore,  $V_{GE(th)}$  is used. The  $V_{GG(on)}$  is not used due to the fact that there is Miller plateau after the threshold point which makes the equation not applicable for the behaviour after Miller plateau. We have added this discussion in the revised manuscript.

The founding assumption of the present work must be better clarified:

"In the case of the loss of bond wire connections to an IGBT chip or some number of chips, the effective inter-chip connection will be altered resulting in a corresponding decline in Cies, total and a rise in RG(int),total." Indeed, the authors refer to complete chip lift off, i.e. isolation of a whole chip emitter, not to single bond wire lift-off, which cannot be detected with their method. The authors need to state clearly this intrinsic limitation of their approach.

We agree with the Reviewer. The proposed method does have the limitation as it cannot detect single bond wire failure. We have included the limitation in the revised manuscript. We have also shown that in multichip power modules the detection of the first few bond wires lift-off is not practical and is not critical as the module could still operate. For that reason, chip failure is an attractive failure precursor compared to a single bond wire lift-off for power modules with a very large number of chips.

#### IEEE-TPEL

The impact of changes in VGG is to be investigated deeper, as it is very crucial to the measurement success. The sentence "has a negligible impact on VGE(pre-th) which can be ignored." is not at all satisfactory, and needs quantitative proof of evidence. Moreover, the claimed 2% temperature compensation has nothing to do with VGG(off) stability, which is indeed the most crucial one. According to my experience, gate drivers, and Concept ones among them, DO NOT provide any regulation of VGG(off).

We have highlighted the need to examine  $V_{GG}$  in the revised manuscript as the equation shows a direct relation with  $V_{GG(off)}$ . The gate driver used has an on board regulation for +15V but -10V is not regulated, when +15Vdc drops down the -10V rail will provide the compensation. We have now included this discussion in the revised manuscript and supported with a reference of the gate driver application note.

We have added experimental results and shown that the proposed method performs well with a stringent 5 % maximum fluctuation of  $V_{GG(off)}$  and we have recommended that for gate drivers operating with larger error, a voltage sensor should be added to determine if the same  $V_{GG}$  conditions are met when measuring  $V_{GE(pre-th)}$ .

The time scale of Fig. 8 is obviously not realistic and anyhow not the same as the experimental ones of Fig. 11 and 14. Please, comment.

Fig. 8 was results from simulations and Reviewer 1 also echoed to value of adding simulation work. We have therefore taken out all of the simulation work in the revised manuscript.