## Gate-Recessed InAlN/GaN HEMTs on SiC Substrate With Al[subscript 2]0[subscript 3] Passivation

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation     | Chung, J.W. et al. "Gate-Recessed InAlN/GaN HEMTs on SiC<br>Substrate With Al[subscript 2]0[subscript 3] Passivation." Electron<br>Device Letters, IEEE 30.9 (2009): 904-906. © 2009 Institute of<br>Electrical and Electronics Engineers. |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| As Published | http://dx.doi.org/10.1109/led.2009.2026718                                                                                                                                                                                                 |

| Publisher    | Institute of Electrical and Electronics Engineers                                                                                                                                                                                          |

| Version      | Final published version                                                                                                                                                                                                                    |

| Citable link | http://hdl.handle.net/1721.1/55351                                                                                                                                                                                                         |

| Terms of Use | Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use.                                                                         |

# Gate-Recessed InAlN/GaN HEMTs on SiC Substrate With Al<sub>2</sub>O<sub>3</sub> Passivation

Jinwook W. Chung, Omair I. Saadat, Jose M. Tirado, Xiang Gao, Shiping Guo, and Tomás Palacios, Member, IEEE

Abstract—We studied submicrometer ( $L_G = 0.15-0.25 \ \mu m$ ) gate-recessed InAlN/AlN/GaN high-electron mobility transistors (HEMTs) on SiC substrates with 25-nm Al<sub>2</sub>O<sub>3</sub> passivation. The combination of a low-damage gate-recess technology and the low sheet resistance of the InAlN/AlN/GaN structure resulted in HEMTs with a maximum dc output current density of  $I_{\rm DS,max} = 1.5$  A/mm and a record peak extrinsic transconductance of  $g_{m,\rm ext} = 675$  mS/mm. The thin Al<sub>2</sub>O<sub>3</sub> passivation improved the sheet resistance and the transconductance of these devices by 15% and 25%, respectively, at the same time that it effectively suppressed current collapse.

*Index Terms*—Al<sub>2</sub>O<sub>3</sub> passivation, GaN, gate recess, highelectron mobility transistor (HEMT), high transconductance, InAlN, SiC substrate.

#### I. INTRODUCTION

**F** OR SOLID-STATE power amplifiers, AlGaN/GaN highelectron mobility transistors (HEMTs) have become one of the most important options. These devices have already demonstrated outstanding performance, including output power densities in excess of 32 W/mm at 4 GHz [1] and more than 10 W/mm at 40 GHz [2]. However, several important challenges need to be overcome to increase the performance of these devices even further, including long-term device reliability, minimization of short-channel effects in deeply scaled devices, and reduction of the parasitic capacitances introduced by Si<sub>x</sub>N<sub>y</sub> passivation layers. InAlN/GaN HEMTs have the potential to overcome all these challenges.

Several authors have related the poor reliability of AlGaN/ GaN devices to lattice defects introduced by the stress resulting from highly mismatched AlGaN/GaN heterojunctions [3], [4].  $In_{0.17}Al_{0.83}N$  can be grown lattice matched to GaN [5], thus reducing the defect density due to stress in the barrier layer. In addition, the InAlN barrier normally has higher polarization than the standard AlGaN barrier, which results in higher output current density and power density. DC output current densities

Manuscript received June 2, 2009; revised June 16, 2009. First published July 31, 2009; current version published August 27, 2009. This work was supported in part by the Office of Naval Research MINE MURI Program monitored by Dr. Dietrich and Dr. Maki and in part by the Air Force Research Laboratory under Contract FA8650-08-C-1443 monitored by Dr. A. Crespo. The work of J. W. Chung was supported by the Korea Foundation for Advanced Studies. The review of this letter was arranged by Editor G. Meneghesso.

J. W. Chung, O. I. Saadat, J. M. Tirado, and T. Palacios are with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: wilchung@mit.edu; oisaadat@mit.edu; JoseMaria.Tirado@uclm.es; tpalacios@mit.edu).

X. Gao and S. Guo are with IQE RF LLC, Somerset, NJ 08873 USA (e-mail: xgao@iqep.com; sguo@iqep.com).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2009.2026718

of 2.3 A/mm have already been reported with 13-nm-thick In<sub>0.19</sub>Al<sub>0.81</sub>N ( $n_s = 2.5 \times 10^{13}$  cm<sup>-2</sup>, 1170 cm<sup>2</sup>/V · s) [6]. In addition, the thickness of the InAlN barrier can be reduced below 10 nm without a significant degradation of the 2-D electron gas density ( $n_s = 1.7 \times 10^{13}$  cm<sup>-2</sup>) [5]. The combination of large current densities and thin barrier layers is very attractive for high-frequency operation as it reduces short-channel effects in transistors with gate lengths below 100 nm.

Surface passivation is another important challenge in highfrequency nitride transistors.  $Si_xN_y$  passivation has commonly been used to mitigate current collapse in AlGaN/GaN and InAlN/GaN transistors [6]; however, the large thickness normally required for the  $Si_xN_y$  passivation (>100 nm) significantly degrades the high-frequency operation of the device by increasing total gate capacitances [7]. Therefore, for future high-frequency devices, a new surface passivation scheme needs to be developed with thinner layers.

In this letter, we demonstrate submicrometer gate-recessed InAlN/GaN HEMTs on SiC substrates with a novel 25-nm  $Al_2O_3$  passivation. The low-damage gate recess allowed a reduction in the gate-to-channel distance down to 3 nm and a record transconductance of 675 mS/mm in 0.15- $\mu$ m gate-length HEMTs. The thin  $Al_2O_3$  passivation effectively removed dispersion and improved transport properties in the channel. No current collapse was observed under 200-ns gate-pulse measurements.

### II. DEVICE FABRICATION

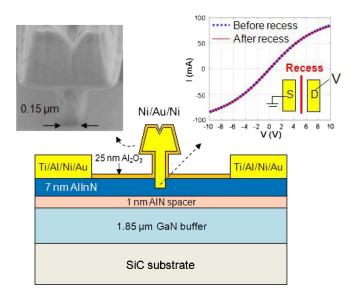

Fig. 1 shows a schematic cross section of one of the InAlN/GaN HEMTs fabricated in this letter. The InAlN/GaN transistor structures were grown on SiC substrates by metal–organic chemical vapor deposition at IQE RF LLC. In these samples, the InAlN barrier had a total thickness of 7 nm and an Al composition of 81%. A 1-nm AlN interlayer between the GaN channel and the InAlN barrier is used to improve the surface morphology and to increase the electron mobility in the channel by reducing the alloy-related interface roughness and scattering [5]. A total charge density of  $1.7 \times 10^{13}$ /cm<sup>2</sup>, an electron mobility of 1060 cm<sup>2</sup>/V · s, and a sheet resistance of 325  $\Omega$ /square were measured for unpassivated samples using van der Pauw structures at room temperature.

The InAlN/GaN HEMTs were fabricated by first depositing a Ti/Al/Ni/Au metal stack for the ohmic contacts followed by annealing at 870 °C for 30 s in a N<sub>2</sub> atmosphere. The source-todrain distance was 2  $\mu$ m in all the devices. Then, mesaisolation was performed with a Cl<sub>2</sub>/BCl<sub>3</sub> plasma. Electron-beam lithography was used to define a T-shaped gate, using a trilayer resist

0741-3106/\$26.00 © 2009 IEEE

Fig. 1. Schematic cross section of an InAlN/GaN HEMT used in this letter. The left inset shows a scanning electron micrograph of the cross section of a 0.15- $\mu$ m-length T-shape gate. The right inset shows the current between source and drain contacts after the gate recess. No degradation was observed.

stack made of PMMA/Copolymer/PMMA. For the gate recess, a low-power electron cyclotron resonance reactive ion etching with  $Cl_2/BCl_3$  gas mixture was used. To minimize the damage induced by ion bombardment, radio-frequency (RF) bias was kept low ( $\sim$ 75 V) while ECR power was set to achieve an etch rate of 1 nm/min (~100 W). The recess depth was 4 nm as measured by an atomic force microscope. The thickness of the remaining InAlN barrier layer was 3 nm. We did not observe any degradation in the source-to-drain current after the recess, and no postannealing step was performed. After the gate recess, a Ni/Au/Ni metal stack was deposited for the gate contact. Devices with gate lengths  $(L_G)$  in the 0.15–0.25- $\mu$ m range were confirmed by a scanning electron microscope. Finally, the devices were passivated with 25 nm of an Al<sub>2</sub>O<sub>3</sub> layer ( $\varepsilon_r = 10.8$  [8]) deposited by atomic layer deposition with a Cambridge Nanotech Savannah reactor.

#### **III. RESULTS AND DISCUSSION**

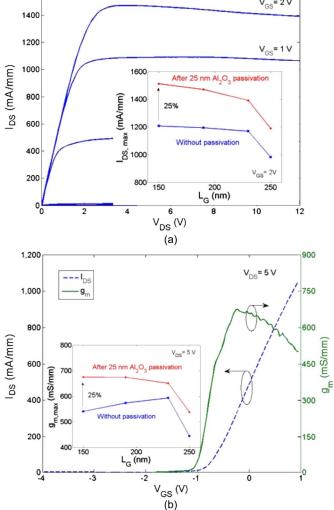

The effect of the  $Al_2O_3$  passivation on the electron transport of InAlN/GaN HEMTs was evaluated by transfer length measurements. Although the contact resistance  $(R_c)$  did not vary (0.3  $\Omega \cdot mm$ ), the sheet resistance ( $R_{\rm sh}$ ) was reduced by 15%, from 325 to 275  $\Omega$ /square, after the Al<sub>2</sub>O<sub>3</sub> deposition. The same improvement in  $R_{\rm sh}$  has been observed in AlGaN/GaN heterostructures [8]. This improvement has been attributed to the increased channel charge density induced by the change in the surface potential due to the high- $\kappa$  dielectric passivation. Fig. 2 shows the dc characteristics of a typical InAlN/GaN HEMT with a gate length of 0.15  $\mu$ m. The maximum drain current  $({\it I}_{\rm DS,max})$  at  ${\it V}_{\rm GS}=2$  V and the peak extrinsic transconductance  $(g_{m,ext})$  at  $V_{DS} = 5$  V simultaneously increased by 25% after the Al<sub>2</sub>O<sub>3</sub> passivation. Owing to this improvement as well as the low-damage gate recess, 0.15- $\mu$ mgate-length devices exhibited a high  $I_{DS,max}$  of 1.5 A/mm with a record  $g_{m,\text{ext}}$  of 675 mS/mm. For comparison, the highest

905

1600

Fig. 2. (a) DC current-voltage characteristics of an InAlN/GaN HEMT ( $L_G = 0.15 \ \mu m$ ,  $W_G = 25 \ \mu m$ ) with a high maximum output current of 1.5 A/mm. (b) Corresponding transfer curve showing a record peak extrinsic transconductance of 675 mS/mm. The insets show the improvement in (a)  $I_{\rm DS,max}$  and (b)  $g_{m,max}$  by the Al<sub>2</sub>O<sub>3</sub> passivation in submicrometer gate devices.

transconductance reported so far in any nitride semiconductor was 635 mS/mm (with  $I_{\rm DS,max} = 1.4$  A/mm) in deep-recessed AlGaN/GaN HEMTs [9]. The combination of high current density and transconductance in a single InAlN/GaN HEMT is very promising particularly for high-frequency high-power applications. The gate recess increased the transconductance of the 0.15- $\mu$ m device from 420 mS/mm (7-nm barrier) to 675 mS/mm (3-nm barrier), and the threshold voltage ( $V_T$ ) shifted from -3 to -0.8 V. The reduction of barrier thickness increases gate leakage current ( $I_G = 0.4$  mA/mm at  $I_{\rm DS,max}$ ). To minimize the gate leakage and to allow an even more aggressive gate recess, we are developing high- $\kappa$  gate dielectrics [8].

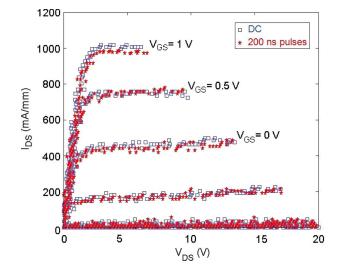

Current collapse in the fabricated devices was characterized by pulsed I-V measurements. A 200-ns pulse was applied to the gate, while a load resistance of 100  $\Omega$  was connected between the drain contact and the drain bias. During the measurement, the drain bias was swept from 0 to 20 V, and the

Fig. 3. DC and pulsed I-V characteristics of InAlN/GaN HEMTs with 25-nm Al<sub>2</sub>O<sub>3</sub> passivation. Very limited dispersion was observed under a 200-ns gate pulse and a 100- $\Omega$  load line.

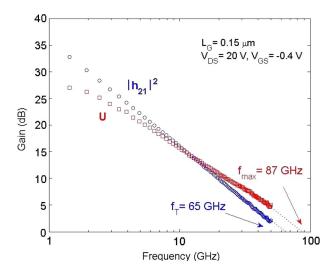

Fig. 4. RF performance of the 0.15- $\mu$ m-gate-length HEMT showing  $f_T = 65$  GHz and  $f_{max} = 87$  GHz.

gate electrode was pulsed from its quiescent value at pinch-off condition, typically -3 V. The transistors showed no current dispersion after the Al<sub>2</sub>O<sub>3</sub> passivation (Fig. 3), which demonstrates the ability of the thin Al<sub>2</sub>O<sub>3</sub> layer to effectively passivate the surface states located in the gate-drain access region.

The high-frequency performance of these devices was characterized from 0.45 to 50 GHz using an Agilent Technologies N5230A network analyzer, calibrated with a short-open-loadthrough calibration standard. On-wafer open and short patterns were used to subtract the effect of parasitic pad capacitances and inductances from the measured S-parameters. Fig. 4 shows the plot of  $|h_{21}|^2$  and Mason's unilateral gain U against frequency for the 0.15- $\mu$ m-gate-length device at  $V_{\rm DS} = 20$  V and  $V_{\rm GS} = -0.4$  V. A unity current gain cutoff frequency ( $f_T$ ) of 65 GHz and a power gain cutoff frequency ( $f_{\rm max}$ ) of 87 GHz were obtained by extrapolating measured data with a slope of -20 dB/dec using a least square fit. Small-signal parameters were extracted from the measured S-parameters following the method described in [10], and we found that both the gate capacitances  $(C_{\rm gs} + C_{\rm gd})$  and the intrinsic transconductance  $(g_{m,i})$  were simultaneously increased by 30%–40% by the Al<sub>2</sub>O<sub>3</sub> passivation, while their overall effect on  $f_T$  and  $f_{\rm max}~(\sim\!g_m/(C_{\rm gs}+C_{\rm gd}))$  was constant. Simulations of the parasitic capacitances introduced by  $Si_xN_y$  and  $Al_2O_3$  passivations show a 20% lower capacitance in the new Al<sub>2</sub>O<sub>3</sub> passivation than that in the conventional  $Si_x N_y$  passivation due to the lower thickness required for the Al2O3 layer (25 versus  $\sim$  100 nm). Thin Al<sub>2</sub>O<sub>3</sub> passivation layers are therefore promising candidates for high-frequency devices where the gate capacitances need to be minimized. The lower-thanexpected  $f_T/f_{\rm max}$  values obtained in this letter are mainly due to a significant reduction of the intrinsic transconductance at high frequencies (> 1 GHz). The study of the origin of this transconductance dispersion between dc and RF measurements is part of our ongoing work.

#### IV. CONCLUSION

We have investigated submicrometer gate-recessed InAlN/ GaN HEMTs on SiC substrates with a thin  $Al_2O_3$  passivation. Owing to the new  $Al_2O_3$  passivation and the low-damage gate recess, devices with a high output current density and record peak transconductance were achieved. The overall device performance demonstrates the great potential of InAlN/GaN HEMTs as a very promising alternative to AlGaN/GaN HEMTs.

#### REFERENCES

- [1] Y. F. Wu, A. Saxler, M. Moore, R. P. Smith, S. Sheppard, P. M. Chavarkar, T. Wisleder, U. K. Mishra, and P. Parikh, "30-W/mm GaN HEMTs by field plate optimization," *IEEE Electron Device Lett.*, vol. 25, no. 3, pp. 117– 119, Mar. 2004.

- [2] T. Palacios, A. Chakraborty, S. Rajan, C. Poblenz, S. Keller, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "High-power AlGaN/GaN HEMTs for Ka-band applications," *IEEE Electron Device Lett.*, vol. 26, no. 11, pp. 781–783, Nov. 2005.

- [3] J. Joh and J. A. del Alamo, "Mechanisms for electrical degradation of GaN high-electron mobility transistors," in *IEDM Tech. Dig.*, 2006, pp. 415–418.

- [4] M. Faqir, G. Verzellesi, G. Meneghesso, E. Zanoni, and F. Fantini, "Investigation of high-electron-field degradation effects in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 55, no. 7, pp. 1592–1602, Jul. 2008.

- [5] F. Medjdoub, J. F. Carlin, C. Gaquiere, N. Grandjean, and E. Kohn, "Status of the emerging InAlN/GaN power HEMT technology," *Open Elect. Electron. Eng. J.*, vol. 2, pp. 1–7, 2008.

- [6] F. Medjdoub, J. F. Carlin, M. Gonschorek, E. Feltin, M. A. Py, D. Ducatteau, C. Gaquiere, N. Grandjean, and E. Kohn, "Can InAlN/GaN be an alternative to high power/high temperature AlGaN/GaN devices?," in *IEDM Tech. Dig.*, 2006, pp. 927–930.

- [7] T. Palacios, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, "AlGaN/GaN high electron mobility transistors with InGaN back-barriers," *IEEE Electron Device Lett.*, vol. 27, no. 1, pp. 13–15, Jan. 2006.

- [8] O. I. Saadat, J. W. Chung, E. L. Piner, and T. Palacios, "Gate-first GaN HEMT technology for high frequency and high temperature applications," in *Proc. Int. Workshop Nitride Semicond.*, Montreux, Switzerland, Oct. 6–10, 2008.

- [9] J. S. Moon, S. Wu, D. Wong, I. Milosavljevic, A. Conway, P. Hashimoto, M. Hu, M. Antcliffe, and M. Micovic, "Gate-recessed AlGaN-GaN HEMTs for high-performance millimeter-wave applications," *IEEE Electron Device Lett.*, vol. 26, no. 6, pp. 348–350, Jun. 2005.

- [10] F. Mieville, "Suitability of GaN HEMTs for digital electronics," M.S. thesis, MIT, Cambridge, MA, 2008.