FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Generation of Custom Run-time Reconfigurable Hardware for Transparent Binary Acceleration

Nuno Miguel Cardanha Paulino

Programa Doutoral em Engenharia Electrotécnica e de Computadores (PDEEC)

Supervisor: João Canas Ferreira (Assistant Professor)

Co-supervisor: João M. P. Cardoso (Associate Professor)

June 2016

© Nuno Miguel Cardanha Paulino, 2016

### Abstract

With the increase of application complexity and amount of data, the required computational power increases in tandem. Technology improvements have allowed for the increase in clock frequencies of all kinds of processing architectures. But exploration of new architecture and computing paradigms over the simple single-issue in-order processor are equally important towards increasing performance, by properly exploiting the data-parallelism of demanding tasks. For instance: superscalar processors, which discover instruction parallelism at runtime; Very Long Instruction Word processors, which rely on compile-time parallelism discovery and multiple issue-units; and multi-core approaches, which are based on thread-level parallelism exploited at the software level.

For embedded applications, depending on the performance requirements or resource constraints, and if the application is composed of well-defined tasks, then a more application-specific system may be appropriate, i.e., developing an Application Specific Integrated Circuit (ASIC). Custom logic delivers the best power/performance ratio, but this solution requires advanced hardware expertise, implies long development time, and especially very high manufacture costs.

This work designed and evaluated a transparent binary acceleration approach, targeting Field Programmable Gate Array (FPGA) devices, which relies on instruction traces to automatically generate specialized accelerator instances. A custom accelerator, capable of executing a set of previously detected loop traces, is coupled to a host MicroBlaze processor. The traces are detected via simulation of the target binary. The approach does not require the application source code to be modified, which ensures the transparency for the application developer. No custom compilers are necessary, and the binary code does not need to be altered either offline or during runtime.

The accelerators contain per-instance reconfiguration capabilities, which allow for the reuse of computing units between accelerated loops, without sacrificing the benefits of circuit specialization. To increase the achievable performance, the accelerator is capable of performing two concurrent memory accesses to the MicroBlaze's data memory. The repetitive nature of the loop traces is exploited via loop-pipelining, which maximizes the achievable acceleration. By supporting single-precision floating-point operations via fully-pipelined units, the accelerator is capable of executing realistic data-oriented loops. Finally, the use of Dynamic Partial Reconfiguration (DPR) allows for significant area savings when instantiating accelerators with numerous configurations, and also ensures circuit specialization per-configuration.

Several fully functional systems were implemented, using commercial FPGAs, to validate the design iterations of the accelerator. An initial design relied on translating Control and Dataflow Graph representations of the traces into a multi-row array of Functional Units. For 15 benchmarks, the geometric mean speedup was  $2.08 \times$ . A second implementation augmented the accelerator with shared memory access to the the entire local data memory of the MicroBlaze. Arbitrary addresses can be accessed without need for address generation hardware. Exploiting data-parallelism allows for targeting of larger, more realistic traces. The mean geometric speedup for 37 benchmarks was  $2.35 \times$ . The most efficient implementation supports floating-point operations and relies on loop pipelining. The developed tools generate an accelerator instance by modulo-scheduling each trace at the minimum possible Initiation Interval. The geometric mean speedup for a set of 24 benchmarks is  $5.61 \times$ , and the accelerator requires only  $1.12 \times$  the FPGA slices required by the MicroBlaze. Finally, resorting to DPR, an accelerator with 10 configurations requires only a third of the Lookup Tables relative to an equivalent accelerator without this capability.

To summarize, the approach is capable of expediently generating accelerator-augmented embedded systems which achieve considerable performance increases whilst incurring a low resource cost, and without requiring manual hardware design.

## Sumário

Com o aumento da complexidade das aplicações, aumenta também a capacidade computacional necessária. Melhorias tecnológicas têm permitido o aumento da frequência de relógio para todo o tipo de arquitecturas computacionais. Contudo, a exploração de novas arquitecturas é igualmente importante para melhorias de desempenho, explorando eficientemente o paralelismo de dados de tarefas exigentes. Por exemplo: processadores *superscalar*, que descobrem paralelismo ao nível da instrução durante a execução; processadores VLIW (Very Large Instruction Word), que dependem de paralelismo explorado durante a compilação e de várias unidades em paralelo; e tecnologias multi-core, que se baseiam na exploração de paralelismo ao nível da *thread* através de software.

Para aplicações embebidas, dependendo dos requisitos de desempenho ou restrições de recursos, e se a aplicação for composta por tarefas bem definidas, um sistema mais especifico poderá ser mais apropriado, i.e., desenhar um ASIC (Application Specific Integrated Circuit). Lógica dedicada beneficia do melhor desempenho por *watt*, mas esta solução requer experiência de desenho de *hardware*, sofre de tempo de desenvolvimento longo, e custos de fabricação elevados.

Este trabalho desenvolveu e avaliou uma abordagem de aceleração transparente de código binário, orientada especificamente para FPGAs. A abordagem baseia-se em sequências frequentes de instruções executadas (i.e, *traces*) para gerar automaticamente aceleradores especializados. Um acelerador, capaz de executar um conjunto de *traces* previamente detectados, complementa um MicroBlaze, que age como processador principal. Os *traces* são detectados por simulação da aplicação, e representam ciclos de execução (i.e., *loops*). Não é necessário modificações ao código-fonte, o que aumenta a transparência da abordagem para o programador. Um compilador especializado não é necessário, e o código binário não sofre modificações pós-compilação.

O acelerador contém lógica de reconfiguração especializada, o que permite a reutilização de unidades de cálculo entre os *loops* acelerados, sem sacrificar a especialização. Para maximizar o desempenho, o acelerador é capaz de efectuar dois acessos paralelos à memória de dados do processador. O uso de *loop-pipelining* maximiza a aceleração, e o suporte para operações de vírgula flutuante permite a execução de tarefas embebidas realistas. Finalmente, o uso de Reconfiguração Parcial Dinâmica (DPR), reduz significativamente a área necessária para suportar várias configuraçãos, e assegura a especialização do hardware respectivo a cada configuração.

Vários sistemas totalmente funcionais foram implementados para validar os aceleradores, usando FPGAs comerciais. Um primeira implementação traduz representações de grafo de dados (i.e., Control and Dataflow Graph) dos *loops* para várias linhas de unidades funcionais interligadas. Para 15 *benchmarks*, a média geométrica da aceleração foi de  $2.08 \times$ . Uma segunda implementação adiciona ao acelerador suporte para acesso à memória. O mesmo é capaz de aceder directamente a toda a memória local de dados do MicroBlaze, sendo suportados acessos endereços arbitrários. Explorar o paralelismo de dados permite acelerar *loops* mais realísticos. Para 37 benchmarks, a média geométrica da aceleração foi de  $2.35 \times$ . A implementação mais eficiente suporta operações de vírgula flutuante e utiliza *loop-pipelining*. Um escalonador gera uma instância do acelerador efectuando *modulo-scheduling* para cada *trace* ao intervalo de iniciação (i.e., Initiation Interval) mínimo. A média geométrica da aceleração é de  $5.61 \times$  em média para 24 aplicações, e os aceleradores requerem  $1.12 \times$  o número de *slices* de FPGA de um MicroBlaze. Finalmente, com o uso de DPR, um acelerador com 10 configurações necessita apenas de um terço das *Lookup Tables* relativamente a um acelerador equivalente sem esta capacidade.

Concluindo, a abordagem permite gerar rapidamente sistemas com aceleradores especializados que aumentam consideravelmente o desempenho, com um custo reduzido em termos de recursos, evitando também a necessidade de desenho de *hardware* manual.

# Acknowledgments

This thesis is the result of four years of work that I was fortunate enough to be able to carry out with focus and nearly undivided attention due mostly, if not totally, to the support of my parents, who helped keep my mind of other, more time consuming, and infinitely less productive matters.

The individual moments where someone lent me their support, and particular people who took the time to care and ask about my work, are too numerous to list. A thank you to the friends that shared a seat in the lab where I sit as I type this. It would go without saying, but I'd also like to thank my supervisor, João Canas Ferreira, for his guidance and insight which helped make sure I didn't stray off into the distance on a random direction. Also, a thank you to my co-supervisor, João Manuel Paiva Cardoso, for many fruitful discussions, and another to João Bispo, both for suggestions and for providing his own set of tools, which were the starting point for what I have developed. I would also like to thank Michael Hübner for his interest in my work, as well as Max Ferger for some helpful suggestions.

Finally, a special thanks goes out to my friend Henrique Martins, with the hope that he comes to his senses and comes back home.

On a completely different note, I would also like to acknowledge the support through PhD grant SFRH/BD/80225/2011, provided by FCT (*Fundação para a Ciência e a Tecnologia* - Portuguese Foundation for Science and Technology). Finally, thank you to Stephen Wong from the Delft University of Technology in the Netherlands, for the  $\rho$ -VEX processor release and tools.

Nuno Paulino

iv

"Terry took Death's arm and followed him through the doors and on to the black desert under the endless night."

Terry Pratchett

vi

# Contents

| 1 | Intr       | roduction 1    |                                                                 |          |

|---|------------|----------------|-----------------------------------------------------------------|----------|

|   | 1.1        | FPGAs          | s as a Platform for HW/SW Partitioning Design                   | 3        |

|   | 1.2        | Autom          | nated HW/SW Partitioning                                        | 4        |

|   |            | 1.2.1          | High-Level Synthesis                                            | 4        |

|   |            | 1.2.2          | Binary-level HW/SW Partitioning                                 | 4        |

|   | 1.3        | Motiva         | ation and Problem Statement                                     | 5        |

|   | 1.4        | Object         | ives                                                            | 7        |

|   | 1.5        | Approa         | ach                                                             | 8        |

|   |            | 1.5.1          | Megablock Trace                                                 | 9        |

|   |            | 1.5.2          | Generating a Reconfigurable Customized Accelerator Instance     | 11       |

|   | 1.6        | Contril        | butions                                                         | 13       |

|   | 1.7        | Summa          | ary of Published Work                                           | 14       |

|   |            | 1.7.1          | International Journals                                          | 14       |

|   |            | 1.7.2          | International Conferences                                       | 15       |

|   |            | 1.7.3          | National Conferences                                            | 16       |

|   | 1.8        | Structu        | re of this document                                             | 16       |

| 2 | Dard       | aion of        | Deleted Work                                                    | 19       |

| 2 |            |                | Related Work                                                    | 19<br>19 |

|   | 2.1        | Overvi         |                                                                 | 20       |

|   |            | 2.1.1<br>2.1.2 | Partitioning                                                    | 20<br>21 |

|   |            | 2.1.2          | Accelerator Structure                                           | 21       |

|   |            | 2.1.5          |                                                                 | 22       |

|   |            | 2.1.4          | Accelerator Memory Access                                       | 23<br>26 |

|   |            | 2.1.5          | Accelerator Programmability and Compilation                     | 20<br>29 |

|   | 2.2        |                | sentative Approaches                                            | 29<br>30 |

|   | 2.2        | 2.2.1          |                                                                 | 30       |

|   |            | 2.2.1          | Warp Processor                                                  | 31       |

|   |            | 2.2.2          | ADEXOR                                                          | 31       |

|   |            | 2.2.5          | Configurable Compute Accelerator                                | 33       |

|   |            | 2.2.4          | ASTRO                                                           | 33<br>34 |

|   |            | 2.2.5          | Work of Ferreira <i>et al.</i>                                  | 34<br>35 |

|   |            | 2.2.0          |                                                                 | 35<br>35 |

|   |            |                | Morphosys                                                       |          |

|   | 0.0        | 2.2.8          | Additional Related Works                                        | 37       |

|   | 2.3        | •              | nic Partial Reconfiguration in FPGAs                            | 38       |

|   |            | 2.3.1          | Examples of Partial Reconfiguration Applications                | 38       |

|   | <b>0</b> 4 | 2.3.2          | Design Considerations for Partial Reconfiguration Based Systems | 39       |

|   | 2.4        | Conclu         | uding Remarks                                                   | 39       |

| 3 | Ove  | rview of Implementations and General Tool Flow            | 41       |

|---|------|-----------------------------------------------------------|----------|

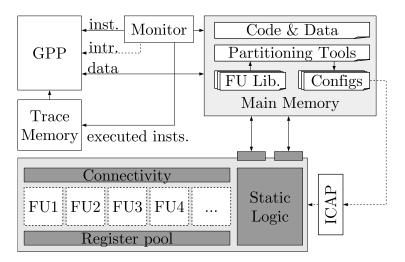

|   | 3.1  | System Level Architecture                                 | 41       |

|   | 3.2  | General Execution Model                                   | 42       |

|   | 3.3  | General Tool Flow                                         | 44       |

|   |      | 3.3.1 Megablock Extraction                                | 45       |

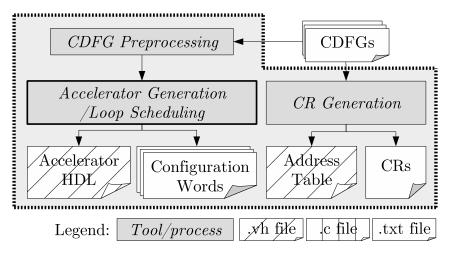

|   |      | 3.3.2 Generation of the accelerator HDL Description       | 47       |

|   |      | 3.3.3 Generation of Communication Routine                 | 49       |

|   | 3.4  | The Injector Module                                       | 51       |

|   | 3.5  | Summary of Accelerator Implementations                    | 52       |

| 4 | Cust | tomized Multi-Row Accelerators                            | 55       |

| 4 |      |                                                           |          |

|   | 4.1  | Accelerator Architecture                                  | 55       |

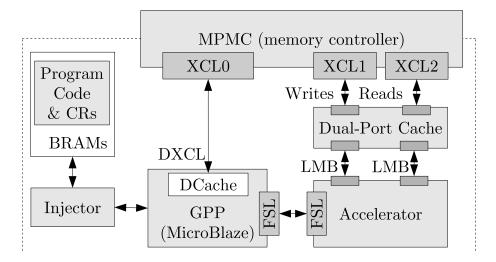

|   |      | 4.1.1 Structure                                           | 56       |

|   |      | 4.1.2 Interface                                           | 57       |

|   |      | 4.1.3 Execution Model                                     | 59       |

|   | 4.2  | Architecture Specific Tool Flow                           | 59       |

|   | 4.3  | Experimental Evaluation                                   | 62       |

|   |      | 4.3.1 Hardware Setup                                      | 62       |

|   |      | 4.3.2 Software Setup                                      | 63       |

|   |      | 4.3.3 Characteristics of the Generated Accelerators       | 64       |

|   |      | 4.3.4 Performance vs. MicroBlaze Processor                | 67       |

|   |      | 4.3.5 Resource Requirements and Operating Frequency       | 71       |

|   | 4.4  | Concluding Remarks                                        | 73       |

| 5 | Acco | elerators with Memory Access Support                      | 75       |

| 5 | 5.1  | Accelerator Architecture                                  | 73<br>76 |

|   | 5.1  |                                                           | 70       |

|   |      | , , , , , , , , , , , , , , , , , , ,                     | 78       |

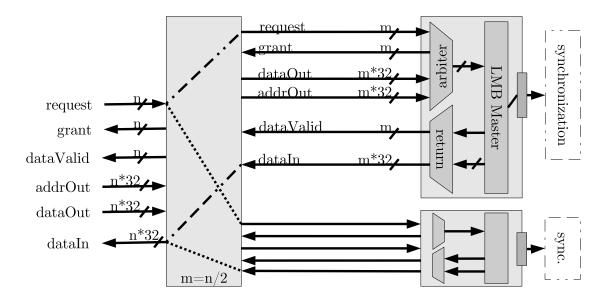

|   |      | 5.1.2 Memory Access Support                               |          |

|   | 5.0  | 5.1.3 Execution Model                                     | 79       |

|   | 5.2  | Accelerator Generation and Loop Translation               | 80       |

|   |      | 5.2.1 List Scheduling                                     | 81       |

|   |      | 5.2.2 Memory Access Scheduling                            | 83       |

|   |      | 5.2.3 Multiplexer Specification                           | 85       |

|   | 5.3  | Experimental Evaluation                                   | 85       |

|   |      | 5.3.1 Hardware Setup                                      | 85       |

|   |      | 5.3.2 Software Setup                                      | 86       |

|   |      | 5.3.3 General Aspects                                     | 87       |

|   |      | 5.3.4 Performance vs. MicroBlaze Processor                | 90       |

|   |      | 5.3.5 Effects of Memory Access Optimizations              | 95       |

|   |      | 5.3.6 Effects of List Scheduling on Functional Unit Reuse | 97       |

|   |      | 5.3.7 Resource Requirements and Operating Frequency       | 99       |

|   |      | 5.3.8 Power and Energy Consumption                        | 101      |

|   | 5.4  | Concluding Remarks                                        | 101      |

|   |      | -                                                         |          |

| 6 |      | lulo Scheduling onto Customized Single-Row Accelerators   | 105      |

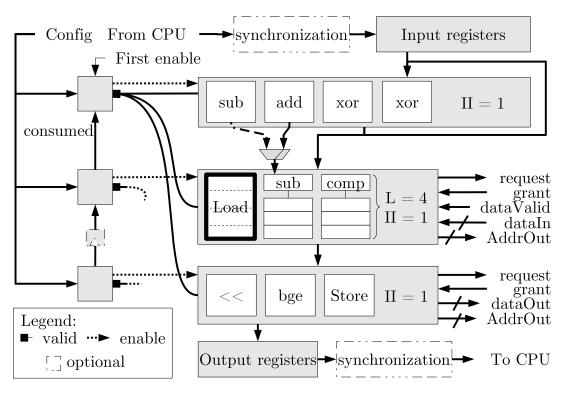

|   | 6.1  | Accelerator Architecture                                  | 107      |

|   |      | 6.1.1 Execution Model                                     | 108      |

|   | 6.2  | Architecture Specific Tool Flow                           | 110      |

|   | 6.3  | Accelerator Generation and Loop Scheduling                | 110      |

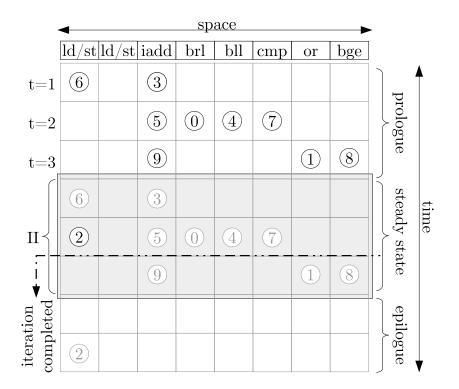

|   |      | 6.3.1   | Scheduling Example                                                      |

|---|------|---------|-------------------------------------------------------------------------|

|   | 6.4  | Experi  | mental Evaluation                                                       |

|   |      | 6.4.1   | Hardware Setup                                                          |

|   |      | 6.4.2   | Software Setup                                                          |

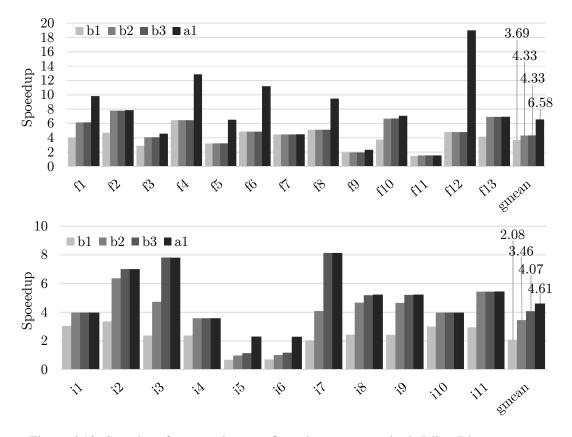

|   |      | 6.4.3   | Performance vs. MicroBlaze Processor                                    |

|   |      | 6.4.4   | Resource Requirements & Operating Frequency 121                         |

|   |      | 6.4.5   | Power and Energy Consumption                                            |

|   |      | 6.4.6   | Performance and Cost of Multi-loop Support                              |

|   | 6.5  |         | nance Comparison with ALU Based Accelerators                            |

|   | 6.6  |         | nance Comparison with VLIW Architectures                                |

|   |      | 6.6.1   | Performance Comparison                                                  |

|   |      | 6.6.2   | Resource Usage Comparison                                               |

|   | 6.7  |         | ding Remarks                                                            |

|   |      |         |                                                                         |

| 7 | •    |         | rtial Reconfiguration of Customized Single-Row Accelerators 135         |

|   | 7.1  |         | rator Architecture                                                      |

|   |      | 7.1.1   | Static Partition                                                        |

|   |      | 7.1.2   | Reconfigurable Partition                                                |

|   | 7.2  |         | ow for Dynamic Partial Reconfiguration                                  |

|   | 7.3  | _       | mental Evaluation                                                       |

|   |      | 7.3.1   | Hardware Setup                                                          |

|   |      | 7.3.2   | Software Setup                                                          |

|   |      | 7.3.3   | Resource Requirements of Static and Reconfigurable Regions 141          |

|   |      | 7.3.4   | Resource Requirements of DPR Accelerator vs. Non-DPR Accelerator . 142  |

|   |      | 7.3.5   | Synthesis Time of DPR-Capable Accelerator vs. Non-DPR Accelerator . 145 |

|   |      | 7.3.6   | Effect of Partial Reconfiguration Overhead on Performance 145           |

|   | 7.4  | Conclu  | ding Remarks                                                            |

| 8 | Con  | clusion | and Future Work 149                                                     |

| Ū | 8.1  |         | teristics of the Developed Approach                                     |

|   | 8.2  |         | Work                                                                    |

|   | 0.2  | 8.2.1   | Potential Improvements to the Developed Approach                        |

|   |      | 8.2.2   |                                                                         |

|   |      | 8.2.3   | Runtime HW/SW Partitioning via DPR                                      |

|   | 8.3  |         | ding Remarks                                                            |

|   | 0.0  | contra  |                                                                         |

| A | Exte | rnal Me | emory Access for Loop Pipelined Multi-Row Accelerators 157              |

|   | A.1  | Accele  | rator Architecture                                                      |

|   |      | A.1.1   | Structure                                                               |

|   |      | A.1.2   | Execution                                                               |

|   |      | A.1.3   | Memory Access                                                           |

|   | A.2  | Config  | urable Dual-Port Cache                                                  |

|   | A.3  | Experi  | mental Evaluation                                                       |

|   |      | A.3.1   | General Aspects                                                         |

|   |      | A.3.2   | Performance                                                             |

|   |      | A.3.3   | Communication and Cache Invalidation Overhead 166                       |

|   |      | A.3.4   | Resource Requirements and Operating Frequency                           |

|   | A.4  | Conclu  | ding Remarks                                                            |

|   |      |         |                                                                         |

171

# **List of Figures**

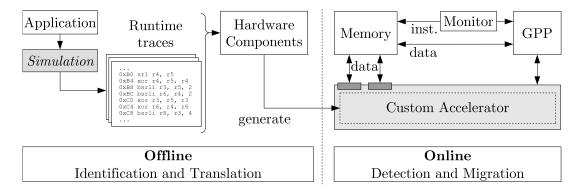

| 1.1                                                                                                                | Proposed transparent binary acceleration approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                          |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

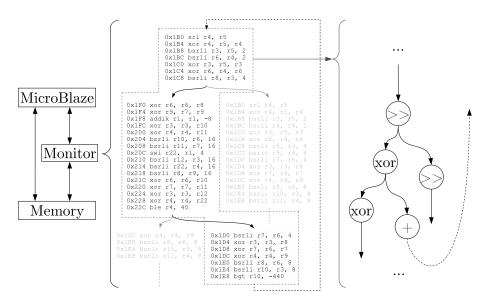

| 1.2                                                                                                                | Megablock trace and CDFG example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                         |

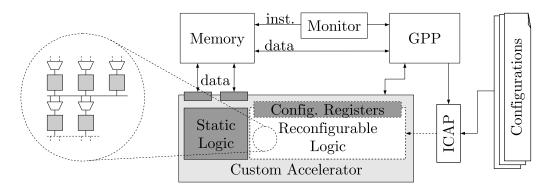

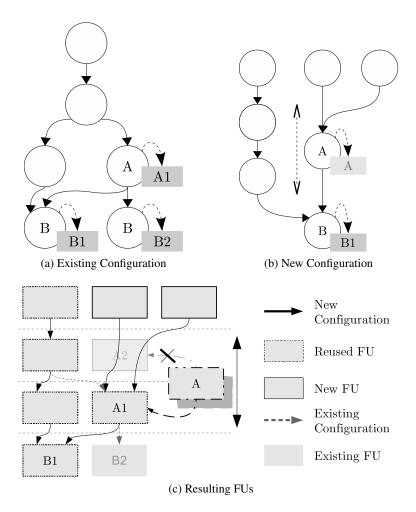

| 1.3                                                                                                                | DPR Oriented system design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                         |

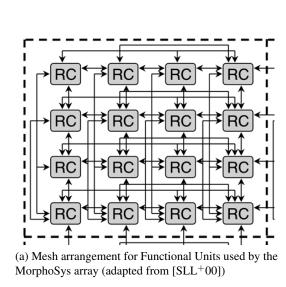

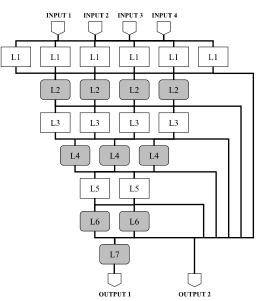

| 2.1                                                                                                                | Two arrangements for Functional Units in reconfigurable arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                                         |

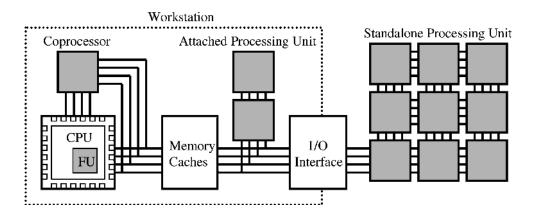

| 2.2                                                                                                                | Types of host-processor/co-processor interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                                                                         |

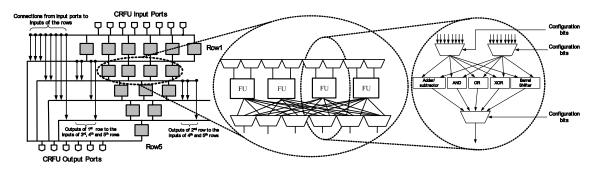

| 2.3                                                                                                                | Modulo-scheduling of loops on mesh based arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                         |

| 2.4                                                                                                                | The Warp processor approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                         |

| 2.5                                                                                                                | A tightly coupled heterogeneous array of Functional Units in the AMBER approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32                                                                         |

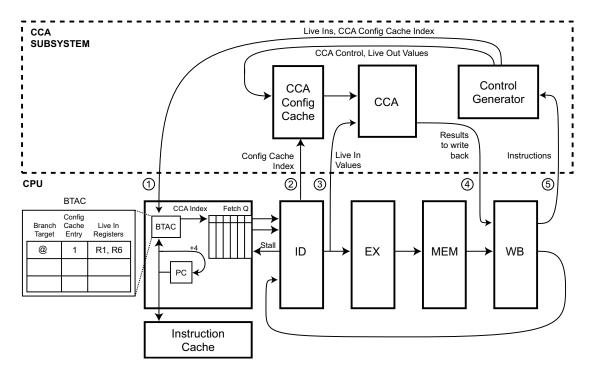

| 2.6                                                                                                                | A tightly coupled heterogeneous array of Functional Units in the CCA approach .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                         |

| 2.7                                                                                                                | The DIM binary translation mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                         |

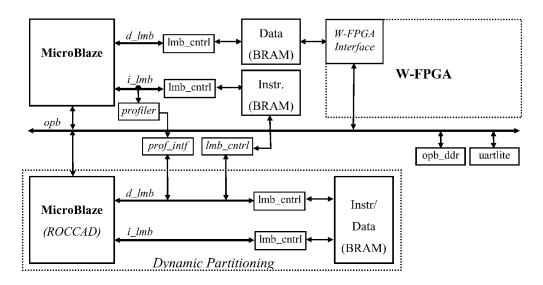

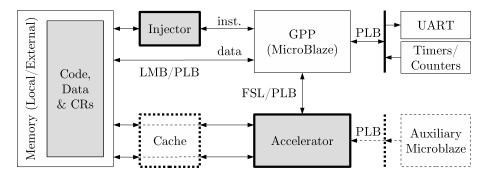

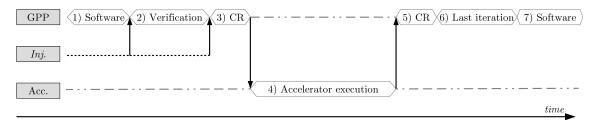

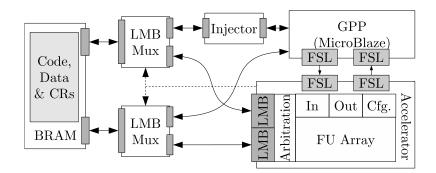

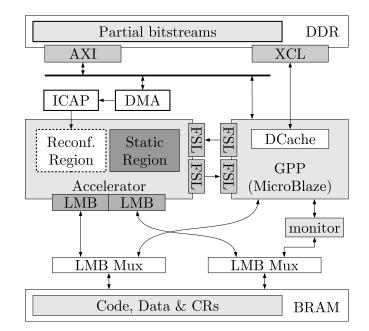

| 3.1                                                                                                                | General overview of developed system architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                                                                         |

| 3.2                                                                                                                | Temporal diagram of migration and instruction level behaviour due to migration .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43                                                                         |

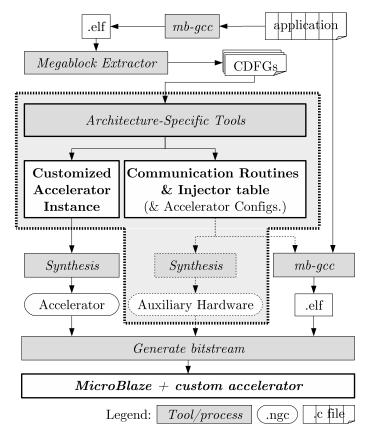

| 3.3                                                                                                                | Generic tool flow of developed approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                         |

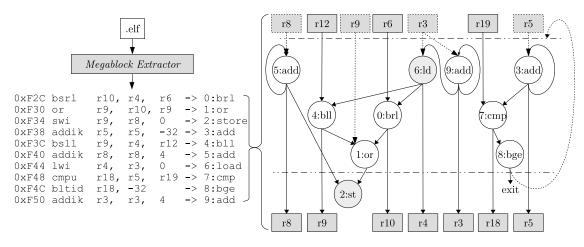

| 3.4                                                                                                                | Example of extracted loop trace and resulting CDFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46                                                                         |

| 3.5                                                                                                                | Example instantiation of multi-row array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                                                                         |

| 3.6                                                                                                                | Example of tool-generated Communication Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                         |

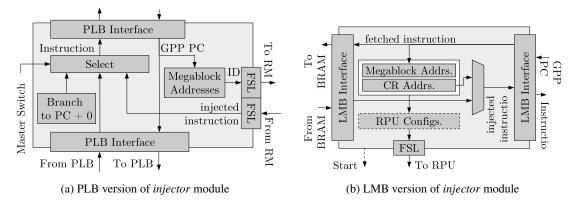

| 3.7                                                                                                                | Architectural variants of the <i>injector</i> module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                         |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| 4.1                                                                                                                | Synthetic example of 2D accelerator instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                         |

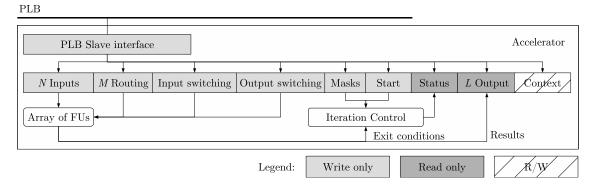

| 4.2                                                                                                                | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                         |

| 4.2<br>4.3                                                                                                         | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>60                                                                   |

| 4.2<br>4.3<br>4.4                                                                                                  | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>60<br>62                                                             |

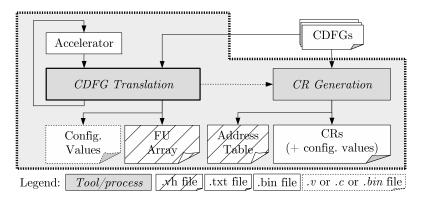

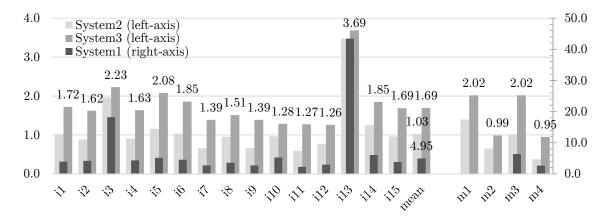

| 4.2<br>4.3<br>4.4<br>4.5                                                                                           | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>60<br>62<br>67                                                       |

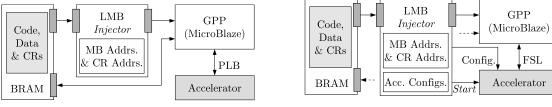

| 4.2<br>4.3<br>4.4                                                                                                  | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>60<br>62                                                             |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>5.1</li> </ul>                           | Bus-type interface for the acceleratorArchitecture-specific flow for 2D accelerator design and supporting hardwareSystem level variants used for evaluation of 2D accelerator designSpeedups for several types of system architecturesSynthesis frequency and resource requirements of the generated accelerators2D Accelerator with memory access logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58<br>60<br>62<br>67<br>72<br>76                                           |

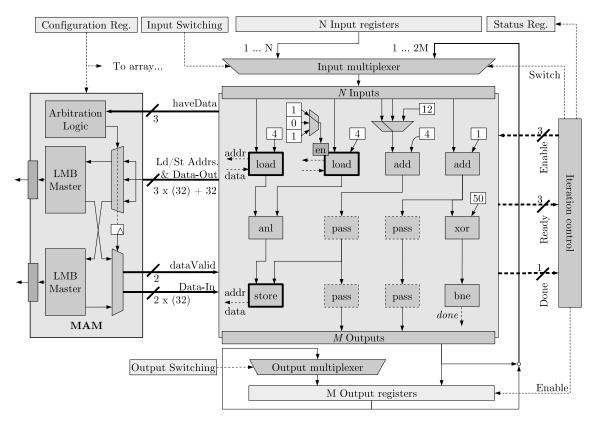

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>5.1</li> <li>5.2</li> </ul>              | Bus-type interface for the acceleratorArchitecture-specific flow for 2D accelerator design and supporting hardwareSystem level variants used for evaluation of 2D accelerator designSpeedups for several types of system architecturesSynthesis frequency and resource requirements of the generated accelerators2D Accelerator with memory access logicLocal Memory Bus Multiplexer module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58<br>60<br>62<br>67<br>72<br>76<br>79                                     |

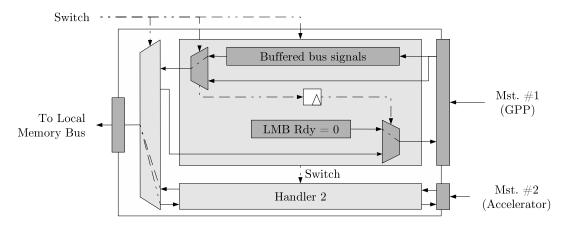

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul> | Bus-type interface for the accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80                               |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4                                                        | Bus-type interface for the accelerator .       .         Architecture-specific flow for 2D accelerator design and supporting hardware .       .         System level variants used for evaluation of 2D accelerator design .       .         Speedups for several types of system architectures .       .         Synthesis frequency and resource requirements of the generated accelerators .       .         2D Accelerator with memory access logic .       .         Local Memory Bus Multiplexer module .       .         Architecture-specific flow for this 2D accelerator design .       .         List scheduling example for a Functional Unit with available slack .       .                                                                                                                                                                                                                                                                                                                                                                                         | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82                         |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                 | Bus-type interface for the acceleratorArchitecture-specific flow for 2D accelerator design and supporting hardwareSystem level variants used for evaluation of 2D accelerator designSpeedups for several types of system architecturesSynthesis frequency and resource requirements of the generated accelerators2D Accelerator with memory access logicLocal Memory Bus Multiplexer moduleArchitecture-specific flow for this 2D accelerator designList scheduling example for a Functional Unit with available slackAssignment of <i>load/store</i> units to ports and cycles, after Functional Unit placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83                   |

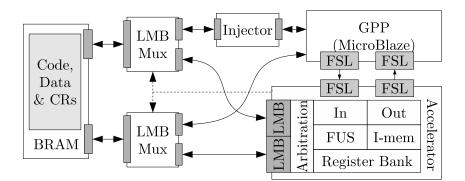

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                          | Bus-type interface for the accelerator .Architecture-specific flow for 2D accelerator design and supporting hardware .System level variants used for evaluation of 2D accelerator design .Speedups for several types of system architectures .Synthesis frequency and resource requirements of the generated accelerators .2D Accelerator with memory access logic .Local Memory Bus Multiplexer module .Architecture-specific flow for this 2D accelerator design .List scheduling example for a Functional Unit with available slack .Assignment of <i>load/store</i> units to ports and cycles, after Functional Unit placementSystem architecture for validation of accelerator local memory access .                                                                                                                                                                                                                                                                                                                                                                        | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83<br>86             |

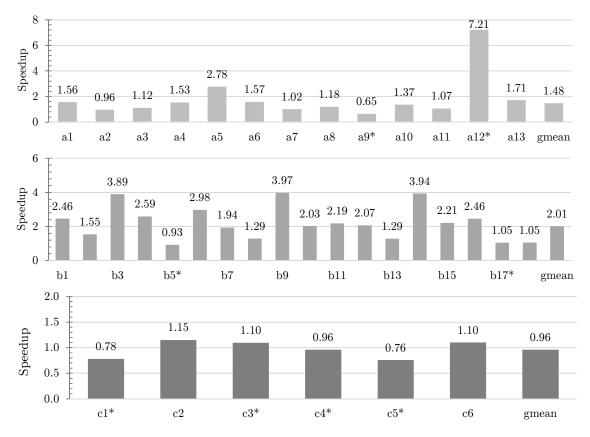

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                   | Bus-type interface for the accelerator .Architecture-specific flow for 2D accelerator design and supporting hardware .System level variants used for evaluation of 2D accelerator design .Speedups for several types of system architectures .Synthesis frequency and resource requirements of the generated accelerators .2D Accelerator with memory access logic .Local Memory Bus Multiplexer module .Architecture-specific flow for this 2D accelerator design .List scheduling example for a Functional Unit with available slack .Assignment of <i>load/store</i> units to ports and cycles, after Functional Unit placementSystem architecture for validation of accelerator local memory access .Speedups for the three benchmark sets .                                                                                                                                                                                                                                                                                                                                 | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83<br>86<br>90       |

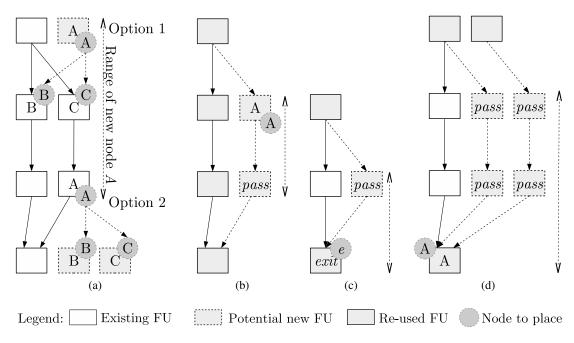

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                            | Bus-type interface for the accelerator .Architecture-specific flow for 2D accelerator design and supporting hardware .System level variants used for evaluation of 2D accelerator design .Speedups for several types of system architectures .Synthesis frequency and resource requirements of the generated accelerators .2D Accelerator with memory access logic .Local Memory Bus Multiplexer module .Architecture-specific flow for this 2D accelerator design .List scheduling example for a Functional Unit with available slack .Assignment of <i>load/store</i> units to ports and cycles, after Functional Unit placementSystem architecture for validation of accelerator local memory access .Speedups for the three benchmark sets .Effects of list scheduling on instantiation of <i>passthrough</i> units .                                                                                                                                                                                                                                                        | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83<br>86<br>90<br>97 |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                   | Bus-type interface for the accelerator .Architecture-specific flow for 2D accelerator design and supporting hardware .System level variants used for evaluation of 2D accelerator design .Speedups for several types of system architectures .Synthesis frequency and resource requirements of the generated accelerators .2D Accelerator with memory access logic .Local Memory Bus Multiplexer module .Architecture-specific flow for this 2D accelerator design .List scheduling example for a Functional Unit with available slack .Assignment of <i>load/store</i> units to ports and cycles, after Functional Unit placementSystem architecture for validation of accelerator local memory access .Speedups for the three benchmark sets .Effects of list scheduling on instantiation of <i>passthrough</i> units .                                                                                                                                                                                                                                                        | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83<br>86<br>90       |

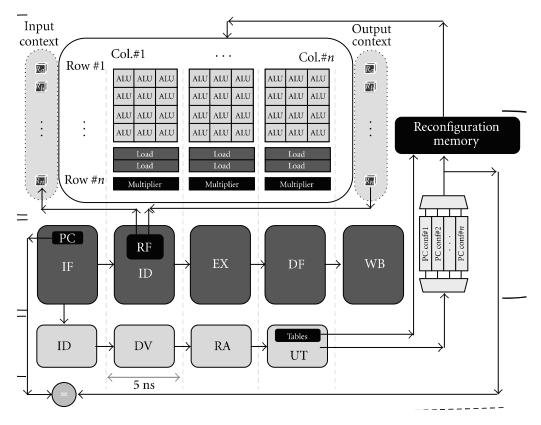

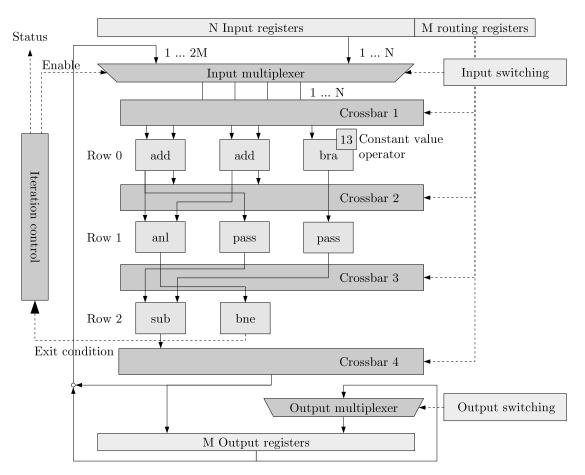

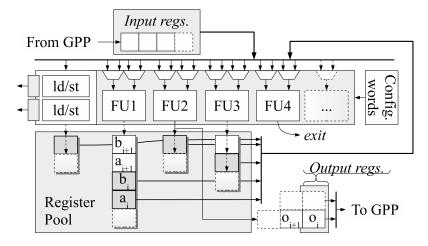

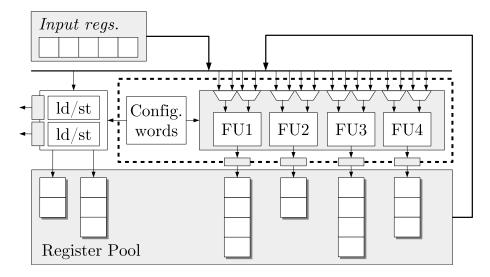

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                            | Bus-type interface for the accelerator .       .         Architecture-specific flow for 2D accelerator design and supporting hardware .       .         System level variants used for evaluation of 2D accelerator design .       .         Speedups for several types of system architectures .       .         Synthesis frequency and resource requirements of the generated accelerators .       .         2D Accelerator with memory access logic .       .         Local Memory Bus Multiplexer module .       .         Architecture-specific flow for this 2D accelerator design .       .         List scheduling example for a Functional Unit with available slack .       .         Assignment of <i>load/store</i> units to ports and cycles, after Functional Unit placement       .         System architecture for validation of accelerator local memory access .       .         Effects of list scheduling on instantiation of <i>passthrough</i> units .       .         Architecture template for a single-row accelerator for modulo scheduling .       . | 58<br>60<br>62<br>67<br>72<br>76<br>79<br>80<br>82<br>83<br>86<br>90<br>97 |

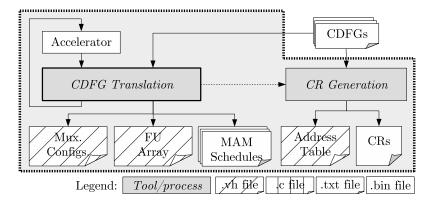

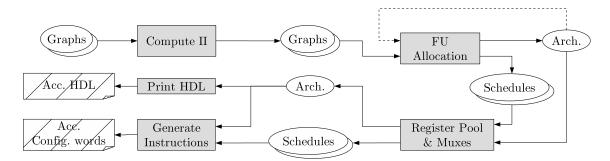

| 6.3                                                                                                   | Architecture-specific flow for the single-row accelerator                                                                                          | 110                                           |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

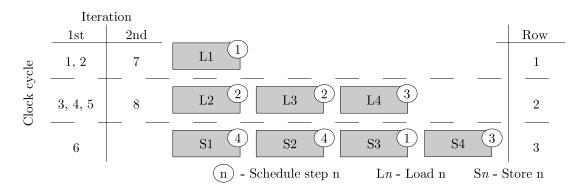

| 6.4                                                                                                   | Execution flow of modulo scheduling for the single-row accelerator                                                                                 | 111                                           |

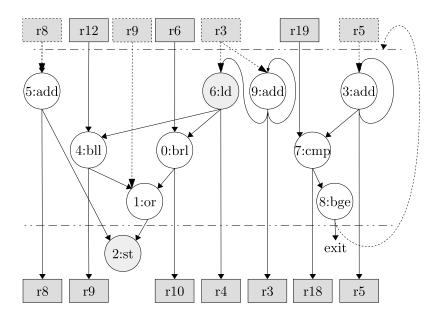

| 6.5                                                                                                   | Example CDFG                                                                                                                                       | 112                                           |

| 6.6                                                                                                   | Modulo schedule for the example CDFG                                                                                                               | 113                                           |

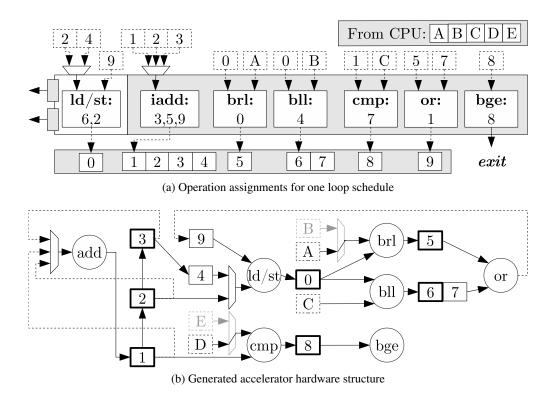

| 6.7                                                                                                   | Example single-row accelerator instance and hardware structure                                                                                     | 114                                           |

| 6.8                                                                                                   | System architecture for validation of the single-row modulo scheduled accelerator                                                                  | 115                                           |

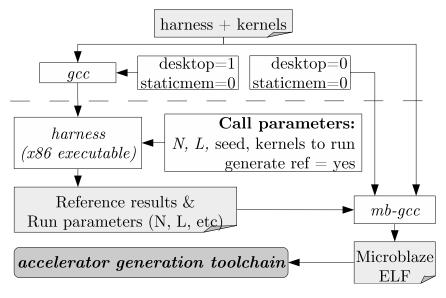

| 6.9                                                                                                   | Compilation flow of the test harness                                                                                                               | 117                                           |

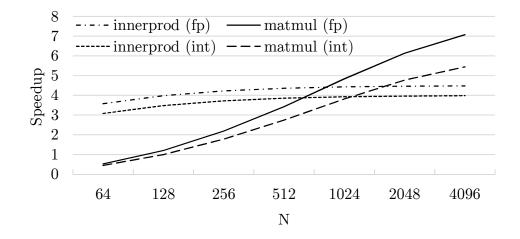

| 6.10                                                                                                  | Speedup as a function of input/output data array sizes                                                                                             | 120                                           |

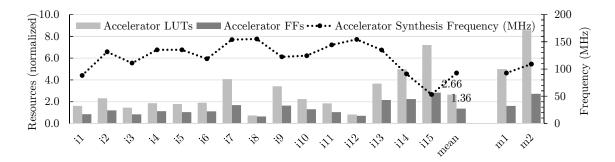

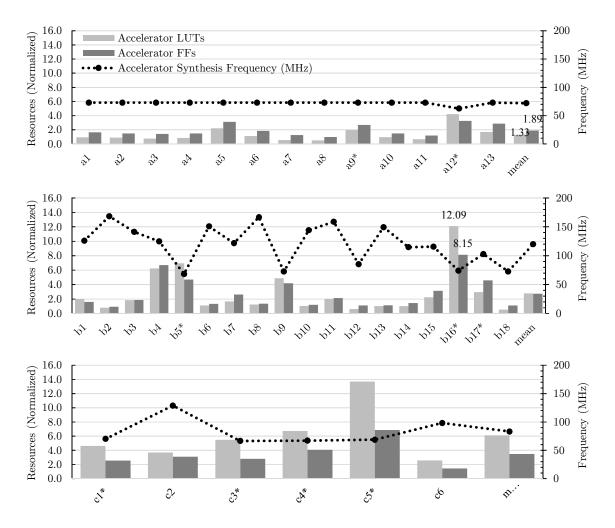

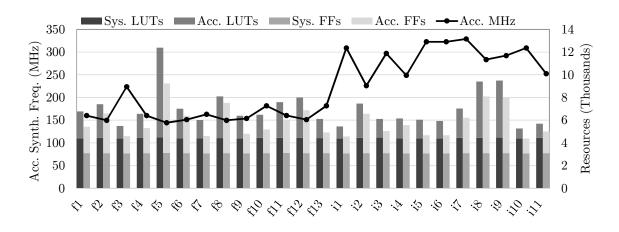

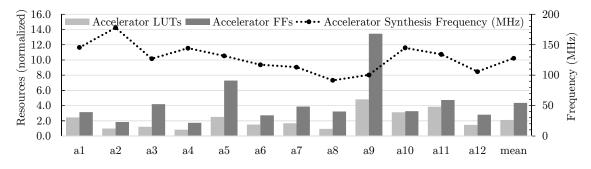

| 6.11                                                                                                  | Resource requirements and operating frequency for single-row accelerator                                                                           | 122                                           |

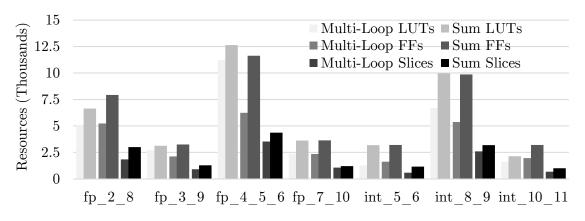

| 6.12                                                                                                  | Resource requirements for multi-loop accelerator vs. single-loop accelerators                                                                      | 125                                           |

| 6.13                                                                                                  | Speedups for several types of accelerators vs. a single MicroBlaze processor                                                                       | 127                                           |

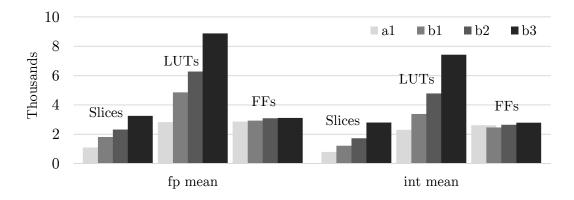

| 6.14                                                                                                  | Resource requirements for several types of accelerators                                                                                            | 128                                           |

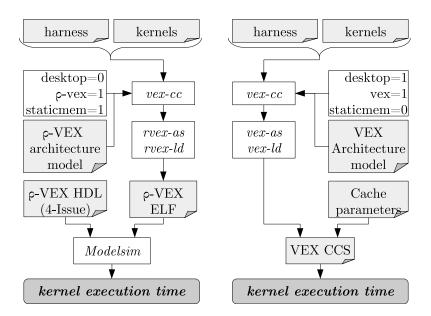

| 6.15                                                                                                  | Simulation flow for $\rho$ -VEX processor and other VEX architecture models                                                                        | 129                                           |

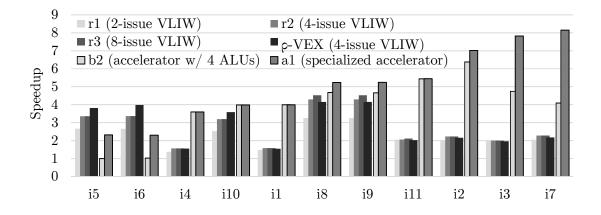

| 6.16                                                                                                  | Speedups for different VLIW models versus single-row accelerator                                                                                   | 131                                           |

|                                                                                                       |                                                                                                                                                    |                                               |

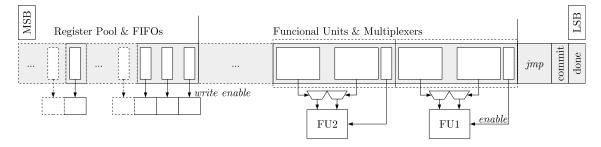

| 7.1                                                                                                   | Single-row accelerator architecture partitioned for Dynamic Partial Reconfiguration                                                                | 136                                           |

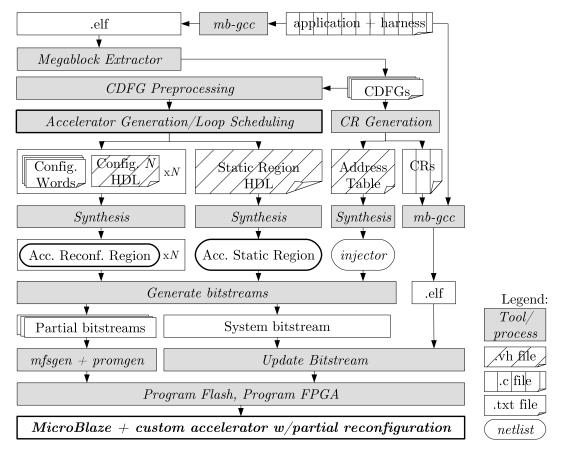

| 7.1<br>7.2                                                                                            | Single-row accelerator architecture partitioned for Dynamic Partial Reconfiguration<br>Complete tool flow for partially reconfigurable accelerator | 136<br>138                                    |

|                                                                                                       |                                                                                                                                                    |                                               |

| 7.2                                                                                                   | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138                                           |

| 7.2<br>7.3                                                                                            | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138                                           |

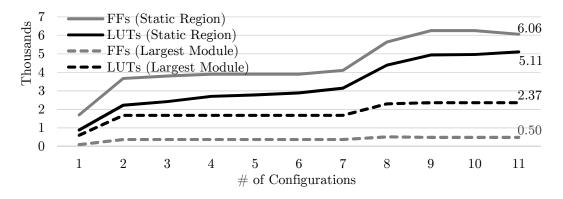

| 7.2<br>7.3                                                                                            | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141                                    |

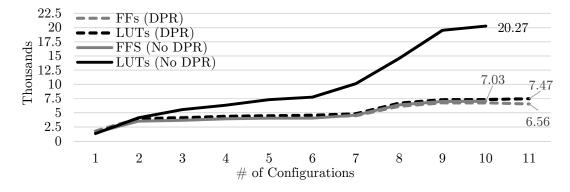

| 7.2<br>7.3<br>7.4                                                                                     | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141<br>142                             |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                             | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141<br>142<br>143                      |

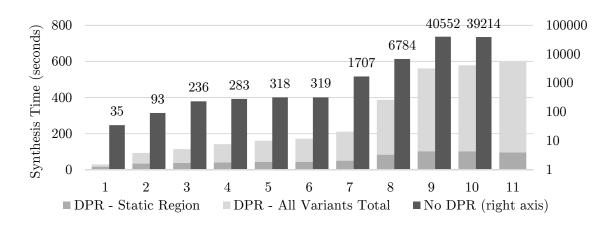

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul>                           | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141<br>142<br>143<br>145               |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>8.1</li> </ul>              | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141<br>142<br>143<br>145<br>155        |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>8.1</li> <li>A.1</li> </ul> | Complete tool flow for partially reconfigurable accelerator                                                                                        | 138<br>141<br>142<br>143<br>145<br>155<br>158 |

# Listings

| 3.1 | Accelerator HDL specification excerpt                                              | 48  |

|-----|------------------------------------------------------------------------------------|-----|

| 3.2 | Fast Simplex Link based Communication Routine in C container                       | 50  |

| 3.3 | Linker Script excerpt to place Communication Routines at known position            | 50  |

| 4.1 | Reconfiguration information placed in C containers                                 | 61  |

| 4.2 | Reconfiguration information placed into a read-only memory module                  | 61  |

| 4.3 | Simplified code for <i>even ones</i> benchmark                                     | 64  |

| 5.1 | Multiplexer HDL specification excerpt                                              | 85  |

| 5.2 | Code excerpt for <i>crc32</i> kernel                                               | 87  |

| 5.3 | Code excerpt for max kernel, without <i>if-conversion</i>                          | 92  |

| 5.4 | Code excerpt for <i>max</i> kernel, with <i>if-conversion</i>                      | 92  |

| 6.1 | Inner product kernel adapted for test harness integration                          | 117 |

| 7.1 | Communication Routine with call to partial reconfiguration function                | 139 |

| 7.2 | Generating a flash programming file from a file system with all partial bitstreams | 140 |

## LISTINGS

# **List of Tables**

| 2.1        | Characteristics of related Transparent Binary Acceleration approaches        | 36       |

|------------|------------------------------------------------------------------------------|----------|

|            |                                                                              | 20       |

| 3.1        | Brief comparison of implemented accelerator architectures and results        | 53       |

| 4.1<br>4.2 | Extracted Megablock and generated accelerator characteristics                | 65<br>69 |

| 5.1        | Extracted Megablock and generated accelerator characteristics                | 89       |

| 5.2        | Executed instructions per clock cycle, for greedy and optimized scheduling   | 95       |

| 5.3        | Power consumption for software-only and accelerated runs                     | 102      |

| 5.4        | Energy consumption for software-only and accelerated runs                    | 102      |

| 6.1        | Generated accelerator characteristics and achieved speedups                  | 119      |

| 6.2        | Power and energy consumption for software-only and accelerated runs          | 123      |

| 6.3        | Generated multi-loop accelerator characteristics and speedups                | 124      |

| 6.4        | Accelerator generation scenarios                                             | 125      |

| 6.5        | Average cost of accelerators per scenario, normalized by a single MicroBlaze | 128      |