Received 1 July 2020; revised 28 August 2020; accepted 3 September 2020. Date of publication 21 September 2020; date of current version 4 November 2020.

The review of this article was arranged by Editor W. Y. Leong.

Digital Object Identifier 10.1109/JEDS.2020.3025336

# Generation of STDP With Non-Volatile Tunnel-FET Memory for Large-Scale and Low-Power Spiking Neural Networks

HISASHI KINO<sup>®</sup> 1 (Member, IEEE), TAKAFUMI FUKUSHIMA<sup>®</sup> 2 (Senior Member, IEEE), AND TETSU TANAKA<sup>2,3</sup> (Member, IEEE)

1 Frontier Research Institute for Interdisciplinary Sciences, Tohoku University, Sendai 980-8579, Japan 2 Department of Mechanical Systems Engineering, Graduate School of Engineering, Tohoku University, Sendai 980-8579, Japan 3 Department of Biomedical Engineering, Graduate School of Biomedical Engineering, Tohoku University, Sendai 980-8579, Japan

CORRESPONDING AUTHOR: H. KINO (e-mail: kino@lbc.mech.tohoku.ac.jp)

This work was supported by Japan Society for the Promotion of Science KAKENHI under Grant JP19K21953.

**ABSTRACT** Spiking neural networks (SNNs) have attracted considerable attention as next-generation neural networks. As SNNs consist of devices that have spike-timing-dependent plasticity (STDP) characteristics, STDP is one of the critical characteristics we need to consider to implement an SNN. In this study, we generated the STDP of a biological synapse with non-volatile tunnel-field-effect-transistor (tunnel FET) memory that has a charge-storage layer and a tunnel FET structure. Tunnel FET is a promising structure to reduce the operation voltage owing to its steep sub-threshold slope. Therefore, the non-volatile tunnel-FET memory we propose enables the implementation of low-operation-voltage SNNs. This article reports the I-V, programming, and both symmetric and asymmetric STDP characteristics of a non-volatile tunnel-FET memory with p-channel-MOS-like operation.

**INDEX TERMS** Spiking neural network, tunnel FET, MONOS, spike-timing-dependent plasticity, synaptic device.

## I. INTRODUCTION

Neuromorphic computing is expected to be a suitable architecture to process flexible tasks such as image recognition. In particular, neural networks (NNs) are promising candidates to perform cognitive tasks that cannot be readily executed via conventional von Neumann computing [1], [2]. Deep neural networks (DNNs) are a type of NN that have been widely used; they have achieved remarkable results in various fields. Spiking neural networks (SNNs) have also received considerable attention. Compared to DNNs, SNNs have the potential to realize low-power NN systems. This is because in DNNs, processing is performed using analog signals, whereas in SNNs, processing is performed using binary or ternary digital signals.

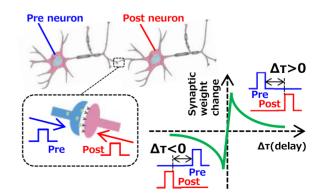

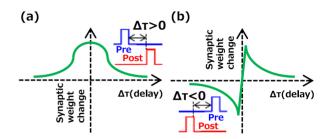

It is generally agreed that the weight coefficient changes of biological synapses are based on Hebbian learning. Fig. 1 shows the synaptic weight change based on Hebbian learning. In Hebbian learning, the weight coefficients of the synapse change according to the timing difference

FIGURE 1. Schematic illustration of the effect of the delay between the post and pre spike on synaptic weight changes.

between the signals arriving from the presynaptic and postsynaptic neurons. As the timing difference between the pre- and post-signals is reduced, the updated weight coefficients increase. However, when the difference is near

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

1266 VOLUME 8, 2020

zero, the coefficient rapidly approaches zero. To implement neuromorphic computing with Hebbian learning, a synaptic device constitutes a critical component [3], [4]. Many types of synaptic devices that consist of semiconductor memory have been developed. However, there are some issues to be resolved while implementing these devices. For example, a two-terminal device such as a resistivechange device needs additional switching devices. In the case of a volatile memory, such as static random-access memory (SRAM), high standby power consumption will be an issue. Therefore, some researchers have studied floatinggate-based synaptic devices with the spike-timing-dependent plasticity (STDP) of biological synapses [5], [6], as shown in Fig. 1 Floating-gate memory can reproduce the STDP of a biological synapse by exploiting the amount of injected charges. The injected charges induce a shift in the threshold voltage of the memory cell. Therefore, we can regard the threshold voltage shift as the synaptic weight change. Many prior studies have developed synaptic devices with floating-gate or charge-trapping memories, e.g., a metaloxide-nitride-oxide-semiconductor (MONOS) structure, to implement SNN circuits [7], [8]. Both floating-gate and charge-trapping memories are suitable for large-scale SNNs owing to their simple one-transistor structure compared with other non-volatile memories, such as phase-change random-access memory, resistive random-access memory, and spin-orbit torque switching [9]-[12].

Tunnel field-effect transistors (tunnel-FETs) have also attracted considerable attention as ultra-low-operation-voltage devices. As a tunnel FET has steep subthreshold slope characteristics owing to an operation based on band-to-band tunneling (BTBT), its operating voltage can be reduced. Thus, tunnel-FETs can reduce the power consumption of circuits.

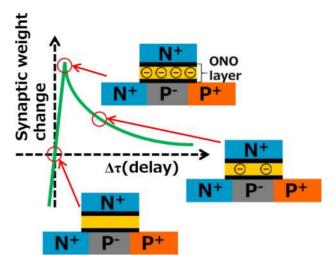

A non-volatile tunnel-FET memory consists of the MONOS and tunnel-FET structures [13]. This memory device has many advantages, such as low-voltage operation and small cell size. Therefore, a non-volatile tunnel-FET is a memory device with potential for large-scale integration and low-power operation. In this study, we propose the use of a non-volatile tunnel-FET memory as a synaptic device to achieve large-scale low-power SNN circuits, as shown in Fig. 2. The figure also shows the schematic images of how to reproduce the biological synapse STDP with non-volatile tunnel-FET memory. The proposed memory device can reproduce the synaptic weight coefficient using a number of trapped charges. In a previous study of ours, we demonstrated the symmetric and asymmetric STDP characteristics of a non-volatile tunnel FET with an operation similar to that of an n-channel metal-oxide-semiconductor (nMOS) [14]-[16]. Specifically, tunnel FETs can operate like an nMOSFET because of BTBT between the P-type source and the body under positive-biased gate. However, the tunnel current between different polar semiconductors results in a lower voltage operation compared with the tunnel current between a P-type drain and a P-type source, as shown in Fig. 3(b). In

FIGURE 2. Biological synapse STDP reproduced with threshold voltage shift induced by charge trapping.

this study, to induce tunnel current between the P-type body and the N-type source, we used p-channel MOS (pMOS) like operation with negative-biased gate.

This study concludes that a tunnel-FET-based charge trapping memory can reproduce the symmetric and asymmetric STDP characteristics of biological synapses. The STDP characteristics were obtained under pMOS-like operation with negative-biased gate.

#### II. NON-VOLATILE TUNNEL FET MEMORY

Charge-trapping memories have been typically used as synaptic devices to compose SNN circuits owing to their small cell area [17]. However, conventional charge-trapping memories require a high operation voltage, which leads to high power consumption. In addition, the power consumption will increase with the improvement of the integration degree of neural network circuits. Therefore, low-voltage synaptic devices are required to implement low-power largescale SNNs. To reduce the operation voltage, we propose a non-volatile tunnel-FET memory [13], [18]. The proposed memory device consists of the MONOS and tunnel-FET structures. The MONOS-structure memory is a suitable memory for implementing large-scale SNN circuits owing to the simple cell structure. Tunnel FETs achieve a steep sub-threshold slope through BTBT. Therefore, a tunnel-FETbased structure can provide the SNN circuit with a lower operation voltage. The proposed memory device structure is a promising candidate for implementing large-scale lowpower SNN circuits owing to the simple cell structure of the charge trapping memory and the steep sub-threshold slope of the tunnel FET.

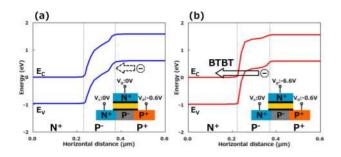

Fig. 3 shows the energy band diagram during OFF and ON state of the pMOS-like tunnel FET induced by BTBT effect between the N-type source and the P-type body. The threshold voltage of the proposed memory device is modulated by the quantity change of charge trapped in the SiN layer. We can use this threshold voltage as a synaptic weight. The

VOLUME 8, 2020 1267

FIGURE 3. Energy band diagram of (a) OFF-state and (b) ON-state non-volatile tunnel-FET memory with pMOS like operation.

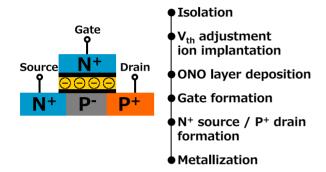

FIGURE 4. Process flow of the non-volatile tunnel-FET memory cell with MONOS structure.

proposed memory device is a one-transistor structure and has the possibility of low-voltage operation. Therefore, to implement large-scale and low-power SNN circuits, the proposed memory device structure is promising. In this study, we fabricated the proposed non-volatile tunnel-FET memory and evaluated the STDP characteristics.

# III. FABRICATION AND I-V CHARACTERISTICS

Fig. 4 illustrates the process flow of the non-volatile tunnel-FET memory. In this study, we used the ONO (SiO<sub>2</sub>/SiN/SiO<sub>2</sub>) layer for charge retention. First, we performed the isolation process on bulk Si wafers. Then, we formed SiO<sub>2</sub> layer with thermal oxidation. Subsequently, the SiN and SiO<sub>2</sub> layers were deposited by low-pressure chemical vapor deposition (LP-CVD). The thickness of the ONO layer was 8/15/3 nm. After ONO layer deposition, we also deposited the Poly-Si through LP-CVD as the gate electrode material. Then, we formed the gate electrode through inductively coupled plasma reactive-ion etching. The Ntype source and the P-type drain regions were subsequently formed through ion implantation. Each doped region was defined using an electron beam lithography system (JEOL: JBX-6300FS) with high alignment accuracy. The source and the drain regions were activated with rapid thermal annealing. The activation temperature and time were 1050 °C and 10 s, respectively. Finally, the metallization process was performed.

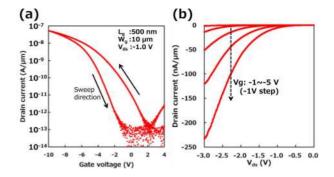

Fig. 5(a) and (b) shows the drain current and gate voltage  $(I_d - V_g)$  and the drain current and voltage between the drain and source  $(I_d - V_{ds})$  characteristics, respectively of

**FIGURE 5.** (a)  $I_d - V_g$  characteristics and (b)  $I_d - V_{ds}$  characteristics of the fabricated pMOS-like non-volatile tunnel-FET memory cell.  $I_d - V_d$  characteristics were measured under negative-biased gate.

FIGURE 6. (a) Symmetric and (b) asymmetric STDP characteristics.

the fabricated memory device. Here, the physical gate length and width were 0.5 µm and 10 µm, respectively. We measured the  $I_d - V_g$  characteristics with gate voltages ranging from -10 to 10 V and from 10 to -10 V. We observed the ON current under both positive and negative gate voltages. The ON current under positive gate voltage was induced by BTBT between the P-type drain and the body region. The ON current under negative gate voltage was induced by BTBT between the N-type source region and the P-type body regions. We also obtained a typical hysteresis of the conventional MONOS memory. The ON current was approximately 240 nA/\(\mu\)m at 3.0 V source-drain voltage and 5.0 V gate voltage in Fig. 5(b). The value of ON current was lower than that for a conventional MONOS memory. We need to consider a method that improves the ON current. We confirmed that the fabricated non-volatile tunnel-FET memory has the typical characteristics of memory devices. Next, we measured and evaluated the symmetric and asymmetric STDP characteristics, which are key characteristics to form SNNs.

# IV. STDP CHARACTERISTICS

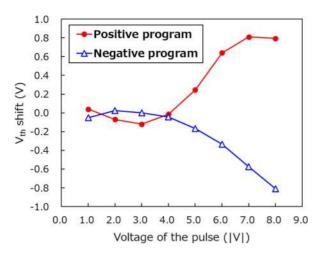

Both symmetric and asymmetric STDP characteristics, as shown in Fig. 6, are essential to implement SNNs. To decide the programming pulse for the STDP measurements, we evaluated the effect of the voltage of the programming pulse on the threshold voltage shift of the fabricated non-volatile tunnel-FET memory. Fig. 7 shows the measurement results. Both the source voltage and the drain voltages were set to 0 V during the programming and erasing operations. The threshold voltage ( $V_{th}$ ) shift was defined as the difference between the  $V_{th}$  of the programmed state and the original

1268 VOLUME 8, 2020

FIGURE 7. Effect of positive and the negative voltages of the pulse for positive and negative programming operation on the  $V_{th}$  shift.

FIGURE 8. Pulse setup for symmetric STDP measurement.

state obtained by the erasing operation. The pulse width  $(\tau_p)$  for the programming and erasing operations was 100 ms. Positive and negative voltages were applied to the gate electrode for the positive and negative programming operations, respectively. Here, the positive and the negative program signify the  $V_{th}$  shifts induced by the positive and the negative gate voltage, respectively. We can assume that the positive and the negative program were induced by the electron and hole injections, respectively. The  $V_{th}$  shift increased drastically at 4 V. These results indicate that a voltage below 4 V leads to little effect on the memory window of the fabricated non-volatile tunnel-FET memory cell. We used these results to decide the waveform to measure the STDP characteristics.

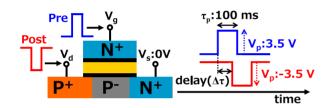

First, we measured the symmetric STDP characteristics of the non-volatile tunnel-FET memory cell using the measurement setup shown in Fig. 8. To evaluate the synaptic weight update, we measured the  $V_{th}$  shift produced by a pair of rectangular pulses. One pulse was applied to the gate electrode, whereas the other was applied to the drain. Here,  $\Delta \tau$  indicates the delay time between the two rectangular pulses. The width  $(\tau p)$  and the absolution value of the amplitude  $(|V_p|)$  were 100 ms and 3.5 V, respectively. The source voltage was 0 V during the programming operation. From the programming characteristic measurements presented in Fig. 7, we can conclude that only the pre-pulse cannot produce the critical effects on  $V_{th}$  of the fabricated non-volatile tunnel-FET memory cell. Therefore, it is inferred that we can obtain similar programming characteristics that are presented

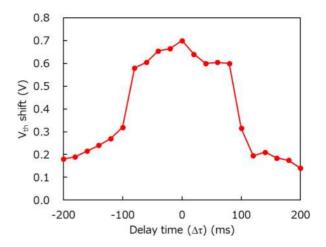

FIGURE 9. Effect of delay time on the  $V_{th}$  shift with the pulse setup shown in Fig. 8.

FIGURE 10. Pulse setup for asymmetric STDP measurement.

in Fig. 7 when the programming pulses are applied to the Ptype drain; this is because a similar field is induced between the gate and the body. Therefore, we could also conclude that only post-pulse cannot produce critical effects on the  $V_{th}$ . Fig. 9 shows the measurement results of the STDP characteristics for the fabricated non-volatile tunnel-FET memory cell using the pulse setup shown in Fig. 8. We observed that the fabricated device could reproduce symmetric STDP characteristics. A high voltage of 7.0 V was applied between the gate electrode and the P-type body when two pulses overlapped. Therefore, the time interval during which high voltage was applied decreased with an increase in the delay between two pulses. Thus,  $V_{th}$ , which depends on the trapping charge, is reduced by an increase in the delay time. This result indicates that we can use the proposed device as a synaptic device using  $V_{th}$  instead of the weight coefficient.

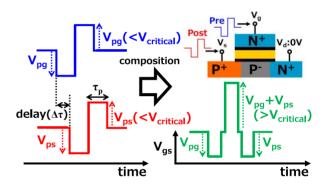

To reproduce asymmetric STDP characteristics of a biological synapse in the floating gate memory or the charge trapping memory, previous studies used triangular waveforms [19], [20]. However, triangular waveforms lead to an increase of the circuit scale and power consumption. In this study, we implemented asymmetric STDP characteristics of biological synapses using a bipolar pulse, which can be achieved with a low-scale circuit and low power consumption. Fig. 10 illustrates the bipolar pulses, which were

VOLUME 8, 2020 1269

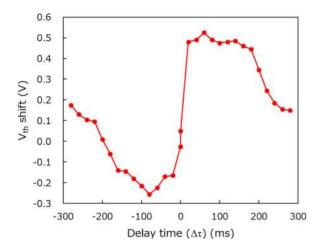

FIGURE 11. Effect of delay time on the  $V_{th}$  shift with the pulse setup shown in Fig. 10.

used for the measurement of STDP characteristics. A significantly positive voltage ( $>V_{critical}$ ), which could affect  $V_{th}$ , was applied to the SiN layer by the composite pulse when the delay was positive. By contrast, a significantly negative voltage  $(< -V_{critical})$  was applied to the SiN layer by the composite pulse when the delay was negative. The polarity of the voltage applied to the SiN layer depended on the direction of the delay. In addition, the time applied to the significant positive and negative voltages also depends on the delay. Therefore, we can implement asymmetric STDP characteristics of biological synapses with bipolar pulses. In the fabricated memory device, V<sub>critical</sub> was 4 V according to the programming characteristics presented in Fig. 7. Therefore, we determined that both  $V_{pg}$  and  $V_{ps}$  were 3.5 V.  $V_{pg}$  and  $V_{ps}$  denote the amplifier of the bipolar pulse applied to the gate and the drain, respectively.  $V_{pg}$  and  $V_{ps}$  cannot significantly affect  $V_{th}$  by themselves. However, when the delay is not zero, the composite pulse can sufficiently affect the  $V_{th}$  of the fabricated device owing to the high voltage of 7.0 V.

Fig. 11 shows the measurement results of the asymmetric STDP characteristics with both bipolar pulses. The source voltage was 0 V while applying the pre- and post-pulse signal. The pre- and post-pulse signals were applied to the gate and drain, respectively. These signals consisted of a bipolar pulse with 100 ms pulse width  $(\tau_p)$ . We achieved the asymmetric STDP characteristics, as shown in Fig. 6 (b), owing to the combination of the two simple bipolar pulses. These results indicate that the proposed non-volatile tunnel FET memory enables the implementation of SNN circuits. The realization of asymmetric STDP characteristics has been attempted with various memories. However, in many memories, the weights diverge near zero delay, [3], [21]-[23]. In actual biological synapses, the weight near zero delay is zero according to the Heb rule. The memory device developed in this study can imitate biological synapses well. Therefore, they can help create an SNN that is closer to actual biological systems.

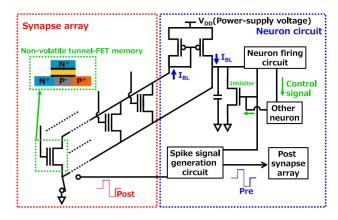

FIGURE 12. Target SNNs system with non-volatile tunnel-FET memories.

Furthermore, we are planning to develop an actual SNN, as shown in Fig. 12. This SNN consists of a synapse array and neuron circuits. In the synapse array, non-volatile tunnel-FET memories are arranged in an array. The result of the product sum operation using the weight factor saved in the memories is output to the neuron circuit. Then, the neuron firing circuit determines if the neurons will fire. Finally, to update the weight information, the spike generator sends post- and pre-signals to the previous and post synaptic arrays, respectively.

## V. CONCLUSION

We fabricated and evaluated a non-volatile tunnel-FET memory with MONOS and tunnel-FET structure to enable the implementation of low-power NN circuits. The fabricated devices exhibited typical  $I_d - V_g$  characteristics of a tunnel FET. Then, we demonstrated that the fabricated devices have the symmetric and asymmetric STDP characteristics of biological synapses. These results imply that the proposed memory device has the potential for implementing large-scale low-power SNN circuits. To enhance the performance of SNN circuits with non-volatile tunnel-FET memory, we consider that novel technologies such as heterojunctions [23], [24], two-dimensional materials [25], metal-nanodots flash memory [26], and three-dimensional integration [24], [27], are promising candidates. In the future, we plan to fabricate this SNN system with the nonvolatile tunnel-FET memory developed in this study and other novel technologies.

# **ACKNOWLEDGMENT**

This study was supported by the Frontier Research Institute for Interdisciplinary Sciences (FRIS) Tohoku University. It was also supported by the VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Cadence Design Systems. This study was conducted in the Micro/Nano-Machining Research and Education Center at Tohoku University.

1270 VOLUME 8, 2020

## **REFERENCES**

- E. M. Izhikevich and G. M. Edelman, "Large-scale model of mammalian thalamocortical systems," *Proc. Nat. Acad. Sci.*, vol. 105, no. 9, pp. 3593–3598, Mar. 2008, doi: 10.1073/pnas.0712231105.

- [2] P. U. Diehl and M. Cook, "Unsupervised learning of digit recognition using spike-timing-dependent plasticity," Front. Comput. Neurosci., vol. 9, pp. 1–9, Aug. 2015, doi: 10.3389/fncom.2015.00099.

- [3] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale memristor device as synapse in neuromorphic systems," *Nano Lett.*, vol. 10, no. 4, pp. 1297–1301, 2010, doi: 10.1021/nl904092h.

- [4] T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski, and M. Aono, "Short-term plasticity and long-term potentiation mimicked in single inorganic synapses," *Nat. Mater.*, vol. 10, no. 8, pp. 591–595, 2011, doi: 10.1038/nmat3054.

- [5] A. W. Smith, L. J. McDaid, and S. Hall, "A compact spike-timing-dependent-plasticity circuit for floating gate weight implementation," *Neurocomputing*, vol. 124, pp. 210–217, Jan. 2014, doi: 10.1016/j.neucom.2013.07.007.

- [6] R. Gopalakrishnan and A. Basu, "Robust doublet STDP in a floating-gate synapse," in *Proc. Int. Joint Conf. Neural Networks*, Beijing, China, 2014, pp. 4296–4301, doi: 10.1109/IJCNN.2014.6889631.

- [7] C. H. Kim et al., "Demonstration of unsupervised learning with spike-timing-dependent plasticity using a TFT-type NOR flash memory array," *IEEE Trans. Electron Devices*, vol. 65, no. 5, pp. 1774–1780, May 2018, doi: 10.1109/TED.2018.2817266.

- [8] H. Kim, J. Park, M. Kwon, J. Lee, and B. Park, "Silicon-based floating-body synaptic transistor with frequency-dependent short- and long-term memories," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 249–252, Mar. 2016, doi: 10.1109/LED.2016.2521863.

- [9] S. Kim et al., "NVM neuromorphic core with 64k-cell (256-by-256) phase change memory synaptic array with on-chip neuron circuits for continuous in-situ learning," in Tech. Dig. Int. Electron Devices Meeting (IEDM), Washington, DC, USA, Feb. 2015, pp. 1–4, doi: 10.1109/IEDM.2015.7409716.

- [10] X. She, Y. Long, and S. Mukhopadhyay, "Improving robustness of ReRAM-based spiking neural network accelerator with stochastic spike-timing-dependent-plasticity," in *Proc. Int. Joint Conf. Neural Netw.*, Budapest, Hungary, Jul. 2019, pp. 1–8, doi: 10.1109/IJCNN.2019.8851825.

- [11] W. Wang et al., "Computing of temporal information in spiking neural networks with ReRAM synapses," Faraday Discuss., vol. 213, pp. 453–469, Feb. 2019, doi: 10.1039/c8fd00097b.

- [12] A. Kurenkov, S. DuttaGupta, C. Zhang, S. Fukami, Y. Horio, and H. Ohno, "Artificial neuron and synapse realized in an antiferromagnet/ferromagnet heterostructure using dynamics of spin-orbit torque switching," Adv. Mater., vol. 31, no. 23, pp. 1–7, 2019, doi: 10.1002/adma.201900636.

- [13] H. Kino, T. Fukushima, and T. Tanaka, "Tunnel field-effect transistor charge-trapping memory with steep subthreshold slope and large memory window," *Jpn. J. Appl. Phys.*, vol. 57, Mar. 2018, Art. no. 04FE07, doi: 10.7567/JJAP.57.04FE07.

- [14] H. Kino, T. Fukushima, and T. Tanaka, "Development of non-volatile tunnel-FET memory as a synaptic device for low-power spiking neural networks," in *Proc. 4th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Penang, Malaysia, Apr. 2020, pp. 1–3, doi: 10.1109/EDTM47692.2020.9118027.

- [15] H. Kino, T. Fukushima, and T. Tanaka, "Spike timing dependent plasticity characteristics of tunnel FET based MONOS memory for low power neural network circuits," in *Proc. Int. Conf. Solid-State Devices Mater.*, 2019, pp. 673–674.

- [16] H. Kino, T. Fukusima, and T. Tanaka, "Symmetric and asymmetric spike-timing-dependent plasticity function realized in a tunnel-field-effect-transistor-based charge-trapping memory," *Jpn. J. Appl. Phys.*, vol. 59, Apr. 2020, Art. no. SGGB12, doi: 10.35848/1347-4065/ab6867.

- [17] Y. Du et al., "An analog neural network computing engine using CMOS-compatible charge-trap-transistor (CTT)," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 38, no. 10, pp. 1811–1819, Oct. 2019, doi: 10.1109/TCAD.2018.2859237.

- [18] H. Kino, T. Fukushima, and T. Tanaka, "New tunnel FET charge-trapping memory with large memory window for ultra low power operation," in *Proc. Int. Conf. Solid-State Devices Mater.*, 2017, pp. 791–792.

- [19] J. Park, M.-W. Kwon, H. Kim, S. Hwang, J.-J. Lee, and B.-G. Park, "Compact neuromorphic system with four-terminal Si-based synaptic devices for spiking neural networks," *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2438–2444, May 2017, doi: 10.1109/TED.2017.2685519.

- [20] M. Pankaala, M. Laiho, and P. Hasler, "Compact floating-gate learning array with STDP," in *Proc. Int. Joint Conf. Neural Netw.*, Atlanta, GA, USA, 2009, pp. 2409–2415.

- [21] H. Tan, S. Majumdar, Q. Qin, J. Lahtinen, and S. van Dijken, "Mimicking neurotransmitter release and long-term plasticity by oxygen vacancy migration in a tunnel junction memristor," *Adv. Intell. Syst.*, vol. 1, no. 2, 2019, Art. no. 1900036, doi: 10.1002/aisy.201900036.

- [22] D. H. Kang, H. G. Jun, K. C. Ryoo, H. Jeong, and H. Sohn, "Emulation of spike-timing dependent plasticity in nano-scale phase change memory," *Neurocomputing*, vol. 155, pp. 153–158, May 2015, doi: 10.1016/j.neucom.2014.12.036.

- [23] M. Kim, Y. K. Wakabayashi, M. Yokoyama, R. Nakane, M. Takenaka, and S. Takagi, "Ge/Si heterojunction tunnel field-effect transistors and their post metallization annealing effect," *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 9–15, Jan. 2015, doi: 10.1109/TED.2014.2371038.

- [24] K. Kato, T. Mori, Y. Morita, T. Matsukawa, M. Takenaka, and S. Takagi, "Source engineering for bilayer tunnel field-effect transistor with hetero tunnel junction: Thickness and impurity concentration," *Appl. Phys. Exp.*, vol. 13, Jul. 2020, Art. no. 074004, doi: 10.35848/1882-0786/ab9875.

- [25] K. Matsuura et al., "Sputter-deposited-MoS2 nMISFETs with top-gate and Al<sub>2</sub>O<sub>3</sub> passivation under low thermal budget for large area integration," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 1246–1252, 2018, doi: 10.1109/JEDS.2018.2883133.

- [26] Y. Pei et al., "MOSFET nonvolatile memory with high-density cobalt-nanodots floating gate and HfO<sub>2</sub> high-k blocking dielectric," *IEEE Trans. Nanotechnol.*, vol. 10, no. 3, pp. 528–531, May 2011, doi: 10.1109/TNANO.2010.2050331.

- [27] H. Kino, T. Fukusima, and T. Tanaka, "Investigation of TSV liner interface with multiwell structured TSV to suppress noise propagation in mixed-signal 3D-IC," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 1225–1231, 2019, doi: 10.1109/JEDS.2019.2936180.

**HISASHI KINO** (Member, IEEE) received the Ph.D. degree in bioengineering and robotics from Tohoku University, Sendai, Japan, in 2012, where he is currently an Assistant Professor with the Frontier Research Institute for Interdisciplinary Sciences.

**TAKAFUMI FUKUSHIMA** (Senior Member, IEEE) received the Ph.D. degree from the Department of Materials Science and Chemical Engineering, Yokohama National University, Yokohama, Japan, in 2003. He is currently an Associate Professor with the Department of Mechanical Systems Engineering and the New Industry Creation Hatchery Center, Tohoku University, Sendai, Japan.

**TETSU TANAKA** (Member, IEEE) received the B.S. and M.S. degrees in electronics engineering, and the Ph.D. degree in machine intelligence and systems engineering from Tohoku University, Sendai, Japan, in 1987, 1990, and 2003, respectively. In 2005, he joined Tohoku University as an Associate Professor, where he became a Professor with the Graduate School of Biomedical Engineering, in 2008.

VOLUME 8, 2020 1271