# Germanium-on-SOI Infrared Detectors for Integrated Photonic Applications

Steven J. Koester, Senior Member, IEEE, Jeremy D. Schaub, Member, IEEE, Gabriel Dehlinger, and Jack O. Chu

(Invited Paper)

Abstract—An overview of recent results on high-speed germanium-on-silicon-on-insulator (Ge-on-SOI) photodetectors and their prospects for integrated optical interconnect applications are presented. The optical properties of Ge and SiGe alloys are described and a review of previous research on SOI and SiGe detectors is provided as a motivation for the Ge-on-SOI detector approach. The photodetector design is described, which consists of lateral alternating p- and n-type surface contacts on an epitaxial Ge absorbing layer grown on an ultrathin-SOI substrate. When operated at a bias voltage of -0.5 V,  $10~\mu m \times 10~\mu m$  devices have dark current  $I_{\text{dark}}$ , of only  $\sim 10$  nA, a value that is nearly independent of finger spacing S, between  $S=0.3~\mu\mathrm{m}$  and  $1.3~\mu\mathrm{m}$ . Detectors with  $S=1.3~\mu m$  have external quantum efficiencies  $\eta$ , of 52% (38%) at  $\lambda = 895$  nm (850 nm) with corresponding responsivities of 0.38 A/W (0.26 A/W). The wavelength-dependence of  $\eta$ agrees fairly well with expectations, except at longer wavelengths, where Si up-diffusion into the Ge absorbing layer reduces the efficiency. Detectors with 10  $\mu$ m imes10  $\mu$ m area and  $S=0.6~\mu$ m have -3-dB bandwidths as high as 29 GHz, and can simultaneously achieve a bandwidth of 27 GHz with  $I_{\rm dark}=24$  nA, at a bias of only -1 V, while maintaining high efficiency of  $\eta = 46\%(33\%)$ , at  $\lambda = 895$  nm (850 nm). Analysis of the finger spacing and areadependence of the device speed indicates that the performance at large finger spacing is transit-time-limited, while at small finger spacing, RC delays limit the bandwidth. Methods to improve the device performance are presented, and it is shown that significant improvement in the speed and efficiency both at  $\lambda = 850$  and 1300 nm can be expected by optimizing the layer structure design.

*Index Terms*—Germanium, optoelectronic devices, photodetectors, silicon-on-insulator (SOI) technology.

#### I. INTRODUCTION

S bandwidth requirements for high-performance servers continue to rise, the incorporation of optical components to replace conventional copper interconnects for local I/O functions is being emphasized greatly [1]. The reason is that the traditional copper links cannot transmit longer than a few meters once the data rates increase beyond several gigabits per second per channel. Furthermore, the edge connector density is restricted using copper interconnects, placing an upper limit on the overall system performance. Not only would highly par-

Manuscript received October 31, 2005; revised August 7, 2006.

- S. J. Koester and J. O. Chu are with the IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 USA (e-mail: skoester@us.ibm.com; chuj@us.ibm.com).

- J. D. Schaub is with the IBM Austin Research Lab, Austin, TX 78758 USA (e-mail: schaubj@us.ibm.com).

- G. Dehlinger was with the IBM T. J. Watson Research Center, Yorktown Heights, NY10598 USA. He is now with Infineon Technologies, 9500 Villach, Austria (e-mail: gabriel.dehlinger@infineon.com).

Digital Object Identifier 10.1109/JSTQE.2006.883160

allel optical data links offer superior performance in terms of bandwidth–length product, but as the data rates scale these links should also increase the overall interconnect density, reduce power dissipation, and improve synchronization. The transition to optical interconnects is expected to occur first at the rack-to-rack level. However, as bandwidth requirements continue to increase, optical solutions will also be needed for board-to-board and eventually chip-to-chip interconnects [2].

Conventional high-speed fiber-optic components mainly utilize compound semiconductors (mostly III–V) due to their excellent light-emission and absorption properties, as well as the wide range of alloys and heterostructures that can be used to precisely optimize device performance in a given system application. Unfortunately, compound-semiconductor devices are generally too costly for utilization in server-based optical interconnects, due to the overhead associated with manufacturing optical components in a separate facility, as well as the costs associated with packaging and assembling the hybrid III–V/complementary metal-oxide-semiconductor (CMOS) interconnect subsystem. When combined with CMOS electronics, III–V-based systems also tend to suffer performance degradation due to packaging parasitics and the crosstalk associated with wire-bond leads.

For these reasons, the interest in utilizing Si-based optical components to realize a fully monolithic solution for high-performance optical interconnects is on the rise [3]. A potential advantage of monolithic integration is reduced cost, which results from the lower starting material costs, as well as the ability to leverage the volume manufacturing infrastructure of Si processing. Integrated optical interconnects could also improve performance by eliminating the parasitics and noise associated with hybrid packaging technology, and may eventually lead to the realization of higher interconnect densities.

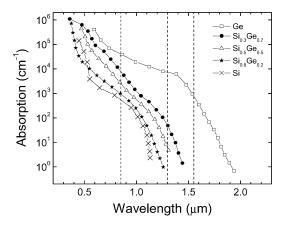

Unfortunately, the poor optical properties of Si have so far precluded the development of several key components needed for integrated optical interconnects. In particular, for receivers, weak absorption in the infrared region makes it difficult to realize high-performance photodetectors in Si. For example, at a wavelength  $\lambda=850$  nm, the most promising platform for nearterm optical interconnects due to the low cost of multimode fiber and the availability of relatively inexpensive GaAs vertical cavity surface-emitting laser (VCSEL) emitters, Si has a very low absorption coefficient of 600 cm $^{-1}$  [4], as shown in Fig. 1. The corresponding absorption depth  $\alpha^{-1}$  of 17  $\mu m$  makes it difficult to overcome the fundamental speed/responsivity tradeoffs associated with photodetector devices. Furthermore, Si is

Fig. 1. Plot of absorption coefficient versus wavelength for relaxed SiGe layers with Ge concentration ranging from 0% (Si) to 100% (Ge) [4], [6], [7].

transparent at  $\lambda=1300$  and 1550 nm, wavelength platforms that are standard for long-distance fiber-optic communications, but which could also be useful for future high-performance short-distance interconnects.

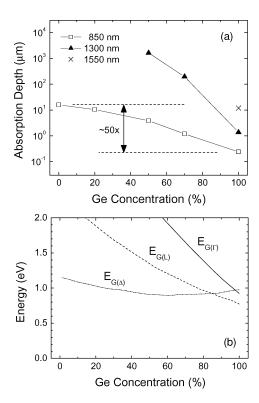

In recent years,  $Si_{1-x}Ge_x$  has been successfully incorporated into both bipolar and CMOS transistor-based manufacturing technologies [5]. However,  $Si_{1-x}Ge_x$  has a number of benefits for photonic applications as well, not the least of which is an increased absorption coefficient and absorption edge at longer wavelengths compared to Si [6]. Unfortunately, as shown in Fig. 1, the absorption advantages gained by  $Si_{1-x}Ge_x$  do not become significant until rather high Ge concentrations are reached, and that the strongest absorption occurs in pure Ge layers [7]. To illustrate this point more clearly, Fig. 2(a) shows the  $Si_{1-x}Ge_x$ absorption depth plotted as a function of the Ge concentration x, for three different wavelengths important for fiber-optic links. The plot shows that at  $\lambda = 850$  nm,  $\alpha^{-1}$  is improved by only a factor of 1.5 in Si<sub>0.8</sub>Ge<sub>0.2</sub> alloys compared to Si, and even for  $Si_{0.5}Ge_{0.5}$  the absorption depth is still  $\sim 4 \,\mu\text{m}$ , roughly only a factor of 4 smaller than Si. Similarly, at  $\lambda = 1300$  nm, the absorption depth is over  $100 \, \mu \text{m}$  at x = 0.7. In contrast, pure Ge has an absorption depth less than 300 nm at  $\lambda = 850$  nm, a factor over 50 times shorter than Si at the same wavelength. At  $\lambda=1300$  nm,  $\alpha^{-1}$  is about  $1\,\mu\mathrm{m}$  in Ge, close to the same as that in GaAs at  $\lambda=850$  nm. Pure Ge even absorbs at  $\lambda=1550$ nm, though the absorption depth ( $\alpha^{-1} \sim 10 \,\mu\text{m}$ ) is only slightly less than Si at  $\lambda = 850$  nm.

The Ge-concentration dependence of the absorption properties can be understood by an examination of Fig. 2(b), which plots the calculated energy gaps associated with various valence-to-conduction-band transitions in  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  as a function of x [8]. The plot shows that while the energy associated with the  $\Delta$ -point transition has a very weak Ge-concentration dependence, the indirect L-point and the direct  $\Gamma$ -point transition energies decrease rapidly at high Ge concentrations. This dependence explains why, at low x, the absorption coefficient at  $\lambda=850$  nm is a very weak function of x, but increases more rapidly at higher x as L- and  $\Gamma$ -point absorptions take effect. At  $\lambda=1300$  nm, even higher Ge concentrations are needed for the upper conduction-band transitions to take effect, with

Fig. 2. (a) Plot of absorption depth versus Ge concentration for SiGe alloys at three different wavelengths. (b) Calculated energy gaps in SiGe as a function of Ge concentration between the valence-band maximum and the L-,  $\Delta$ -, and  $\Gamma$ -point conduction-band local minima [8].

L- and  $\Gamma$ -point transitions not allowed until  $x \gtrsim 0.8$  and 0.9, respectively.

From the above discussion, it is clear that the high absorption coefficient in Ge makes it an extremely attractive material for use in high-performance infrared detectors. In addition to its absorption advantage, Ge also has improved mobilities compared to Si, with intrinsic bulk electron and hole mobilities of 3900 and 1900 cm<sup>2</sup> /V·s, respectively. The mobility advantage should not only improve the device speed compared to Si, but also allow operation at low voltages, a key priority for integrated detector applications.

Despite the advantages described above, Ge can be a challenging material to integrate into a CMOS in the manufacturing environment. The main difficulty is the 4.2% lattice mismatch between Si and Ge, which can cause rough growth and lead to high defect densities in epitaxial films grown on Si [9]. The process temperatures for Ge and Si devices could also be incompatible since Ge melts at 934°C, and dopant diffusion is generally much faster in Ge than in Si. Finally, for detector applications, excess dark current is a major concern, not only due to the low band gap of Ge (0.66 eV at room temperature), but also due to the defects mentioned earlier, and the known surface passivation difficulties of Ge [10]. In recent years, many of the above-mentioned difficulties have been overcome to varying extents, and the status of Ge-on-Si technology, as well as the remaining challenges, will be discussed in later sections.

In this paper, we describe our approach toward realizing an optimized Ge photodetector that can allow high-performance

operation suitable for integrated optical interconnect applications. The approach, based upon Ge-on-silicon-on-insulator (Ge-on-SOI) technology, allows the demonstration of photodetectors that provide nearly all of the characteristics desirable for integrated optoelectronic receivers, and could be practical for near-term 10- and 40-Gb/s optical interconnects applications. The detectors also have good potential for extendibility to higher speeds and operation at longer wavelengths.

In the following sections, we first discuss the performance requirements for integrated photodetectors, and review recent developments in Si- and Ge-based high-performance photodetectors. Then, we describe the design and fabrication strategy of our Ge-on-SOI detectors approach. The dc and high-frequency properties of these devices are described next, followed by an assessment of the overall performance figures of merit. Finally, we discuss possible methods of improving the device design to allow even higher performance in the future.

## II. BACKGROUND

# A. Performance Requirements for Integrated Detectors

As a preface to describing previous work on Si and Ge photodetectors, it is beneficial to review the performance requirements of photodetectors to be used for integrated receiver applications. First, it is important that the devices are capable of high-speed operation, particularly in order to accommodate the anticipated bit rates of future optical interconnect applications. Considering that optoelectronic interconnects utilizing hybrid detectors have already been demonstrated [2], it is essential that integrated devices operate at 10 Gb/s with a foreseeable path to at least 40-Gb/s operation in the future. Together with high-speed operation, the devices must have reasonable responsivity in order to maintain acceptable signal-to-noise ratio and ease performance and noise constraints on amplifier circuitry. For datacom applications, to achieve adequate receiver sensitivity, photodiode responsivities must be  $\gtrsim 0.1 \,\mathrm{A/W}$  [11], corresponding to external quantum efficiencies  $\eta$  of 15%, 10%, and 8% at  $\lambda = 850, 1300$ , and 1550 nm, respectively. Dark current in the integrated photodetectors is an important issue, since the shot noise associated with this leakage current can increase the bit error rate (BER). In typical detectors, dark currents less than  $1 \mu A$  are desirable, though a precise value of the required dark current depends upon the speed of operation and the amplifier design. An often-overlooked requirement of integrated detectors is low-voltage operation. It would be desirable for the detector and CMOS circuitry to operate on a single power supply. This requirement essentially restricts the bias voltage to < 5 V, and for advanced CMOS generations, to biases as low as 1 V.

## B. Bulk Si Detectors

A number of bulk Si photodetector geometries have been reported in the literature [11]–[14]. A good example of the performance of bulk Si detectors designed for integrated receiver applications is described in [11], where a lateral p-i-n photodetector was fabricated on a high-resistivity bulk Si substrate.

Those detectors had a high external quantum efficiency of  $\eta = 85\%$  at  $\lambda = 850$  nm. However, even at a bias of -10 V (-30 V), -3-dB bandwidths of only 124 MHz (234 MHz) were obtained. This is a direct result of the long absorption depth in Si, where a majority of the electron-hole pairs are generated deep within the substrate, far from the high-field drift region generated by the surface electrodes. A novel approach to improving bulk detectors was described by Yang et al. [14], who demonstrated a lateral trench detector (LTD) that consisted of a lateral p-i-n detector with 7- $\mu$ m-deep trench electrodes designed to maintain a uniform electric field deep within the absorbing region. These detectors were able to simultaneously show high efficiency ( $\eta = 68\%$ ) and high-speed operation (3 GHz) at  $\lambda = 670$  nm. However, at longer wavelengths of 850 nm, the devices still suffered from degraded bandwidth due to carrier generation and collection below the electrodes.

#### C. SOI Detectors

The use of SOI substrates has been investigated extensively to improve the performance of Si-based photodetectors [11], [15]–[22]. This technique is particularly attractive given the widespread acceptance of SOI technology as a platform for high-performance CMOS [23]. The main benefit gained by using SOI is that the buried insulator can be used to prevent carriers generated in the substrate (below the oxide) from reaching the surface electrodes above the oxide. The index contrast offered by the buried oxide has the additional advantage that it can reflect a portion of the incident light back into the absorbing layer, thus improving efficiency.

Perhaps the best example of speed improvements that can be gained using SOI photodetectors has been shown by Liu *et al.* [15], who demonstrated metal–semiconductor–metal (MSM) detectors on thin SOI substrates with bandwidth as high as 140 GHz. However, these results also reveal a fundamental difficulty with the SOI approach, which is low responsivity due to the thin absorbing region. The devices in [15], which used an absorbing layer of 200 nm, had external quantum efficiencies of only 2.0% and 0.87%, at  $\lambda=650$  and 780 nm, respectively. SOI detectors with thicker absorbing layers have been reported in [22]. Predictably, the thicker absorbing layer improved the efficiency (to 24% at  $\lambda=840$  nm), but also resulted in a reduced bandwidth of 3.4 GHz.

One approach to improving the bandwidth–efficiency product in Si photodetectors is to utilize novel detector geometries to decouple the transport and absorption lengths in the detector. The LTD geometry described earlier is one such technique, and when fabricated on SOI wafers, circular LTD detectors with 75  $\mu m$  diameter [19] have produced values of  $\eta=51\%$  and 2-GHz bandwidth at  $\lambda=850$  nm, and bandwidths over 10 GHz, with comparable efficiency, have been realized in smaller area (14  $\mu m \times 17 \ \mu m$ ) detectors [20]. The waveguide detector geometry is another approach (commonly used for integrated photonics in III–V materials) to decouple the transport distance from the absorption length in a low-capacitance configuration with thin absorbing layers. Recent demonstrations of these devices on SOI [17] have produced bandwidths of 15 and 8 GHz in

geometries producing external efficiencies of  $\eta=2\%$  and 12%, respectively.

The resonant-cavity detector design [24] is another technique that can be applied to Si detectors [25]–[27] to improve efficiency while maintaining a thin absorbing layer. Schaub et al. [27] reported an example of such detectors that utilized Si laterally grown over a Si/SiO<sub>2</sub> Bragg reflecting mirror stack. These devices produced a -3-dB bandwidth of 34 GHz, while displaying high quantum efficiency (up to  $\eta = 42\%$ ) at wavelengths corresponding to sharp resonance peaks in the responsivity. However, in off-resonance conditions, the efficiency dropped by over an order of magnitude, suggesting that devices based upon the resonant-cavity design could be very sensitive to process-induced variations. Detectors with roughened [28] or grating [18] backside reflectors can accomplish much of the same effect as resonant-cavity structures, and 84-GHz-bandwidth devices with  $\eta = 19\%$  at  $\lambda = 850$  nm have been demonstrated using the latter technique [18].

#### D. SiGe and Ge Detectors

A second method for improving the bandwidth–efficiency product is to utilize an alternative material with increased absorption coefficient compared to Si. As described in the previous section, SiGe, and ideally, pure Ge absorbing layers are very promising materials to achieve enhanced absorption at  $\lambda=850$  nm, while having the additional benefit of extending the absorption edge to wavelengths beyond 1550 nm.

Much of the early work on photodetectors utilizing SiGe involved the use of quantum well or strained-layer superlattice absorbing regions [29]–[35] because these structures can be grown pseudomorphically on Si substrates. Strained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  structures are useful because the strain reduces the band gap, allowing absorption at longer wavelengths for a given Ge concentration. However, for operation at  $\lambda=1300$  nm, these layers tend to have very low absorption, and typically require the use of a waveguide geometry in order to achieve high responsivity [34].

The concept of using relaxed Ge-on-Si as an absorbing layer for a photodetector was first proposed and demonstrated in the pioneering work of Luryi et al. [36]. However, not until recently has the Ge-on-Si concept been resurrected to study its potential for high-performance fiber-optic applications. Several approaches to the Ge-on-Si detector design have been investigated. In order to overcome the lattice-mismatch problem described in the previous section, a number of demonstrations of Ge detectors grown on graded buffer layers have been made, since these structures can greatly reduce the density of threading dislocations penetrating into the top layer [37]. Samavedam et al. [38] demonstrated vertical p-i-n devices with excellent dark current density of only 2 pA/ $\mu$ m<sup>2</sup> on graded buffer detectors, while lateral p-i-n geometries on graded buffers with  $\eta=49\%$  and 3.8-GHz bandwidth were demonstrated by Oh et al. [39]. However, devices on thick graded buffer layers could suffer from integration difficulties due to nonplanarity with the CMOS devices. Furthermore, though low defect density are needed for very large-scale integration (VLSI) CMOS

applications, it is not clear whether elaborate defect-reduction techniques are needed for photodetectors.

For this reason, more recent work on Ge-on-Si detectors has focused on the use of thin buffer layers, or even direct growth of Ge on Si. Such structures are beneficial for integration due to the thinner layers used, and it has been found that reasonable defect densities ( $\sim 10^7 \ \rm cm^{-2})$  can still be achieved in such structures when the layers are subjected to post-growth annealing, or grown in limited-area structures [40]. Initial demonstrations of direct-grown Ge-on-Si detectors were made by Colace  $et\ al.$  [41] and Masini  $et\ al.$  [42], as well as in [43], where lateral MSM devices were demonstrated with similar speed, responsivity, and dark current to devices grown on graded buffer layers. Vertical p-i-n photodiodes utilizing Ge on thin SiGe buffers were also demonstrated by Huang  $et\ al.$  [44] who reported devices with  $\eta=61\%$  and 8.1-GHz bandwidth using backside illumination at  $\lambda=1300\ \rm nm.$

Our previous work in this area was performed using Ge-on-bulk-Si lateral p-i-n photodiodes with Ge layers of only  ${\sim}400$  nm [45]. Because of the thin absorbing layer and the transparency of Si at  $\lambda>1100$  nm, these devices were able to achieve bandwidths in excess of 15 GHz at  $\lambda=1300$  nm, and operated at extremely low voltage of  ${\sim}1$  V, but had low quantum efficiency of only 2.5%. For operation at  $\lambda=850$  nm, the efficiency improved to  $\eta=30\%$ , but the bandwidth was degraded due to absorption in the underlying Si, similar to the bulk Si devices described earlier. More details of these device results will be described in the following section. Very recently, the ultrathin Ge-on-Si approach was demonstrated in a vertical p-i-n photodiode by Jutzi  $et\ al.$  [46]. These devices had 39-GHz bandwidth and efficiency values of  $\eta=16\%$  at  $\lambda=1298$  nm, and  $\eta=2.8\%$  at  $\lambda=1552$  nm.

## E. Summary of Previous Work

The results from the previous work described here clearly demonstrate that tremendous improvement in the performance of Si-based photodetectors can be achieved both from a device design perspective by using the SOI technology, and from a materials perspective by using the Ge absorbing layers. In the next section, we describe our approach toward combining the two technologies to produce Ge-on-SOI detectors that can simultaneously achieve nearly all of the performance requirements needed for integrated detector applications on Si, and provide an extendable platform that could lead to further performance enhancements in the future.

#### III. GE-ON-SOI PHOTODETECTORS

#### A. Device Description

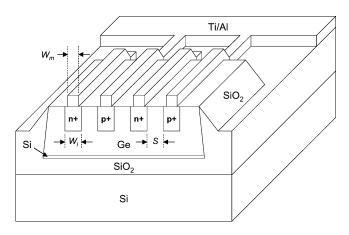

The basic Ge-on-SOI photodetector device design used in the present paper is shown in Fig. 3. The device structure consists of a Ge absorbing layer directly on a thin SOI wafer. In this design, the high absorption coefficient of the Ge layer allows the absorbing region to be kept very thin, while the buried oxide serves to prevent any carriers generated in the underlying Si from reaching the top electrodes. The SOI layer is also kept as

Fig. 3. Schematic diagram of Ge-on-SOI photodetector structure. The figure is not drawn to scale.

thin as possible, not only to maintain maximum efficiency in the absorbing region, but also to minimize the amount of Si available for diffusion into the Ge layer upon subsequent annealing. This is an important feature of this design, since dilution of the Ge layer with even a small amount of Si can reduce the detector efficiency, especially at longer wavelengths. The device utilizes a lateral p-i-n geometry, which is favored over a vertical detector design for several reasons. First of all, the lateral design results in a planar contact scheme, which is simpler to integrate than a vertical structure. The top-side contacts also minimize the impact of defects that form at the lower Si-Ge interface as a result of the lattice mismatch between Si and Ge. The lateral p-i-n structure is also preferred over an MSM design to ensure that the dark current is kept as low as possible. Finally, the device has interdigitated metal fingers overlaying the implanted electrodes. The metal fingers, while blocking a portion of the incident light, considerably reduce the series resistance of the device, which is crucial for high-speed operation.

#### B. Fabrication

The fabrication of the photodetectors has already been described in detail in [47]. Briefly, the layer structure was grown by ultrahigh vacuum chemical vapor deposition (UHV-CVD) directly on an ultrathin (15 nm) SOI substrate with buried oxide thickness of 140 nm. The epitaxial layer structure consisted of a 30-nm Si buffer layer, followed by a thick Ge layer. SEM inspection indicated that the combined thickness of the Si and Ge layers was  $\sim 400$  nm. After growth, the layer structure was subjected to thermal cyclic annealing to reduce the density of threading dislocations [40]. In all, during this step, the accumulated thermal budget was 900 °C for 1 h, and the threading dislocation density was reduced from  $\sim 1 \times 10^9~{\rm cm}^{-2}$  before annealing to  $\sim 1 \times 10^8$  cm<sup>-2</sup> after annealing. In addition to reducing the dislocation density, the annealing also improved the mobility. Hall measurements on the as-grown sample indicated p-type conduction with hole mobility of 710 cm<sup>2</sup>/V·s, while after annealing the mobility improved to  $1140 \text{ cm}^2/\text{V} \cdot \text{s}$  [48].

The devices were fabricated by first defining square mesas with areas A of  $10 \,\mu\text{m} \times 10 \,\mu\text{m}$ ,  $20 \,\mu\text{m} \times 20 \,\mu\text{m}$ , and

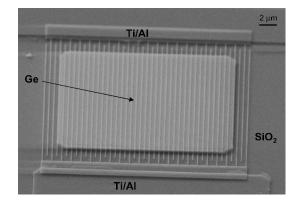

Fig. 4. Tilted-view SEM micrograph of completed Ge-on-SOI photodetector with a mesa area of 20  $\mu$ m $\times$ 20  $\mu$ m and implant spacing of 0.3  $\mu$ m. The width of the metal fingers is 0.2  $\mu$ m.

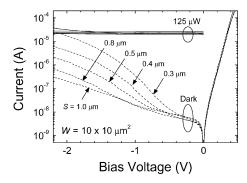

Fig. 5. Current–voltage characteristics of  $10~\mu\mathrm{m}\times10~\mu\mathrm{m}$  photodiodes with finger spacings S, ranging from 0.3 to  $1.0~\mu\mathrm{m}$ . The plot shows both the dark current and the photocurrent from a 822-nm source, using the illumination scheme described in the text.

$30~\mu\mathrm{m} \times 30~\mu\mathrm{m}$ . Oxide was then deposited on the sidewalls in a self-aligned manner (as shown in Fig. 3) to prevent leakage arising from the metal fingers overlapping the edges of the devices. The device fabrication was completed by the formation of the n- and p-type implants, activation, and patterning of Ti/Al (30/150 nm) contact metal. No antireflection coating (ARC) was used. For the devices described in this paper, the following device dimensions have been utilized. The electrode spacing S, defined as the distance between the edges of adjacent n- and p-type implants, ranges from 0.3 to  $1.3~\mu\mathrm{m}$ . The implanted region width  $W_{\rm i}$ , and the metal finger width  $W_{\rm m}$ , have both been kept fixed at values of  $0.3~\mathrm{and}~0.2~\mu\mathrm{m}$ , respectively. The metal fingers are nominally centered within the boundaries of the implanted regions. An SEM micrograph of a completed  $20~\mu\mathrm{m} \times 20~\mu\mathrm{m}$  device with  $S=0.3~\mu\mathrm{m}$  is shown in Fig. 4.

# C. DC Characteristics

Fig. 5 shows a plot of the dark current  $I_{\rm dark}$  versus the bias voltage  $V_{\rm b}$ , for 10  $\mu{\rm m}\times10~\mu{\rm m}$  detectors with finger spacing S, ranging from 0.3 to 1.0  $\mu{\rm m}$ . All the devices show diodelike behavior, with rectifying current–voltage characteristics and very similar current at forward bias. The reverse leakage current has a strong bias dependence that scales roughly with the finger spacing, particularly in the range of S=0.3 to  $0.5~\mu{\rm m}$ . The

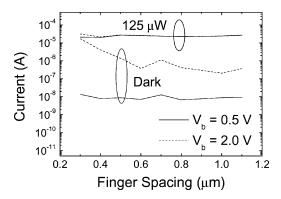

Fig. 6. Plot of the dark current and the photocurrent as a function of finger spacing for two different applied bias voltages  $V_{\rm b}$ . The dark current is essentially independent of finger spacing at  $V_{\rm b}=-0.5$  V.

dark current increases with decreasing S at  $|V_{\rm b}| \gtrsim 0.5 \, \rm V$ , but at sufficiently low bias,  $I_{\rm dark}$  is relatively independent of S. The photocurrent for the different devices is also shown in Fig. 5. For these measurements, the devices have been overfilled with 822-nm light using a lensed, 50- $\mu$ m-core multimode fiber. The total power exiting the fiber was  $125 \, \mu$ W. As shown in the figure, the photocurrent is nearly independent of bias, and decreases slightly for smaller finger spacing due to the greater shadowing from the metal fingers, an effect that will be described in more detail later.

In order to highlight the significance of the bias dependence of the dark current, Fig. 6 shows a plot of the photocurrent and the dark current versus S at different values of  $V_{\rm b}$ . The plot shows that at  $V_{\rm b} = -2 \, {\rm V}$ ,  $I_{\rm dark}$  increases significantly with decreasing finger spacing, becoming comparable to the photocurrent at  $S=0.3\,\mu\mathrm{m}$ . However, at  $V_{\rm b}=-0.5\,\mathrm{V},I_{\rm dark}$  is considerably lower, and essentially independent of S. Even for detectors with  $S = 0.3 \,\mu\text{m}$ , a dark current of only 13 nA is obtained at  $V_{\rm b} = -0.5\,{\rm V}$ . This current value is over three orders of magnitude lower than the photocurrent at  $125-\mu W$  incident power. The ability to reduce the dark current at low bias voltages is important, since, as will be shown later, devices with  $S=0.4 \, \mu \mathrm{m}$ can achieve nearly the same bandwidth at  $V_{\rm b} = -0.5 \, {\rm V}$  as they can at -2 V. It is this ability to operate at low bias voltages, while still maintaining high speed, which is a key benefit of the Ge-on-SOI detector scheme.

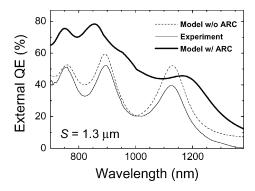

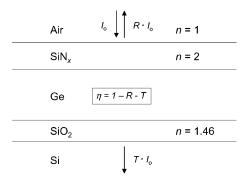

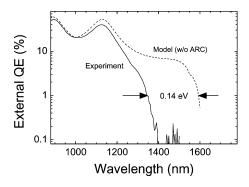

Fig. 7 shows the measured external quantum efficiency plotted versus the wavelength for a  $30~\mu m \times 30~\mu m$  device with  $S=1.3~\mu m$ , as well as the calculated responses for the detectors with and without an ARC. The quantum efficiency was measured using a tungsten-halogen light source and a monochrometer. In this setup, the light was focused onto the active area of the device using free-space optics, where a calibrated commercial germanium photodetector was used to measure the incident optical power at each wavelength. The calculated quantum efficiency values have been obtained using a transfer matrix method, assuming the layer stack shown in Fig. 8. For these calculations, the buried oxide thickness is 140 nm, while a Ge absorbing layer thickness of 392 nm has been utilized, a value that provides the best possible fit to the measured data. For the model utilizing an ARC, the SiN<sub>x</sub> layer has a thickness of 120 nm and a refractive

Fig. 7. Measured external quantum efficiency for a Ge-on-SOI detector with 30  $\mu$ m  $\times$  30  $\mu$ m area and finger spacing  $S=1.3~\mu$ m. Also shown is the calculated efficiency with and without a SiN $_x$  (n=2) ARC. The calculated results have been scaled by a factor of 0.87 to account for the shadowing from the metal fingers.

Fig. 8. Diagram of layer stack utilized for transmission matrix calculations of the detector quantum efficiency shown in Fig. 7.

index of 2.0, while for the model with no ARC, the thickness of the  $SiN_x$  layer is zero. The refractive index and the absorption values for Ge have been taken from [7], and in all the cases the calculated quantum efficiency values have been scaled by a factor of 0.87 to account for the shadowing from the metal fingers. For the sake of simplicity, the calculations do not take into account the thin Si part of the absorbing region.

Fig. 7 shows that, as expected, due to the buried oxide, the quantum efficiency is an oscillatory function of the wavelength, with a peak external efficiency of 52% occurring at  $\lambda = 895$  nm, while at  $\lambda = 850$  nm, the devices have  $\eta = 38\%$ . These values correspond to responsivities of 0.38 and 0.26 A/W, respectively. The devices maintain efficiencies greater than 20% up to  $\lambda = 1200$  nm, before the efficiency (responsivity) drops sharply to  $\eta = 3.4\%$  (0.036 A/W) at  $\lambda = 1300$  nm. The magnitude of the resonance effects observed for the Ge-on-SOI devices is considerably less than that occurring in the resonant-cavity Si detectors [27]. The results of our calculation for detectors using a 120-nm  $SiN_x$  ARC show that the resonances can be nearly eliminated, while the quantum efficiency can be improved to  $\eta = 78\%$ . This value is very close to the maximum theoretical value of  $\eta = 87\%$ , which is limited by the shadowing factor of the metal fingers. The calculations also indicate that improved absorption can be obtained at longer wavelengths, with a quantum efficiency of  $\eta=22\%$  predicted for  $\lambda=1300$  nm, a value that corresponds to a responsivity of 0.23 A/W. This latter result

Fig. 9. Semi-log plot of the measured and calculated external quantum efficiency for a 30  $\mu$ m  $\times$  30  $\mu$ m Ge-on-SOI detector with finger spacing  $S=1.3\,\mu$ m. The difference between the measured and the expected cutoff wavelength corresponds to an energy difference of 0.14 eV.

suggests that the operating range of these detectors can be extended to longer wavelengths, and that the layer structure can be optimized to achieve higher speeds at shorter wavelengths. Further details of the device design optimization are provided in the next section.

For wavelengths in the range of 600 nm  $< \lambda < 1200$  nm, a reasonably good agreement between the model and the experiment is obtained. However, for  $\lambda > 1200$  nm, the measured quantum efficiencies become much lower than the values predicted by the model. For instance at  $\lambda = 1300$  nm,  $\eta$  is only 3.4% compared to the predicted value of  $\eta = 9.3\%$ . To understand the origin of the discrepancy at longer wavelengths, the results from Fig. 7 have been expanded and plotted on a log scale in Fig. 9. The plot shows that the deviation between the simulated and the measured responses gets larger with increasing wavelength up to  $\lambda \sim 1400$  nm, beyond which the device responsivity can no longer be measured. However, the model predicts that this cutoff should not occur until  $\lambda > 1600$  nm. In our earlier studies, we postulated that this discrepancy occurs due to Si diffusion into the Ge absorbing region during the high-temperature cyclic annealing utilized to reduce the defect density [47]. Despite the fact that the degree of up-diffusion has not been measured directly, if we assume that the absorption is primarily dominated by the  $\Gamma$ -point transition in Ge, then the change in the cutoff wavelength can be used to estimate the amount of Si in the Ge absorbing region. The plot in Fig. 9 shows that the cutoff wavelength corresponds to a 0.14-eV higher  $\Gamma$ -point transition energy  $E_{G(\Gamma)}$  than that predicted for pure Ge. Since Fig. 2(b) predicts that  $E_{G(\Gamma)}$  increases by 25 meV for every 1% mole fraction of Si added to Ge, the atomic percentage of Si calculated to have diffused into the Ge layer from thermal annealing is 6%.

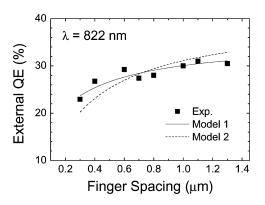

For high-speed applications, it is important that high efficiency can be maintained in devices with smaller finger spacings. However, the efficiency is expected to drop as S decreases, due to the increased shadowing from the metal fingers. Therefore, the quantum efficiency was measured for devices with smaller finger spacing, and the results are shown in Fig. 10. Here,  $\eta$  is plotted versus finger spacing for 30  $\mu$ m  $\times$ 30  $\mu$ m detectors at a single incident wavelength of  $\lambda=822$  nm. (It

Fig. 10. Plot of the external quantum efficiency for Ge-on-SOI photodetectors as a function of finger spacing at  $\lambda=822$  nm along with two different electrode shadowing models described in the text. The wavelength corresponds to a minimum in the efficiency, as shown in Fig. 7.

should be noted that this wavelength corresponds to a minimum in the  $\eta$  versus  $\lambda$  curve shown in Fig. 7.)

The results show that the quantum efficiency ranges between a minimum value of  $\eta = 23\%$  at  $S = 0.3 \,\mu\text{m}$ , and a maximum value of  $\eta = 31\%$  at  $S = 1.1 \,\mu\text{m}$ . To understand the finger spacing dependence better, the results have been modeled according to two functions. Model 1 assumes that shadowing only occurs under the metal fingers, while model 2 assumes that the carriers generated within the exposed n- and p-type implanted regions on either side of the metal fingers also do not contribute to the photocurrent. Mathematically, model 1 can be described by  $\eta \propto (S + W_{\rm i} - W_{\rm m})/(S + W_{\rm i})$ , while the formula for model 2 is  $\eta \propto S/(S+W_i)$ . The results have then been fitted to the experimental data and plotted in Fig. 10. The fits clearly show that model 1 matches the data more closely than model 2, indicating that the exposed part of the implanted regions do not affect the quantum efficiency. This result is encouraging as it suggests that in optimized geometries even smaller electrode spacing may be possible before the onset of excessive shadowing limits the ability to obtain acceptable responsivities.

# D. Pulse Response Characteristics

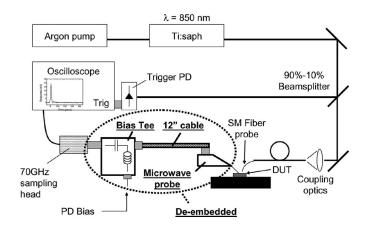

The high-frequency properties of the devices have been characterized extensively using impulse response measurements. A diagram of the setup used for these measurements is shown in Fig. 11. The devices were illuminated using a 850-nm modelocked Ti-sapphire laser, with a pulse width of 1–2 ps, pulse repetition rate of 13 ns, and a steady-state optical power of  $\sim 3 \,\mu W$ . The devices were contacted using a microwave probe, and the resulting photocurrent was measured using a high-speed oscilloscope with a 70-GHz sampling head. The data have been analyzed by performing a Fourier transform of the impulse response in order to determine the frequency-domain response. For the transformed frequency-dependent characteristics, the frequency response of the bias tee, the electrical probe, and the 12-in. cable resulted in a combined attenuation of just over 0.1 dB/GHz. Therefore, in order to make an accurate determination of the detector bandwidth, the responses of these components

Fig. 11. Diagram of the test setup used for the impulse response measurements. The responses of the items indicated in bold have been de-embedded from the transformed frequency response characteristics.

Fig. 12. Impulse response of a 10  $\mu$ m  $\times$  10  $\mu$ m Ge-on-SOI detector with finger spacing  $S=0.4\,\mu$ m at a bias of -1 V and wavelength  $\lambda=850$  nm. Impulse response for a similar 10  $\mu$ m  $\times$  10  $\mu$ m Ge-on-bulk-Si detector with  $S=0.34\,\mu$ m (inset).

were de-embedded from the frequency-dependent data reported in this paper.

The impulse response for a 10  $\mu$ m  $\times$ 10  $\mu$ m detector with  $S=0.4~\mu$ m at  $V_{\rm b}=-1~\rm V$  is shown in Fig. 12, where the voltage developed by the transient photocurrent across the 50- $\Omega$  input of the high-speed oscilloscope is plotted versus time. The response consists of a single sharp peak with full-width at half-maximum (FWHM) of only 14.8 ps. This result is in contrast to our previous results for Ge-on-bulk-Si detectors [45], where the main peak is accompanied by a longer time-scale response, associated with electron-hole pair generation in the Si substrate and subsequent slow diffusion of the deep carriers to the surface contacts. The pulse response for that device, which had similar dimensions ( $A=10~\mu$ m  $\times$ 10  $\mu$ m and  $S=0.34~\mu$ m) to the Ge-on-SOI device, is shown in the inset of Fig. 12.

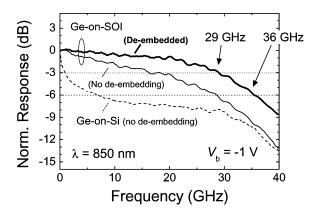

In order to extract the bandwidth of the devices, the Fourier transform of the impulse response has been calculated and the response of the bias tee, probe, and cable de-embedded as described earlier. The resulting frequency response is shown in Fig. 13, where the curve has been normalized to equal 0 dB at

Fig. 13. Normalized Fourier transforms of the impulse responses from the Ge-on-SOI and Ge-on-bulk-Si photodetectors shown in Fig. 12. The curve for the Ge-on-bulk-Si device has not been de-embedded, while the transforms both with and without de-embedding are shown for the Ge-on-SOI device.

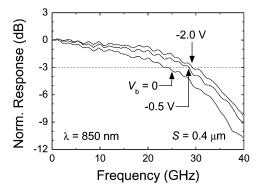

Fig. 14. Normalized frequency response for a 10  $\mu$ m  $\times$  10  $\mu$ m Ge-on-SOI detector with  $S=0.4~\mu$ m at bias voltages of 0, -0.5, and -2.0 V, showing -3 dB bandwidths of 25, 27, and 29 GHz, respectively.

a frequency of 10 MHz. Also shown in the figure is the (unde-embedded) transform of the Ge-on-bulk-Si detector pulse response shown in the inset of Fig. 12. In order to provide a consistent comparison, the un-de-embedded response of the Ge-on-SOI detector has also been included in the figure.

The de-embedded frequency response of the Ge-on-SOI device indicates a -3-dB bandwidth of 29 GHz, and a -6-dB bandwidth of 36 GHz at  $V_{\rm b}=-1\,\rm V$ . The response shows very little attenuation at low frequencies, with only  $\sim\!\!1$  dB of attenuation at 20 GHz. However, due to the carrier generation in the underlying Si layer, the Ge-on-bulk-Si device shows significant attenuation at low frequencies, having -3- and -6-dB bandwidths of 1 and 6 GHz, respectively. The fact that the Geon-SOI device eliminates this low-frequency tail, and maintains a flat response over a broad frequency range, underscores the advantage of the Ge-on-SOI device design for high-speed operation at  $\lambda=850\,\rm nm$ .

Fig. 14 shows the frequency response for 10  $\mu$ m  $\times$ 10  $\mu$ m Ge-on-SOI detectors with a finger spacing of  $S=0.4\,\mu$ m at  $V_{\rm b}=0,-0.5,$  and -2.0 V. The plot shows that the bandwidth saturates at very low bias voltages. At  $V_{\rm b}=-0.5$  V, the bandwidth is 27 GHz, which is nearly the same as the 29-GHz bandwidth obtained at  $V_{\rm b}=-2.0$ V. Even at  $V_{\rm b}=0,$  a bandwidth of 25 GHz is determined for these devices. Given the dark

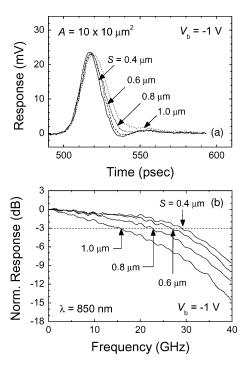

Fig. 15. (a) Impulse response of 10  $\mu$ m  $\times$  10  $\mu$ m Ge-on-SOI detectors with finger spacings S, ranging from 0.4 to 1.0  $\mu$ m at  $V_{\rm b}=-1$  V and  $\lambda=850$  nm. (b) Corresponding normalized frequency response for same devices as in (a).

current data shown in Fig. 6, these results are very significant as they indicate that our devices can maintain high speed while operating in a regime of low dark current. The excellent zerobias operation also suggests that the detectors may be suitable for use in differential amplifier circuit configurations, which can reduce the noise and improve the BERs for sensitive receiver applications [49].

Impulse response measurements have also been performed on  $10~\mu\mathrm{m} \times 10~\mu\mathrm{m}$  detectors with different finger spacing. The results of these measurements for devices with S=0.4 to  $1.0~\mu\mathrm{m}$  at  $V_{\rm b}=-1~\mathrm{V}$  are shown in Fig. 15(a). The plot shows that the FWHM increases with increasing finger spacing, from a value of 14.8 ps at  $S=0.4~\mu\mathrm{m}$ , to values of 16.2, 16.7, and 19.3 ps for devices with S=0.6,0.8, and  $1.0~\mu\mathrm{m}$ , respectively. The normalized frequency responses for the same devices are shown in Fig. 15(b). As expected from the pulse response measurements, the detectors with the smallest finger spacing have the highest bandwidths. The -3-dB bandwidths extracted from the data in Fig. 15(b) are 29, 27, 22, and 16 GHz, for devices with S=0.4,0.6,0.8, and  $1.0~\mu\mathrm{m}$ , respectively.

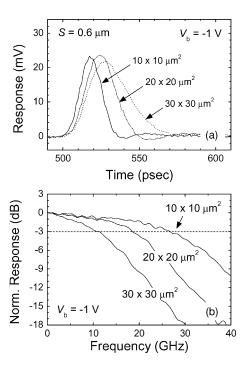

Pulse response measurements for detectors with different areas are shown in Fig. 16. Fig. 16(a) shows the impulse response for detectors with  $A=10~\mu m \times 10~\mu m$ ,  $20~\mu m \times 20~\mu m$ , and  $30~\mu m \times 30~\mu m$ , for a fixed finger spacing  $S=0.6~\mu m$  at  $V_{\rm b}=-1$  V. The plot in Fig. 16(a) indicates that the device performance slows considerably with a larger detector size, with the FWHM increasing from 16.2 ps at  $A=10~\mu m \times 10~\mu m$ , to 22.3 and 30.1 ps for 20  $\mu m \times 20~\mu m$  and 30  $\mu m \times 30~\mu m$  detectors, respectively. Once again, the transform of the pulse response is shown in Fig. 16(b), where -3-dB bandwidths of

Fig. 16. (a) Impulse response of Ge-on-SOI detectors with  $S=0.6~\mu m$ , and device areas ranging from  $10~\mu m \times 10~\mu m$  to  $30~\mu m \times 30~\mu$  at  $V_b=-1~V$  and  $\lambda=850~nm$ . (a) Corresponding normalized frequency response for same devices as in (b).

27, 19, and 11 GHz are extracted for devices with respective areas of 10  $\mu$ m ×10  $\mu$ m, 20  $\mu$ m ×20  $\mu$ m, and 30  $\mu$ m ×30  $\mu$ m.

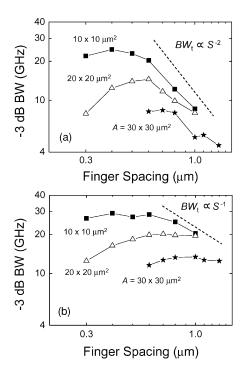

Insight into the speed-limiting mechanisms of the detectors can be gained by an investigation of the finger spacing dependence of the bandwidth for different device areas. The results of this analysis are shown in Fig. 17, which shows log-log plots of the -3-dB bandwidth versus finger spacing for the three detector sizes at zero and high bias ( $|V_b| > 2 \text{ V}$ ). The results confirm the performance improvement with decreasing area, as at every finger spacing the bandwidth increases as the area decreases. However, the devices also show an interesting trend; with decreasing S, the bandwidth tends to increase, then reaches a maximum value, and subsequently starts to decrease again. Furthermore, the finger spacing at which the maximum occurs is different for each detector area. At zero bias, for  $A = 10 \ \mu \text{m} \times 10 \ \mu \text{m}$ , the maximum bandwidth BW<sub>max</sub>, occurs for  $S=0.4\,\mu\text{m}$ , while at  $A = 20 \,\mu\text{m} \times 20 \,\mu\text{m}$  and  $30 \,\mu\text{m} \times 30 \,\mu\text{m}$ , BW<sub>max</sub> is achieved at S=0.6 and  $0.7\,\mu\mathrm{m}$ , respectively. At high bias, BW<sub>max</sub> occurs at a larger finger spacing (S = 0.4, 0.7, and  $0.8 \,\mu\text{m}$ , respectively) than at  $V_{\rm b}=0$ , and the bandwidth has a less-pronounced finger spacing dependence at high bias.

The results of Fig. 17 can be understood by modeling the speed-limiting mechanism as being affected by two factors, the transit-time delay and the RC delay. At zero bias, the transit time delay  $\tau_{\rm t}$  can be estimated as follows:

$$\tau_{\rm t} = 0.5 \left(\frac{W_{\rm d}^2}{V_{\rm bi}}\right) \left(\frac{1}{\mu_{\rm e}} + \frac{1}{\mu_{\rm h}}\right) \tag{1}$$

where  $\mu_{\rm e}$  and  $\mu_{\rm h}$  are the respective electron and hole mobilities,  $W_{\rm d}$  is the depletion width, and  $V_{\rm bi}$  is the built-in voltage. In

Fig. 17. Log–log plot of -3-dB bandwidth versus finger spacing for detectors with different areas. (a) At zero bias. (b) At high bias ( $|V_b| > 2 \text{ V}$ ).

a lateral p-i-n geometry,  $W_{\rm d}$  depends not only on S, but also on the absorbing layer thickness  $t_{\rm Ge}$ . However, in the limit of  $S\gg t_{\rm Ge},W_{\rm d}$  approaches S, and so (1) can approximated by

$$\tau_{\rm t} \approx 0.5 \left(\frac{S^2}{V_{\rm bi}}\right) \left(\frac{1}{\mu_{\rm e}} + \frac{1}{\mu_{\rm h}}\right).$$

(2)

The relation in (2) assumes that transport is not limited by velocity saturation, a reasonable assumption at zero bias and large finger spacing. At high-bias voltages, the device operation approaches the opposite limit, where the transport is expected to be dominated by velocity saturation. Once again, assuming  $W_{\rm d} \to S$  for large S, the velocity-saturated transit time delay can be calculated as

$$\tau_{\rm t} \approx 0.5 \, S \, \left( \frac{1}{v_{\rm sat(e)}} + \frac{1}{v_{\rm sat(h)}} \right)$$

(3)

where  $v_{\rm sat(e)}$  and  $v_{\rm sat(h)}$  are the saturated velocities for electrons and holes, respectively. Assuming that the transit-time-limited - 3-dB bandwidth BW $_{\rm t}$  equals  $(2\pi\tau_{\rm t})^{-1}$ , then (2) and (3) indicate that at zero bias BW $_{\rm t} \propto 1/S^2$ , and at high bias, BW $_{\rm t} \propto 1/S$ . As shown in Fig. 17, the trends predicted by (2) and (3) appear to match the experimental data very well, with bandwidth versus S characteristics asymptotically approaching the expected power-law behavior in the limit of large S, both at high and zero bias.

For small finger spacings, the measured bandwidths deviate from the transit-time-limited behavior described earlier. This deviation is believed to be due, in large part, to the onset of RC-limited performance. This conclusion is supported by the area-dependent results in Fig. 17, where larger area devices deviate from the transit-time-limited performance at higher values of S than the smaller area devices. In order to confirm this trend, admittance measurements were performed at 1 MHz on the de-

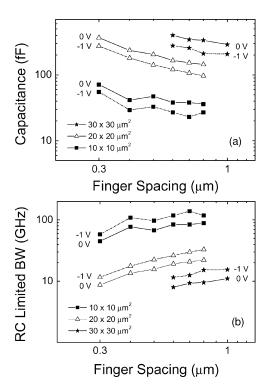

Fig. 18. (a) Device capacitance plotted versus finger spacing at  $V_{\rm b}=0$  and -1 V for devices with areas ranging from  $10~\mu{\rm m}\times10~\mu{\rm m}$  to  $30~\mu{\rm m}\times30~\mu{\rm m}$ . (b) RC-limited bandwidth versus finger spacing for same devices as in (a).

vices to determine the capacitance as a function of finger spacing at different bias voltages. The results are shown in Fig. 18(a), which plots the capacitance versus finger spacing at  $V_{\rm b}=0$  and -1 V. In this figure, the capacitance of an open-circuit probe-pad geometry has been subtracted in order to determine the intrinsic device capacitance. The figure shows that the capacitance scales with increasing device area and also increases with decreasing S. As expected, the zero-bias capacitance is also consistently higher than the capacitance at  $V_{\rm b}=-1$  V.

From the capacitance measurements, a rough calculation of the RC-limited bandwidth BW<sub>RC</sub>, can be determined by assuming  $BW_{RC} = (2\pi\tau_{RC})^{-1}$ , where  $\tau_{RC} = RC$ . For these calculations, we assume that C is equal to the capacitance values in Fig. 18(a), and  $R = 50 \Omega$ , which is simply the resistance of the terminating load. The value of BW<sub>RC</sub> calculated in this manner is only an estimate, due to additional series resistance components that may be present, and uncertainty as to the effect of the probe pads on the admittance at microwave frequencies. Nevertheless, Fig. 18(b) plots  $BW_{RC}$  versus S for the three different device areas at  $V_{\rm b}=0$  and -1 V. The plot shows that the values of BW<sub>RC</sub> extracted from the 20  $\mu$ m  $\times$  20  $\mu$ m and 30  $\mu$ m  $\times$  30  $\mu$ m detectors agree quite well with the experimental data for the same detector areas shown in Fig. 17, both at  $V_{\rm b} = 0$  and -1 V, suggesting that the performance of the large-area detectors is indeed RC-limited at small S. For the 10  $\mu$ m  $\times$ 10  $\mu$ m devices, the extracted BW<sub>RC</sub> values are much higher than the measured bandwidths. This discrepancy is likely due to the effect of the probe-pad capacitance, which is neglected in our calculation. This result suggests that the RC-limited performance of the 10  $\mu$ m ×10  $\mu$ m detectors could

Fig. 19. Maximum bandwidth–efficiency product (at  $\lambda=895$  nm) plotted versus finger spacing for  $10~\mu m \times 10~\mu m$  Ge-on-SOI detectors at various bias voltages.

be improved further by reducing parasitics associated with the probe-pad geometry. Clearly, additional microwave s-parameter measurements are needed to clarify the impact of the probe pads on the RC-limited performance, and more accurately determine the intrinsic bandwidth limitations of these devices.

#### IV. DISCUSSION

#### A. Overall Performance Assessment

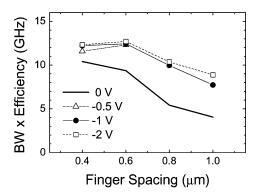

As discussed in Section II, the properties needed for integrated photodetectors are high speed, high responsivity, low dark current, and low operating voltage. Since it is important that all of these figures of merit are achieved at the same time, we have attempted to assess the ability of our Ge-on-SOI detectors to simultaneously provide these performance requirements. To do this, we have first identified the device dimensions and operating conditions that provide the optimum performance. The results of this analysis are shown in Fig. 19, where the bandwidthefficiency product of the  $10~\mu m \times 10~\mu m$  detectors is plotted as a function of the finger spacing for bias voltages ranging from  $V_{\rm b}=0~{\rm to}-2~{\rm V}$ . In this analysis, the data of Figs. 7 and 10 have been utilized to calculate the maximum efficiency as a function of finger spacing corresponding to the responsivity maximum at  $\lambda=895~{\rm nm}$ .

The plot in Fig. 19 shows that the highest bandwidth efficiency product is achieved at  $S = 0.4 \,\mu\mathrm{m}$  for  $V_{\rm b} = 0$ , but at  $|V_b| \ge 0.5 \,\mathrm{V}$ , the maximum shifts to  $S = 0.6 \,\mu\mathrm{m}$ . This shift occurs due to the fact that the devices with  $S=0.4\,\mu\mathrm{m}$  have lower efficiency as a result of the increased shadowing factor of the metal fingers, as described in Fig. 10. At zero bias, the devices with  $S=0.4\,\mu\mathrm{m}$  have higher bandwidth than at  $S = 0.6 \,\mu\text{m}$ , which compensates for the lower efficiency. However, at higher bias, the devices tend to have similar bandwidths, giving the device with  $S = 0.6 \,\mu\mathrm{m}$  the overall bandwidth–efficiency advantage. At  $V_{\rm b}=0$  and -0.5 V, bandwidth–efficiency products of 10.4 and 11.6 GHz are obtained for  $S=0.4\,\mu\mathrm{m}$ , while at  $V_\mathrm{b}=-0.5$  and -1.0 V, the  $S=0.6 \,\mu\mathrm{m}$  device produces bandwidth–efficiency values of 12.3 and 12.4 GHz, respectively. Further increasing the bias up to -4 V enables bandwidth–efficiency products as high as 13.2 GHz [47], but as will be described later, the slight improvement in the performance is offset by the much higher dark current that occurs at these voltages.

Finally, the results can be combined with the dark current data to determine the optimum operating voltage. The devices with  $S=0.6 \,\mu\mathrm{m}$  have a low  $I_{\mathrm{dark}}$  value of 7 nA at  $V_{\mathrm{b}}=-0.5\,\mathrm{V}$ , but a bandwidth of only 25 GHz. At  $V_{\rm b} = -1 \, \rm V$ , the bandwidth increases to 27 GHz, with only a slight increase in  $I_{\rm dark}$  to 24 nA. For  $|V_{\rm b}| > 1$  V, the bandwidth increases only marginally, going up to 29 GHz at  $V_{\rm b} = -4$  V. However at  $V_{\rm b} = -4$  V, the dark current exceeds 9  $\mu$ A, making it impractical to operate the devices at such a high bias. The optimum performance metrics for the 10  $\mu$ m ×10  $\mu$ m detectors with S=0.4 and  $0.6 \mu$ m are summarized in Table I. The results clearly show that the Ge-on-SOI detectors in their current state can meet the simultaneous performance requirements needed for integrated optical interconnect applications at 10 Gb/s and higher. Recently, these predictions have been confirmed by measurements of Ge-on-SOI detectors integrated with CMOS receiver circuits that display sensitivities of -11.0 dBm at 12.5 Gb/s [50] and operate error-free to data rates as high as 19 Gb/s [51].

## B. Outlook for Improved Performance

Despite the excellent performance of the current detector technology, it is important that a pathway should exist to improve the device performance even further for future applications. In this section, we describe how the performance can be optimized, not only for operation at  $\lambda=850$  nm, but at longer wavelengths as well.

The simplest and most obvious method of improving the performance is through the use of an ARC. The simulations shown in Fig. 7 indicate that with no other modification to the structure, a properly designed  $\mathrm{SiN}_x$  ARC could improve the external quantum efficiency by a factor of  $1.3 \times (2.0 \times)$  at  $\lambda = 895$  nm (850 nm). This improvement alone could increase the bandwidth–efficiency product to over 20 GHz, though the possible adverse effects of the  $\mathrm{SiN}_x$  ARC on the parasitic capacitance of the device would need to be evaluated.

The efficiency of the devices, particularly at longer wavelengths, could also be improved dramatically by optimizing the layer structure design and post-growth annealing process. As described earlier, substantial up-diffusion of Si into the Ge likely occurs due to the aggressive cyclic annealing utilized to reduce the defect density. Therefore, reduction of the underlying SOI layer thickness could help to limit the amount of Si available for diffusion during this process. Furthermore, recent results have shown that such aggressive annealing may not be necessary and that reduced defect density can be achieved by the use of lower temperature annealing, as well as selective-area growth. As shown in Fig. 7, an optimized process with minimal SiGe mixing could result in values of  $\eta > 20\%$  at  $\lambda = 1300$  nm.

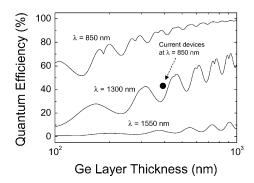

Much greater improvements in the device efficiency can be achieved by a complete optimization of the entire layer stack. We have performed such an optimization using transfer matrix calculations on the idealized layer structure shown in Fig. 8. The results are shown in Fig. 20, where the maximum quantum efficiency is plotted versus the Ge thickness, where at

| Finger<br>spacing<br>(µm) | Bias<br>(V) | Ext. QE<br>at 850 nm<br>(%) | Ext. QE<br>at 895 nm<br>(%) | Responsivity<br>at 850 nm<br>(A/W) | Responsivity<br>at 895 nm<br>(A/W) | BW<br>(GHz) | I <sub>dark</sub> (nA) | Area (μm²) |

|---------------------------|-------------|-----------------------------|-----------------------------|------------------------------------|------------------------------------|-------------|------------------------|------------|

| 0.4                       | -0.5        | 30                          | 42                          | 0.21                               | 0.30                               | 27          | 8                      | 10 x 10    |

| ,,                        | -1.0        | ,,                          | ,,                          | ,,                                 | ,,                                 | 29          | 85                     | ,,         |

| 0.6                       | -0.5        | 33                          | 46                          | 0.23                               | 0.33                               | 25          | 7                      | 10 x 10    |

| **                        | 1.0         | ,,                          | ,,                          | ,,                                 | ,,                                 | 27          | 24                     | ,,         |

TABLE I

PERFORMANCE METRICS FOR GE-ON-SOI DETECTORS INDICATING SIMULTANEOUS ACHIEVEMENT OF HIGH BANDWIDTH,

HIGH EFFICIENCY/RESPONSIVITY, LOW DARK CURRENT, AND LOW OPERATING BIAS

Fig. 20. Plot of the calculated optimum quantum efficiency as a function of Ge thickness at  $\lambda=850$ , 1300, and 1550 nm, using the model layer structure in Fig. 8. No shadowing from the metal fingers has been assumed for these calculations.

each x-axis value, the thicknesses of the  $SiN_x$  and  $SiO_2$  layers have been tuned for maximum absorption in the Ge layer. This plot indicates that not only can much higher efficiencies be achieved utilizing the current absorbing layer thickness  $(\sim 400 \text{ nm})$ , but that with proper tuning, much thinner Ge layers can be utilized to achieve the same responsivity as the current detectors. For instance, Fig. 20 shows that quantum efficiencies of 50% (not including shadowing) can be achieved for a Ge thickness of only 100 nm. If the finger spacing were correspondingly reduced to S = 100 nm, it is conceivable that tremendous improvements in the bandwidth could also be achieved. Performance improvement at such smaller finger spacings would, however, require reduction of the intrinsic junction capacitance, or a significant reduction in the metallization resistance. At least some improvement in these parameters should be possible due to the nonoptimized fabrication process utilized for the current devices. Finally, the results in Fig. 20 also show that with proper optimization of the absorbing layer thickness the prospects for efficient detector operation at  $\lambda = 1300$  nm can be greatly improved. For instance, the results of Fig. 20 predict that quantum efficiencies as high as 40% can be expected at  $\lambda = 1300$  nm for Ge absorbing layer thicknesses of only 310 nm.

It is important to remember that the optimization study assumes that the Si layer beneath the Ge absorbing region can be reduced to arbitrarily thin layers. Though some promise for creating "pure" Ge-on-insulator exists, either through wafer bonding [52] or novel epitaxial techniques [53], using the current direct Ge growth process, a minimum SOI layer thickness of  $\sim \! 10$  nm would probably need to be maintained. Also, in order to realize speed improvements by correspondingly reducing the

finger spacing and Ge layer thickness, the RC-limited delay time would have to be reduced. Such improvement may be possible in thin Ge layers due to the reduced fringing capacitance associated with the deep n- and p-type contacts. The device area can be reduced as well, though further reduction of the device size could make the use of lensed fibers or integrated lenses necessary to allow efficient optical coupling into the detector, and may lead to alignment difficulties with the optical fiber as well.

Finally, although our single-buried-oxide Ge-on-SOI design is advantageous due to its compatibility with current CMOS technology, the results in Fig. 20 show that this structure has little prospect for achieving efficiencies much greater than 10% at  $\lambda = 1550$  nm. Despite the fact that our model does not include strain effects that can improve absorption at longer wavelengths [54], alternative geometries may still have to be utilized for optimal operation at 1550 nm. Recently, very promising results have been obtained by Dosunmu et al. [55], who demonstrated Geon-SOI Schottky detectors with  $\eta = 59\%$  at  $\lambda = 1550$  nm, and bandwidths as high as 12 GHz. The resonant-cavity photodetector concept can also be applied to Ge-on-SOI detectors, and promising results using Ge on double-buried-oxide structures have recently been demonstrated [56]. Finally, another possible alternative for achieving efficient absorption at  $\lambda = 1550$  nm in Ge is the use of a waveguide geometry similar to that utilized for Si and strained SiGe detectors [17], [29]–[32], [34], [35]. The use of Ge in a waveguide fashion is very advantageous due to the relatively short absorption length of 10  $\mu$ m at  $\lambda = 1550$  nm, which could allow low-capacitance geometries to be realized. This structure is also compatible with other SOI-based optical devices such as modulators and switches that have been intensively studied in recent years, due to their promise for realizing fully integrated optical systems on Si substrates [57].

#### V. CONCLUSION

In conclusion, we have demonstrated the feasibility of high-performance infrared detectors based upon Ge-on-SOI technology, which are suitable for integrated optical interconnect applications in high-performance servers. For operation at  $\lambda=850$  nm, the devices meet all of the requirements of integrated detector operation, including high speed, high efficiency, low operating bias, and low dark current. The Ge-on-SOI detector design has potential for integration with standard CMOS, and should be extendable to even higher speeds, and operation at longer wavelengths. However, continued investigation into these devices is needed, particularly

to develop integration strategies with CMOS, as well as to understand and improve yield and reliability issues for Ge-based devices in a manufacturing environment. Nevertheless, the approach we have developed has tremendous potential not only for integrated optical interconnects but also for serving as a basic high-speed detector platform for a wide range of novel Si-based optoelectronic applications.

#### REFERENCES

- A. F. Benner, M. Ignatowski, J. A. Kash, D. M. Kuchta, and M. B. Ritter, "Exploitation of optical interconnects in future server architectures," *IBM J. Res. Dev.*, vol. 49, pp. 755–775, 2005.

- [2] L. Schares et al., ""Terabus'—A waveguide-based parallel optical interconnect for Tb/s-class on-board data transfers in computer systems," presented at the 31st Eur. Conf. Opt. Commun., Glasgow, Scotland, 2005.

- [3] R. A. Soref, "Si-based optoelectronics," *Proc. IEEE*, vol. 81, no. 12, pp. 1687–1706, Dec. 1993.

- [4] D. F. Edwards, "Silicon (Si)," in Handbook of Optical Constants of Solids,

E. D. Palik, Ed. Orlando, FL: Academic, 1985, pp. 547–569.

- [5] D. L. Harame et al., "The revolution in SiGe: Impact on device electronics," Appl. Surf. Sci., vol. 224, pp. 9–17, 2004.

- [6] J. Humlicek, F. Lukes, and E. Schmidt, "Silicon–germanium alloys (Si<sub>x</sub>Ge<sub>1-x</sub>)," in *Handbook of Optical Constants of Solids II*, E. D. Palik, Ed. Boston, MA: Academic, 1991, pp. 607–636.

- [7] R. F. Potter, "Germanium (Ge)," in Handbook of Optical Constants of Solids, E. D. Palik, Ed. Orlando, FL: Academic, 1985, pp. 465–478.

- [8] M. V. Fischetti and S. E. Laux, "Band structure, deformation potentials, and carrier mobility in strained Si, Ge and SiGe alloys," *J. Appl. Phys.*, vol. 80, pp. 2234–2252, 1996.

- [9] B. Cunningham, J. O. Chu, and S. Akbar, "Heteroepitaxial growth of Ge on (1 0 0) Si by ultrahigh vacuum, chemical vapor deposition," *Appl. Phys. Lett.*, vol. 59, pp. 3574–3576, 1991.

[10] G. W. Anderson, M. C. Hanf, P. R. Norton, Z. H. Lu, and M. J. Graham,

- [10] G. W. Anderson, M. C. Hanf, P. R. Norton, Z. H. Lu, and M. J. Graham, "The S-passivation of Ge(1 0 0)-(1 × 1)," *Appl. Phys. Lett.*, vol. 66, pp. 1123–1125, 1996.

- [11] J. D. Schaub, R. Li, S. M. Csutak, and J. C. Campbell, "High-speed monolithic silicon photoreceivers on high resistivity and SOI substrates," *J. Lightw. Technol.*, vol. 19, no. 2, pp. 272–278, Feb. 2001.

- [12] L.-H. Laih, T.-C. Chang, Y.-A. Chen, W.-C. Tsay, and J.-W. Hong, "Characteristics of MSM photodetectors with trench electrodes on p-type Si wafer," *IEEE Trans. Electron Devices*, vol. 45, no. 9, pp. 2018–2023, Sep. 1998.

- [13] J. Y. L. Ho and K. S. Wong, "Bandwidth enhancement in silicon metalsemiconductor-metal photodetector by trench formation," *IEEE Photon. Technol. Lett.*, vol. 8, no. 8, pp. 1064–1066, Aug. 1996.

- [14] M. Yang et al., "A high-speed, high-sensitivity silicon lateral trench photodetector," *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 395–397, Jul. 2002.

- [15] M. Y. Liu, E. Chen, and S. Y. Chou, "140-GHz metal-semiconductor-metal photodetectors on silicon-on-insulator substrate with a scaled active layer," *Appl. Phys. Lett.*, vol. 65, pp. 887–888, 1994.

- [16] T. Yoshida, Y. Ohtomo, and M. Shimaya, "A novel p-i-n photodetector fabricated on SIMOX for 1 GHz 2 V CMOS OEICs," in *IEDM. Tech. Dig.*, San Francisco, CA, 1998, pp. 29–32.

- [17] S. M. Csutak, J. D. Schaub, W. E. Wu, R. Shimer, and J. C. Campbell, "CMOS-compatible high-speed planar silicon photodiodes fabricated on SOI substrates," *IEEE J. Quantum Electron.*, vol. 38, no. 2, pp. 193–196, Feb. 2002.

- [18] E. Chen and S. Y. Chou, "High-efficiency and high-speed silicon metalsemiconductor-metal photodetectors operating in the infrared," *Appl. Phys. Lett.*, vol. 70, pp. 753–755, 1997.

- [19] M. Yang, J. Schaub, J. D. Rogers, M. Ritter, K. Rim, J. Welser, and B. Park, "High speed silicon lateral trench detector on SOI substrate," in *IEDM Tech. Dia*. Washington, DC 2001, pp. 547–550.

- Tech. Dig., Washington, DC, 2001, pp. 547–550.

[20] J. D. Schaub, S. J. Koester, G. Dehlinger, Q. C. Ouyang, D. Guckenberger, M. Yang, D. Rogers, J. Chu, and A. Grill, "High speed, lateral PIN photodiodes in silicon technologies," presented at Photonics West 2004, San Jose. CA.

- [21] M. Ghioni, F. Zappa, V. P. Kesan, and J. Warnock, "A VLSI-compatible high-speed silicon photodetector for optical data links," *IEEE Trans. Electron Devices*, vol. 43, no. 7, pp. 1054–1060, Jul. 1996.

- [22] C. L. Schow, R. Li, J. D. Schaub, and J. C. Campbell, "Design and implementation of high-speed planar Si photodiodes fabricated on SOI substrates," *IEEE J. Quantum Electron.*, vol. 35, no. 10, pp. 1478–1482, Oct. 1999.

- [23] G. G. Shahidi, "SOI technology for the GHz era," *IBM J. Res. Dev.*, vol. 46, pp. 121–131, 2002.

- [24] M. S. Ünlü and S. Strite, "Resonant cavity enhanced (RCE) photonic devices," J. Appl. Phys., vol. 78, pp. 607–639, 1995.

- [25] J. C. Bean, J. Qi, C. L. Schow, R. Li, H. Nie, J. Schaub, and J. C. Campbell, "High-speed polysilicon resonant-cavity photodiode with SiO<sub>2</sub>-Si Bragg reflectors," *IEEE Photon. Technol. Lett.*, vol. 9, no. 6, pp. 806–808, Jun. 1997.

- [26] M. K. Emsley, O. Dosunmu, and M. S. Ünlü, "Silicon substrates with buried distributed Bragg reflectors for resonant cavity-enhanced optoelectronics," *IEEE J. Sel. Topics Quantum Electron.*, vol. 8, no. 4, pp. 948–955, Jul.–Aug. 2002.

- [27] J. D. Schaub, R. Li, C. L. Schow, J. C. Campbell, G. W. Neudeck, and J. Denton, "Resonant-cavity-enhanced high-speed Si photodiode grown by epitaxial lateral overgrowth," *IEEE Photon. Technol. Lett.*, vol. 11, no. 12, pp. 1647–1649, Dec. 1999.

- [28] H. C. Lee and B. Van Zeghbroeck, "A novel high-speed silicon MSM photodetector operating at 830 nm wavelength," *IEEE Electron Device Lett.*, vol. 16, no. 5, pp. 175–177, May 1995.

- [29] S. Luryi, T. P. Pearsall, H. Temkin, and J. C. Bean, "Waveguide infrared photodetectors on a silicon chip," *IEEE Electron Device Lett.*, vol. EDL-7, no. 2, pp. 104–107, Feb. 1986.

- [30] T. P. Pearsall, H. Temkin, J. C. Bean, and S. Luryi, "Avalanche gain in  $Ge_xSi_{1-x}$  infrared waveguide detectors," *IEEE Electron Device Lett.*, vol. EDL-7, no. 5, pp. 330–332, May 1986.

- [31] H. Temkin, T. P. Pearsall, J. C. Bean, R. A. Logan, and S. Luryi, " $Ge_xSi_{1-x}$  strained-layer superlattice waveguide photodetectors operating near 1.3  $\mu$ m," *Appl. Phys. Lett.*, vol. 48, pp. 963–965, 1986.

- [32] A. Splett, T. Zinke, K. Petermann, E. Kasper, H. Kibbel, H.-J. Herzog, and H. Presting, "Integration of waveguides and photodetectors in SiGe for 1.3 μm operation," *IEEE Photon. Technol. Lett.*, vol. 6, no. 1, pp. 59–61, Jan. 1994.

- [33] F. Y. Huang, X. Zhu, M. O. Tanner, and K. L. Wang, "Normal-incidence strained-layer superlattice Ge<sub>0.5</sub>Si<sub>0.5</sub>/Si photodiodes near 1.3 μm," Appl. Phys. Lett., vol. 67, pp. 566–568, 1995.

- [34] L. Naval, B. Jalali, L. Gomelsky, and J. M. Liu, "Optimization of  $Si_{1-x}Ge_x/Si$  waveguide photodetectors operating at  $\lambda=1.3~\mu m$ ," *J. Lightw. Technol.*, vol. 14, no. 5, pp. 787–797, May 1996.

- [35] T. Tsutomu, T. Tatsumi, M. Sugiyama, T. Hashimoto, and T. Morikawa, "A selective epitaxial SiGe/Si planar photodetector for Si-based OEIC's,," *IEEE Trans. Electron. Devices*, vol. 44, no. 4, pp. 545–550, Apr. 1997.

- [36] S. Luryi, A. Kastalsky, and J. C. Bean, "New infrared detector on a silicon chip," *IEEE Trans. Electron. Devices*, vol. ED-31, no. 9, pp. 1135–1139, Sep. 1984.

- [37] E. A. Fitzgerald, Y. H. Xie, M. L. Green, D. Brasen, A. R. Kortan, J. Michel, Y. J. Mii, and B. E. Weir, "Totally relaxed  $Ge_xSi_{1-x}$  layers with low threading dislocation densities grown on Si substrates," *Appl. Phys. Lett.*, vol. 59, pp. 811–813, 1991.

- [38] S. B. Samavedam, M. T. Currie, T. A. Langdo, and E. A. Fitzgerald, "High-quality germanium photodiodes integrated on silicon substrates using optimized relaxed buffers," *Appl. Phys. Lett.*, vol. 73, pp. 2125–2127, 1998.

- [39] J. Oh, J. C. Campbell, S. G. Thomas, S. Bharatan, R. Thoma, C. Jasper, R. E. Jones, and T. E. Zirkle, "Interdigitated Ge p-i-n photodetectors fabricated on a Si substrate using graded SiGe buffer layers," *IEEE J. Quantum Electron.*, vol. 38, no. 9, pp. 1238–1241, Sep. 2002.

- [40] H.-C. Luan, D. R. Lim, K. K. Lee, K. M. Chen, J. G. Sandland, K. Wada, and L. C. Kimerling, "High-quality Ge epilayers on Si with low threading-dislocation densities," *Appl. Phys. Lett.*, vol. 75, pp. 2909–2911, 1999

- [41] L. Colace, G. Masini, F. Galluzzi, G. Assanto, G. Capellini, L. Di Gaspare, E. Palange, and F. Evangelisti, "Metal-semiconductor-metal near-infrared light detector based on epitaxial Ge/Si," *Appl. Phys. Lett.*, vol. 72, pp. 3175–3177, 1998.

- [42] G. Masini, L. Colace, G. Assanto, H.-C. Luan, K. Wada, and L. C. Kimerling, "High responsivity near infrared Ge photodetectors integrated on Si," *Electron. Lett.*, vol. 35, pp. 1467–1468, 1999.

- [43] J. Oh, S. K. Banerjee, and J. C. Campbell, "Metal-germanium-metal photodetectors on heteroepitaxial Ge-on-Si with amorphous Ge Schottky barrier enhancement layers," *IEEE Photon. Technol. Lett.*, vol. 16, no. 2, pp. 581–583, Feb. 2004.

- [44] Z. Huang, J. Oh, and J. C. Campbell, "Back-side-illuminated high-speed Ge photodetector fabricated on Si substrate using thin SiGe buffer layers," *Appl. Phys. Lett.*, vol. 85, pp. 3286–3288, 2004.

- [45] G. Dehlinger, J. D. Schaub, J. O. Chu, S. J. Koester, Q. C. Ouyang, and A. Grill, "High speed lateral PIN germanium-on-silicon photodetectors," presented at the 1st Int. SiGe Technology and Device Meeting, Nagoya, Japan, 2003.

- [46] M. Jutzi, M. Berroth, G. Wöhl, M. Oehme, and E. Kasper, "Ge-on-Si vertical incidence photodiodes with 39-GHz bandwidth," *IEEE Photon. Technol. Lett.*, vol. 17, pp. 1510–1512, Jul. 2005.

- [47] G. Dehlinger, S. J. Koester, J. D. Schaub, J. O. Chu, Q. C. Ouyang, and A. Grill, "High-speed germanium-on-SOI lateral PIN photodiodes," *IEEE Photon. Technol. Lett.*, vol. 16, no. 11, pp. 2547–2549, Nov. 2004.

- [48] S. J. Koester, J. D. Schaub, G. Dehlinger, J. O. Chu, Q. C. Ouyang, and A. Grill, "High-efficiency, Ge-on-SOI lateral PIN photodiodes with 29 GHz bandwidth," presented at the 62nd Annu. Device Res. Conf., Notre Dame, IN, 2004.

- [49] D. Guckenberger, J. D. Schaub, and K. Kornegay, "1 V, 10 mW, 10 Gb/s CMOS optical receiver front-end," presented at the IEEE Radio Frequency Integr. Circuits Symp., Long Beach, CA, 2005.

- [50] C. L. Schow, L. Schares, S. J. Koester, G. Dehlinger, R. John, and F. E. Doany, "A 15-Gb/s, 2.4 V optical receiver using a Ge-on-SOI photodiode and a CMOS IC," in *IEEE Photon. Technol. Lett.*, vol. 18, pp. 1981–1983, Oct. 2006.

- [51] C. L. Schow, L. Schares, S. J. Koester, G. Dehlinger, and R. John, "A 19-Gb/s, 1.8 V optical receiver front-end comprised of a Ge-on-SOI photodiode and a CMOS transimpedance amplifier," in *Proc. 32nd Eur. Conf. Opt. Commun., ECOC*, Cannes, France, Sep. 24–28, 2006.

- [52] G. Taraschi, A. J. Pitera, and E. A. Fitzgerald, "Strained Si, SiGe, and Ge on-insulator: Review of wafer bonding fabrication techniques," *Solid State Electron.*, vol. 48, pp. 1297–1305, 2004.

- [53] N. A. Bojarczuk, M. Copel, S. Guha, V. Narayanan, E. J. Preisler, F. M. Ross, and H. Shang, "Epitaxial silicon and germanium on buried insulator heterostructures and devices," *Appl. Phys. Lett.*, vol. 83, pp. 5443– 5445, 2003.

- [54] J. Liu et al., "High-performance, tensile-strained Ge p-i-n photodetectors on a Si platform," Appl. Phys. Lett., vol. 87, pp. 103501–103503, 2005.

- [55] O. I. Dosunmu, D. D. Cannon, M. K. Emsley, L. C. Kimerling, and M. S. Ünlü, "High-speed resonant cavity enhanced Ge photodetectors on reflecting Si substrates for 1550-nm operation," *IEEE Photon. Technol. Lett.*, vol. 17, no. 1, pp. 175–177, Jan. 2005.

- [56] O. I. Dosunmu, D. D. Cannon, M. K. Emsley, B. Ghyselen, J. Liu, L. C. Kimerling, and M. S. Ünlü, "Resonant cavity enhanced Ge photodetectors for 1550 nm operation on reflecting Si substrates," *IEEE J. Sel. Topics Quantum Electron.*, vol. 10, no. 4, pp. 694–701, Jul.–Aug. 2004.

- [57] C. Gunn, "CMOS photonics," presented at the Int. Conf. Group-IV Photonics, Antwerp, Belgium, 2005.

**Steven J. Koester** (M'96–SM'02) was born in Defiance, OH, in 1966. He received the B.S.E.E. and M.S.E.E. degrees from the University of Notre Dame, Notre Dame, IN, in 1989 and 1991, respectively.

He was a Research Fellow at the University of California, Santa Barbara, where he was engaged in research on the fabrication of quantum devices in the InAs/AISb heterostructure system. Since 1995, he has been with the IBM T. J. Watson Research Center, Yorktown Heights, NY, and has performed research on group-IV heterostructure materials and

devices, with emphasis on strained-layer field-effect transistors and photodetectors. He was also a Postdoctoral Researcher working on the fabrication and characterization of nanostructured devices in Si/SiGe strained-layer materials. He possesses over 15 years of experience in the field of semiconductor device research. He is the author or coauthor of over 80 technical publications and conference presentations. He is the holder of nine U.S. patents.

**Jeremy D. Schaub** (S'93–M'95) received the B.S. degree in engineering science from Trinity University, San Antonio, TX, in 1995, and the M.S. and Ph.D. degrees in electrical and computer engineering from the University of Texas at Austin, in 1998 and 2000, respectively.

He is currently a Research Staff Member with the IBM Austin Research Lab, Austin, TX, where he is engaged in research on computer interconnects and high-speed measurement of on-chip signals.

**Gabriel Dehlinger** received the Graduate degree (*magna cum laude*) from the University of Tübingen, Tübingen, Germany, and the Ph.D. degree from the Swiss Federal Institute of Technology Zürich, Zürich, Switzerland, in 1997 and 2001, respectively.

In 2001, he joined IBM Research, where he was engaged in research on direct growth of Ge-on-Si using ultrahigh vacuum chemical vapor deposition, and on the processing and measurement of Ge high-speed photodetectors. Since 2003, he has been with Infineon, Villach, Austria, where he is currently a