Received 24 January 2021; accepted 8 February 2021. Date of publication 11 February 2021; date of current version 26 February 2021. The review of this article was arranged by Editor N. Collaert.

Digital Object Identifier 10.1109/JEDS.2021.3058631

# **Graded Crystalline HfO<sub>2</sub> Gate Dielectric** Layer for High-k/Ge MOS Gate Stack

CHAN HO LEE<sup>® 1</sup>, JEONG YONG YANG<sup>® 1</sup>, JUNSEOK HEO<sup>® 2</sup> (Member, IEEE), AND GEONWOOK YOO<sup>® 1</sup>

1 School of Electronic Engineering, Soongsil University, Seoul 06938, South Korea 2 Department of Electrical and Computer Engineering, Ajou University, Suwon 16499, South Korea

CORRESPONDING AUTHOR: J.HEO and G. YOO (e-mail: jsheo@ajou.ac.kr; gwyoo@ssu.ac.kr)

This work was supported in part by the Industrial Strategic Technology Development Program under Grant 20000300; and in part by the National Research and Development Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT under Grant 2020M3F3A2A01082593

**ABSTRACT** Germanium (Ge) has gained great attention not only for future nanoelectronics but for back-end of line (BEOL) compatible monolithic three-dimensional (M3D) integration recently. For high performance and low power devices, various high-k oxide/Ge gate stacks including ferroelectric oxides have been investigated. Here, we demonstrate atomic layer deposited (ALD) polycrystalline (p-) HfO<sub>2</sub>/GeO<sub>X</sub>/Ge stack with an amorphous (a-) HfO<sub>2</sub> capping layer. The consecutively deposited a-HfO<sub>2</sub> capping layer improves hysteretic behaviors ( $\Delta V$ ) and interface state density (D<sub>it</sub>) of the p-HfO<sub>2</sub>/GeO<sub>X</sub>/Ge stack. Furthermore, leakage current density (J) is significantly reduced (×100) by passivating leakage paths through grain boundaries of p-HfO<sub>2</sub>. The proposed HfO<sub>2</sub> layer with the graded crystallinity suggests possible high-k/Ge stacks for further optimized Ge MOS structures.

**INDEX TERMS** Ge, amorphous, polycrystalline, ALD HfO<sub>2</sub>, leakage.

# I. INTRODUCTION

Germanium (Ge) has been one of the promising candidates for modern very large-scale integrated circuits and future nanoelectronics because of its high carrier mobility, stable performance and relatively silicon-compatible low-temperature process [1]-[5]. Most recently, back-end of line (BEOL) compatible monolithic three-dimensional (M3D) integration of high performance memory and logic has attracted much attention [6], [7]. Under the constraint of thermal budget (< 400 °C), polycrystalline (p-) Ge is one of the strong candidates along with p-Si, metal-oxides, and two-dimensional semiconductors [7]-[11]. Although the scaling of Ge devices to the physical limit and thus thin equivalent oxide thickness (EOT) of gate-oxide are not aggressively demanded for BEOL-M3D integration, the thermal budget and other process conditions should be considered.

The stable and high quality gate stack formation on Ge has been the critical challenge to realize the aforementioned prediction [1], [3]. In particular, high-permittivity (k) oxides is mandatory for low power consumption [12]. For the high-k/Ge gate stack, HfO<sub>2</sub>, one of the most promising

high-k materials in Si, is also very attractive because of its k value and/or ferroelectricity by doping or elaborated thermal annealing [13], [14], [15]. However, Ge atoms can easily diffuse into the HfO<sub>2</sub> during the atomic layer deposition (ALD) process and even low-temperature annealing process, resulting in large leakage current [16]. Moreover, the diffused Ge atoms significantly affect electrical characteristics such as poor hysteresis and mobility degeneration [1], [17], [18]. Other than single crystal oxides, poor interface properties and large leakage current are inevitable without an interfacial passivating layer.

Regarding the interfacial layer, extensive research has been conducted to passivate the Ge surface and various methods of high-quality GeO<sub>2</sub> [18]–[21], oxynitrides [22], [23], and 2-D materials such as molybdenum disulfied (MoS<sub>2</sub>) [24] have been investigated. Unlike the HfO<sub>2</sub> and ZrO<sub>2</sub>, the Y<sub>2</sub>O<sub>3</sub> layer is known to achieve high interface quality by suppressing the GeO<sub>2</sub> desorption [25]. However, the post-oxidation to introduce high-quality GeO<sub>2</sub> typically requires high-temperature thermal annealing process [26], [27], which is not compatible with the BEOL M3D integration. The Hf-based ferroelectric oxides with negative capacitance, which is very promising for

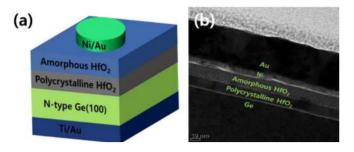

**FIGURE 1.** (a) A schematic diagram of the fabricated Ge MOSCAP with p-HfO<sub>2</sub> (10 nm)/a-HfO<sub>2</sub> (10 nm) gate dielectric layer, and (b) its cross-sectional TEM image.

low-power steep switching transistors, also require thermal annealing process. So alternative schemes of high-k oxide stack needs be considered.

In this work, we proposed a-HfO<sub>2</sub> capping layer on top of the p-HfO<sub>2</sub>/GeO<sub>X</sub>/Ge gate stack. An oxide stack of HfO<sub>2</sub> with different oxide layers is known to have high density of dipoles inducing hysteresis and interface states [28], [29]; This HfO<sub>2</sub> stack allows minimized formation of dipoles inbetween. The crystallinity of the ALD p-HfO<sub>2</sub>/a-HfO<sub>2</sub> stack was confirmed by high resolutiontransmission electron microscopy (HR-TEM). Bidirectional frequency-dependent capacitance- voltage (C-V) measurements were conducted to compare hysteretic behaviors ( $\Delta V$ ) of both p-HfO<sub>2</sub>/a-HfO<sub>2</sub> and p-HfO<sub>2</sub> gate stacks as a control sample. Moreover, interface trap densities  $(D_{it})$  were characterized and compared using Hi-Lo and conductance methods. Finally, leakage current density (J) vs. oxide electric field  $(E_{OX})$  was characterized, and the effects of a-HfO<sub>2</sub> capping layer was discussed.

# **II. EXPERIMENTS**

Ge MOSCAPs were fabricated on n-type As-doped (100) Ge wafer with a nominal resistivity of 0.04  $\sim$  0.05  $\Omega$ cm. First, the surface was chemically cleaned, and then p-HfO<sub>2</sub> dielectric layer (10 nm) was deposited using ALD at an elevated stage temperature of 350 °C, followed by a-HfO<sub>2</sub> (~10 nm) deposition at 200 °C. Tetrakis(ethylmethy lamino)hafnium (TEMAH) and ozone were used as Hf precursor and oxygen source, respectively. The deposition rate was  $\sim 0.9$  Å/cycle. To avoid crystallization of the a-HfO<sub>2</sub>, we first deposit p-HfO<sub>2</sub> using ALD at 350 °C followed by a-HfO<sub>2</sub> deposition at 200 °C, consecutively. Top contact electrodes of Ni/Au (10/50nm) were deposited by thermal evaporation and patterned using conventional photolithography and lift off process. Next, as a bottom contact, Ti/Au (20/80nm) was deposited by e-beam evaporation. No post-deposition annealing was conducted. For the comparison, Ge MOSCAPs with only p-HfO<sub>2</sub> dielectric layer (15 nm) was also prepared. Figs. 1 (a) and (b) show a schematic of the fabricated MOSCAP with p-HfO<sub>2</sub>/a-HfO<sub>2</sub> bilayer dielectrics and its cross-sectional TEM image at a low magnification, confirming the Ge gate stacks. C-V and current density-voltage (J-V) measurements were conducted using a HP 4284A LCR meter and 4200A SCS

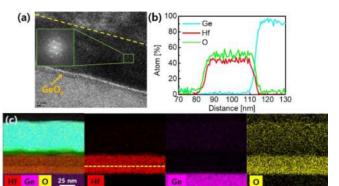

FIGURE 2. (a) A cross sectional HR-TEM image of the

p-HfO<sub>2</sub>/a-HfO<sub>2</sub>/GeO<sub>X</sub> stack with a FFT micrograph of the p-HfO<sub>2</sub> in the inset. (b) STEM EDS line profiles of the p-HfO<sub>2</sub>/a-HfO<sub>2</sub>/GeO<sub>X</sub>/Ge showing the change of atomic ratios at the interfaces. (c) Compositional element mapping of the several layer (Ge, Hf and O), and a higher density of Hf atom from the p-HfO<sub>2</sub> is observed.

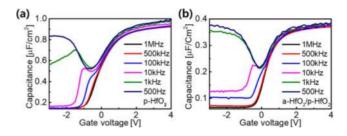

FIGURE 3. Frequency dependent C-V characteristics of Ge MOSCAPs with (a) p-HfO<sub>2</sub> monolayer and (b) p-HfO<sub>2</sub>/a-HfO<sub>2</sub> bilayer gate dielectric.

semiconductor parameter analyzer, respectively. Structural analysis was conducted using focused ion-beam (FIB)-SEM and transmission electron microscopy (TEM, JEOL JEM-2100F) equipped with an energy-dispersive X-ray spectrometer (EDS).

# **III. RESULTS AND DISCUSSION**

Fig. 2(a) shows the cross-sectional high-resolution (HR)-TEM image of the p-HfO<sub>2</sub>/a-HfO<sub>2</sub>/Ge (100) interface; The crystallinity of each HfO<sub>2</sub> layer is clearly shown. The p-HfO<sub>2</sub> layer possesses a polycrystalline structure containing multiple grains and boundaries, and an interfacial GeO<sub>X</sub> layer of  $\sim 0.54$  nm is formed on the Ge surface. The inset shows a fast Fourier transform (FFT) micrograph of the HfO<sub>2</sub> grain, clearly indicating its crystallized phase. Fig. 2(b) shows changes of atomic ratio across the interface, and Fig. 2(c) represents the EDS mapping of individual layers, confirming the uniform distribution of elements Ge, Hf, and O. A higher density of Hf atom was observed in p-HfO<sub>2</sub> compared with a-HfO<sub>2</sub> layer.

Figs. 3(a) and (b) show the frequency-dependent C-V curves of the p-HfO<sub>2</sub>/a-HfO<sub>2</sub> and p-HfO<sub>2</sub> Ge MOSCAPs from 500 Hz to 1 MHz, respectively. Stronger inversion and less frequency-dispersion were observed in the p-HfO<sub>2</sub>/a-HfO<sub>2</sub> MOSCAPs due to improved leakage characteristics achieved by a-HfO<sub>2</sub> capping layer [30]. However, a relatively

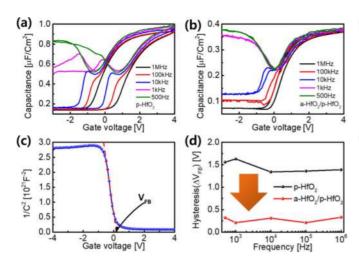

**FIGURE 4.** Bidirectional C-V characteristics of Ge MOSCAPs with (a) p-HfO<sub>2</sub> monolayer and (b) p-HfO<sub>2</sub>/a-HfO<sub>2</sub> bilayer gate dielectric. (c)  $1/C^2$  vs. gate voltage plot for extracting V<sub>FB</sub> through linear fitting. (d) Comparison of extracted hysteresis ( $\Delta$ V<sub>FB</sub>) versus frequency.

low k value of ~ 9 was obtained from p-HfO<sub>2</sub>/a-HfO<sub>2</sub> in comparison with  $k \sim 15$  of p-HfO<sub>2</sub> gate dielectric. Further experiments to optimize the thickness ratio between p-HfO<sub>2</sub> and a-HfO<sub>2</sub> layer and ALD process conditions could enhance the k of p-HfO<sub>2</sub>/a-HfO<sub>2</sub> [31].

Figs. 4(a) and (b) show the frequency-dependent bidirectional C-V curves of the Ge MOSCAPS with p-HfO<sub>2</sub>/a-HfO<sub>2</sub> and p-HfO<sub>2</sub> for the same frequency range of 500 Hz to 1 MHz, respectively. Although the a-HfO<sub>2</sub> layer contains various oxide defects inducing non-ideal C-V properties, p-HfO<sub>2</sub> capped by a-HfO<sub>2</sub> layer (i.e., p-HfO<sub>2</sub>/a-HfO<sub>2</sub>) exhibits significant reduction of hysteresis ( $\Delta V_{\text{FB}}$ ) as well as dispersion. In order to describe the effect of a-HfO<sub>2</sub> capping layer on  $\Delta V_{\rm FB}$  quantitatively, the  $V_{\rm FB}$  is determined through the extrapolated line of  $1/C^2 - V_{GS}$  in the depletion region as shown in Fig. 4(c) exhibiting  $V_{\text{FB}}$  of 0.32 V.  $\Delta V_{\text{FB}}$  is calculated to be difference of  $V_{\rm FB}$  under bi-directional bias sweep C-V measurements, and Fig. 4(d) compares the hysteresis  $(\Delta V_{\rm FB})$  as a function of frequency. The average  $\Delta V_{\rm FB}$  of p-HfO<sub>2</sub>/a-HfO<sub>2</sub> and p-HfO<sub>2</sub> was 0.28 V and 1.46 V, respectively. Therefore, the additional a-HfO2 layer deposited on p-HfO<sub>2</sub> results in the reduction of  $V_{\rm FB}$  by  $\sim 1.18$  V, and exhibits lower  $\Delta V_{\rm FB}$  in comparison with the reported value of a Ge gate stack with a-HfO<sub>2</sub> layer [32].

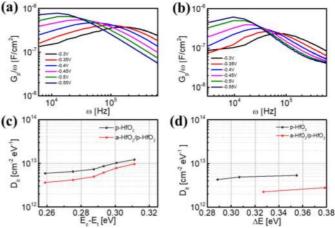

Next, Hi-Lo and conductance methods were used to investigate  $D_{it}$  at the interface. The ac conductance  $(G_m)$  and capacitance  $(C_m)$  of the MOSCAPs were measured at various gate biases. Based on the measured  $G_m$ , the normalized equivalent parallel conductance is calculated using [28], [29]:

$$\frac{Gp}{\omega} = \frac{C^2 \omega G_m}{G_m^2 + \omega^2 (C_{ox} - C_m)^2},\tag{1}$$

where  $C_{\text{OX}}$  is the oxide capacitance measured in accumulation region and  $\omega$  is the angular frequency. Figs. 5(a) and (b) show the extracted equivalent conductance ( $G_p$ ) versus measurement frequency ( $\omega$ ) for both MOSCAPs. The

FIGURE 5. Normalized equivalent conductance spectrum at various gate bias derived from conductance measurements for (a) p-HfO<sub>2</sub> and (b) p-HfO<sub>2</sub>/a-HfO<sub>2</sub>. Interface trap density (D<sub>it</sub>) versus  $\Delta E$  calculated from (c) conductance method and (d) Hi-Lo method.

peaks correspond to interface states' response, and their positions were modulated by the gate bias. From the conductance peak,  $D_{it}$  was extracted using [33], [34],

$$D_{it} = \frac{2.5}{Aq} \left(\frac{Gp}{\omega}\right)_{peak},\tag{2}$$

where A is the area of devices. Fig. 5(c) shows the calculated  $D_{it}$  as a function of  $\Delta E$  which is the energy difference between trap level (E<sub>T</sub>) and conduction band edge (E<sub>C</sub>). The  $D_{it}$  of p-HfO<sub>2</sub> and p-HfO<sub>2</sub>/a-HfO<sub>2</sub> were extracted to be  $6.0 \times 10^{12}$  and  $3.5 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>, respectively, at  $\Delta E$ = 0.26 eV;  $D_{it}$  from p-HfO<sub>2</sub>/a-HfO<sub>2</sub> was lower than that of p-HfO<sub>2</sub>. Because the conductance method could overestimate  $D_{it}$  due to the minority carrier responses in the weak inversion and provide  $D_{it}$  values only over the limited energy range [35], [36], we further investigated the  $D_{it}$  using the Hi-Lo method and  $D_{it}$  was calculated from Figs. 3(a) and (b) using

$$D_{it}(V_g) = \left(\frac{C_{OX}C_{LF}}{C_{OX} - C_{LF}} - \frac{C_{OX}C_{HF}}{C_{OX} - C_{HF}}\right)/qA,\qquad(3)$$

where A is the area,  $C_{\text{LF}}$  and  $C_{\text{HF}}$  is the capacitance at low and high frequency, respectively [33], [37]. The p-HfO<sub>2</sub>/a-HfO<sub>2</sub> also exhibits reduced  $D_{\text{it}}$  of 2.0 × 10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> compared with p-HfO<sub>2</sub> of  $4.0 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. The reduced hysteretic behaviors and improved interface states of Ge MOSCAPs with the p-HfO<sub>2</sub>/a-HfO<sub>2</sub> dielectric can be attributed not only to capping effects of the p-HfO<sub>2</sub> surface by the a-HfO<sub>2</sub> layer but the post-oxidation at the interface between p-HfO<sub>2</sub> and Ge during ALD deposition process [12], [38]. Although the ALD temperature (~ 200 °C) of a-HfO<sub>2</sub> was relatively low, thermal diffusion of oxygen can proceed and the oxidation at the interface is speculated to be involved [16].

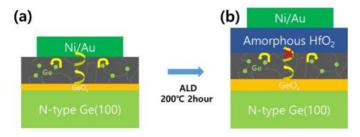

Fig. 6 shows a schematic illustration of the a-HfO<sub>2</sub> capping effect on p-HfO<sub>2</sub>/GeO<sub>x</sub>/Ge stack. Although the p-HfO<sub>2</sub>

**FIGURE 6.** Schematic illustration of the reactions occurring within the Ge MOSCAPs with (a) p-HfO<sub>2</sub> and (b) p-HfO<sub>2</sub>/a-HfO<sub>2</sub> stack. The a-HfO<sub>2</sub> capping layer and post-oxidation at the interface during ALD a-HfO<sub>2</sub> process (200 °C, 2 hours) suppress the diffusion of Ge atoms through grain boundaries and passivate leakage paths.

monolayer provides a relatively higher k of ~ 15, the incorporation of Ge atoms into p-HfO<sub>2</sub> and their diffusion within the layer are known to be the origin of poor electrical characteristics [1], [18]. Even worse, the GeO (g) is known to trigger metal-Ge (HfGe<sub>2</sub>) generation playing a role of leakage current paths as shown in the following reactions [1],

$$3\text{GeO}_2 + 3\text{Ge6GeO}$$

(g) (4)

$$HfO_2 + 6GeO (g)HfGe_2 + 4GeO_2$$

(5)

As shown in Fig. 6(a), the diffusion of Ge atoms into the p-HfO<sub>2</sub> through grain boundaries induces larger hysteresis as well as higher  $D_{it}$ . In order to confine the Ge diffusion within the p-HfO<sub>2</sub>, the a-HfO<sub>2</sub> capping layer is deposited as shown in Fig. 6(b). Although other amorphous high-k films can be applied as a capping layer, it is reported that the interface dipoles at the boundary of different oxide layers can cause additional hysteresis [28], [29]. Even compared with the direct diffusion of Ge atoms into the a-HfO<sub>2</sub> gate-dielectric, the proposed p-HfO<sub>2</sub>/a-HfO<sub>2</sub> dielectric shows better interface quality [32]. Therefore, the proposed p-HfO<sub>2</sub> dielectric capped by a-HfO<sub>2</sub> can exhibit improvement of interface quality and reduction of leakage current. Moreover, the consecutive ALD deposition of polycrystalline and amorphous HfO2 at different temperature can simplify the gate-oxide deposition process. It is to be noted that the results can be limited because the reference p-HfO<sub>2</sub> dielectric did not adopt high-quality GeO<sub>2</sub> or passivation layer using additional processes. At the same time, it can be further improved by adopting thin Al<sub>2</sub>O<sub>3</sub> interlayer and/or additional pre-/post-oxidation of GeO<sub>x</sub> [21], [26], [27]. In particular, considering the thermal budget for BEOL-M3D integration, the plasma postoxidation method might be preferred [21], [39].

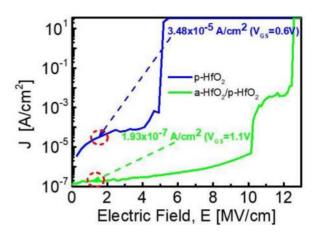

Furthermore, the proposed graded HfO<sub>2</sub> gate dielectric layer can yield significantly improved leakage current and breakdown characteristics. Fig. 7 shows the gate leakage current density (*J*) vs. oxide electric field ( $E_{OX}$ ) of the measured devices; An equivalent oxide thickness (EOT) was used for calculating  $E_{OX}$ . At the same effective V<sub>G</sub> bias condition of V<sub>FB</sub> + 1 V, the *J* of p-HfO<sub>2</sub> and p-HfO<sub>2</sub>/a-HfO<sub>2</sub> was  $3.47 \times 10^{-5}$  A/cm<sup>2</sup> and  $1.93 \times 10^{-7}$  A/cm<sup>2</sup>, respectively. This suppressed leakage current can be attained by

FIGURE 7. Current density (J) versus oxide electric field ( $E_{0X}$ ) curves of the Ge MOSCAPs showing p-HfO<sub>2</sub>/a-HfO<sub>2</sub> stack exhibits reduced leakage current and improved breakdown characteristics compared with p-HfO<sub>2</sub>.

eliminating leakage paths. Regarding the breakdown  $E_{OX}$ , p-HfO<sub>2</sub>/a-HfO<sub>2</sub> exhibits 4.9 × 10<sup>-6</sup> A/cm<sup>2</sup> at 4.4 MV/cm, and p-HfO<sub>2</sub> shows 1.0 × 10<sup>-4</sup> A/cm<sup>2</sup> at 1.0 MV/cm. The p-HfO<sub>2</sub>/a-HfO<sub>2</sub> exhibits significantly lower J (< 100 ×) and better breakdown characteristics (> 4 ×) compared with p-HfO<sub>2</sub>, attributed to the aforementioned capping effect of the a-HfO<sub>2</sub>.

#### **IV. CONCLUSION**

In summary, we proposed and investigated p-HfO<sub>2</sub>/a-HfO<sub>2</sub> gate dielectric for n-Ge MOSCAPs in comparison with p-HfO<sub>2</sub> dielectric. The crystallinity of each HfO<sub>2</sub> layer and interfacial GeO<sub>X</sub> layer were confirmed by HR-TEM. Although the p-HfO<sub>2</sub>/a-HfO<sub>2</sub> has a lower dielectric constant  $(k \sim 9)$  than that  $(k \sim 15)$  of p-HfO<sub>2</sub>, it showed a reduced hysteresis ( $\Delta V_{\rm FB}$ ) by the amount of  $\sim 1.3$  V. The k is expected to be increased by optimizing the thickness ratio. Both Hi-Lo and conductance methods were used to evaluate the interface state.  $D_{it}$  of p-HfO<sub>2</sub>/a-HfO<sub>2</sub> and p-HfO<sub>2</sub> were extracted to be  $6.0 \times 10^{12}$  and  $3.5 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>, respectively, at  $\Delta E = 0.26$  eV. Similar level of difference (~  $2.0 \times 10^{12} \text{ cm}^{-2} \text{eV}^{-1}$ ) was obtained from the Hi-Lo method. These reduced hysteresis and improved interface quality can be attributed to the effect of surface capping by the a-HfO<sub>2</sub> layer and additional post-oxidation at the interface between p-HfO<sub>2</sub> and GeO<sub>X</sub>/Ge substrate during ALD a-HfO<sub>2</sub> deposition. Moreover, the diffused Ge atoms through the grain boundaries were speculated to be confined within p-HfO<sub>2</sub> layer by a-HfO<sub>2</sub> capping layer. Consequently, a-HfO<sub>2</sub> could suppress leakage current paths, and thus significantly reduced leakage J of  $1.93 \times 10^{-7}$  A/cm<sup>2</sup> was obtained from the p- $HfO_2/a-HfO_2$  compared with 3.47  $\times$  10<sup>-5</sup> A/cm<sup>2</sup> from the p-HfO<sub>2</sub> at the bias of  $V_{FB}$  + 1 V. These results show that the p-HfO<sub>2</sub> with consecutively deposited a-HfO<sub>2</sub> capping layer can be a promising gate stack for Ge devices.

#### ACKNOWLEDGMENT

The EDA tool was supported by the IC Design Education Center (IDEC), South Korea.

#### REFERENCES

- Y. Kamata, "High-k/Ge MOSFETs for future nanoelectronics," *Mater. Today*, vol. 11, nos. 1–2, pp. 30–38, 2008, doi: 10.1016/S1369-7021(07)70350-4.

- [2] A. Toriumi *et al.*, "Material potential and scalability challenges of germanium CMOS," in *Tech. Dig. Int. Electron Devices Meeting*, 2011, pp. 646–649, doi: 10.1109/IEDM.2011.6131631.

- [3] P. S. Goley and M. K. Hudait, "Germanium based field-effect transistors: Challenges and opportunities," *Materials*, vol. 7, no. 3, pp. 2301–2339, 2014, doi: 10.3390/ma7032301.

- [4] C. Claeys et al., "Status and trends in Ge CMOS technology," ECS Trans., vol. 54, no. 1, pp. 25–37, 2013.

- [5] S. Gupta, X. Gong, R. Zhang, Y. C. Yeo, S. Takagi, and K. C. Saraswat, "New materials for post-Si computing: Ge and GeSn devices," MRS Bull., vol. 39, no. 8, pp. 678–686, 2014, doi: 10.1557/mrs.2014.163.

- [6] P. Batude *et al.*, "Advances, challenges and opportunities in 3D CMOS sequential integration," in *Tech. Dig. Int. Electron Devices Meeting*, May 2014, pp. 3–7, doi: 10.1109/IEDM.2011.6131506.

- [7] S. Datta, S. Dutta, B. Grisafe, J. Smith, S. Srinivasa, and H. Ye, "Back-end-of-line compatible transistors for monolithic 3-D integration," *IEEE Micro*, vol. 39, no. 6, pp. 8–15, Nov./Dec. 2019, doi: 10.1109/MM.2019.2942978.

- [8] M. M. Shulaker *et al.*, "Three-dimensional integration of nanotechnologies for computing and data storage on a single chip," *Nature*, vol. 547, no. 7661, pp. 74–78, 2017, doi: 10.1038/nature22994.

- [9] G. Hautier, A. Miglio, G. Ceder, G. M. Rignanese, and X. Gonze, "Identification and design principles of low hole effective mass ptype transparent conducting oxides," *Nat. Commun.*, vol. 4, pp. 1–7, Aug. 2013, doi: 10.1038/ncomms3292.

- [10] M. Jiang and D. Ahn, "Seed-induced crystallization of polycrystalline germanium thin films at low temperature," *Results Phys.*, vol. 14, Sep. 2019, Art. no. 102502, doi: 10.1016/j.rinp.2019.102502.

- [11] Y.-S. Li *et al.*, "Effects of crystallinity on the electrical characteristics of counter-doped polycrystalline germanium thinfilm transistor via continuous-wave laser crystallization," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 544–550, Nov. 2019, doi: 10.1109/JEDS.2019.2914831.

- [12] C. Hu et al., "A low-leakage epitaxial high-κ gate oxide for germanium metal-oxide-semiconductor devices," ACS Appl. Mater. Interfaces, vol. 8, no. 8, pp. 5416–5423, 2016, doi: 10.1021/acsami.5b10661.

- [13] J. A. Kittl *et al.*, "High-k dielectrics for future generation memory devices (invited paper)," *Microelectron. Eng.*, vol. 86, nos. 7–9, pp. 1789–1795, 2009, doi: 10.1016/j.mee.2009.03.045.

- [14] M. H. Park, Y. H. Lee, T. Mikolajick, U. Schroeder, and C. S. Hwang, "Review and perspective on ferroelectric HfO<sub>2</sub>-based thin films for memory applications," *MRS Commun.*, vol. 8, no. 3, pp. 795–808, 2018, doi: 10.1557/mrc.2018.175.

- [15] P. Polakowski and J. Müller, "Ferroelectricity in undoped hafnium oxide," *Appl. Phys. Lett.*, vol. 106, no. 23, 2015, Art. no. 232905, doi: 10.1063/1.4922272.

- [16] S. Ogawa *et al.*, "Insights into thermal diffusion of germanium and oxygen atoms in HfO<sub>2</sub>/GeO<sub>2</sub>/Ge gate stacks and their suppressed reaction with atomically thin AlOx interlayers," *J. Appl. Phys.*, vol. 118, no. 23, pp. 1–6, 2015, doi: 10.1063/1.4937573.

- [17] Y. Kamata, Y. Kamimuta, T. Ino, R. Iijima, M. Koyama, and A. Nishiyama, "Dramatic improvement of Ge p-MOSFET characteristics realized by amorphous Zr-silicate/Ge gate stack with excellent structural stability through process temperatures," in *Tech. Dig. Int. Electron Devices Meeting*, vol. 2005, 2005, pp. 429–432, doi: 10.1109/iedm.2005.1609370.

- [18] N. Lu *et al.*, "Ge diffusion in Ge metal oxide semiconductor with chemical vapor deposition HfO<sub>2</sub> dielectric," *Appl. Phys. Lett.*, vol. 87, no. 5, pp. 1–4, 2005, doi: 10.1063/1.2001757.

- [19] C. H. Lee, T. Tabata, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, "Ge/GeO<sub>2</sub> interface control with high-pressure oxidation for improving electrical characteristics," *Appl. Phys. Exp.*, vol. 2, no. 7, pp. 3–6, 2009, doi: 10.1143/APEX.2.071404.

- [20] B. Kaczer *et al.*, "Electrical and reliability characterization of metalgate/HfO<sub>2</sub>/Ge FET's with Si passivation," *Microelectron. Eng.*, vol. 84, nos. 9–10, pp. 2067–2070, 2007, doi: 10.1016/j.mee.2007.04.100.

- [21] R. Zhang, P.-C. Huang, J.-C. Lin, N. Taoka, M. Takenaka, and S. Takagi, "High-mobility Ge p- and n-MOSFETs with 0.7-nm EOT using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeOx/Ge gate stacks fabricated by plasma postoxidation," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 927–934, Mar. 2013, doi: 10.1109/TED.2013.2238942.

- [22] E. P. Gusev *et al.*, "Microstructure and thermal stability of HfO<sub>2</sub> gate dielectric deposited on Ge(100)," *Appl. Phys. Lett.*, vol. 85, no. 12, pp. 2334–2336, 2004, doi: 10.1063/1.1794849.

- [23] C. O. Chui, H. Kim, P. C. McIntyre, and K. C. Saraswat, "Atomic layerdeposition of high-κ dielectric for germanium MOS applications— Substrate surface preparation," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 274–276, May 2004, doi: 10.1109/LED.2004.827285.

- [24] J. Li *et al.*, "High performance and reliability Ge channel CMOS with a MoS<sub>2</sub> capping layer," in *Tech. Dig. Int. Electron Devices Meeting*, 2017, pp. 33.3.1–33.3.4, doi: 10.1109/IEDM.2016.7838533.

- [25] Y. Seo *et al.*, "The impact of an ultrathin Y<sub>2</sub>O<sub>3</sub> layer on GeO<sub>2</sub> passivation in Ge MOS gate stacks," *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3303–3307, Aug. 2017, doi: 10.1109/TED.2017.2710182.

- [26] R. Zhang, J. Li, and X. Yu, "Electrical properties of Ge pMOS-FETs with ultrathin EOT HfO<sub>2</sub>/AlO<sub>x</sub>/GeO<sub>x</sub> gate-stacks and NiGe metal source/drain," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 4831–4837, Dec. 2017, doi: 10.1109/TED.2017.2761885.

- [27] M. Ke, M. Takenaka, and S. Takagi, "Impact of atomic layer deposition high k films on slow trap density in Ge MOS interfaces with GeOx interfacial layers formed by plasma pre-oxidation," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 950–955, Feb. 2018, doi: 10.1109/JEDS.2018.2822758.

- [28] E. Chen, Y.-T. Tung, Z.-R. Xiao, T.-M. Shen, J. Wu, and C. H. Diaz, "Ab initio study of dipole-induced threshold voltage shift in HfO 2/Al<sub>2</sub>O<sub>3</sub>/(100)Si," in *Proc. Int. Workshop Comput. Electron. (IWCE)*, 2014, pp. 1–3, doi: 10.1109/IWCE.2014.6865828.

- [29] F.-Y. Jin *et al.*, "Abnormal positive bias temperature instability induced by dipole doped N-type MOSCAP," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 897–901, May 2019, doi: 10.1109/jeds.2019.2932603.

- [30] J. Tao *et al.*, "Extrinsic and intrinsic frequency dispersion of highk materials in capacitance-voltage measurements," *Materials*, vol. 5, no. 6, pp. 1005–1032, 2012, doi: 10.3390/ma5061005.

- [31] D. W. McNeill *et al.*, "Atomic layer deposition of hafnium oxide dielectrics on silicon and germanium substrates," *J. Mater. Sci. Mater. Electron.*, vol. 19, no. 2, pp. 119–123, 2008, doi: 10.1007/s10854-007-9337-y.

- [32] H.-S. Jung *et al.*, "Properties of atomic layer deposited HfO<sub>2</sub> films on Ge substrates depending on process temperatures," *J. Electrochem. Soc.*, vol. 159, no. 4, pp. G33–G39, 2012, doi: 10.1149/2.014204jes.

- [33] K. Zeng, Y. Jia, and U. Singisetti, "Interface state density in atomic layer deposited SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub> (2-01) MOSCAPs," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 906–909, Jul. 2016, doi: 10.1109/LED.2016.2570521.

- [34] R. Engel-Herbert, Y. Hwang, and S. Stemmer, "Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces," *J. Appl. Phys.*, vol. 108, no. 12, 2010, Art. no. 124101, doi: 10.1063/1.3520431.

- [35] K. Martens *et al.*, "On the correct extraction of interface trap density of MOS devices with high-mobility semiconductor substrates," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 547–556, Feb. 2008, doi: 10.1109/TED.2007.912365.

- [36] C. Schulte-Braucks *et al.*, "Low temperature deposition of highk/metal gate stacks on high-Sn content (Si)GeSn-alloys," ACS Appl. Mater. Interfaces, vol. 8, no. 20, pp. 13133–13139, 2016, doi: 10.1021/acsami.6b02425.

- [37] H. Dong *et al.*, "C-V and J-V investigation of HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer dielectrics MOSCAPs on (100) β-Ga<sub>2</sub>O<sub>3</sub>," *AIP Adv.*, vol. 8, no. 6, 2018, Art. no. 065215, doi: 10.1063/1.5031183.

- [38] H. Matsubara, T. Sasada, M. Takenaka, and S. Takagi, "Evidence of low interface trap density in GeO<sub>2</sub>/Ge metal-oxide- semiconductor structures fabricated by thermal oxidation," *Appl. Phys. Lett.*, vol. 93, no. 3, 2008, Art. no. 032104, doi: 10.1063/1.2959731.

- [39] R. Asahara *et al.*, "Comprehensive study and design of scaled metal/high-k/Ge gate stacks with ultrathin aluminum oxide interlayers," *Appl. Phys. Lett.*, vol. 106, no. 23, 2015, Art. no. 233503, doi: 10.1063/1.4922447.