#### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# Graphene field-effect transistors and devices for advanced high-frequency applications

Fabrication, characterisation and analysis of limitations

#### MARLENE BONMANN

Department of Microtechnology and Nanoscience - MC2 CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden 2019.

Graphene field-effect transistors and devices for advanced high-frequency applications Fabrication, characterisation and analysis of limitations MARLENE BONMANN ISBN 978-91-7905-237-9

© MARLENE BONMANN, 2019.

Doktorsavhandlingar vid Chalmers Tekniska Högskola Ny serie nr 4704 ISSN 0346-718X Department of Microtechnology and Nanoscience - MC2 Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone: +46 (0)31-772 1000

Cover:

Top-left: Schematic cross section of a MOSFET or GFET with one gate finger. Top-right: Infrared image of a GFET. Bottom: SEM image of GFET.

Chalmers Reproservice Göteborg, Sweden 2019. Graphene field-effect transistors and devices for advanced high-frequency applications Fabrication, characterisation and analysis of limitations Thesis for the degree of Doctor of Philosophy MARLENE BONMANN Department of Microtechnology and Nanoscience - MC2 Chalmers University of Technology

#### Abstract

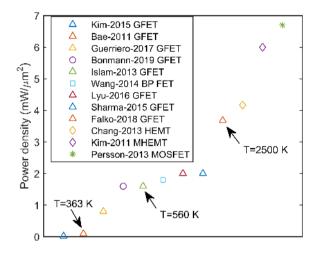

New device technologies and materials are continuously investigated, in order to increase the bandwidth of high-speed electronics, thereby extending data rate and range of applications. The 2D-material graphene, with its intrinsically extremely high charge carrier velocity, is considered as a promising new channel material for advanced high frequency field-effect transistors. However, most fabrication processes introduce impurities and defects at the interface between graphene and adjacent materials, which degrade the device performance. In addition, at high drain fields, required for high transistor gain, the close proximity of the adjacent materials limits the saturation velocity, and there is a significant increase in the channel temperature caused by self-heating.

In this thesis, the influence of impurities and defects on charge transport, the limitations of the saturation velocity, and the effect of velocity saturation and self-heating on the transit frequency  $f_{\rm T}$  and the maximum frequency of oscillation  $f_{\rm max}$  of graphene field effect transistor (GFETs) are analysed. In addition, GFETs with state-of-the-art extrinsic  $f_{\rm T} = 34$  GHz and  $f_{\rm max} = 37$  GHz, and an integrated 200-GHz GFET based receiver are presented. Also, through the development of a fabrication process of GFETs with a buried gate configuration, this work contributed to the direct nanoscopic observation of plasma waves in the GFET channel during terahertz illumination.

The study was conducted by (i) setting up a model describing the influence of impurities and defects on capacitance and transfer characteristics at low electric fields, (ii) by developing a method for studying the limiting mechanisms of the charge carrier velocity in the graphene channel at high electric fields and answering the question whether velocity saturation improves  $f_{\text{max}}$ , (iii) by developing a method to study the channel temperature and its effect on  $f_{\text{T}}$  and  $f_{\text{max}}$ . It was found that scattering by remote optical phonons limits the saturation velocity and charge carriers emitted from interface states at high fields are preventing the current to saturate and, hence, limiting  $f_{\text{T}}$  and  $f_{\text{max}}$ . Additionally, the study shows that the channel temperature in GFETs can increase significantly causing degradation of the high frequency performance due to the decrease of charge carrier mobility and velocity. In summary, this work shows that it is necessary to develop a GFET design and fabrication process providing clean and defect-free interfaces, to minimise parasitic effects, and to use materials with higher optical phonon energies and higher thermal conductivities than those used today. This will allow for realisation of GFETs with extrinsic  $f_{\text{T}}$  and  $f_{\text{max}}$  in the sub-terahertz range.

Keywords: graphene, field-effect transistors, microwave devices, saturation velocity, traps, impurities and defects, remote phonons, carrier transport, self-heating

#### LIST OF PUBLICATIONS

This thesis is based on the work contained in the following papers:

- Paper A M. Bonmann, A. Vorobiev, J. Stake, and O. Engström. 'Effect of oxide traps on channel transport characteristics in graphene field effect transistors.' Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena 35, 01A115 (2017), doi:10.1116/1.4973904.

- Paper B M. Bonmann, M. A. Andersson, A. Vorobiev, and J. Stake. 'Charge carrier velocity in graphene field-effect transistors.' Applied Physics Letters 111, 233505 (2017), doi:10.1063/1.5003684.

- Paper C M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, and J. Stake. 'Graphene Field-Effect transistors With High Extrinisc  $f_{\rm T}$  and  $f_{\rm max}$ .' *IEEE Electron Device Letters* 40, pp. 131-143 (2019), doi:10.1109/LED.2018.

- Paper D M. Bonmann, M. Krivic, X. Yang, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, and J. Stake. 'Effects of Self-Heating on  $f_{\rm T}$  and  $f_{\rm max}$  Performance of Graphene Field-Effect Transistors.' submitted to the journal *IEEE Transactions on Electron Devices*, Aug., 2019.

- Paper E P. Feijoo Guerro, F. Pasadas, M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, J. Stake, and D. Jiménez, 'Does carrier velocity saturation help to enhance f<sub>max</sub> in graphene field-effect transistors?' submitted to the journal Nanoscale Advances, Nov. 2019.

- Paper F M. Bonmann, M. A. Andersson, Y. Zhang, X. Yang, A. Vorobiev, and J. Stake. 'An Integrated 200-GHz Graphene FET Based Receiver,' extended paper in *proceedings IRMMW-THz 2018*, doi:10.1109/IRMMW-THz.2018.8510069.

- Paper G A. Soltani, F. Kuschewski, M. Bonmann, A. Generalov, A. Vorobiev, F. Ludwig, M. Wiecha, D. Čibaraitė, F. Walla, S. Kehr, L. Eng, J. Stake, and H. G. Roskos, 'Direct nanoscopic observation of plasma waves in channels of graphene field-effect transistors.' submitted to the journal *Light: Science & Applications*, Jul. 2019.

## Nomenclature

| $\hbar = 6.58 \times 10^{-16}$      | $[eV \cdot s]$                                                           | reduced Planck constant                          |

|-------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------|

| $\hbar\omega_{\mathrm{OP}}$         | [meV]                                                                    | optical phonon energy                            |

| $k_{\rm B} = 8.62 \times 10^{-5}$   | $[eV \cdot K^{-1}]$                                                      | Boltzmann constant                               |

| au                                  | [s]                                                                      | delay time                                       |

| $\epsilon_0 = 8.85 \times 10^{-12}$ | $[F \cdot m^{-1}]$                                                       | vacuum permittivity                              |

| $\epsilon$                          | L J                                                                      | relative permittivity                            |

| $\kappa$                            | $[W \cdot cm^{-1} \cdot K^{-1}]$                                         | thermal conductivity                             |

| $C_{\rm ox}$                        | $[F \cdot m^{-2}]$                                                       | oxide capacitance                                |

| $C_{\rm g}$                         | [F]                                                                      | gate capacitance                                 |

| $\widetilde{C}_{\mathrm{gd}}$       | [ <b>F</b> ]                                                             | gate-drain capacitance                           |

| $C_{ m gs}$                         | [ <b>F</b> ]                                                             | gate-source capacitance                          |

| $C_{\rm PG}$ and $C_{\rm PD}$       | [F]                                                                      | parasitic gate/drain pad capacitances            |

| $e = 1.6 \times 10^{-16}$           | [C]                                                                      | elementary charge                                |

| $E_{\rm DS,(int)}$                  | $[kV \cdot \mu m^{-1}]$                                                  | (intrinsic) electric field                       |

| $E_{\rm F}$                         | [eV]                                                                     | Fermi energy                                     |

| $E_{\rm g}$                         | [eV]                                                                     | bandgap energy                                   |

| $f_{\max,(int)}$                    | [Hz]                                                                     | (intrinsic) maximum frequency of oscillation     |

| $f_{\mathrm{T},(\mathrm{int})}$     | [Hz]                                                                     | (intrinsic) transit frequency                    |

| $g_{ m ds}$                         | [S]                                                                      | output conductance                               |

| $\sigma_{ m ds}$                    | [S]                                                                      | output conductivity                              |

| $g_{ m m}$                          | [S]                                                                      | transconductance                                 |

| $I_{\rm DS}$                        | [A]                                                                      | drain current                                    |

| l                                   | [nm]                                                                     | mean free path                                   |

| $L_{\rm g}$                         | [µm]                                                                     | gate length                                      |

| $L_{a}$                             | [µm]                                                                     | access area length                               |

| $\mu_0$                             | $\left[\mathrm{cm}^2 \cdot \mathrm{V}^{-1} \cdot \mathrm{s}^{-1}\right]$ | low-field mobility                               |

| $\mu$                               | $[cm^2 \cdot V^{-1} \cdot s^{-1}]$                                       | mobility                                         |

| $\hat{n}$                           | $[m^{-2}]$                                                               | charge carrier concentration                     |

| $n_0$                               | $[m^{-2}]$                                                               | residual charge carrier concentration            |

| $n_{ m imp}$                        | $[m^{-2}]$                                                               | charged impurity concentration                   |

| $n_{ m th}$                         | $[m^{-2}]$                                                               | thermally generated charge carrier concentration |

| $P_{\rm diss,(int)}$                | [mW]                                                                     | (intrinsic) dissipated power                     |

| $P_{\text{density},(\text{int})}$   | $[\mathrm{mW}\cdot\mu\mathrm{m}^{-2}]$                                   | (intrinsic) dissipated power density             |

| $ ho_{ m C}$                        | $[\Omega \cdot \mu \mathrm{m}]$                                          | specific width contact resistivity               |

| $R_{ m C}$                          | $[\Omega]$                                                               | contact resistance                               |

| $R_{\rm D}$                         | $[\Omega]$                                                               | drain resistance                                 |

| $R_{ m G}$                          | $[\Omega]$                                                               | gate resistance                                  |

| $R_{\rm S}$                         | $[\Omega]$                                                               | source resistance                                |

| $r_{ m i}$                          | $[\Omega]$                                                               | charging resistance of gate-source capacitance   |

| $R_{ m th}$                         | $[K \cdot mW^{-1}]$                                                      | thermal resistance                               |

| T                     | [K]                | Temperature                      |

|-----------------------|--------------------|----------------------------------|

| $t_{ m b}$            | $[\mu m]$          | bottom oxide thickness           |

| $t_{\rm s}$           | $[\mu m]$          | substrate thickness              |

| $t_{\rm ox}$          | $[\mu m]$          | (top) oxide thickness            |

| $v_{\rm F} \sim 10^6$ | $[m \cdot s^{-1}]$ | Fermi velocity                   |

| v                     | $[m \cdot s^{-1}]$ | charge carrier velocity          |

| $v_{\rm sat}$         | $[m \cdot s^{-1}]$ | charge carrier velocity          |

| $V_{\rm GS,(int)}$    | [V]                | (intrinsic) gate-source voltage  |

| $V_{\rm DS,(int)}$    | [V]                | (intrinsic) drain-source voltage |

| $V_{\rm Dir}$         | [V]                | Dirac voltage                    |

| $W_{\rm g}$           | $[\mu m]$          | gate width                       |

## Abbreviations

| FET          | field-effect transistor           | BOE                  | buffered oxide etch       |

|--------------|-----------------------------------|----------------------|---------------------------|

| GFET         | graphene FET                      | $\operatorname{CVD}$ | chemical vapor deposition |

| MOSFET       | metal-oxide-seminconductor FET    | $\mathbf{rf}$        | radio frequency           |

| HEMT         | high-electron-mobility transistor | R-V                  | resistance-voltage        |

| $SiO_2$      | silicon dioxide                   | I-V                  | current-voltage           |

| hBN          | hexagonal boron nitride           | C-V                  | capacitance-voltage       |

| S-parameters | scattering parameters             |                      |                           |

## Contents

| Abstract                                                                                                | i         |

|---------------------------------------------------------------------------------------------------------|-----------|

| List of publications                                                                                    | iii       |

| Nomenclature                                                                                            | v         |

| Abbreviations                                                                                           | vi        |

| Contents                                                                                                | vii       |

| 1 Introduction                                                                                          | 1         |

| 1.1 Thesis outline                                                                                      | 4         |

| 2 Graphene field-effect transistors                                                                     | <b>5</b>  |

| 2.1 Operation principle of FETs                                                                         | 5         |

| 2.2 DC characteristics of GFETs vs MOSFETs                                                              | 6         |

| 2.2.1 Scattering mechanisms                                                                             | 9         |

| 2.3 RF characteristics of FETs                                                                          | 11        |

| 2.3.1 Figures of merit                                                                                  | 11        |

| 2.3.2 Equivalent circuit                                                                                | 12        |

| 2.3.3 Dependencies of $f_{\rm T}$ and $f_{\rm max}$ on GFET design $\ldots \ldots \ldots \ldots \ldots$ | 13        |

| 2.4 Properties of graphene                                                                              | 16        |

| 2.4.1 Crystal structure and electronic band structure of graphene                                       | 16        |

| 2.4.2 Charge carrier statistics                                                                         | 18        |

| 2.4.3 Quantum capacitance                                                                               | 19        |

| 3 Fabrication and characterisation of GFETs                                                             | <b>21</b> |

| 3.1 GFET design and fabrication                                                                         | 21        |

| 3.2 Synthesis of graphene and characterization                                                          |           |

| of material quality                                                                                     | 25        |

| 3.2.1 Synthesis of graphene                                                                             | 25        |

| 3.2.2 Characterisation of material quality                                                              | 25        |

| 3.3 Device characterisation                                                                             | 28        |

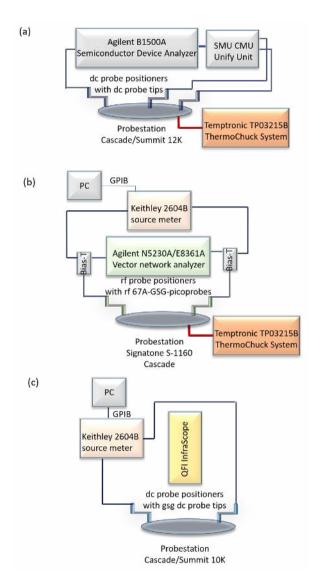

| 3.4 Measurement set-ups                                                                                 | 28        |

| 3.4.1 Evaluation of charge carrier mobility                                                             | 30        |

| 3.4.2 The drain-source resistance model                                                                 | 30        |

| 3.4.3 Evaluation of saturation velocity                                                                 | 32        |

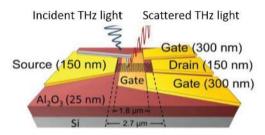

| 3.4.4 Near-field terahertz nanoscopy                                                                    | 33        |

| 4 Effects of imperfections and self-heating                            | <b>35</b> |

|------------------------------------------------------------------------|-----------|

| 4.1 Effect of imperfections on transport characteristics               | 35        |

| 4.1.1 C-V and R-V characteristics                                      | 35        |

| 4.1.2 Output characteristics                                           | 37        |

| 4.1.3 Effect of interface state density distribution                   | 38        |

| 4.2 Effect of saturation velocity on $f_{\rm T}$ and $f_{\rm max}$     | 39        |

| 4.2.1 Velocity limitations at high electric field                      | 39        |

| 4.3 GFET with state-of-the-art extrinsic $f_{\rm T}$ and $f_{\rm max}$ | 40        |

| 4.4 Effect of self-heating on $f_{\rm T}$ and $f_{\rm max}$            | 41        |

| 4.4.1 Self-heating                                                     | 41        |

| 4.4.2 Thermal resistance and temperature models                        | 41        |

| 4.4.3 Effect of substrate on $f_{\rm T}$ and $f_{\rm max}$             | 45        |

| 5 Conclusions and future outlook                                       | 47        |

| 6 Summary of appended papers                                           | 51        |

| 7 Appendix                                                             | 55        |

| 7.1 Fabrication of graphene field-effect transistors                   | 55        |

| 7.2 Delay-time analysis                                                | 57        |

| 7.3 Analytic thermal resistance model                                  | 58        |

| 7.4 Thermo-sensitive electrical parameters                             | 60        |

| -                                                                      | 00        |

| Acknowledgement                                                        | 60<br>63  |

| Acknowledgement<br>References                                          |           |

## Chapter 1

## Introduction

The long-sighted goal of this work is to develop devices for advanced electronics applications in the emerging areas of high-speed communication, terahertz sensing, and imaging [1, 2]. The relevant frequency ranges in this context are the extended microwave frequency region (200 MHz to 300 GHz), where applications range from communication to radar, GPS and many more, and the field of terahertz frequencies (300 GHz to 10 THz), where applications are mostly limited to space applications, such as remote sensing and spectroscopy [3], because water in the Earth's atmosphere strongly attenuates THz radiation [4]. However, due to continued technology development the generated output power by THz sources has been increased [1]. This allows for utilisation of THz radiation in security imaging systems [5], in diagnostic tools in medicine and life sciences [6] and in high-speed communication networks [7]. An elementary component for the successful realisation of these applications are fast transistors, which are elementary components of all electronic devices.

The first bipolar transistor was based on the semiconductor material germanium. It was demonstrated in 1947 by Shockley, Bardeen and Brattain who were awarded the Nobel prize for their work. Today, transistors based on silicon, i.e. metal-oxide-semiconductor field-effect transistor (MOSFET), are the most common. The material is the second most abundant in the Earth's crust [8], and the technology is very mature. Other successful transistor technologies are high-electron-mobility transistors (HEMTs) based on gallium arsenide (GaAs) [9] or indium phosphide (InP) [10]. Over the past years, the gate length of MOSFETS has been continuously reduced to reach higher operating speeds. However, the scaling of the MOSFET technology is about to reach its fundamental limits. Therefore, new device technologies, such as nanowire MOSFETs [11] and vacuum channel transistors [12], and new materials with higher charge carrier velocities are explored for the application in transistors. The extremely high intrinsic charge carrier mobility and velocity in the 2D-material graphene, superior to those in the semiconductor counterparts, have attracted attention for using graphene as a potential channel material in high-frequency field-effect transistors (FETs). Furthermore, the atomical thickness of graphene helps to reduce short channel effects, which become more prominent as the gate length is scaled down, due to increased electrostatic control [13].

The band structure and electrical properties of a monolayer of graphite, i.e., graphene, was first theoretically described in 1947 by P.R. Wallace *et al.* [14]. However, it was not until 2004 that graphene was separated from graphite by K. S. Novoselov *et al.* [15] and its thermodynamic stability along with the electric field effect in graphene could be proven. Graphene is unique in that it combines high room-temperature charge carrier velocity  $(6 \times 10^7 \text{ cm/s on hBN [16]})$ , high thermal conductivity (suspended graphene  $(1 - 5.3) \times 10^3$  W/m·K [17, 18]), mechanical strength, bendability and transparency in a single material. Graphene absorbs 2.3% of incident visible light [19]. This can be exploited in a number of emerging applications, such as transparent, stretchable electrodes [20, 21] and flexible

electronics [22].

The challenge of utilising graphene for transistor applications is its lack of a bandgap. It is not possible to achieve a high ratio between the on and off currents and a very small leakage current with graphene field-effect transistor (GFET), which makes it inapplicable for switching applications. Therefore, it is not possible to efficiently use graphene in logic circuits. Rather, research focuses on applications such as microwave amplifiers, mixers, power detectors and terahertz photonics [23, 24, 25, 26, 27, 28]. The first top-gated GFETs were developed in 2007 [29], followed by the development of subharmonic resistive mixers utilizing the symmetrical channel resistance vs. gate voltage characteristic of GFETs [30, 24] and a GFET amplifier operating at 1 GHz [23], leading to the demonstration of integrated components and circuits [31, 32], and the receiver composed by a graphene FET 200 GHz mixer and a 1 GHz intermediate frequency amplifier integrated on silicon substrate as presented in PAPER C. In PAPER G we report on the direct observation of plasma waves in the GFET channel under terahertz illumination.

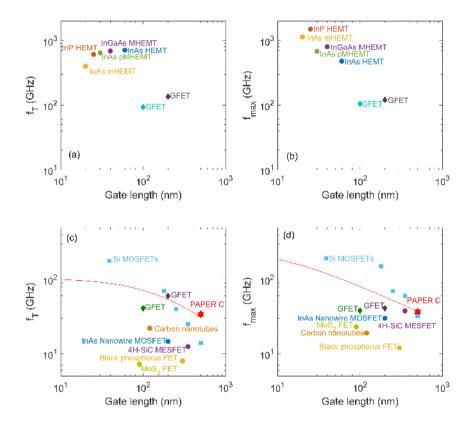

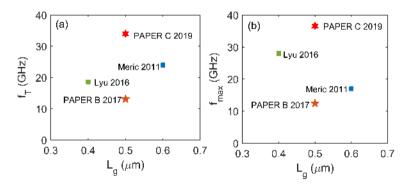

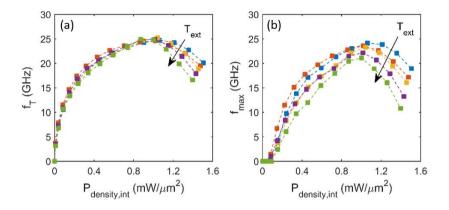

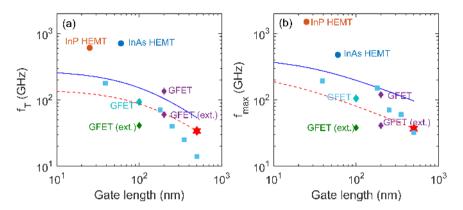

For amplifier applications, power gain and current gain are important parameters of a transistor. The figures of merit related to the power and current gain are the maximum frequency of oscillation  $(f_{\text{max}})$  and the transit frequency  $(f_{\text{T}})$ , respectively. Another figure of merit is the noise figure which is not addressed in this work. The microwave noise characterization of graphene field effect transistors and terahertz detectors is analysed in [33, 34]. Figure 1.1 summarises the state-of-the-art  $f_{\rm T}$  and  $f_{\rm max}$  of different device technologies. It is important to distinguish between extrinsic and intrinsic parameters. Often intrinsic performances are presented, leading to miss-interpretation if they are compared with extrinsic performances of the devices. The intrinsic values are obtained by de-embedding the measurements to exclude the effects of the parasitic capacitance, resistance, and inductance associated with the contact pads of the transistors [51]. Figure 1.1 shows that GFETs compete well with other transistor technologies when comparing  $f_{\rm T}$  at similar gate lengths. Values of  $f_{\rm T,int}$  of 407 GHz was achieved in GFETs with a gate length of  $L_{\rm g} = 100 \,\mathrm{nm}$  using bilayer graphene on a silicon carbide (SiC) substrate [49]. However, GFETs perform quite poorly in terms of  $f_{\rm max}$  compared to transistors based on other material systems, such as InAs PHEMTs with  $f_{\rm T}=644\,{\rm GHz}$ ,  $f_{\text{max}} = 681 \text{ GHz}$  [42], GaAs mHEMT with  $f_{\text{T}} = 688 \text{ GHz}$ ,  $f_{\text{max}} = 800 \text{ GHz}$  [43], and InP HEMT with  $f_{\text{max}} = 1 \text{ THz} [10]$ . For GFETs the highest  $f_{\text{max,int}}$  is 120 GHz with gate lengths of  $L = 200 \,\mathrm{nm}$  [49].

This poor performance is due to the lack of a bandgap and the associated poor current saturation, which leads to a high drain conductance. Additionally parasitic capacitances and resistances degrade the performance. Attempts were made to induce a bandgap in graphene, but when inducing a bandgap, the carrier mobility rapidly decreases. In conclusion, in terms of mobility and for a given bandgap, graphene does not offer a distinct advantage over conventional semiconductors [52]. Current saturation can also be achieved when the velocity of the charge carriers saturates [53]. This work considers the development of this approach and the impact of velocity saturation on the high-frequency performance is studied in PAPER E. In PAPER C, the design, technology and fabrication of GFETs with state-of-the-art  $f_{\rm T}$  and  $f_{\rm max}$  and promising scaling down behaviour were demonstrated. At similar gate lengths, the values of extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  are higher than those of the best published GFETs and comparable or even higher of the best published Si

Figure 1.1: State-of-the-art intrinsic (a)  $f_{\rm T}$  and (b)  $f_{\rm max}$  and extrinsic (c)  $f_{\rm T}$  and (d)  $f_{\rm max}$  for different HEMT and FET technologies (circles) [10, 35, 36, 37, 38, 39, 40, 41, 42, 43, 11], Si MOSFETs (squares) [44, 45, 46, 47] and GFETs [48, 49, 50] (diamonds) as well as for the GFET presented in PAPER C (star).

MOSFETs, see Fig. 1.1. The theoretically achievable intrinsic high-frequency performance limit of a top-gated GFET has been estimated to be approximately  $f_{\rm T,int}=640$  GHz at a channel length of 100 nm and approximately 3.7 THz at a channel length of 20 nm [54].

A clean fabrication process and high-quality interfaces between graphene and adjacent materials are needed for high and reliable performance of GFETs. Critical steps are the growth of high-quality graphene, a clean transfer process from the growth substrate to the target substrate, and a clean fabrication process of the device. It remains challenging to achieve high conformity in performance between GFETs on the same substrate. It has been shown that super-clean graphene can actually reach the theoretically predicted mobility limit at cryogenic temperatures of  $2 \times 10^5$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [55], but as soon as graphene comes into contact with another material, its mobility degrades severely due to the inclusion of

impurities and remote phonon scattering [56, 57]. In GFETs, there is at least one substrategraphene interface involved, when the transistor is backgated, and even two interfaces have to be considered for a top-gated GFET. Due to impurities and defects in the oxide and due to adsorbates at unprotected areas, the typical transfer and the capacitance versus gate voltage characteristics exhibit hysteresis [58, 59]. This is caused by charge transfer in and out of interface states associated with impurities. Therefore, it is important to study how impurities effect the charge transport in GFETs as is done in this work. In Paper A, a model was developed to describe how oxide traps affect the capacitance and transfer characteristics and it allows to study how these affect the extracted values of mobility, and residual charge carrier concentration, as well as to study how uncertainties in the parameters affect the extracted values. In Paper B, a model and method is presented for evaluation of the channel velocity in GFETs, via delay-time analysis, establishing relations between saturation velocity, extrinsic/intrinsic transit frequency, and concentration of charged impurities. This allows for understanding of the limitation of charge carrier velocity at high fields. Another limitation is the considerable increase of the channel temperature in GFETs operating under high drain bias, which is required for power gain. Self-heating at high fields as discussed in PAPER D, which provides a method to analyse the effect of self-heating on high-frequency performance of GFETs. In summary, this work contains the device modelling, fabrication, characterisation, and analysis of GFETs, with the aim to understand the limiting factors of the high-frequency performance of GFETs with the presented methods, and provide guidelines for further development.

## 1.1 Thesis outline

The following chapters serve as complementary background information for the content presented in the appended papers. In Chapter 2 the general working principle of FETs, the difference between GFETs and MOSFETs, and graphene properties for high-frequency FETs are explained. In Chapter 3 the fabrication process and device characterisation techniques are presented. The effect of impurities, defects and self-heating on  $f_{\rm T}$  and  $f_{\rm max}$  are discussed in Chapter 4. Finally, the main results are concluded in Chapter 5 with discussion of possible future pathways.

## Chapter 2

## Graphene field-effect transistors

In this chapter the operating principle of field-effect transistors and the figures of merit for current gain and power gain of rf transistors are introduced. The distinguishable features of graphene field-effect transistors compared to other transistor technologies are discussed and associated with graphene-specific properties.

## 2.1 Operation principle of FETs

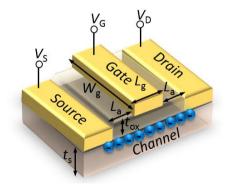

Field-effect transistors are active electronic components that can be found in any electronic device. The name field-effect transistor arises from the utilisation of the field effect in this type of transistor [60]. The field effect entails the modulation of the current between a drain and source terminals with potentials of,  $V_{\rm D}$  and  $V_{\rm S}$ , respectively, through the application of an out-of-plane electric field on the gate terminal by applying a gate potential  $V_{\rm G}$ . The current through the channel is either modulated by altering the channel height or by changing the charge carrier concentration in the channel. Junction field-effect transistors (JFETs) and metal-semiconductor field-effect transistors (MESFETs) belong to the former group, whereas in MOSFETs, HEMTs and GFETs, the carrier concentration is changed. In GFETs, it is even possible to change the majority charge carrier type in the channel due to lack of bandgap in graphene. Figure 2.1 shows a schematic cross section of a MOSFET structure.

Figure 2.1: Schematic cross section of a MOSFET or GFET with one gate finger. The gate, drain and source contacts, the corresponding potentials, the gate width  $W_{\rm g}$ , the gate length  $L_{\rm g}$ , the ungated access area length  $L_{\rm a}$ , the substrate thickness  $t_{\rm s}$ , and oxide thickness  $t_{\rm ox}$  are labeled and the channel region is illustrated with circles.

### 2.2 DC characteristics of GFETs vs MOSFETs

The current density in the channel of a field-effect transistor is expressed as:

$$J = e \cdot n \cdot v, \tag{2.1}$$

where e is the elementary charge, n is the charge carrier concentration, and v is the charge carrier drift velocity. The charge carrier concentration n is modulated by applying a gate voltage  $V_{\rm GS}$  as explained in Section 2.4.2, whereas the charge carrier drift velocity depends on the in-plane electric field between the source and drain  $E_{\rm int} = V_{\rm DS,int}/L_{\rm g}$ , where  $V_{\rm DS,int}$  is the applied intrinsic drain voltage. The charge carrier mobility  $\mu$  is defined as  $\mu = v \cdot E_{\rm int}$ .  $\mu$  is a measure of how well charge carriers can move through a material and is proportional to their mean free path. The field-dependent drift velocity is commonly modelled as follows [61]:

$$v = \frac{\mu_0 E_{\rm int}}{(1 + (\mu_0 E_{\rm int}/v_{\rm sat})^{\gamma})^{1/\gamma}},$$

(2.2)

where  $\mu_0$  is the low-field mobility,  $v_{\text{sat}}$  is the saturation velocity of the charge carriers, and  $\gamma$  is a fitting parameter. At low electric fields Eq. 2.2 can be approximated by

$$v \approx \mu_0 E_{\text{int}}.$$

(2.3)

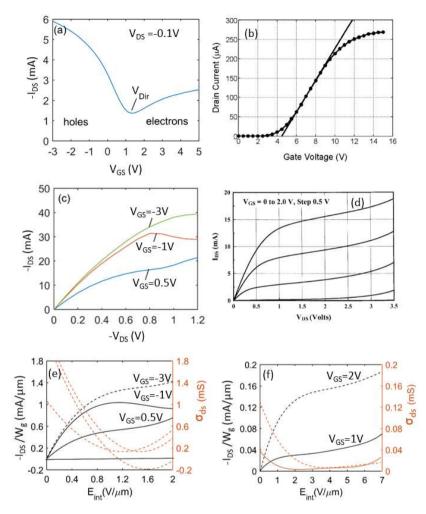

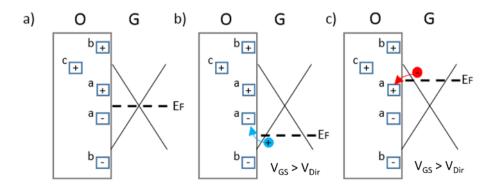

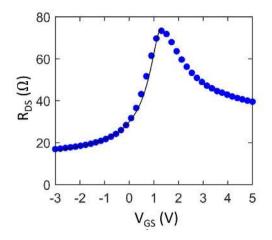

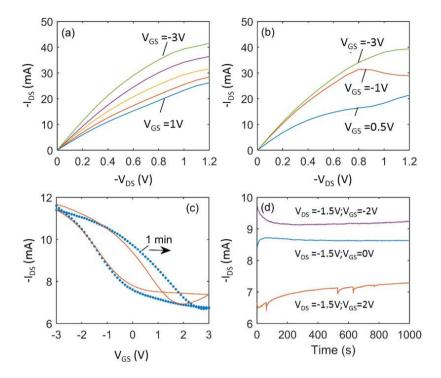

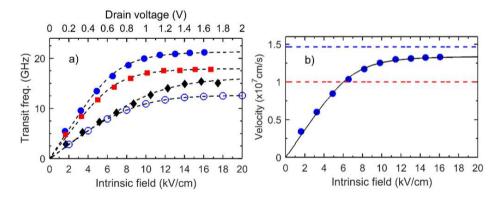

At low-fields,  $\mu_0$  is used as a quality parameter of the material. The larger  $\mu_0$  the fewer scattering centers, i.e. imperfections and impurities, are apparent. At high fields, i.e., high  $V_{\rm DS}$ , the drift velocity saturates and approaches  $v_{\rm sat}$ . The scattering mechanism at low and high fields are different as discussed in Section 2.2.1. Therefore,  $v_{\rm sat}$  is used to characterise transistors at high fields. Fig. 2.2 shows the typical output and transfer characteristics of GFETs and conventional semiconductor MOSFETs. It is apparent that the dc characteristics of the two devices differ significantly. Figures, 2.2(a) and (b) show the transfer characteristics of the GFET presented in PAPER C and of a MOSFET [62], respectively. In the transfer characteristic of the GFET the drain current  $I_{\rm DS}$  is increasing with sweeping  $V_{\rm GS}$  in both directions from the charge neutrality point  $V_{\rm Dir}$ . At the charge neutrality point the Fermi level is at  $E_{\rm F} = 0 \, {\rm eV}$  and the conductance is defined by the residual charge carrier concentration  $n_0$  which consists of thermally generated charge carriers  $n_{\rm th}$  and charge carriers induced due to charged defects [56]. The effect of defects and impurities on the charge transport characteristics is discussed in Section 4.1 and analysed in PAPER A. Typically, the transfer characteristics of graphene are not symmetrical and the resistance increases when the majority charge carrier type changes from holes to electrons. Partly, this can be explained by the difference in scattering cross sections of holes and electrons, which can result in the ratio  $\mu_{\rm e}/\mu_{\rm h}=0.83$  or 0.37 between the electron and hole mobilities, according to experimental and theoretical studies [63, 64]. Partly, the asymmetry can be explained by differing contact resistances of the source and drain sides of the GFETs due to formation of p-n junctions between the gated channel and the ungated regions [65]. In contrast, as can be seen in Fig. 2.2(b), the drain current  $I_{\rm DS}$  of a semiconductor MOSFET reduces to approximately zero below the threshold voltage  $V_{\rm T}$ . Figures 2.2(c) and (d) show the output characteristics of the GFET presented

Figure 2.2: Comparison of the transfer and output characteristics of typical GFETs and MOSFETs. (a) Transfer characteristic of the GFET presented in PAPER C with  $L_{\rm g} = 0.5 \,\mu{\rm m}$  and  $W_{\rm g} = 30 \,\mu{\rm m}$ . The position of the charge neutrality point, i.e., the gate voltage for minimal conductance  $V_{\rm Dir}$  is marked. (b) The transfer curve of a MOSFET [62]. In contrast to the GFET in (a) there is a threshold voltage  $V_{\rm T}$ . For  $V_{\rm GS} < V_{\rm T}$  the MOSFET is considered to be off. (c) The output characteristics of the GFET presented in PAPER C. The output curve at  $V_{\rm GS} = 0.5 \,\rm V$  shows the "kink" where the charge carrier type in the channel changes from holes to electrons. (d) Output characteristics of a MOSFET with  $L_{\rm g} = 0.5 \,\mu{\rm m}$  and  $W_{\rm g} = 100 \,\mu{\rm m}$  [46]. The output characteristics exhibit current saturation over a wide bias range of the drain voltage  $V_{\rm DS}$ . Drain current densities  $I_{\rm DS}/W_{\rm g}$  and the drain conductivity  $\sigma_{ds}$  versus intrinsic drain field  $E_{\rm int}$  of the output characteristics of (e) the GFET and (f) the MOSFET in (c-d).

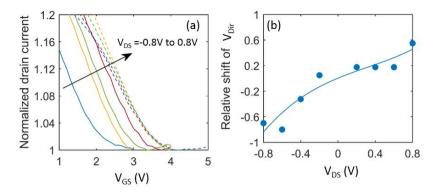

Figure 2.3: Illustration of how the gate voltage of minimum conductance, i.e., the Dirac voltage  $V_{\text{Dir}}$ , shifts with the applied drain voltage  $V_{\text{DS}}$ . (a) The normalized measured drain current versus gate voltage  $V_{\text{GS}}$ . The lines are at negative  $V_{\text{DS}}$ , the dashed lines are at positive  $V_{\text{DS}}$ . (b) The measured shift of  $V_{\text{Dir}}(V_{\text{DS}})$  relative to  $V_{\text{Dir}}(V_{\text{DS}} = 0 \text{ V})$  versus applied  $V_{\text{DS}}$  (circles). The line is a polynomial fitting curve.

in PAPER C with  $L_{\rm g} = 0.5\,\mu{\rm m}$  and  $W_{\rm g} = 30\,\mu{\rm m}$  and a MOSFET with  $L_{\rm g} = 0.5\,\mu{\rm m}$ and  $W_{\rm g} = 100\,\mu{\rm m}$  [46]. Figure 2.2(d) shows that for the semiconductor MOSFETs the drain current saturates at high drain voltages (high electric fields). The current saturation in semiconductor MOSFETs is caused by velocity saturation and pinch-off of the channel. Figure 2.2(c) shows that a saturation plateau, the so-called "kink", in the output characteristics of GFETs can be observed only for a small voltage range. The kink is obtained in a condition where the applied voltages effectively moves the Fermi level to the Dirac point at the drain side of the GFET channel, this is the point where the charge carrier concentration reduces to a minimum [66]. As illustrated in Fig. 2.3, this condition is approximately established, when  $V_{\rm DS} = V_{\rm GS} - V_{\rm Dir}$ . Because graphene has no bandgap, a further increase of the in-plane electric field changes the charge carrier type in the channel and the concentration increases. Therefore, the current continues increasing instead of saturating. At large  $V_{\rm GS}$  the current will saturate before the drain voltage is large enough to fulfil the condition  $V_{\rm DS} = V_{\rm GS} - V_{\rm Dir}$ . As discussed in PAPER C and PAPER D the observed current saturation and even negative differential conductance are due to velocity saturation and due to the decrease of the saturation velocity caused by self-heating. Figure 2.2(e-f) compares the drain current densities  $I_{\rm DS}/W_{\rm g}$  and the drain conductivity  $\sigma_{\rm ds}$  versus intrinsic drain field  $E_{\rm DS,int}$  of the output characteristics of the GFET and MOSFET in Fig. 2.2(c-d), where the drain conductivity is calculated as:

$$\sigma_{\rm ds} = g_{\rm ds} \cdot \frac{L_{\rm g}}{W_{\rm g}}.\tag{2.4}$$

The drain current density and hence the minimal drain conductivity are approximately ten times larger in the GFET than in the MOSFET, due to the lack of a bandgap. Due to the negative slope in the current density curve of the GFET at  $V_{\rm GS} = -1$  V the drain conductivity exhibits negative values at the corresponding drain fields.

#### 2.2.1 Scattering mechanisms

Scattering of charge carriers in the graphene lattice can occur via different mechanisms, which are categorised into intrinsic and extrinsic scattering. Extrinsic scattering can be minimised by careful device design and an appropriate fabrication technology, whereas intrinsic scattering is inherent to the graphene lattice and sets an upper limit on the achievable performance of GFETs. Intrinsic scattering is due to lattice vibration, i.e., optical and acoustical phonons, and scattering between charge carriers within graphene. Extrinsic scattering mechanisms are scattering at neutral and charged impurities, scattering at defects and remote phonon scattering by adjacent materials. Experimentally, the dependencies of conductivity, of mobility, of the temperature, of the charge carrier concentration, and the electric field are often investigated to determine which are the dominating and limiting scattering mechanisms.

In graphene, at low fields and at room temperature elastic scattering mechanisms, i.e., resonant scattering, long range Coulomb scattering and scattering by surface polar phonons are most relevant. Every scattering mechanism has a specific mean free path, which is the distance that a mobile charge carrier can travel through an atomic lattice before it is scattered. The mean free path of resonant scatters  $(l_{\rm RS})$  and Coulomb scattering  $(l_{\rm CL})$  depend on charge carrier concentration as  $l_{\rm RS}(n) \propto \sqrt{n} ln(\sqrt{n})^2$  and  $l_{\rm Cl}(n) \propto \sqrt{n}$ , respectively [67]. The mobility is proportional to l

$$\mu \propto \frac{el}{\hbar\sqrt{\pi n}}.\tag{2.5}$$

When several scattering mechanisms are active at the same time,  $\mu$  is approximated as effective  $\mu_{\text{eff}}$  using Matthiessen's rule [68]:

$$\frac{1}{\mu_{\rm eff}} = \frac{1}{\mu_1} + \frac{1}{\mu_2} + \dots + \frac{1}{\mu_{\rm n}}.$$

(2.6)

At high electric fields charge carriers gain enough kinetic energy to transfer energy to the material lattice. The relevant extrinsic scattering mechanism is inelastic soft optical phonon remote scattering by adjacent dielectrics. The dependence of the saturation velocity on charge carrier concentration and temperature is described by simplified models for the optical-phonon-scattering-limited saturation velocity model [69, 70, 71]

$$v_{\rm sat}(n,T) = \frac{2}{\pi} \frac{\omega_{\rm OP}}{\sqrt{\pi n}} \sqrt{1 - \frac{\omega_{\rm OP}^2}{4\pi n v_{\rm F}^2} \frac{1}{N_{\rm OP} + 1}} \quad \text{or} \quad v_{\rm sat} \approx \frac{2}{\pi} \frac{\omega_{\rm OP}}{\sqrt{\pi n}},\tag{2.7}$$

where  $\hbar\omega_{\rm OP}$  is the optical phonon (OP) energy, and  $N_{\rm OP} = 1/[exp(\hbar\omega_{\rm OP}/kT) - 1]$  is the phonon occupation. How charged impurity scattering affects  $v_{\rm sat}$  is discussed in PAPER B and Section 4.2.1.

#### Ballistic transport

The scattering time relates to the mean free path l, which is the distance that a charge carrier can travel before it is scattered. When the mean free path is much smaller than

the channel length  $l \ll L_{\rm g}$  it is appropriate to consider diffusive transport. The condition  $l \gg L_{\rm g}$  is called ballistic transport. Ballistic-like transport can be achieved in devices with high-quality graphene and short gate length. For a device with the dimensions  $L_{\rm g} \times W_{\rm g} = 0.5 \,\mu{\rm m} \times 1.4 \,\mu{\rm m}$ , the maximum ballistic mobility is ~ 280000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at the charge carrier concentration  $n \sim 4 \times 10^9 \,{\rm cm}^{-2}$  [72]. Furthermore, ballistic transport has been observed at room temperature over a distance of  $1 \,\mu{\rm m}$  in Hall bar structures with graphene encapsulated in hexagonal boron nitride with  $n \sim 10^{11} \,{\rm cm}^{-2}$  and  $\mu > 100000 \,{\rm cm}^2 {\rm V}^{-1} {\rm s}^{-1}$  [73]. However, for the mobilities and gate lengths of the transistors considered in this work it is sufficient to assume diffusive transport. The fabrication process of GFETs unintentionally introduces impurities at the interfaces between the graphene layer and the adjacent substrate and the gate dielectric. Inevitably, these impurities act as scattering centres and shorten the scattering length.

### 2.3 RF characteristics of FETs

#### 2.3.1 Figures of merit

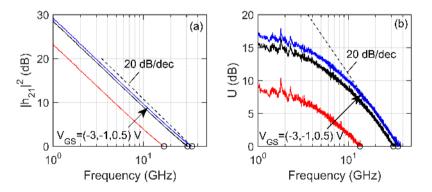

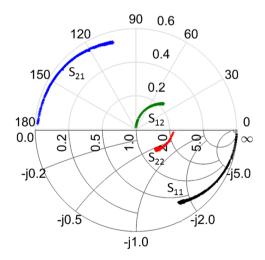

To benchmark analog radio frequency (rf) applications the important figures of merit are the maximum frequency of oscillation  $(f_{\text{max}})$  and the transit frequency  $(f_{\text{T}})$  for the characterization of the high-frequency performance. The maximum frequency of oscillation is the frequency at which the unilateral power gain U is unity, and the transit frequency is the frequency at which the short-circuit current gain  $h_{21}$  is unity (0 dB).  $f_{\text{max}}$  and  $f_{\text{T}}$ of a device are estimated from scattering parameters (S-parameters) measured by a vector network analyser, calculating and extrapolating U and  $h_{21}$  to 0 dB using the fact that they roll off at a slope of -20 dB/dec with frequency, as shown in Fig. 2.4. The unilateral gain is calculated in terms of the measured scattering parameter matrix S by [74]

$$U = \frac{|S_{12} - S_{21}|^2}{\det[\mathbf{1} - \mathbf{SS^*}]},$$

(2.8)

where 1 is the unitary matrix and \* denotes the complex conjugate. The short-circuit current gain can be expressed via S-parameters as follows [75],

$$h_{21} = \frac{-2S_{21}}{(1 - S_{11})(1 + S_{22}) + S_{12}S_{21}}.$$

(2.9)

Depending on the intended application,  $f_{\rm T}$  and  $f_{\rm max}$  should be at least three times larger than the operation frequency of the transistor [76]. Other important figures of merit are the minimum noise figure, output power and power-added efficiency [76] which are not part of the discussion in this work.

Figure 2.4: (a) Small-signal current gain  $(|h_{21}|^2)$ , and (b) unilateral power gain (U) versus frequency at  $V_{\rm DS}$ =-1.1 V and  $V_{\rm GS} = (-3, -1, 0.5)$  V. The dashed line indicates the 20 dB/dec slope.

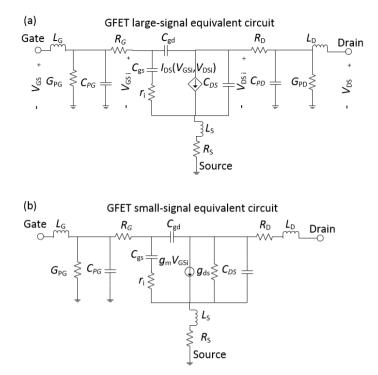

#### 2.3.2 Equivalent circuit

Important tools for modelling and optimisation of the rf performance of full microwave circuits are the small-signal or large-signal equivalent circuits, which are representing FETs with lumped elements as shown in Fig. 2.5. The large-signal modelling requires consideration of non-linearities within the device when a large signal is applied to describe the behaviour of the transistor. A large-signal model of GFETs has been presented in [77] and is used for the analysis of the integrated mixer-amplifier circuit in PAPER F. In contrast, for small-signal modelling, the amplitude of the signal is assumed to be small enough such that the behaviour of the lumped elements can be linearised around the bias point. These circuits are used in the analysis of the GFETs in PAPER B-D.

The elements in the equivalent circuit correspond to actual physical effects in the transistor and can be extracted using dc measurements and S-parameter measurements [78, 79, 77]. The equivalent circuits consist of intrinsic and extrinsic elements. The intrinsic elements are the gate-source and gate-drain capacitances ( $C_{\rm gs}$  and  $C_{\rm gd}$ ) and the charging resistance for the gate-source capacitance ( $r_{\rm i}$ ). Furthermore, the current source  $g_{\rm m}V_{\rm GSi}$  and the drain conductance  $g_{\rm ds}$  are parts of the intrinsic device, where  $g_{\rm m}$  is the intrinsic transconductance. The intrinsic transconductance is defined as the derivative of the drain current ( $I_{\rm d}$ ) with respect to the intrinsic gate voltage ( $V_{\rm GSi}$ ):

$$g_{\rm m} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GSi}} \Big|_{V_{DSi} = \rm const.}$$

(2.10)

The drain conductance is the derivative of the drain current with respect to the intrinsic drain voltage  $(V_{\text{DSi}})$ :

$$g_{\rm ds} = \frac{\partial I_{\rm DS}}{\partial V_{\rm DSi}} \Big|_{V_{Gi} = {\rm const.}}$$

(2.11)

The extrinsic elements are the parasitic drain, source and gate resistances ( $R_{\rm D}$ ,  $R_{\rm S}$  and  $R_{\rm G}$ ), the bond and lead inductances ( $L_{\rm D}$ ,  $L_{\rm S}$  and  $L_{\rm G}$ ), the parasitic pad conductances  $G_{\rm PG}$  and  $G_{\rm PD}$ , the parasitic pad capacitances  $C_{\rm PG}$  and  $C_{\rm PD}$ , the drain-source capacitance ( $C_{\rm DS}$ ), which is the junction capacitance of the parasitic diode formed at the drain side of a MOSEFET. Since, there is no real formation of a depletion region in the GFET channel due to the lack a bandgap in graphene,  $C_{\rm DS}$  is mostly negligible. The intrinsic and extrinsic figures of merit,  $f_{\rm T,int}$ ,  $f_{\rm max,int}$  and  $f_{\rm T}$ ,  $f_{\rm max}$ , respectively, can be approximated in terms of the small-signal equivalent circuit elements as [80, 81]

$$f_{\rm T,int} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})},$$

(2.12)

$$f_{\rm max,int} = \frac{g_{\rm m}}{4\pi C_{\rm gs}} \times \frac{1}{\sqrt{g_{\rm ds}r_{\rm i}}},\tag{2.13}$$

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})} \frac{1}{1 + g_{\rm ds}(R_{\rm S} + R_{\rm D}) + \frac{C_{\rm gd}g_{\rm m}(R_{\rm S} + R_{\rm D})}{C_{\rm gs} + C_{\rm gd}}} + \frac{C_{\rm PG}}{C_{\rm gs} + C_{\rm gd}},$$

(2.14)

$$f_{\rm max} = \frac{g_{\rm m}}{4\pi C_{\rm gs}} \frac{1}{\sqrt{g_{\rm ds}(r_{\rm i} + R_{\rm S} + R_{\rm G}) + g_{\rm m}R_{\rm G}\frac{C_{\rm gd}}{C_{\rm gs}}}}.$$

(2.15)

Figure 2.5: (a) Large-signal equivalent circuit of the GFETs used in the mixer and amplifier modelled in PAPER F. (b) Small-signal equivalent circuit of the GFETs modelled in PAPER B-D.

#### 2.3.3 Dependencies of $f_{\rm T}$ and $f_{\rm max}$ on GFET design

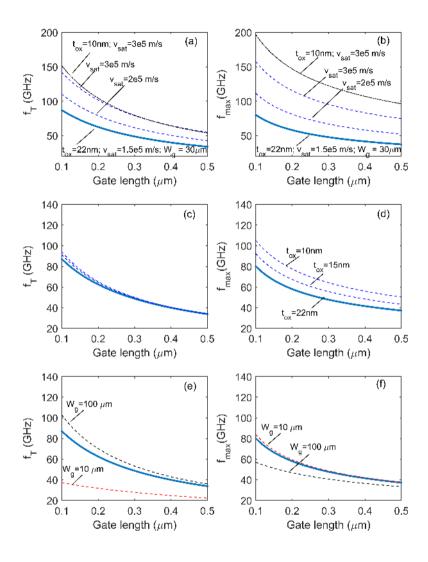

Apparently, the values of the circuit elements are defined by the design of the transistor, and thus,  $f_{\rm T}$  and  $f_{\rm max}$  can be optimised by a careful transistor design. Analysis of Eqs. (2.14-2.15) suggests that  $g_{\rm ds}$  and all parasitic elements, i.e., parasitic pad capacitances and gate, source and drain resistances, should be as small as possible, whereas  $g_{\rm m}$  has to be maximized. As an example, Figure 2.6 illustrates how  $f_{\rm max}$  and  $f_{\rm T}$  of the GFET presented in PAPER C are affected by varying the gate length, the saturation velocity, the gate oxide thickness, and the gate width. For calculations, the values of the specific width contact resistivity ( $\rho_{\rm C} = 3.3 \cdot 10^{-4} \,\Omega$ m), of the low-field mobility ( $\mu_0 = 1800 \,{\rm cm}^2/{\rm Vs}$ ), of the intrinsic electric field ( $E_{\rm int} = 1.65 \,{\rm V}/\mu$ m), and of the pad capacitance  $C_{\rm PG} = 7 \,{\rm fF}$  are taken from PAPER C. The resistances are calculated as  $R_{\rm C} = \rho_{\rm C}/(2W_{\rm g})$  and  $R_{\rm S} = R_{\rm D} = \rho_{\rm C}/W_{\rm g}$ . To account for the dependence on saturation velocity ( $v_{\rm sat}$ ), the expression for the fielddependent velocity (Eq. 2.2) is used. The found effective velocity value (v) is then used to calculate  $f_{\rm T,int}$  [82]:

$$f_{\rm T,int} = \frac{v}{2\pi L_{\rm g}}.$$

(2.16)

Figure 2.6: The modelled dependencies of  $f_{\rm T}$  and  $f_{\rm max}$  on different device parameters. The solid thick line in (a-f) is calculated for the original values of the GFET presented in PAPER C with the gate oxide thickness  $t_{\rm ox} = 22 \,\mathrm{nm}$ , the saturation velocity  $v_{\rm sat} = 1.5 \cdot 10^5 \,\mathrm{m/s}$ , and the gate width  $W_{\rm g} = 30 \,\mu\mathrm{m}$  and varying gate length  $L_{\rm g}$ . (a) and (b) shows the effect of varying  $v_{\rm sat}$ . The thin solid line is with  $t_{\rm ox} = 10 \,\mathrm{nm}$ . (c) and (d) show the effect of varying  $t_{\rm ox}$ . (e) and (f) show the effect of varying gate width  $W_{\rm g}$ . The solid lines assume that the drain conductivity  $\sigma_{\rm ds}$  scales with drain current, i.g., with  $W_{\rm g}$ .

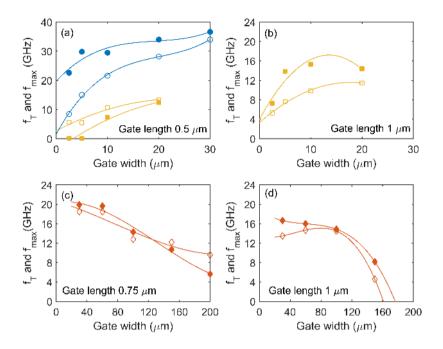

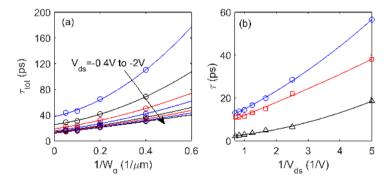

Figure 2.7: Gate width dependence of  $f_{\rm T}$  (open symbols) and  $f_{\rm max}$  (filled symbols) for different gate length and different device technologies. (a) The circles are the values of GFETs prepared as in PAPER C. The squares in (a) and (b) are the values of GFETs prepared in PAPER B. The diamonds in (c) and (d) are GFETs with graphene sandwiched between Al<sub>2</sub>O<sub>3</sub>.

Next,  $f_{\rm T,int}$  is used to estimate  $g_{\rm m}$  using Eq. (2.12). The found value of  $g_{\rm m}$  is then used to calculate the charging resistance  $r_{\rm i} = 1/(3g_{\rm m})$  [82]. The gate-source and gate-drain capacitances are scaled as in PAPER C,  $C_{\rm gs} = 0.5C_{\rm g}$  and  $C_{\rm gd} = 0.2C_{\rm g}$ , where the gate capacitance  $C_{\rm g} = C_{\rm ox} W_{\rm g} L_{\rm g}$  with the oxide capacitance  $C_{\rm ox} = \epsilon \epsilon_0 / t_{\rm ox}$ . The relative permittivity of  $Al_2O_3$  is  $\epsilon = 7.5$ . The gate resistance is calculated using the resistivity of gold ( $\rho_{\rm g} = 2.44 \times 10^{-8} \,\Omega{\rm m}$ ) and the dimensions of the gate finger as  $R_{\rm G} = \rho_{\rm g} W_{\rm g} / (3L_{\rm g} t_{\rm g} N)$ [82], where  $t_{\rm g} = 300 \,\rm nm$  is the thickness of the gate metal, and N the number of gate fingers. Note, that the width of the gate here is the length of the gate resistor. The drain conductance  $g_{ds}$  is calculated using the expression for the drain conductivity Eq. 2.4. Figure. 2.6 shows that increasing  $v_{\text{sat}}$  improves both  $f_{\text{T}}$  and  $f_{\text{max}}$ . Reducing the oxide thickness improves  $f_{\rm max}$ , but has almost no effect on  $f_{\rm T}$ . Varying the gate width has opposite effects on  $f_{\rm T}$  and  $f_{\rm max}$ . A larger  $W_{\rm g}$  reduces the negative impact of  $C_{\rm PG}$  and  $R_{\rm C}$ , but  $R_{\rm G}$  is increasing, hence,  $f_{\rm T}$  is improved whereas  $f_{\rm max}$  is worsen. Figure 2.7 shows the gate width dependence of  $f_{\rm T}$  and  $f_{\rm max}$  for different GFET device technologies presented in this work. It appears as if there is fairly width independent performance between  $W_{\rm g} = 10-40 \,\mu{\rm m}$ . Below and above this gate width the performance decreases

rapidly. The reduction with increasing  $W_{\rm g}$  can be explained by the increase of  $R_{\rm G}$  and with increasing probability of holes and imperfections in the graphene sheet, the reduction in performance with small width can be associated with a relatively larger impact of the parasitic pad capacitances.

## 2.4 Properties of graphene

The room temperature charge carrier velocity in graphene is larger than that in other semiconductor materials, which in combination with its unique high thermal conductivity and mechanical properties motivates the interest for using graphene in high-frequency electronic devices. The material properties of graphene and other common semiconductor materials are compared in Table 2.1. Note, the given values of thermal conductivity, mobility, and saturation velocity might vary in the literature depending on the measurement conditions.

#### 2.4.1 Crystal structure and electronic band structure of graphene

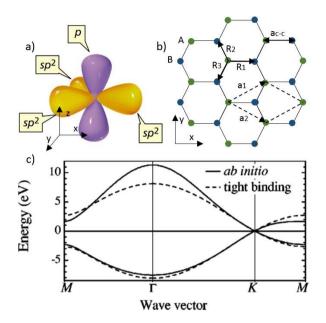

Fig. 2.8(a) shows the orbital model of the carbon atoms in graphene. The three sp2 orbitals are equally spaced in the x-y-plane by an angle of 120° and form strong covalent  $\sigma$  bonds between the carbon atoms with a carbon-carbon bond length of approximately  $a_{\rm c-c} \approx 1.42$  Å, which leads to the typical hexagonal arrangement as shown in Fig. 2.8(b) and explains the mechanical strength of graphene. The 2p<sub>z</sub> orbital forms out-of-plane  $\pi$  bonds with the neighbouring carbon atoms, which allows electrons to move rather freely across the graphene sheet and is responsible for the notable electronic properties of graphene. The corresponding electronic band structure of graphene, which describes the allowed energy sates versus the momentum of electrons, is found by solving the Schrödinger equation. An approximate expression for the dispersion relation is found using the nearest-neighbor tight-binding model (NNTB) assuming electron-hole symmetry [24, 88] as

$$E(k)^{\pm} = \pm \gamma \sqrt{1 + 4\cos\left(\frac{\sqrt{3}a}{2}k_{\mathrm{x}}\right)\cos\left(\frac{a}{2}k_{\mathrm{y}}\right) + 4\cos^{2}\left(\frac{a}{2}k_{\mathrm{y}}\right)},\tag{2.17}$$

Table 2.1: Comparison of graphene properties at T = 300 K with conventional semiconductors.  $E_{\rm g}$  is the energy bandgap,  $m * / m_{\rm e}$  is the electron effective mass,  $\mu$  is the mobility,  $v_{\rm sat}$  is the saturation velocity, and  $\kappa$  is the thermal conductivity [83, 16, 17, 84, 85, 86, 87].

| Properties                                        | Graphene                     | Si   | GaAs    | GaN  | InAs  | InP  |

|---------------------------------------------------|------------------------------|------|---------|------|-------|------|

| $E_{\rm g}~({\rm eV})$                            | 0                            | 1.12 | 1.42    | 3.44 | 0.35  | 1.34 |

| $m * / m_{\rm e}$                                 | $0 @V_{\mathrm{Dir}}$        | 0.98 | 0.06    | 1.5  | 0.02  | 0.08 |

| $\mu \ (\mathrm{cm}^2/\mathrm{V}\cdot\mathrm{s})$ | 100000 (on hBN)              | 1450 | 900     | 9000 | 33000 | 5400 |

| $v_{\rm sat} \ (\times 10^7  {\rm cm/s})$         | 5 (on hBN)                   | 1    | 0.7/2.7 | 1.4  | 0.9   | 0.7  |

| $\kappa  (\mathrm{W cm^{-1} K^{-1}})$             | 1 (supported) 10 (suspended) | 1.3  | 0.6     | 1.3  | 0.3   | 0.7  |

Figure 2.8: a) Orbital model of a carbon atom, [90]. b) The graphene lattice. The two inequivalent atom sites A (green dots) and B (blue dots) form the basis of the primitive unit cell indicated by the parallelogram (dashed lines).  $a_1$  and  $a_2$  are the primitive unit vectors (dashed arrows).  $R_1$ ,  $R_2$  and  $R_3$  describe the separation between atom site A and its nearest-neighbour atoms.  $a_{c-c} \approx 1.42 \text{ Å}$  is the carbon-carbon bond length. c) Comparison of the energy-momentum dispersion of ab initio calculations and the nearest-neighbour tight-binding approximation; adapted from [89].

where  $\gamma$  (typically between 2.7-3.1 eV) is the nearest neighbour overlap found by fitting Eq. 2.17 to ab initio calculations of the band structure at low energies (at the K point), as shown in Fig. 2.8(c) [89, 88].  $k_x$  and  $k_y$  are the coordinate components of the wave vector. The + and - signs denote the signs for the conduction ( $\pi^*$ ) and valence ( $\pi$ ) bands, respectively.

The dispersion relation centred at the K point can be further simplified to the linear relation

$$E(k)^{\pm} = \pm \hbar v_{\rm F} \sqrt{k {\rm x}^2 + k {\rm y}^2},$$

(2.18)

where  $\hbar$  is the reduced Planck's constant and  $v_{\rm F} = 3\gamma a_{\rm c-c}/2 \approx 10^6 \,{\rm m/s} \approx c_0/300$ , is the Fermi velocity, where  $c_0$  is the speed of light in vacuum. The dispersion relation of conventional semiconductor materials, such as silicon and gallium arsenide, is approximated by a parabolic function and exhibits a band gap, whereas in graphene, the dispersion relation is linearly approximated, and the electron states are described by the Dirac equation, similar to weightless particles. This is the reason why the cone-like shape of the energy band structure is called a Dirac cone, and the point where the valence and conduction bands touch ( $E = 0 \,{\rm eV}$ ) is called the Dirac point.

#### 2.4.2 Charge carrier statistics

From the dispersion relation, the density of states (DOS) can be derived, which is the density of available states per energy interval. For graphene, the DOS has the following form [91]:

$$g(E) = \frac{2}{\pi (\hbar v_{\rm F})^2} |E|.$$

(2.19)

The DOS together with the Fermi-Dirac distribution

$$f(E_{\rm F}) = \frac{1}{1 + e^{(E - E_{\rm F})/kT}},$$

(2.20)

where  $E_{\rm F}$  is the Fermi energy, k is the Boltzmann constant and T is the temperature, is used to calculate the charge carrier concentration in the graphene sheet. For a given temperature and position of the Fermi level, the Fermi distribution describes the probability that an electron occupies an available energy state. The charge carrier concentrations of electrons,  $n_{\rm e}(E_{\rm F})$ , and holes,  $n_{\rm h}(E_{\rm F})$ , are derived as

$$n_{\rm e}(E_{\rm F}) = \int_0^\infty g(E)f(E, E_{\rm F})dE \qquad (2.21)$$

and

$$n_{\rm h}(E_{\rm F}) = \int_{-\infty}^{0} g(E)(1 - f(E, E_{\rm F}))dE.$$

(2.22)

The total charge carrier concentration  $n_{\rm g}(E_{\rm F})$  is given by the sum of electrons and holes:

$$n_{\rm g}(E_{\rm F}) = n_{\rm e}(E_{\rm F}) + n_{\rm h}(E_{\rm F}).$$

(2.23)

The total charge is given by the difference between electrons and holes times the elementary charge:

$$Q_{\rm g}(E_{\rm F}) = e(n_{\rm h}(E_{\rm F}) - n_{\rm e}(E_{\rm F})) = -e \cdot \operatorname{sign}(E_{\rm F}) \frac{4\pi E_{\rm F}^2}{(hv_{\rm F})^2}.$$

(2.24)

Figure 2.9: Charge carrier concentration of holes (solid line) and electrons (dashed line) for different positions of the Fermi level as indicated by the vertical dashed line.

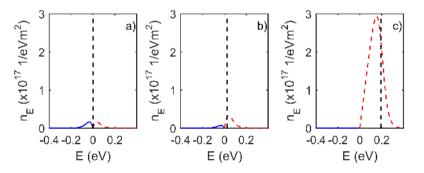

For  $E_{\rm F} = 0 \,\mathrm{eV}$ , the density of occupied states per unit volume and energy  $(n_{\rm E})$  for holes and electrons is the same as that shown in Fig. 2.9(a). The area below the curves is equal to the charge carrier concentrations of electrons and holes derived by Eqs. 2.21 and 2.22. As soon as the Fermi level is shifted to more positive energies, the charge carrier concentration will be dominated by electrons (Fig. 2.9(b-c)). The position of the Fermi level is tuned by either doping graphene with impurity atoms or via the field effect by electrical gating [15].

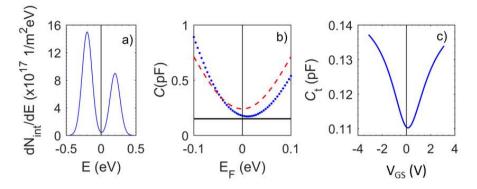

#### 2.4.3 Quantum capacitance

Due to the low density of states in graphene, a small shift in the Fermi level noticeably changes the charge carrier concentration. For material systems with low DOS, the so-called quantum capacitance  $(C_q)$  [92] needs to be considered.  $C_q$  is defined as the derivative of the total charge  $(Q_g)$  in graphene with respect to the local electrostatic channel potential  $V_{\rm ch} = E_{\rm F}/e$ , and for pristine graphene, it can be expressed as follows [93, 94]:

$$C_{\rm q} = \frac{\partial Q_{\rm g}}{\partial V_{\rm ch}} = \frac{8\pi e^2 kT}{(hv_{\rm F})^2} ln \Big[ 2 + 2\cosh\Big(\frac{E_{\rm F}}{kT}\Big) \Big]. \tag{2.25}$$

In GFETs the total gate capacitance  $(C_t)$  will be reduced due to the quantum capacitance  $(C_q)$  acting in series with the geometrical capacitance  $c_{ox} = \epsilon/t_{ox}$ :

$$C_{\rm t} = \frac{C_{\rm ox}C_{\rm q}}{C_{\rm ox} + C_{\rm q}}.$$

(2.26)

However, in the case that one of the capacitances is substantially lager than the other capacitance, the total capacitance can be approximated by the smaller capacitance, for example, when the gate oxide thickness is relatively large then

$$C_{\rm q} \gg C_{\rm ox} \to C_{\rm t} \approx C_{\rm ox}.$$

(2.27)

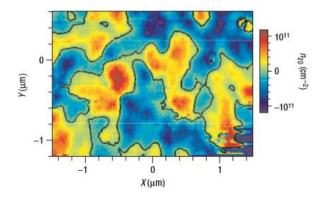

In PAPER A we consider the quantum capacitance for ideal graphene, but one needs to keep in mind that any distortion of the ideal graphene lattice that influences the electronic properties will affect the quantum capacitance since  $C_q$  is directly related to the density of states. Distortions can be generated by doping with impurity atoms, by forming nanoribbons (graphene strips with a width of a few nanometres) or by inducing strain [95, 96, 97, 98]. Also, charged defects introduce potential fluctuations across the graphene sheet. In that case, the quantum capacitance can be modelled assuming a Gaussian distribution of the potential [99].

## Chapter 3

## Fabrication and characterisation of GFETs

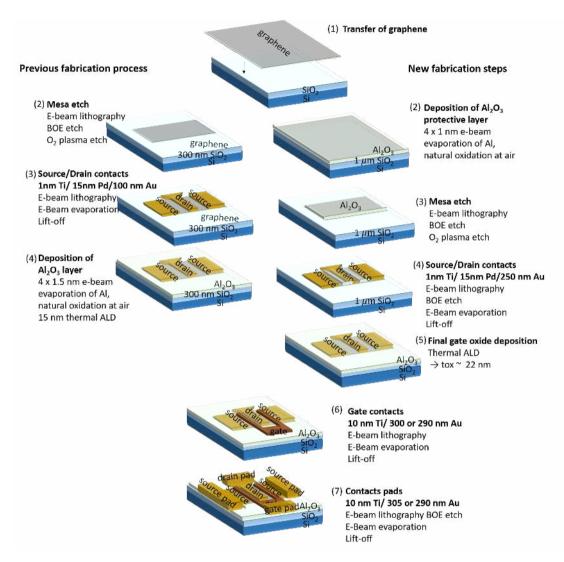

In this work, GFETs are designed and fabricated with the aim to achieve as high as possible  $f_{\rm T}$  and  $f_{\rm max}$ . Therefore, we developed a new fabrication process for GFETs, which is used in PAPER C-E, and is presented in this chapter together with the previous fabrication process used in PAPER A, B and F. For PAPER G a buried gate configuration of the detector was developed and is presented here. Furthermore, in this chapter, techniques for material quality and device characterization are explained.

### 3.1 GFET design and fabrication

The GFETs that have been reported in literature (Fig. 1.1) with high values of intrinsic and/or extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  have been fabricated utilising a fabrication process with self-aligned T-gate structures with the aim to reduce the ungated access area length and, simultaneously, reduce the gate resistance [49, 48, 50]. Additionally, most GFETs were fabricated on SiC since it has superior optical phonon energy compared to  $SiO_2$ [49, 48, 50]. However, the self-aligned technique does not necessary reduce  $L_{\rm a}$ . Some of the reported values are still in the range of  $\sim 100 \,\mathrm{nm}$  [49, 48], which is similar to that of the GFET design in this work (see description below). Also the charge carrier concentration in graphene on SiC can be larger than that of samples prepared on  $SiO_2$ due to charge transfer from the SiC substrate to graphene [100]. The large charge carrier concentration strongly degrades the saturation velocity according to Eq. 2.7 and entails reduction of  $f_{\rm T}$  and  $f_{\rm max}$ . Other fabrication techniques employ buried gates electrodes, followed by transfer of exfoliated hBN and exfoliated graphene [101]. The highest intrinsic  $f_{\rm T} = 427 \, {\rm GHz}$  has been reported for transferable nanowire gate stacks on silicon glass at 67 nm [51]. However, simultaneously, due to high parasitic resistances, these devices perform extremely poorly in terms of  $f_{\text{max}}$  of only 8 GHz at  $L_{g} = 46$  nm.

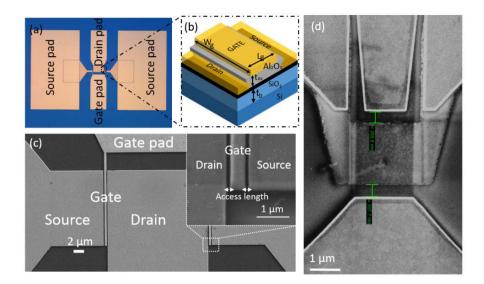

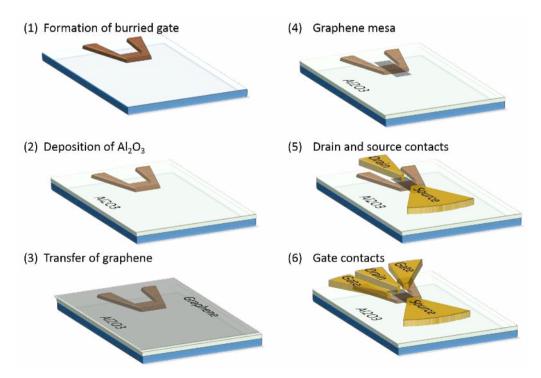

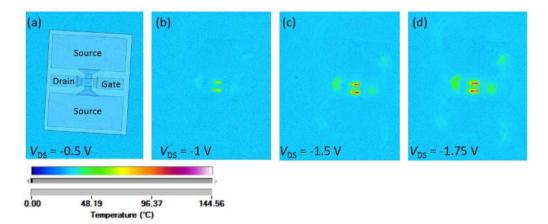

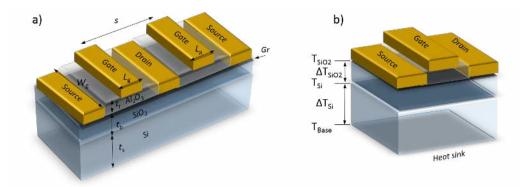

The design of the GFETs used in this work is shown in Fig. 3.1. Figure. 3.1(a) shows a micrograph of the top view of a double-finger GFET. The metal pads for probing the GFET constitute the largest part. Figure 3.1(b) shows a schematic magnification of the gate-stack structure. The important layout parameters are the gate length Lg, the gate width  $W_g$ , the top-oxide thickness  $t_{\text{ox}}$ , and the bottom gate thickness  $t_b$ . Figure 3.1(c) shows a SEM image of the GFET in PAPER C. In the inset the un-gated access length  $L_a = 0.1 \,\mu\text{m}$  between the gate and the source/drain contacts is indicated. Figure 3.1(d) shows a SEM image of the graphene channel of the terahertz detector fabricated in PAPER G. The fabrication steps of the GFETs in PAPER A-E are illustrated in Fig. 3.2 and a detailed recipe of the new fabrication process described below can be found in the

Figure 3.1: General two-finger gate layout of the GFETs used in this work. (a) The micrograph shows the top view of a GFET. (b) The schematic is a magnification of the gate-stack structure indicating the gate width  $W_{\rm g}$ , gate length  $L_{\rm g}$ , top-oxide thickness  $t_{\rm ox}$ , and substrate material. (c) SEM image of the GFET in PAPER C. (d) SEM image of the terahertz detector fabricated in PAPER G.

APPENDIX. For the development of the new fabrication process the previous process used in PAPER A, B and F was modified to achieve better high-frequency performance. This was achieved by using high quality CVD graphene grown on copper transferred onto the substrate using an transfer method assisted by hBN instead of polymethylmethacrylate (PMMA) [83]. The latter usually leaves polymer residuals on the graphene sheet. Secondly, by depositing a protective Al<sub>2</sub>O<sub>3</sub> layer as a first processing step after the graphene transfer instead of first patterning the graphene mesa, and thirdly, by using a thicker SiO<sub>2</sub> layer (1  $\mu$ m instead of 300 nm) which reduces the parasitic pad capacitances. As discussed in PAPER C, the new fabrication sequence resulted in cleaner interfaces, which allowed for realisation of extremely low specific width contact resistivity of  $\rho_{\rm C} \sim 90 \,\Omega\mu$ m.  $\rho_{\rm C}$  was measured by transfer-length method.

In all papers high bulk resistivity  $(10 \text{ k}\Omega \text{cm})$  Si substrate with 500  $\mu$ m (PAPER A-E) or 280  $\mu$ m (PAPER F) thickness was used, with the exception of PAPER A, where lithium niobate (LiNbO<sub>3</sub>) substrate was used. The seed layer and the protective Al<sub>2</sub>O<sub>3</sub> layers were formed by repeating deposition of 1 nm Al by e-beam evaporation and subsequent oxidation in air at 60 °C four times. The full oxide thickness was obtained by deposition of 15 nm Al<sub>2</sub>O<sub>3</sub> using atomic layer deposition in thermal mode at 300 °C. The mesa, the drain, source and gate contacts were defined by E-beam lithography. Buffered oxide etch (BOE:water=1:10) was used to remove the Al<sub>2</sub>O<sub>3</sub> layer in the areas intended for the the ohmic contacts and O<sub>2</sub> plasma etch was used to remove graphene in the mesa pattering step. The drain, source and gate metallisation was deposited by e-beam evaporation

Figure 3.2: Fabrication processes of the GFETs in this work. The previous fabrication process was used in PAPER A, B and F. The new fabrication process was used in PAPER C-E.

followed by lift-off. Fabrication of the receiver presented in PAPER F was not part of this work. In short, the amplifier GFETs and the mixer GFETs were first fabricated together onto the silicon substrate following the previous fabrication process, and, subsequently, the coplanar waveguide circuitry, including the band pass filters and matching networks, were formed around the GFETs. The SiO<sub>2</sub> thickness is 90 nm.

Figure 3.3 shows the fabrication steps for the GFET in PAPER G, which were the following. The buried gate was patterned by e-beam lithography followed by the deposition

of 2 nm of Ti and 20 nm of Au by e-beam evaporation and lift-off. Two versions of the buried gate were fabricated. One version with vertical sidewalls of the burried gate, and one with sloped sidewalls. Vertical sidewalls were obtained by standard e-beam evaporation of the gate metal and lift-off. Sloped sidewalls were obtained evaporating the gate metal onto the substrate while tilting the substrate  $20^{\circ}$  and rotating it. The deposition rate is 0.8 Å/s with 4 revolutions per second. Next, the gate oxide was deposited by atomic layer deposition of  $Al_2O_3$  in thermal mode at 300 °C with the final oxide thickness of 25 nm Fig. 3.3(2). After that, "Easy Transfer" graphene from Graphenea was transferred onto the  $Al_2O_3$  layer following the company's recommended transfer method from a sacrificial polymer layer onto the substrate [102]. Patterning of the graphene channel was conducted by e-beam lithography and  $O_2$  plasma etch (Fig. 3.3(4)). The parts of the bow-tie antenna which constitute the drain/source contacts and the contact pads were formed by e-beam lithography followed by e-beam evaporation of 2 nm Ti / 10 nm Pd / 150 nm Au and lift-off(Fig. 3.3(5)). In the final step, the gate contact pads were formed by e-beam lithography, followed by BOE etch to provide electrical contact to the buried gate. The gate contact metal was deposited by e-beam evaporation of 4 nm Ti and 270 nm Au followed by lift-off (Fig. 3.3(6)).

Figure 3.3: Fabrication process of the GFET in PAPER G. In contrast to the fabrication process of the GFETs in Fig. 3.2, the gate was formed first. This way the graphene is accessible for the near-field terahertz nanoscopy.

# 3.2 Synthesis of graphene and characterization of material quality

#### 3.2.1 Synthesis of graphene

Originally, graphene was obtained by mechanical exfoliation from graphite using adhesive tape [15]. Graphite consists of stacked layers of graphene that adhere to each other by van der Waals forces. Using adhesive tape and repeatedly folding and unfolding the tape, the graphene layers can be detached from each other, until only one layer of graphene remains.

Following the first mechanical exfoliation of graphene, other synthesis processes have been developed. Graphene can be grown by chemical vapour deposition (CVD) on a catalyst material (most commonly copper) [103]. Another technique is the formation of graphene by intercalation on a silicon carbide crystal (SiC). This is performed under ultrahigh vacuum and at high temperatures, which are sufficient to sublimate silicon from the surface and leave the carbon-rich surface layer to transform to graphene [104]. Furthermore, graphene can be obtained by liquid exfoliation from graphite powder in a solvent using ultrasonication or sheer forces applied by a mixer to separate the graphene sheets [105, 106]. The graphene quality in terms of mobility has been highest in mechanically exfoliated graphene because it had less defects and impurity residuals, and did not include grain boundaries. However, advances in the growing and transfer technology of CVD graphene has been improved so that CVD graphene encapsulated in hexagonal boron nitride (hBN) can reach mobilities up to  $10 \times 10^4 \,\mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$  at room temperature and, at cryogenic temperatures, similar mobilities as suspended graphene [83, 55]. At cryo-temperatures, suspended graphene reaches the theoretical intrinsic mobility limit of  $2 \times 10^5 \,\mathrm{cm^2 V^{-1} s^{-1}}$  [55]. On SiO<sub>2</sub> the mobility is approximately in the order of  $1 \times 10^4 \,\mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$ , limited by elastic scattering of the charge carriers by remote polar optical phonons of the substrate [107, 108]. Considering the combination of price for large-scale production and quality, the CVD graphene is the most promising. The CVD graphene can be grown at large scales and then be transferred onto arbitrary substrates. The bottleneck is the necessity to develop a clean transfer method that results in an ultra-clean and atomically flat graphene layer that does not exhibit wrinkles or holes.

#### 3.2.2 Characterisation of material quality

#### Raman spectroscopy

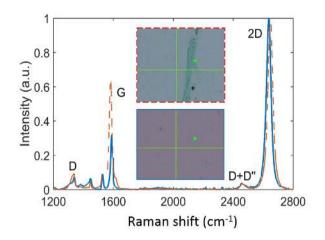

Raman spectroscopy is a fast and nondestructive characterisation tool that provides structural and electronic information about graphene sheets. Raman spectroscopy is often used after transferring graphene onto the substrate to identify the graphene quality. The shape, intensities and positions of the characteristic peaks in the Raman spectrum provide information about any structural damage, unwanted dopants or chemical modifications of the graphene [110]. Fig. 3.4 shows the Raman spectra of CVD graphene provided by Graphenea after transfer onto  $SiO_2$ . The Raman spectra are measured using a Horiba scientific spectrometer with a 638 nm laser. The characteristic G peak and 2D peak are

Figure 3.4: Raman spectra of graphene ("Easy Transfer" CVD graphene from Graphenea) at two different positions on the  $SiO_2$  substrate. The Raman spectra are measured on single layer graphene (solid line) and on folded multi-layer graphene (dashed line). The position of measurements are indicated on the inset images. Both spectra are exhibiting the characteristic G and 2D peaks, and the D and D' peaks, which appear when defects are present. The G peak can be larger because of higher charge carrier concentration [109].

present in the Raman spectrum. The 2D to G peak intensity ratio, and the position of the G peak is a strong function of the charge carrier concentration and can be utilized to estimate the residual charge carrier concentration [109]. The full width half maximum of the G-peak is related to the number of graphene layers [111]. Since defects are present, the D peak and D' peak appear in the spectrum. As disorder increases the intensity ratio of the D and G peak increases and all peaks widen. Additionally, the shape of the D peak also depends on the number of graphene layers [110]. Another peak that is related to interlayer coupling and that can be used to estimate the number of graphene layers is the C peak; however, this peak is not shown in Fig. 3.4.

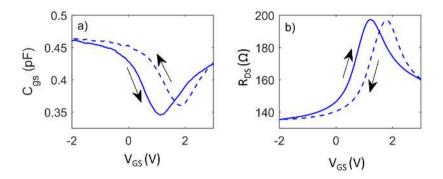

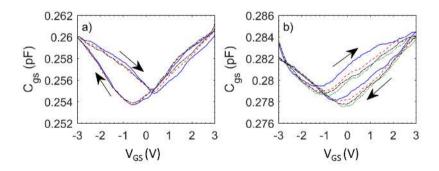

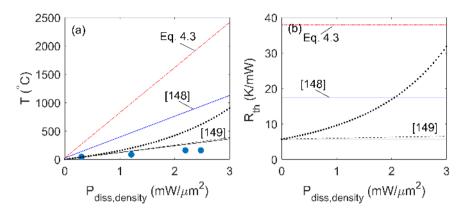

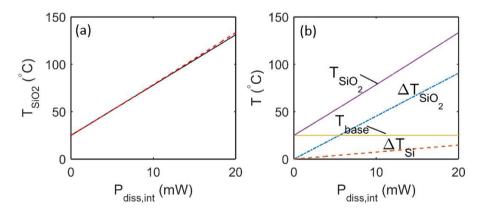

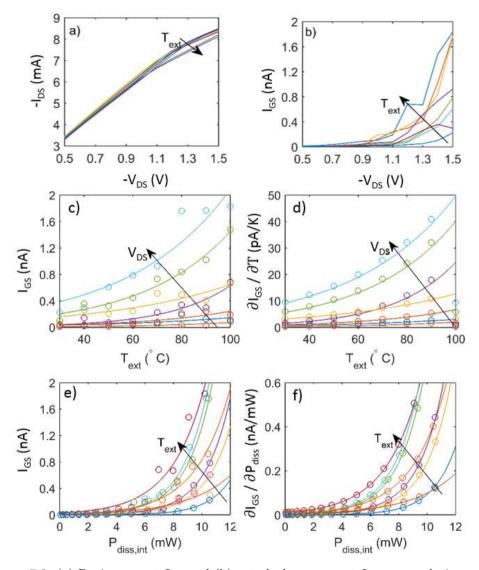

#### Characterisation of gate oxide