# Growth, Thermodynamics, and Electrical Properties of Silicon Nanowires<sup>†</sup>

V. Schmidt,\*,<sup>‡</sup> J. V. Wittemann,<sup>‡</sup> and U. Gösele<sup>‡,§,II</sup>

Max Planck Institute of Microstructure Physics, Halle, Germany, and School of Engineering, Duke University, Durham, North Carolina

Received April 7, 2009

# Contents

| 1.  | Introduction                                                       | 361 |

|-----|--------------------------------------------------------------------|-----|

| 2.  | Silicon Nanowire Synthesis Techniques                              | 363 |

| 2   | .1. High Temperature Chemical Vapor Deposition                     | 363 |

| 2   | .2. Low Temperature Chemical Vapor Deposition                      | 364 |

| 2   | .3. Supercritical-Fluid-Based and Solution-Based Growth Techniques | 365 |

| 2   | .4. Molecular Beam Epitaxy                                         | 366 |

| 2   | .5. Laser Ablation                                                 | 367 |

| 2   | .6. Silicon Monoxide Evaporation                                   | 367 |

| 3.  | Catalyst Materials                                                 | 368 |

| 3   | .1. Gold as Catalyst                                               | 368 |

| 3   | .2. Alternative Catalyst Materials                                 | 369 |

|     | 3.2.1. Type-A, Au-like Catalysts                                   | 370 |

|     | 3.2.2. Type-B, Low Si Solubility Catalysts                         | 371 |

|     | 3.2.3. Type-C, Silicide Forming Catalysts                          | 371 |

| 4.  | Crystallography                                                    | 372 |

| 5.  | Heterostructures                                                   | 373 |

| 6.  | Surface Induced Lowering of the Eutectic Temperature               | 375 |

| 7.  | Diameter Expansion of the Nanowire Base                            | 376 |

| 8.  | Surface Tension Criterion                                          | 378 |

| 9.  | Growth Velocity and Gibbs-Thomson Effect                           | 379 |

| 10. | Doping                                                             | 380 |

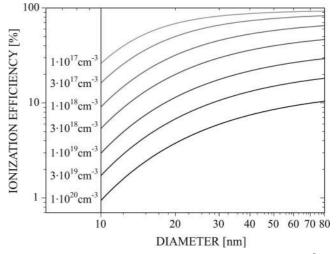

| 11. | Dopant Ionization                                                  | 381 |

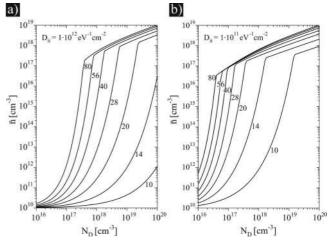

| 12. | Surface States and Charge Carriers                                 | 382 |

| 13. | Summary and Open Questions                                         | 385 |

| 14. | Acknowledgments                                                    | 386 |

| 15. | References                                                         | 386 |

|     |                                                                    |     |

# 1. Introduction

Research on silicon nanowires has developed rapidly in recent years. This can best be inferred from the sharply increasing number of publications in this field. In 2008, more than 700 articles on silicon nanowires were published, which is twice the number published in 2005. Because of this strong increase in research activities and output, the vast majority of publications on silicon nanowires are found to be younger than ten years. At first glance, one could therefore be tempted to assume that Si nanowire research is a very young research field. This, however, is not the case. Si nanowire research had a rather long incubation period before it became a

Deceased.

Volker Schmidt studied Physics at the Bayerische Julius-Maximilians-Universität Würzburg, Germany, and at the State University of New York at Buffalo. He received his Ph.D. from the Max Planck Institute of Microstructure Physics in Halle, Germany, working on growth and properties of silicon nanowires. Volker Schmidt also worked as a guest scientist at the IBM Zurich research laboratories in Rüschlikon, Switzerland, and at the Materials Science Department of Stanford University, CA.

Joerg V. Wittemann studied Physics at the Bayerische Julius-Maximilians-Universität Würzburg, Germany, and at the University at Albany—State University of New York, where he received a M.Sc. in 2007. Afterward, he joined the Max Planck Institute of Microstructure Physics as a Ph.D. student under the supervision of Prof. U. Gösele. He is currently working on fabrication and characterization of silicon nanowires.

fashionable subject, driven by potential applications in nanoelectronics and sensors.

The review, which to our knowledge is the first on silicon wires, dates back to the late 1950s.<sup>1</sup> Therein, Treuting and Arnold reported the successful synthesis of  $\langle 111 \rangle$  oriented Si whiskers. The term whisker was at that time the commonly used expression when reference was made to filamentary crystals. Nowadays, the term whisker has almost disappeared. Instead, the terms "wire" and "nanowire" have found widespread use. In this article, we will adopt this newer

<sup>\*</sup> To whom correspondence should be addressed. E-mail: vschmidt@mpi-halle.de.

<sup>&</sup>lt;sup>†</sup> This article is dedicated to the memory of Professor Ulrich Gösele.

<sup>\*</sup> MPI of Microstructure Physics.

<sup>&</sup>lt;sup>§</sup> Duke University.

Ulrich Gösele was Director of the Experimental Department II at the Max Planck Institute of Microsctructure Physics, Halle, Germany, Honorary Professor of Experimental Physics at Martin Luther University Halle-Wittenberg, Germany, as well as Adjunct Professor of Materials Science at Duke University's School of Engineering, Durham, North Carolina. While staying with the Max Planck Institute of Metal Physics, Stuttgart, Germany, he received his Ph.D. from the University of Stuttgart in 1975. Afterward, he worked as a researcher for Siemens (Munich, Germany), IBM (Yorktown Heights, New York), NTT (Japan), and a nuclear research center in South Africa. In 1985, he became Full Professor of Materials Science and, later on, J. B. Duke Professor of Materials at Duke University, Durham, NC. Since 1993, he was a Scientific Member of the Max Planck Society and Director at its Max Planck Institute of Microstructure Physics in Halle. Ulrich Gösele was a Fellow of the American Physical Society and Great Britain's Institute of Physics. He was a member of the German National Academy of Sciences and was on the board of the Materials Research Society in the USA. He passed away in November 2009.

terminology. Rodlike crystals with a diameter of less than 100 nm will be referred to as nanowires. In places where rodlike crystals of larger diameters are considered, the term wire will be used. The term wire will also be used in a generalized sense, i.e. when reference is to be made to both wires and nanowires.

Regarding silicon wire growth, it is remarkable to see how much was already known in the 1960s. The best example of this is the vapor-liquid-solid mechanism of Si wire growth proposed by Wagner and Ellis in their seminal article published in March 1964.<sup>2</sup> Till today, the vapor-liquid-solid (VLS) growth mechanism was the most prominent method for silicon wire synthesis. The VLS mechanism really represents the core of silicon wire research, though it does not only work for silicon but also for a much broader range of wire materials. The VLS mechanism can best be explained on the basis of Au catalyzed Si wire growth on silicon substrates by means of chemical vapor deposition (CVD) using a gaseous silicon precursor such as silane.

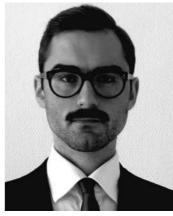

The Au-Si binary phase diagram possesses a characteristic peculiarity, namely that the melting point of the Au-Si alloy strongly depends on composition. A mixture of 19 atom % Si and 81 atom % Au already melts at 363 °C, which is about 700 K lower than the melting point of pure Au and more than 1000 K lower than the melting point of pure Si. Thus, heating Au in the presence of a sufficient amount of Si, considering e.g. a Au film on a Si substrate, to temperatures above 363 °C will result in the formation of liquid Au-Si alloy droplets as schematically depicted in Figure 1a. Exposing these Au-Si alloy droplets to a gaseous silicon precursor such as silane, SiH<sub>4</sub>, will cause precursor molecules to preferentially crack at the surface of these droplets, thereby supplying additional Si to the droplet. At equilibrium the phase diagram allows only for a limited amount of Si

Figure 1. (a) Schematics of the vapor-liquid-solid growth mechanism. (b) Scanning electron micrograph of epitaxially grown Si nanowires on Si  $\langle 111 \rangle$ . Transmission electron micrograph of the interface region between Si nanowire and substrate. Note the epitaxy and the curved shape of the nanowire flank. Parts b and c are reprinted from ref 3 with permission from Zeitschrift für Metallkunde, Carl Hanser Verlag, München.

dissolved in the Au-Si droplets. The additional supply of Si from the gas phase therefore forces the droplets to find a way of how to dispose of the excess Si. This is accomplished by crystallizing solid Si at the droplet-wire interface. A continuous supply of Si consequently leads to the growth of wires with a Au-Si droplet at their tip, as schematically indicated in Figure 1a.

The name vapor-liquid-solid (VLS) mechanism reflects the pathway of Si, which coming from the vapor phase diffuses through the liquid droplet and ends up as a solid Si wire. Related is the so-called vapor-solid-solid (VSS) mechanism, which describes cases where a solid catalyst particle instead of a liquid droplet is involved. An example of Au-catalyzed Si nanowires grown homoepitaxially on a  $\langle 111 \rangle$  substrate via the VLS-mechanism is shown in Figure 1b. These nanowires were grown at about 450 °C using silane as precursor.<sup>3</sup> The transmission electron micrograph in Figure 1c proves the epitaxial relation between nanowire and substrate. What should also be noted in Figure 1c is the curved shape of the nanowire flank; an aspect that will be discussed in detail later on in section 7. The most remarkable feature of the VLS growth mechanism, however, is its universality. VLS growth works well for a multitude of catalyst and wire materials and, regarding Si wire growth, over a size range of at least 5 orders of magnitude; from wire diameters of just a few nanometers up to several hundred micrometers.

The VLS mechanism has numerous direct and indirect implications for Si wire growth. Consequently, a large part of this review, which is an extended version of a previous article,4 focuses on the limitations and implications of the VLS mechanism. This concerns experimental issues such as the choice of growth method (section 2) and catalyst material (section 3), the crystallography of the wires (section 4), and the synthesis of heterostructures (section 5), as well as theoretical issues such as the depression of the eutectic temperature (section 6), the expansion of the wire base (section 7), the surface tension criterion (section 8), and the Gibbs-Thomson effect (section 9). The last part of this article deals with the electrical properties of silicon nanowires: from nanowire doping (section 10) and the question of dopant ionization (section 11) to the influence of surface states on the effective charge carrier density (section 12).

# 2. Silicon Nanowire Synthesis Techniques

Different techniques for silicon nanowire synthesis were developed in the past, with chemical vapor deposition (CVD) being just one of them. Which growth method is suited best depends on the application in mind as well as on the intrinsic capabilities and limitations of the technique in question. In this section, we therefore want to take a closer look at the different growth techniques and their particular advantages and disadvantages.

The different growth techniques mainly differ in the way silicon is supplied. There are two possibilities, either wire growth is fed directly by elemental silicon or silicon is provided as a silicon compound. It is clear that in the latter case a chemical reaction has to take place at the catalyst particle to initiate wire growth. Silicon itself is very sensitive to oxidation. Depending on whether oxygen-rich or nominally oxygen-free conditions are applied, growth results differ strongly. It therefore turns out to be convenient to distinguish between the use of oxygen-rich and oxygen-free Si precursors. In the following, the term chemical vapor deposition will only be applied to the use of oxygen-free precursors. Oxygen-rich precursors, such as, for example, SiO, shall be excluded by definition and dealt with separately. Of course, one could argue that using SiO as precursor also represents some sort of chemical vapor deposition; nevertheless, for practical reasons, we will make this distinction here.

# 2.1. High Temperature Chemical Vapor Deposition

In chemical vapor deposition (CVD), as defined above, the necessary silicon for wire growth is provided by an oxygen-free precursor. The most frequently used precursors are silane, SiH<sub>4</sub>, disilane, Si<sub>2</sub>H<sub>6</sub>, dichlorosilane (silicon dichloride), SiH<sub>2</sub> Cl<sub>2</sub>, and tetrachlorosilane (silicon tetrachloride), SiCl<sub>4</sub>. Replacing hydrogen atoms by chlorine mainly comes with two effects. The first, almost trivial, effect is that the use of a chlorinated silane precursor in the presence of hydrogen will lead to the creation of hydrochloric acid during nanowire processing; and hydrochloric acid usually causes some desirable or undesirable etching of the substrate, the nanowires, and the equipment. The second is related to the fact that chlorinated silanes are, generally speaking, chemically more stable than their nonchlorinated counterparts.<sup>5</sup> Consequently, higher temperatures need to be applied to thermally crack the precursor. For tetrachlorosilane, SiCl<sub>4</sub>, growth temperatures typically range from about 800  $^{\circ}\mathrm{C}^{6-9}$ to well beyond 1000 °C, 10,11 compared to temperatures of about 400-600 °C, typical for Si wires grown in the presence of silane.<sup>3,12,13</sup> In view of this difference in process temperature, which, for example, affects the choice of the catalyst material, the discussion on chemical vapor deposition is split into a high temperature and a low temperature part; with high temperature being defined as covering temperatures higher than about 700 °C.

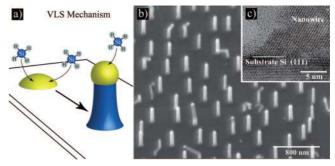

High temperature CVD Si wire growth experiments are often performed in tubular hot wall reactors.<sup>7–9,11</sup> As schematically depicted in Figure 2a, a gas flow—typically hydrogen or a hydrogen/inert gas mixture—is directed through an externally heated quartz tube held at about atmospheric pressure. Prior to entering the reactor, a part of the gas is led through a bubbler filled with SiCl<sub>4</sub> (SiCl<sub>4</sub> is liquid at room temperature and atmospheric pressure), thereby supplying SiCl<sub>4</sub> to the reactor. If a Si sample, onto

**Figure 2.** (a) Schematic setup of high temperature CVD. (b) Tilted scanning electron micrograph of a Cu-catalyzed Si wire array. The scale bar in the inset is  $10 \,\mu$ m. Part b was reprinted with permission from ref 7. Copyright 2007 American Institute of Physics.

which some amount of the catalyst metal has been deposited beforehand, is placed in the hot zone of the reactor, silicon wires will commence growing. An excellent example of what can be achieved this way can be seen in Figure 2b, which shows a scanning electron microscope (SEM) image reprinted from the work of Kayes et al.<sup>7</sup> The almost optimal arrangement of the homoepitaxially grown, Cu-catalyzed Si wires, based on an appropriate arrangement of the catalyst by lithography, is striking. There are reports that homoepitaxial growth of Si wires on Si substrates is facilitated by the use of SiCl<sub>4</sub> if used in combination with H<sub>2</sub>,<sup>8</sup> as the developing HCl gas can etch away an unwanted oxide coverage of the substrate.

Historically, high temperature CVD via SiCl<sub>4</sub> was preceded by experiments using a closed reaction vessel instead of a flow reactor. Wagner et al.<sup>14</sup> and Greiner et al.,<sup>15</sup> for instance, obtained their early results by using evacuated and sealed quartz ampules into which iodine was placed together with silicon and the catalyst material. Upon heating, iodine reacts with silicon to form gaseous silicon iodide products, which then serve as a locally produced CVD precursor. Silicon wire growth takes place at the colder parts of the quartz ampule. This version of high temperature CVD, mentioned here for the sake of completeness, is attractive for its technical simplicity and low cost—assuming an apparatus for sealing evacuated quartz ampules is at hand.

Like most thermally activated processes, also Si wire growth using Au as catalyst and SiCl<sub>4</sub> as precursor shows an Arrhenius-type exponential dependence on process temperature ( $\propto \exp(-E_a/kT)$ ), with  $E_a$  being the activation energy and kT having its usual meaning. The data of Wagner et al.<sup>16</sup> indicate an activation energy  $E_{\rm a}$  of about 32  $\pm$  1 kcal/ mol (1.38  $\pm$  0.06 eV), which is slightly smaller than the activation energy of 37 kcal/mol obtained by Theuerer<sup>17</sup> for Si layer deposition using SiCl<sub>4</sub>. Due to the exponential temperature dependence of the Si wire growth velocity and the high temperatures applied, growth velocities can be quite substantial. Often wire growth velocities on the order of  $\mu$ m/min<sup>7,10,18</sup> or even  $\mu$ m/s<sup>11</sup> are observed. Although this is not of major concern considering the growth of Si wires with micrometer lengths, such high growth velocities represent a restriction for the controllability if synthesis is aimed at Si nanowires of submicrometer lengths.

Another effect of the elevated temperatures is related to the diffusion of the catalyst metal. It is generally known that metal clusters, islands, or droplets on a surface tend to agglomerate; a phenomenon usually referred to as Ostwald ripening.<sup>19–23</sup> Considering the growth of Si wires via the VLS mechanism, Ostwald ripening causes the larger catalyst droplets to grow (ripen) at the expense of the smaller ones. The speed at which this ripening proceeds depends on the rate at which the different catalyst droplets can exchange material with each other. That means, for wire growth on a substrate, that ripening mainly depends on surface diffusion, which can be expected to be faster at higher temperatures. As a consequence of the Ostwald ripening of the catalyst droplets, it becomes exceedingly more difficult to grow nanowires with well-defined diameters at elevated temperatures-simply because the droplet size does not stay constant during processing. This has been reported, for example, by Kayes et al.,<sup>7</sup> who deposited a regular array of Au-dots on a bare Si substrate. Upon heating, the droplets agglomerated, thereby destroying the regularity of the arrangement. To prevent/minimize droplet agglomeration, Kayes et al.<sup>7</sup> had to deposit an additional SiO<sub>2</sub> layer, serving as a diffusion barrier for the catalyst material. Not only does surface diffusion, however, affect the initial catalyst size, but also growth itself might be affected, as catalyst material can diffuse to neighboring wires.<sup>24,25</sup> In view of the problems related to catalyst diffusion, high temperature CVD seems to be more suited for the growth of microscopic Si wires rather than nanowires; though high temperature CVD growth of nanowires with diameters of about 40 nm has nevertheless been demonstrated.8

The main advantage of high temperature CVD consists in the much broader choice of possible VLS catalyst materials. Au and Cu<sup>7,16</sup> yield excellent results at temperatures above 850 °C (see Figure 2b). At even higher temperatures, also Pt and Ni seem to be a good choice.<sup>16</sup> A more thorough discussion on the choice of catalyst materials will be given in section 3. Independent of the catalyst material used, the main crystallographic growth direction of these nanowires appears to be the  $\langle 111 \rangle$  direction,<sup>8,16,17</sup> probably because of the large diameter of the wires.<sup>26,27</sup> The corresponding wires are typically single crystalline and free of crystallographic defects. Wagner et al.,<sup>16</sup> however, point out that also  $\langle 112 \rangle$ orientated wires, showing a twin defect parallel to the wire axis can be found.

A doping of the growing wire directly from the gas phase is possible, even at high temperatures. Givargizov reports the use of AsCl<sub>3</sub><sup>10,28</sup> and PCl<sub>3</sub><sup>10</sup> as vapor phase dopants. Interestingly, the introduction of the dopant precursor does influence the wire morphology. Givargizov points out that the periodic instability of the wires (a periodic variation of the wire diameter observed at high temperatures and pressures) disappears once AsCl<sub>3</sub> is added to the gas mixture,<sup>28</sup> presumably because AsCl<sub>3</sub> changed the surface tension configuration of the wire and/or the catalyst droplet.

### 2.2. Low Temperature Chemical Vapor Deposition

Low temperature chemical vapor deposition (CVD) shall comprise the growth temperatures lower than 700 °C. The typical precursors for low temperature CVD are silane (SiH<sub>4</sub>) and, though less frequently, disilane (Si<sub>2</sub>H<sub>6</sub>). In contrast to tetrachlorosilane, silane already decomposes at about 350 °C so that the temperature range from the Au–Si eutectic at 363–700 °C is fully covered. Another noteworthy difference to SiCl<sub>4</sub> is that both silane and disilane are selfigniting gases that are potentially explosive if brought into contact with air. Thus, working with silane or disilane requires great care to prevent issues with machinery or personnel.

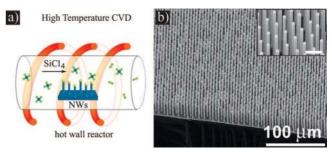

The most frequently used catalyst material for VLS Si nanowire growth is Au. Using Au and silane, homoepitaxial

**Figure 3.** (a) Schematic of a low temperature chemical vapor deposition reactor. (b) Al-catalyzed Si nanowires on Si $\langle 111 \rangle$  grown at about 430 °C. Part b is reprinted from ref 95. Copyright 2006 Macmillan Publishers LTD: Nature Nanotechnology.

growth of Si wires or nanowires can be achieved without much difficulty (see Figure 1b), provided that the native oxide, naturally covering silicon substrates, is removed prior to the Au deposition. Wire diameters from a few nanometers up to several micrometers can be realized. The dominant orientation of wires with diameters larger than about 50 nm orientation is  $\langle 111 \rangle$ .<sup>26,27</sup> More details on the crystallography are given in section 4.

Often dedicated, low pressure, cold wall reactors are used, as schematically shown in Figure 3a. For the use of Au as catalyst, high-vacuum equipment (base pressure around  $10^{-6}$  mbar) is sufficient for growing nanowires. This is, however, not the case when more sensitive catalyst materials are used. Aluminum, for instance, is very sensitive to oxidation, so that the use of an ultrahigh-vacuum reactor with a base pressure lower than about  $10^{-9}$  mbar is recommended. Yet, if oxidation of Al is prevented, excellent results can be achieved with Al as catalyst; see, for example, Figure 3b.

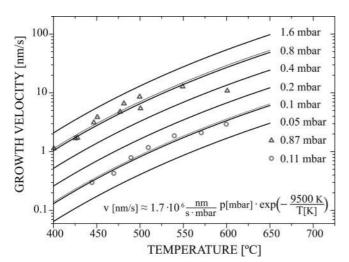

Typical silane partial pressures range from 0.1 mbar to 1 mbar,<sup>12,27,29</sup> which results in growth velocities on the order of nanometers per second. Concerning the pressure dependence, the data published by Lew et al.<sup>12</sup> indicate that the growth velocity increases approximately linearly with silane partial pressure. Nanowire growth velocities related to the use of silane as precursor show an exponential dependence on inverse temperature ( $\propto \exp(-E_a/kT)$ ). From observations at growth temperatures of 450-600 °C, Schmid et al.<sup>29</sup> deduced an activation energy,  $E_a$ , of  $19 \pm 1.5$  kcal/mol (0.82  $\pm$  0.07 eV). Lew et al.<sup>12</sup> investigated nanowire growth at a similar temperature range and reported an activation energy of 22 kcal/mol. However, their data seem to indicate a somewhat smaller value, closer to the 19 kcal/mol of Schmid et al.<sup>29</sup> From the data of Bootsma and Gassen,<sup>30</sup> who studied Si nanowires growth at temperatures of 600-800 °C, an activation energy of  $11.1 \pm 0.4$  kcal/mol (0.48  $\pm$  0.02 eV) can be deduced.

Combining the pressure and temperature dependencies,<sup>12,29</sup> one can obtain the following estimate for the temperature and pressure dependence of the growth velocity of Aucatalyzed nanowires:

$$v \approx 1.7 \times 10^6 \frac{\text{nm}}{\text{s mbar}} p \exp\left(\frac{-9500 \text{ K}}{T}\right)$$

(1)

with p being the silane partial pressure in millibar; see Figure 4. This formula serves only as a crude estimate for practical use. The accuracy is presumably not much better than a factor of 2. One should furthermore keep in mind that the growth velocity also depends on the nanowire diameter (see section 9) and other parameters.

Si nanowires obtained by using Au and silane are usually only slightly tapered, which indicates that radial growth is

**Figure 4.** Approximate Si nanowire growth velocity (using Au as a catalyst) as a function of pressure and temperature using data from Lew et al.<sup>12</sup> (triangles) and Schmid et al.<sup>29</sup> (circles).

slow compared to axial growth. According to the data by Schmid et al.,<sup>29</sup> radial growth rates are about 2 orders of magnitude smaller than axial growth rates. The activation energy for radial growth is found to be larger than that for axial growth. Schmid et al.<sup>29</sup> determined a value of  $29 \pm 3$  kcal/mol (1.26 eV). This value is still slightly smaller than the activation energy of 35.4 kcal/mol derived from silicon thin film deposition experiments using silane.<sup>31,32</sup> The fact that the activation energy of radial growth is still smaller than the nominal activation energy for Si thin film deposition could possibly be explained by the catalytic effect of a Au contamination of the nanowire surface.<sup>24</sup>

Another attractive precursor for low temperature CVD is disilane, Si<sub>2</sub>H<sub>6</sub>. Disilane is more reactive than monosilane, SiH<sub>4</sub>. Silicon thin film deposition experiments gave an activation energy of 28.4 kcal/mol (1.23 eV) compared to 35.4 kcal/mol (1.53 eV) for silane.<sup>31,32</sup> The higher reactivity of disilane compared to silane represents its main advantage, as it allows for Si wire growth at much lower pressures compared to that for silane. The lower pressures are particularly important for the in situ observation of Si nanowire growth, for example, in a transmission electron microscope (TEM).<sup>24,33-35</sup> Kodambaka et al.<sup>36</sup> investigated the diameter, temperature, and pressure dependence of the nanowire growth velocity. They grew Au-catalyzed nanowire at disilane partial pressures as low as  $2 \times 10^{-8}$  Torr, corresponding to a growth velocity of about 1 nm/min. From the temperature dependence, they deduced an activation energy of  $12.2 \pm 0.5$  kcal/mol  $(0.53 \pm 0.02 \text{ eV})$ .<sup>36</sup>

In summary, one should keep in mind that the activation energies for Au-catalyzed Si nanowire growth are about half as large as those for Si thin film growth: 19 kcal/mol vs 35 kcal/mol for silane and 12 kcal/mol vs 28 kcal/mol for disilane. This reduction by about a factor of 2 is what makes the Au droplet a catalyst droplet.

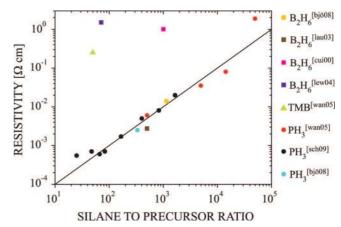

Doping of silicon nanowires directly from the vapor phase is also possible for low temperature CVD. Often phosphine, PH<sub>3</sub>, or diborane,  $B_2H_6$ , is used to that end. Due to the crucial importance of a proper doping for the electrical properties, doping will be discussed in detail in section 10.

One subclass of low temperature CVD that requires mentioning here is plasma enhanced CVD (PECVD).<sup>37–40</sup> By means of a plasma in the nanowire growth reactor, the silicon precursor, silane in most cases, is partially precracked.

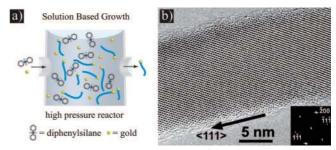

**Figure 5.** (a) Schematic setup for solution-based growth of Si nanowires. (b) Transmission electron micrograph of a Si nanowire grown from solution. Part b is reprinted with permission from Tuan et al.<sup>54</sup> Copyright 2008 American Chemical Society.

Such a precracking facilitates and enhances the supply of Si to the catalyst droplet. PECVD turns out to be a successful method for the low temperature synthesis of Ga- or Incatalyzed Si nanowires.<sup>37–40</sup>

The advantages of low temperature CVD are that nanowires with a large variety of diameters and lengths can be grown epitaxially on Si substrates. With the lengths of the wires being essentially proportional to the process time, they can be easily adjusted. Nanowire growth at predefined positions on the substrate is possible.<sup>29,41</sup> Furthermore, the electrical properties of the nanowires can be tuned directly by doping from the gas phase,<sup>29,42,43</sup> allowing also for modulated doping profiles.<sup>44</sup> One of the major problems of epitaxially grown Si nanowires is that they exhibit a certain variation of the growth direction, especially for diameters smaller than about 50 nm.<sup>27</sup> A related, ubiquitous problem is that a certain percentage of the nanowires tends to change their growth direction during growth; as a result, they show a kink (see Figure 1b).<sup>29,45,46</sup> This kinking problem, however, can be circumvented by growing the nanowires inside a template such as anodic aluminum oxide (AAO).<sup>47-49</sup> The template forces the nanowire to grow straight along the pore direction. This approach also leads to epitaxial (100) oriented nanowires, an orientation usually not favored by free-standing nanowires.49

# 2.3. Supercritical-Fluid-Based and Solution-Based Growth Techniques

Approaches similar to chemical vapor deposition are the so-called supercritical-fluid-based and solution-based growth techniques, developed in the group of Korgel.<sup>50</sup> In their original design, diphenylsilane,  $SiH_2(C_6H_5)_2$ , was used as Si precursor, which was mixed with hexane and sterically stabilized gold nanoparticles in a high pressure reactor. High pressures of 200–270 bar and a temperature of 500 °C were applied to the reaction vessel. Under these conditions, hexane becomes supercritical, which is why this method is referred to as being supercritical-fluid-based.

The synthesis is often performed in a way that a flow reactor<sup>51,52</sup> such as that sketched in Figure 5a is used instead of a closed reaction vessel. In this case, gold colloid particles together with a well-defined amount of the Si precursor, e.g. diphenylsilane, are fed into the solution as dispersions and transferred into the heated and pressurized reactor, where the nanowire synthesis takes place. The fact that nanowire synthesis can be performed in a continuous process instead of a batch process is one of the inherent decisive advantages of this method. Furthermore, the variability with respect to the choice of the precursor offers an additional degree of

freedom for optimization. Lee et al.,<sup>53</sup> for example, reported that the results using monophenylsilane,  $SiC_6H_8$ , and diphenylsilane as precursor differ in that the use of monophenylsilane leads to a higher product yield and additionally to a smaller amount of carbonaceous byproduct as compared to using diphenylsilane.

Using the method described above, Si nanowire growth is assumed to proceed via the supercritical-fluid–liquid–solid (SFLS) growth mechanism, the equivalent to the vapor–liquid–solid (VLS) growth mode explained before. As in VLS nanowire growth, nanowire diameters can be adjusted by the size of the metal nanoparticles, serving as catalysts. The fabrication of single crystalline nanowires with diameters as low as 5 nm and lengths of several micrometers has been demonstrated.<sup>52</sup> A high resolution transmission electron micrograph of a Au-catalyzed silicon nanowire grown via the SFLS mechanism using monophenylsilane as precursor<sup>54</sup> is reprinted in Figure 5b. Please note the perfect crystallinity of the nanowire.

Having the vapor–solid–solid (VSS) mechanism in mind, one would expect that Si nanowire growth in supercritical fluid can also be mediated by a solid catalyst particle; and, indeed, this is the case. Growth of Cu-, Ni-, and Co-catalyzed Si nanowires performed at temperatures well below the melting point of the corresponding metal-Si alloy has been demonstrated.<sup>55,56</sup>

Another very attractive approach for the high yield production of nanowires is solution-based nanowire growth, a good example of which has been published very recently. Heitsch et al.<sup>57</sup> demonstrated the Au- and Bi-catalyzed growth of silicon nanowires in solution at atmospheric pressure. Trisilane, Si<sub>3</sub>H<sub>8</sub>, which is even more reactive than disilane, is used as silicon precursor. The growth reaction takes place in a vessel filled with a long-chain, low-vapor-pressure hydrocarbon. Nanowire synthesis temperatures higher than the eutectic temperatures of Au–Si or Bi–Si were applied, so that, analogously to the VLS mechanism, a solution-liquid–solid mechanism can be assumed.<sup>57</sup> Using the above-described method, Heitsch et al. demonstrated the synthesis of micrometer long, crystalline nanowires with diameters of about 25 nm.<sup>57</sup>

The main advantages of this method are that thin nanowires of good crystalline quality can be synthesized in large amounts using comparably simple equipment. Compared to other nanowire synthesis methods, the yield is excellent. The only disadvantage is that a controlled, in-place, epitaxial growth can hardly be realized.

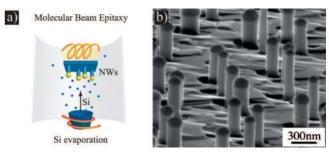

# 2.4. Molecular Beam Epitaxy

A further Si nanowire growth technique is molecular beam epitaxy (MBE).<sup>58–62</sup> Here, elemental Si, instead of a chemical Si compound, serves as the source for Si nanowire growth. Si nanowire growth is achieved by evaporating Si onto a catalyst covered substrate, typically Si $\langle 111 \rangle$ , as illustrated in Figure 6a. To prevent oxidation or contamination of the substrate or the nanowires, an ultrahigh vacuum (UHV) system with a base pressure in the  $10^{-10}$  mbar range is typically used for MBE. To maintain such low pressures even during nanowire processing, parts of the system are often additionally cooled with liquid nitrogen.

Preceding Si evaporation, Au is deposited onto the substrate. Annealing the substrate at temperatures above the Au–Si eutectic temperature causes the Au film to break up. Au mixes with Si from the substrate, and Au–Si alloy

Figure 6. (a) Schematics of MBE Si nanowire growth. (b) Scanning electron micrograph of Au-catalyzed Si nanowires on Si $\langle 111 \rangle$ . Part b is reprinted from ref 59 with permission from Elsevier.

droplets form, which then act as catalysts for the subsequent VLS Si nanowire growth. Since MBE does use elemental Si instead of a chemical compound as Si source, the role of the Au catalyst merely consists of facilitating Si crystallization. From a chemical point of view, one could argue that the catalyst droplets are not real catalysts anymore, as there is no chemical reaction involved. However, the fact that the Si nanowires grow faster than the substrate by about a factor of 2—a fact that is not obvious in the first place—indicates that the catalyst droplets do have an effect on Si crystallization.

Typically, Si nanowires are grown at substrate temperatures of 500–700 °C.<sup>58,60,63,64</sup> The necessary Si evaporated onto the substrate diffuses on the substrate surface until it either crystallizes directly or finds a Au catalyst droplet. MBE growth of Si nanowires therefore strongly relies on Si surface diffusion, which is the main reason why growth temperatures higher than 500 °C are used. Yet, at these temperatures, it is difficult to realize small Au–Si droplet sizes (due to Ostwald ripening), and the diameters of the nanowires therefore usually exceed 40 nm. Another potential cause for the fact that only nanowires with diameters larger than about 40 nm can be obtained<sup>58,62</sup> is the Gibbs–Thomson effect, as discussed in section 9.

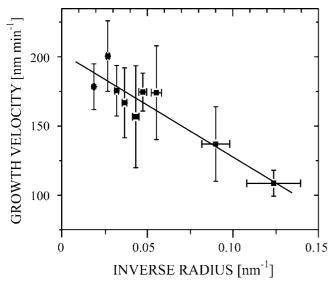

The fact that Si nanowire growth depends on Si surface diffusion has direct implications for the nanowire growth velocity. As surface diffusion is a rather slow process, one can expect the nanowire growth velocities to be comparably small; typically growth velocities of 1-10 nm/min are realized.<sup>60,63</sup> The second implication concerns the diameter dependence of the growth velocity. If the areal density of Si adatoms diffusing toward the catalyst droplet is taken to be constant, then the amount of Si per unit time reaching the droplet is proportional to the circumference of the nanowire. Moreover, at a given Si supply rate, the growth velocity has to be inversely proportional to the nanowire cross-sectional area. Combining both, it becomes immediately clear the growth velocity should be inversely proportional to the nanowire diameter.

In general, Si nanowires grown by MBE are single crystalline and  $\langle 111 \rangle$  oriented. They can be grown homoepitaxially on Si without much problem. Nanowire growth at predefined positions on the substrate is possible.<sup>61</sup> The advantages of MBE are clearly that the fluxes can be accurately controlled. A precise control of the incoming particle fluxes is particularly important for a doping of the nanowires. When the MBE system is equipped with evaporation sources for Si dopants such as B or Sb, Si nanowires with well controlled doping profiles can be realized.<sup>65</sup> If additional evaporation sources, for example, for Ge, exist, also axial nanowire heterostructures can be achieved by simply switching sources.<sup>59</sup>

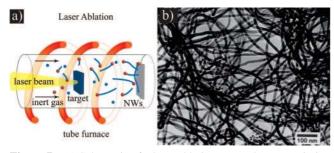

**Figure 7.** (a) Schematic of a laser ablation setup. (b) Transmission electron micrograph of Si nanowires grown by laser ablation. Part b is reprinted with permission from ref 235. Copyright 1999 American Institute of Physics.

The main disadvantages of Si nanowire synthesis via MBE are the considerable Si film growth on the substrate and the limited flexibility concerning nanowire diameters and aspect ratios; see Figure 6b. The rather limited aspect ratios are due to the minute growth velocity of just a few nanometers per minute.

# 2.5. Laser Ablation

Silicon nanowire growth via laser ablation differs in many respects from the nanowire growth techniques discussed so far. The two major differences are that (A), unlike growth via CVD or MBE, the catalyst material is coablated together with Si and (B) silicon nanowire growth does at least partially take place already in the vapor phase.

This is illustrated in Figure 7a. Typically, experiments are performed in a tube furnace into which the laser ablation target is placed. Morales and Lieber,<sup>66</sup> who pioneered this nanowire synthesis method, used a mixed Si-Fe target containing about 90% Si and 10% Fe. They heated the tube furnace to a temperature of 1200 °C, which is close to the minimum temperature required for Fe-catalyzed VLS Si nanowire growth. A constant Ar flow of 500 sccm was directed through the furnace, held at a pressure of 500 Torr. Under these conditions, they ablated Fe and Si from the laser target by shooting at it with a pulsed, frequency doubled Nd:YAG laser (wavelength 532 nm).<sup>66</sup> The ablated material collides with inert gas molecules and condenses in the gas phase, resulting in Fe-Si nanodroplets, which act as seeds for VLS Si nanowire growth. Zhang et al.<sup>67</sup> reported nanowire growth velocities on the order of micrometers per minute. The nanowires are harvested at the downstream end of the tube. The thus obtained Si nanowires had a crystalline core of less than 10 nm in diameter and were covered by an amorphous shell of 5 nm thickness, with the preferential growth direction being  $\langle 111 \rangle$ .<sup>66</sup>

Similar experiments were performed by other groups,<sup>67–69</sup> and a typical example of Si nanowires obtained by laser ablation is shown in Figure 7b. Peng et al.<sup>69</sup> investigated the influence of temperature, Zhang et al.<sup>70</sup> the influence of ambient gas, and Zhou et al.<sup>71</sup> the crystallography of the nanowires. As an alternative to Fe, also Ni,<sup>72</sup> Pr,<sup>73</sup> and Ru<sup>73</sup> were successfully tested as catalyst metals. Most interestingly, also the addition of SiO<sub>2</sub> to the laser ablation target served the purpose well.<sup>74,75</sup> What is remarkable about this oxide-assisted growth<sup>76</sup> is that SiO<sub>2</sub> containing targets clearly increased the Si nanowire yield compared to pure silicon targets or mixed silicon—metal targets.<sup>72</sup> If growth is carried out with an SiO<sub>2</sub> containing target, the preferential growth directions are  $\langle 112 \rangle$  and  $\langle 110 \rangle$ ,<sup>73,76,77</sup> but Zhang et al.<sup>76</sup> also report to have found pentagon-shaped,  $\langle 100 \rangle$  oriented Si

**Figure 8.** (a) Schematic of a setup of nanowire growth via SiO evaporation. (b) Transmission electron micrograph of a thick silicon nanowire with its crystalline silicon core and the thick amorphous oxide shell. Part b is reprinted from ref 83. Reproduced with permission of The Electrochemical Society.

nanowires. This is interesting, because thin Si nanowires with a regular, pentagon-shaped cross section have been proposed by theory to be energetically favorable structures.<sup>78</sup> Unfortunately, the experimentally observed pentagon-shaped nanowires do not appear to be regularly pentagon-shaped but rather square-shaped with one corner diagonally cut off.<sup>79</sup>

The advantages of laser ablation as a Si nanowire growth technique are mainly technical simplicity and versatility: technical simplicity, because there is no need for sophisticated gas installations; versatility, because the composition of the nanowires can be varied by simply changing the composition of the laser ablation target. Tang et al.,<sup>80</sup> for example, produced phosphorus doped Si nanowires by means of laser ablation. By combining silane CVD with laser ablation, Cui et al.<sup>81</sup> managed to synthesize p- and n-doped Si nanowires. Another advantage is that due to the high temperatures generated, also nongold catalyst materials such as Fe can be used. The main disadvantage of laser ablation is that it is not the right method for an in-place epitaxial growth of silicon nanowires.

# 2.6. Silicon Monoxide Evaporation

A cost-effective method to produce Si nanowires is silicon monoxide, SiO, evaporation. For this, a simple tube furnace connected to an inert gas supply can be used, as indicated in Figure 8a. For the successful nanowire synthesis, it is important that the tube furnace exhibits a temperature gradient and that the inert gas flows from the hotter to the colder part of the furnace. Some amount of SiO is then placed in the hotter zone, where it evaporates. The evaporated SiO is carried away by the gas stream to the cooler end of the tube, where it undergoes a disproportionation reaction into Si and SiO<sub>2</sub>, thereby forming the nanowires.<sup>82</sup> Due to the disproportionation reaction, the Si nanowires are covered by a thick  $SiO_x$  shell (see Figure 8b), with x having a value between 1.5 and 2.82 Another implication of the disproportionation reaction is that the diameter ratio between crystalline core and amorphous shell remains approximately constant.<sup>83</sup> Typical growth parameters involve pressures in the 100 Torr range, flow rates of 50 sccm of inert gas or an inert gas hydrogen mixture, temperatures of 1100-1350 °C for SiO evaporation, and temperatures of 900-1000 °C for Si nanowire growth.83-86

With SiO evaporation, two different growth modes are possible: growth with and without metal catalyst. Growth without catalyst<sup>82,85–87</sup> works via the aforementioned oxide assisted growth mode and presumably involves a liquid SiO<sub>x</sub> phase at the nanowire tip.<sup>76</sup> For this mode,  $\langle 111 \rangle$  and  $\langle 112 \rangle$  growth directions have been reported. Metal catalyzed growth

via the VLS mechanism has been demonstrated for Au.<sup>83,84</sup> In contrast to the normal VLS mechanism, however, the interaction between the droplet and the nanowire is far more complex, because not only the growth of the crystalline Si core but also the growth of the SiO<sub>x</sub> shell has to be considered. Therefore, it is not too astonishing that this more complex growth mechanism also leads to more complex phenomena, such as the periodic instability observed by Kolb et al.<sup>84</sup> They found that Au-catalyzed Si–SiO<sub>x</sub> core–shell nanowires exhibit nicely regular diameter oscillations with the oscillations of core and shell being slightly phase shifted with respect to each other.

The main disadvantage of Si nanowire growth via SiO evaporation is clearly its lack of controllability of nanowire diameters and lengths. Also, a controlled doping of the nanowires seems difficult. Another main drawback is that epitaxial growth on Si substrates is impossible, as the substrate would oxidize rapidly under the prevailing oxygenrich conditions. The main advantage is clearly its technical simplicity, as a tube furnace is the only equipment required. Together with the solution based approach, Si nanowire growth via SiO evaporation presumably represents the most cost-efficient way of producing Si nanowires.

# 3. Catalyst Materials

Au has been the catalyst material of choice for Si wire growth ever since the early publications of Wagner and Ellis.<sup>2</sup> It is instructive to take a closer look at the Au–Si system and try to figure out what it is that makes Au such a favorable catalyst material, because it provides some valuable insight into the criteria for catalyst metals in general.

# 3.1. Gold as Catalyst

From a purely practical point of view, many reasons favor the use of Au as catalyst material. The first is availability. Gold is one of the standard metals used in solid state research. Evaporation systems equipped with Au can presumably be found in most semiconductor research laboratories, so that depositing a thin layer of Au onto a sample is usually not a major obstacle. Alternatively to a thin evaporated layer, one can also use Au colloid nanoparticles, which are commercially available with diameters ranging from 2 to 250 nm.<sup>88</sup> Another advantage of Au is its high chemical stability. Although seemingly trivial, the fact that the Au does not oxidize in air is a decisive advantage for the pregrowth sample preparation, as it makes an in situ deposition unnecessary. The high chemical stability of Au furthermore reduces the technical requirements on the growth system, especially in view of the tolerable oxygen background pressure. The final practical advantage of Au is that Au is nontoxic, which is convenient from a work safety point of view.

The main reason why Au is used for Si wire growth, however, lies in its binary phase diagram with Si, shown in Figure 9a. One can see that the Au–Si phase diagram is of the simple eutectic type, with its dominant feature being a eutectic point at a composition of about 19 atom % Si and a temperature of 363 °C. The eutectic temperature is about 700 K lower than the melting point of pure Au and about 1050 K below the melting point of pure Si, which signifies a quite remarkable reduction of melting temperature. The phase within the V-shaped region, visible in Figure 9a, is the liquid phase, the actual composition of which depends

**Figure 9.** Schematic phase diagrams of different metal–Si systems. (a) Au–Si, (b) Al–Si, (c) Ag–Si, (d) Zn–Si, (e) Ti–Si, (f) Pd–Si.<sup>121,123</sup> After Schmidt et al.<sup>4</sup> The types refer to the classifications given in Figure 10.

on the amount of Si supplied. For Au-Si alloy droplets on a Si substrate, Si is abundant, and the composition of such Au–Si droplets is therefore given by the position of the liquidus line on the Si side, i.e. the phase boundary on the right-hand side (rhs) of the liquid phase. If such Au-Si droplets on a Si substrate, held at temperatures above the eutectic temperature, are exposed to a Si precursor such as silane, SiH<sub>4</sub>, silane molecules will crack at the surface of the droplets, thereby supplying additional Si to the droplet. This additional Si supply causes an increase of the Si concentration in the droplet to a value greater than the equilibrium concentration. Considering the Au-Si phase diagram shown in Figure 9a, this means that, by switching on the silane, the Au–Si droplet system is pushed over the liquidus line; and the only way for the droplet to reduce the Si concentration is to precipitate a Si-rich solid. In general, the composition of such a Si-rich solid would be given by the nearest phase boundary on the Si side of the liquidus. In the Au–Si case, the Si-rich solid happens to be pure Si. Consequently, the droplet precipitates Si, which with time results in the growth of a wire.

To formulate the requirement on the catalyst—Si binary phase diagram in a more abstract way, Si wire growth requires a nonhorizontal phase boundary over which one can push the catalyst—Si system to enforce the precipitation of a Si rich solid. Since we are interested in the growth of Si wires, the Si-rich solid needs to be Si itself, which means that the phase boundary over which to push the catalyst—Si system has to adjoin the pure Si side of the phase diagram. In the case of the VLS growth mode, this phase boundary is a liquidus line, as in Figure 9a. But this is not a necessary condition. For VSS Si wire growth, that is, growth via a solid catalyst particle, the phase boundary in question can also be a phase boundary limiting the Si solubility in the

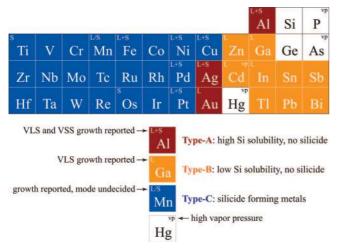

**Figure 10.** Periodic table with potential catalyst metals classified according to their phase diagram. Type-A: phase diagram dominated by a eutectic point at a Si concentration > 10%; no metal-silicide phase present. Type-B: phase diagram dominated by a eutectic point at a Si concentration < 1%; no metal-silicide phases present. Type-C: phase diagram with one or more metal-silicide phases; eutectic points located at temperatures above 800 °C. Elements marked with superscript vp have a vapor pressure of more than 0.01 mbar at 300 °C.

solid catalyst material itself, such as the Al pocket on the left-hand side (lhs) of Figure 9b, or it can as well be a silicide phase, such as the  $TiSi_2$  phase shown in Figure 9e. According to what was stated above, namely that the phase boundary required for Si wire growth has to neighbor the pure Si of the phase diagram, one can expect the most Si-rich silicide phase to be present during VSS Si wire growth. We will see later on that this indeed turns out to be the case.

Another quite important feature of the Au-Si binary phase diagram (see Figure 9a) is its relatively high Si concentration of about 19 atom % at the eutectic point. Si apparently likes to mix with Au. Consequently, the energetic costs per Si atom of increasing the Si concentration beyond its equilibrium value can be expected to be small. This can also be seen from the moderate slope of the liquidus line near the eutectic. As a consequence, the Si pressure required to achieve a certain increase of the Si concentration can be expected to be lower for liquids with a high equilibrium solubility of Si than for those with low equilibrium solubility. Expressed differently, catalyst metals with low Si solubility such as In or Ga, presumably require higher precursor pressures than Au. For completeness, it must be mentioned here that the large Si solubility may also turn into a disadvantage regarding the synthesis of axial nanowire heterostructures, as discussed in section 5.

One important property of Au is its conveniently low vapor pressure, even at high temperatures. At temperatures below about 800 °C, the vapor pressure of Au is smaller than  $10^{-8}$ mbar, and evaporation of Au is not an issue under usual Si wire growth conditions. We will see later on that some potential catalyst materials can be excluded just because of their high vapor pressure. Hg with a vapor pressure greater than 1 mbar at 400 K is one example. One aspect that has not been addressed so far concerns the surface tension of the liquid Au–Si alloy. According to the surface tension criterion, discussed in section 8, a certain minimum value of the droplet surface tension is required for wire growth. This criterion is well met by the Au–Si alloy.

In summary, the main advantages that make Au such a favorable catalyst material are that it is nontoxic, chemically

stable, and readily available; that it possesses a low temperature eutectic with comparably high Si solubility; that it has a low vapor pressure at elevated temperatures; and that the Au–Si liquid alloy has a high enough surface tension. Unfortunately, these advantages are balanced by one serious drawback, which is that Au, known to contaminate the nanowires,<sup>89–91</sup> is very much disliked by the semiconductor industry, because it is associated with deep-level defects in Si, leading to strongly enhanced carrier recombination.

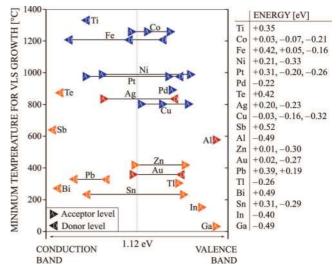

# 3.2. Alternative Catalyst Materials

In view of the incompatibility of Au with complementary metal-oxide-semiconductor (CMOS) production standards, strong efforts have been made in the past to identify an alternative, non-Au catalyst material for Si wire growth. Metal impurities in semiconductors are generally known to affect the charge carrier lifetimes by facilitating charge carrier recombination. The maximal recombination rate associated with a particular metal impurity, however, strongly depends on the energetic positioning of the corresponding impurity level within the band gap of the semiconductor. To be more precise, the recombination rate critically depends on the energy difference between the impurity level or levels and the band gap middle; the closer the impurity level is to the band gap middle, the more efficient it is as a recombination center. The use of metals with impurity levels close to the band gap middle, so-called deep levels, is therefore to be avoided. Concerning the use of Au, the problem is further exacerbated by the high chemical stability of Au that makes a cleaning of Au contaminated samples or Au contaminated equipment difficult, to say the least.

A large variety of catalyst materials have been tested for their ability to replace Au. Those metals for which successful Si wire synthesis is reported in the literature are as follows:

Ag, 211,14,16309293 Al, 4093–99 Bi, 57,100 Cd,  $^{14}$ Co,  $^{55}$ Cu,  $^{27,11,14,1630,56,899,3101,102}$ Dy,  $^{3}$  Fe,  $^{3,66-69,72,103-106}$  Ga,  $^{37,39,93,99,107}$  Gd,  $^{14}$  In,  $^{40,93,100,107,108}$ Mg,  $^{14}$ Mn,  $^{14}$ Ni,  $^{2,10,11,14-16,30,55,72,93,109-111}$ Os,  $^{14}$ Pb,  $^{100}$ Pd,  $^{2,10,14,30,35,93}$ Pr,  $^{73}$  Pt,  $^{2,6,10,11,16,93,112,113}$  Ru,  $^{73}$  Sn,  $^{114}$  Te,  $^{100}$  Ti,  $^{115-117}$  and Zn,  $^{13,93,100,118}$

As one can see, the number of possible catalyst materials is quite large. Although the quality of the wires obtained as well as the required growth conditions differ strongly, there are also similarities in the behavior of the different catalysts. In order to discuss the differences and similarities in a concise manner, it is useful to classify the catalyst materials with respect to the characteristics of their corresponding metal–Si binary phase diagrams. We will adopt here the classification scheme similarly introduced by Bootsma et al.<sup>30</sup> The catalyst materials are classified into three different categories: type-A, type-B, and type-C, as shown in Figure 10.

Type-A catalysts are the Au-like metals. Their phase diagram is of the simple eutectic type; that is, it is dominated by a single eutectic point. This eutectic point is located at a Si composition of more than 10 atom % Si. Furthermore, type-A catalysts do not possess any metal-silicide phases. There are only three type-A metals: Al, Ag, and Au.

Type-B catalysts are the low Si solubility metals. Their phase diagrams also show a single dominant eutectic point but no silicide phases. In contrast to the type-A catalysts, the eutectic point is located at much lower Si concentrations, less than 1 atom % Si. Typical type-B catalysts are In, Ga, or Zn.

Type-C catalysts are the silicide forming metals. Their phase diagram indicates the presence of one or more silicide

phases. In addition, the lowest eutectic temperature is higher than 800 °C. Typical type-C catalysts are Cu, Pt, or Ti.

#### 3.2.1. Type-A, Au-like Catalysts

Among the various catalyst materials, Al is the one whose Si binary phase diagram (see Figure 9b) shows the closest similarity with Au-Si. Though the eutectic point of the Al-Si system is located at a higher temperature (577 °C) and at a slightly lower Si concentration (12 atom %), the Al-Si and Au-Si phase diagrams are very much alike. With the phase diagrams being so similar, it is not too astonishing that VLS growth can be performed with Al as catalyst. Osada et al.94 demonstrated Al catalyzed VLS growth of crystalline Si wires in a CVD process using silane and applying temperatures of 580-700 °C. Al-catalyzed Si nanowire growth under comparable conditions was also reported by Whang et al.96-98 The authors claim to have grown Si nanowires at 540 °C via the VLS mechanism. This at first seems inconsistent, as the growth temperature reported by them is about 40 K below the eutectic temperature of the bulk A1-Si system. Even considering the surface-induced reduction of the eutectic temperature (see section 6), one may ask whether these wires actually grew in the VSS rather than the VLS growth mode. This is supported by the fact that Wang et al.<sup>95</sup> demonstrated the synthesis of well shaped, single crystalline, Al-catalyzed Si nanowires grown epitaxially on Si(111) substrates at a growth temperature of 430-490 °C; see Figure 3b. Since this growth temperature was well below the Al-Si eutectic point, Wang et al.<sup>95</sup> concluded that Si nanowires grew via the VSS mechanism, though this conclusion has recently been questioned.<sup>119</sup> Wang et al. point out that Al-catalyzed VSS growth is related to a peculiarity of the Al-Si phase diagram, not present in the Au–Si phase diagram, namely the pocket on the lhs of Figure 9b. This pocket indicates that up to about 1 atom % Si can be dissolved in solid Al at temperatures of 500 °C. The phase boundary limiting the Si solubility in solid Al is adjoining the pure Si side of the phase diagram. Therefore, all requirements for Si wire growth are fulfilled. By supplying a sufficient Si pressure, this phase boundary can be used to induce the precipitation of solid Si, that is, the growth of Si wires.

Synthesis via a solid Al particle brings the advantage that the solubility of Si in the catalyst particle is about 1 order of magnitude smaller than the eutectic composition. This low solubility, though potentially slowing down the growth process, could be beneficial for the fabrication of axial Si-Ge heterostructures with sharp transitions. As will be discussed in section 5, axial Au-catalyzed Si-Ge heterostructure nanowires do not show sharp transitions between Si and Ge, because of the high solubility of Si or Ge in the Au catalyst droplet. With lower solubility in the catalyst droplet or particle, sharper transitions between Si and Ge should be achievable. The use of Al, however, has another important advantage. Al does not create deep level defects. On the contrary, the position of the impurity level (see Figure 11) shows that Al is a p-type dopant, and one can therefore expect the nanowires to be strongly p-doped. A comparison with Al solid phase epitaxy experiments implies an Al doping of  $10^{18}$  to  $10^{19}$  cm<sup>-3</sup>.<sup>120</sup> Whether p-type doping is an advantage or not is difficult to decide, but having the possibility to directly synthesize highly p-doped wires, without the need of a vapor-phase dopant, is at least a potentially useful feature. The major drawback of the use of

**Figure 11.** Minimum temperature of certain metals required for vapor-liquid-solid (VLS) growth of Si nanowires plotted versus their respective impurity level energies in Si<sup>193</sup> after ref 4. The energies of these impurity levels are given on the rhs with respect to the middle of the band gap (assuming a band gap of Si of 1.12 eV). The color code refers to the catalyst classification of Figure 10: red, type-A; orange, type-B; blue, type-C.

Al, however, is its oxygen sensitivity. Oxidation of the Al catalyst particle has to be prevented during the whole processing sequence, which clearly limits the usability of Al.

Silver is the second nongold, type-A catalyst. Like Au, the Ag–Si system (see Figure 9c) possesses a single eutectic point (at 11 atom % Si and 836 °C).<sup>121</sup> Due to the high eutectic temperature, high process temperatures are required for Ag-catalyzed VLS growth of Si wires. Wagner and Ellis<sup>16</sup> reported VLS growth of single crystalline Ag-catalyzed Si wires by a SiCl<sub>4</sub>CVD process at temperatures of 950–1050 °C. That VLS growth under such conditions is indeed possible has been confirmed by Nebolsin et al.,<sup>11</sup> who managed to grow Si wires at a growth rate of about 1.5  $\mu$ m/s in a similar process. What is astonishing about these results is that the catalyst material did not evaporate completely under these conditions, as the vapor pressure of Ag reaches a value close to 10<sup>-2</sup> mbar at 1000 °C, which is about 3 orders of magnitude larger than that of Au.<sup>122</sup>

Regarding the use of Ag, it is interesting that Tatsumi et al.<sup>92</sup> claim to have synthesized amorphous Si wires by a silane CVD process at 650 °C, that is, well below the eutectic temperature, indicating VSS growth. This seems surprising, as most Ag–Si phase diagrams (see, for example, ref 123) do not show any significant solubility of Si in solid Ag, and wire growth experience suggests that a certain solubility of Si is necessary. This problem, however, has recently been resolved by a reevaluation of the Ag–Si phase diagram,<sup>121</sup> which revealed that the solid solubility of Si in Ag is about 0.2 atom % at 650 °C and 0.9 atom % close to the eutectic temperature, as shown in Figure 9c. The Ag-Si phase diagram thus resembles the Al-Si phase diagram, except that the eutectic point is located at higher temperatures and that the pocket on the lhs is less pronounced. Consequently, VSS Si nanowire growth with Ag as catalyst seems possible, and in view of the excellent results that have been obtained with Al as catalyst, Ag-catalyzed VSS growth seems very promising; particularly as the impurity levels of Ag (see Figure 11) are well positioned, being neither too close to

the band gap center nor to the conduction or valence band. Initial experiments on Ag-catalyzed VSS growth of silicon nanowires have been performed in our group.

# 3.2.2. Type-B, Low Si Solubility Catalysts

The type-B catalysts are characterized by a eutectic point at very small Si concentrations. Let us first look at the transition metals Zn and Cd. The Zn-Si binary phase diagram is dominated by a single eutectic point at 420 °C and 0.02 atom % Si, shown in Figure 9d, and despite its high vapor pressure of 0.2 mbar at 420 °C, Zn has proven to be an effective catalyst material for VLS growth. Chung, Yu, and Heath<sup>13,118</sup> demonstrated VLS Si nanowire growth by a silane CVD process at temperatures of 440-500 °C. They managed to synthesize Si nanowires with diameters between 15 and 35 nm and observed both  $\langle 111 \rangle$  and  $\langle 211 \rangle$ oriented nanowires, with the (211) oriented nanowires being virtually defect-free.<sup>118</sup> In view of the electronic properties, however, one must conclude that the impurity levels of Zn in Si (see Figure 11) are basically as detrimental as those of Au. The only real advantage of using Zn is that a potential Zn contamination of wafers or equipment can be removed more easily than a potential Au contamination.

Little is known on the use of Cd as catalyst, except for the remark that "cadmium promoted whisker growth when the source material was arsenic-doped silicon".<sup>14</sup> The phase diagram (eutectic at 321 °C and 0.14 atom % Si) strongly resembles that of Zn. Thus, Cd-catalyzed Si wire growth via the VLS mechanism could be possible, if one manages to prevent a complete evaporation of the catalyst material during growth. The Cd vapor pressure (greater than 1 mbar at 321 °C) is even higher than that of Zn, and this high vapor pressure is the main limitation for the use of Cd as catalyst material.

The use of Ga or In appears to be much more attractive than that of Zn or Cd from a vapor pressure point of view. At 500 °C, the vapor pressure of In is below  $10^{-7}$  mbar, and the vapor pressure of Ga is even lower:  $10^{-10}$  mbar. Moreover, In and Ga would also be attractive from an electronics point, as both would induce a p-type doping of the wires (see Figure 11). In terms of phase diagrams, Ga and In show great similarities. The Si concentrations at the eutectic point (smaller 0.01 atom %) as well as the eutectic temperatures (Ga, 30 °C; In, 156 °C) are very low in both cases, and any reasonable CVD growth temperatures will be way above the respective eutectic temperature. One can therefore expect In or Ga to produce similar results, a fact that has been experimentally confirmed by Givargizov et al.<sup>107</sup> They synthesized conical Si wires using In and Ga at high temperatures (900-1050 °C) using SiCl<sub>4</sub>. The authors attributed the conical shape to the incorporation and/or evaporation of the catalyst material.<sup>107</sup> More recently, Iacopi et al.<sup>40,108</sup> and Sharma et al.<sup>39</sup> using In and Ga, respectively, demonstrated Si nanowire synthesis by plasma-enhanced chemical vapor deposition (PECVD) at temperatures of 500-600 °C using silane as Si precursor.

Only little information exists on Si wire growth with other type-B catalysts, such as Tl, Sn, Pb, Sb, and Bi. Miyamoto et al.<sup>100</sup> reported amorphous Si fibers at temperatures of 500–600 °C using Bi and Pb as catalysts. The eutectic temperatures of Pb and Bi are 328 and 271 °C, respectively. VLS growth therefore seems likely. According to Nebolsin et al.,<sup>93</sup> the surface tensions of liquid Sn, Pb, Sb, or Bi are too small for stable wire growth, as discussed in detail in

section 8. In the case of Bi, for example, it is unclear whether indeed the too low surface tension or the too low Si solubility hinders nanowire growth under conditions comparable to the ones used for Au as catalyst. As mentioned in subsection 3.1, it could be that one simply has to apply higher Si partial pressures to realize wire growth with type-B catalysts. Both the fact that plasma assistance was necessary in order to obtain In- or Ga-catalyzed wires as well as the fact that solubility and growth velocity are correlated<sup>11</sup> would support such an assumption. This would also fit with recent results of Heitsch et al.,<sup>57</sup> who managed to synthesize Bi-catalyzed Si nanowires using trisilane, which is very reactive, as a precursor. Even if the assumption that lower Si solubility means higher minimum partial pressures is taken for granted, the question whether it is the solubility itself or the surface tension that causes the problems remains undecided, as the surface tension somehow correlates with the Si solubility. There is definitively a need for clarifying experimental and theoretical investigations, especially since the use of Bi, Tl, and Sn as catalyst would be quite attractive from an electronics point of view (see Figure 11).

# 3.2.3. Type-C, Silicide Forming Catalysts

Type-C catalysts are the silicide forming catalyst metals. The phase diagrams of type-C catalysts are typically rather complex, exhibiting several silicide phases and various eutectic points. Due to the presence of silicide phases, the type-C catalyst can be used not only for VLS but also for VSS wire growth via the silicide particle. This shall be discussed here considering Si nanowire growth based on Ti.<sup>39,115,116</sup> Figure 9e schematically depicts the Si-rich half of the Ti-Si phase diagram. As indicated therein, Ti-Si possesses a eutectic point at 1330 °C adjoining the pure Si side of the phase diagram, whose liquidus can be used for Si wire growth via the VLS mechanism. At growth temperatures below 1330 °C, growth should theoretically proceed via the phase that at this temperature is neighboring the pure Si side. As one can see in Figure 9f, this would be TiSi<sub>2</sub>. Considering growth at 1000 °C and starting from a Ti particle, this Ti particle will first transform into Ti<sub>5</sub>Si<sub>3</sub> and then into Ti<sub>5</sub>Si<sub>4</sub>, which becomes TiSi, which will finally transform into TiSi<sub>2</sub>. Only once this transformation process is complete can Si wire growth start. TiSi2-catalyzed, VSS Si nanowire growth has first been demonstrated by Kamins et al.,<sup>115</sup> who synthesized Si nanowires at 640–670 °C by means of a CVD process. The main advantages of Ti are its favorably positioned impurity level (see Figure 11) and its low solubility in Si. Ti is assumed to be compatible with CMOS technology. The crystallographic quality of Si nanowires grown via a TiSi2 catalyst particle, however, seems to be rather poor compared to what can be obtained by using Au as catalyst.

The use of Fe or Dy as catalysts in CVD processes at temperatures around 600 °C leads to similar growth results as for Ti, in the sense that the Si nanowires show a high density of crystallographic defects.<sup>3</sup> It appears to be a general trend that nanowires grown via a silicide particle tend to have a higher density of crystallographic defects than VLS-grown ones. This finding is indirectly supported by the results of Morales et al.,<sup>66</sup> who grew nanowires of high crystalline quality using Fe as catalyst; but they used laser ablation from a mixed Fe–Si target and applied temperatures of about 1200 °C, which is close to the melting point of the Fe–Si alloy. Thus, one can assume that their nanowires grew via the VLS

mechanism, with no silicide phase present, which would explain the good crystalline quality.

Other type-C catalysts are the noble metals Pd and Pt, which are known to have similar physical and chemical properties. According to their binary phase diagrams, both Pd (see Figure 9f) and Pt would require high temperatures for VLS growth (Pd, 892 °C; Pt, 979 °C). At such high temperatures, results similar to those obtained with Au as catalyst can been obtained.<sup>2</sup> This can best be seen in the work of Weyher<sup>112</sup> and Wagner et al.,<sup>16</sup> who both synthesized Pt-catalyzed VLS grown Si wires by SiCl<sub>4</sub> CVD at temperatures around 1000 °C; and both obtained  $\langle 111 \rangle$  oriented wires with hexagonal cross sections and {211} side facets. A very interesting result has been reported by Bootsma et al.,30 who stated therein that "Filamentary growth was also obtained with Ag, Cu, Ni and Pd at substrate temperatures of about 800 °C". This is surprising as each of these metals requires temperatures of more than 800 °C for VLS Si wire growth (see Figure 11). In the case of Pd, the reported growth temperature is almost 100 K below the minimum temperature required for VLS growth. Of course, one has to consider the possibility that the catalyst particle is in a metastable undercooled state, so that despite the low temperature, growth could possibly still proceed via the VLS mechanism. Growth via the VSS mechanism, employing a solid silicide particle, however, could provide another plausible explanation. The Pd-Si phase diagram shown in Figure 9f indicates that VSS growth at 824-892 °C would be mediated by a PdSi silicide particle. At temperatures below 824 °C, VSS growth should be catalyzed by a Pd<sub>2</sub> Si particle. This has recently been confirmed by Hofmann et al.,<sup>35</sup> who performed in situ transmission electron microscopy (TEM) studies on Pdsilicide catalyzed Si nanowire growth. Hofmann et al.,<sup>35</sup> applying growth temperatures of 892 °C, furthermore found that the nanowires grow via lateral ledge flow at the Si-silicide interface. With regard to possible silicides, the situation for Pt is less complex than that for Pd. According to the Pt-Si phase diagram, growth at temperatures below 979 °C should proceed via a solid PtSi particle, which has been confirmed by Baron et al.<sup>113</sup> Similar results have also been obtained by Garnett et al.<sup>6</sup>

Both, Cu and Ni are very attractive catalyst materials, but for different reasons. Although Cu, like Au is a very efficient recombination center in Si, it is attractive because Cu is already used for interconnects in integrated circuits (ICs); so one cannot argue that Cu is totally incompatible with CMOS technology. Ni on the other hand is attractive because of its favorable impurity levels in Si (see Figure 11) and because Ni-silicide is used for electrical contacts in wellknown standard technologies. The minimum temperature required for Ni VLS Si wire growth is 993 °C, which is about 200 K higher than that of Cu (802 °C); and at these comparably high temperatures, both Cu and Ni produce Si wires of similar quality to Au.<sup>14,16</sup> In the case of Cu, this has recently been demonstrated by Kaves et al.;<sup>7</sup> see Figure 2b. They synthesized arrays of perfectly aligned,  $\langle 111 \rangle$ oriented Si wires using Cu as catalyst in a SiCl<sub>4</sub>CVD process at temperatures of 850-1100 °C. For Cu also, VSS growth has been demonstrated. Yao et al.<sup>101</sup> grew  $\langle 111 \rangle$  Si nanowires at 500 °C via the VSS growth mode, and in accordance with the Cu-Si phase diagram, they found a Cu<sub>3</sub>Si silicide particle at the tip of the nanowires. The Si nanowires obtained, however, showed a significant number of crystallographic defects. Similar results were obtained by Arbiol et al.<sup>102</sup>

To summarize this section, the type-C catalysts work well, but only in the VLS growth mode, i.e. at high temperatures. At lower temperatures, where silicide-catalyzed VSS growth prevails, problems with the crystalline quality of the wires arise. The type-B catalysts such as In and Ga work, but only under rather harsh experimental conditions. Compared to In or Ga, growth using Zn seems to be easier, but there is no big advantage of Zn compared to Au, except for the contamination removal. Thus, in the end, for low-temperature processes, everything boils down again to the use of the three type-A catalysts, Al, Au, and possibly Ag.

# 4. Crystallography

VLS grown silicon nanowires are in most cases highly crystalline diamond-type crystal structures. Aiming at an inplace epitaxial growth of Si nanowires on Si substrates, one typically wants to control the nanowire position and diameter and—seemingly most challenging—also the crystallographic growth direction of the nanowires. Growing nanowires with well-defined crystallographic orientations is not only important for an in-place growth of Si nanowires, where random growth directions are not what is intended. Since the physical and particularly the electrical properties of Si depend on the crystallographic orientation, control of the nanowire growth direction would be advantageous.

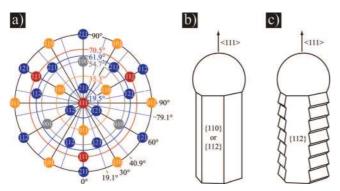

Considering epitaxial in-place growth of silicon nanowires on Si substrates, one faces two problems related to the crystallographic orientation of the nanowires. And these two problems should be clearly distinguished. The first concerns the question as to which family of growth directions the nanowires belong. This question can be answered, for instance, by breaking the wires off the substrate and investigating them by transmission electron microscopy. Typically, only three families of growth directions are observed; these are  $\langle 110 \rangle$ ,  $\langle 112 \rangle$ , and  $\langle 111 \rangle$ .<sup>1,16,26,27,76,79,124</sup> With few exceptions,<sup>16,48,50,76,79,113</sup> this observation holds for Si nanowire growth in general and, interestingly, is almost independent of the growth method employed. The observation that Si nanowires are typically  $\langle 111 \rangle$ ,  $\langle 110 \rangle$ , or  $\langle 112 \rangle$ oriented does, of course, not rule out that one or the other of these three families is favored by the specific growth conditions, such as, for example,  $\langle 111 \rangle$  for wires of large diameter.

For CVD grown Si nanowires, it has been observed that the nanowire growth direction shows a marked diameter dependence.<sup>26,27</sup> Nanowires with diameters less than about 20 nm prefer to grow in  $\langle 110 \rangle$  directions, whereas thicker Si nanowires with diameters larger than about 50 nm favor the  $\langle 111 \rangle$  orientation. In addition, there exists a certain probability that  $\langle 112 \rangle$  nanowires can be found;, with the probability for this being maximal in the transition region between 20 and 50 nm.<sup>26,27</sup> This change of growth direction can presumably be attributed to the scaling behavior of different energetic contributions: the contribution of the side faces, being proportional to the diameter d, versus the contribution of the liquid-solid interface and the Si volume, being proportional to  $d^{2,26,27}$  One can argue that, due to this difference in scaling behavior, thin Si nanowires rather tend to choose an orientation that provides energetically favorable side faces, whereas thick Si nanowires choose the orientation that minimizes the contribution of the wire-catalyst interface.

Nonetheless, even if growth conditions can be adjusted such that only one specific family of directions, e.g.  $\langle 111 \rangle$ , is preferred, one still faces the problem that there is usually

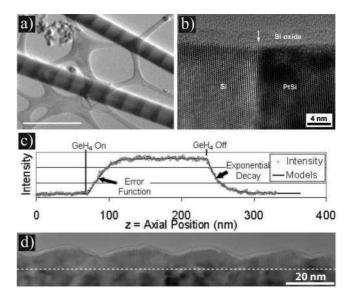

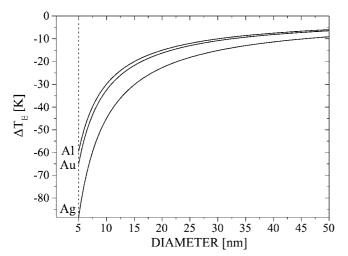

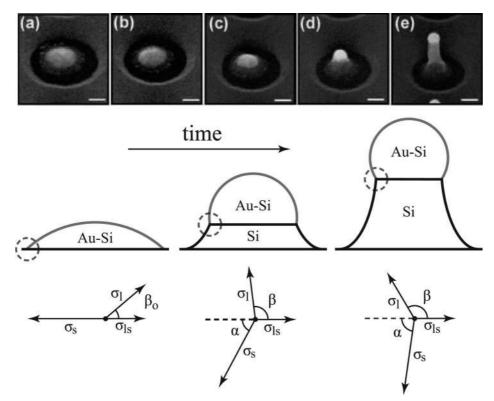

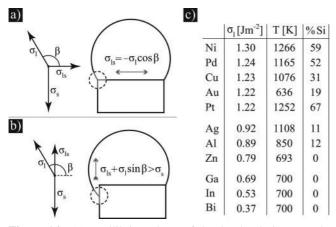

**Figure 12.** (a) Stereographic projection with respect to the [111] orientation. The degrees on the circles indicate the inclination angle with respect to the [111] direction. The degrees at the perimeter correspond to the azimuth angle. (b) Hexagonal nanowire. (c) Sawtooth faceting after Ross et al.<sup>33</sup>