# Guidelines for Etching Silicon MEMS Structures Using Fluorine High-Density Plasmas at Cryogenic Temperatures

Meint J. de Boer, J. G. E. (Han) Gardeniers, Henri V. Jansen, Edwin Smulders, Melis-Jan Gilde, Gerard Roelofs, Jay N. Sasserath, and Miko Elwenspoek, *Associate Member, IEEE*

Abstract—This paper presents guidelines for the deep reactive ion etching (DRIE) of silicon MEMS structures, employing  $SF_6/O_2$ -based high-density plasmas at cryogenic temperatures. Procedures of how to tune the equipment for optimal results with respect to etch rate and profile control are described. Profile control is a delicate balance between the respective etching and deposition rates of a  $SiO_xF_y$  passivation layer on the sidewalls and bottom of an etched structure in relation to the silicon removal rate from unpassivated areas. Any parameter that affects the relative rates of these processes has an effect on profile control. The deposition of the  $SiO_x F_y$  layer is mainly determined by the oxygen content in the SF<sub>6</sub> gas flow and the electrode temperature. Removal of the  $SiO_x F_y$  layer is mainly determined by the kinetic energy (self-bias) of ions in the  $SF_6/O_2$  plasma. Diagrams for profile control are given as a function of parameter settings, employing the previously published "black silicon method". Parameter settings for high rate silicon bulk etching, and the etching of micro needles and micro moulds are discussed, which demonstrate the usefulness of the diagrams for optimal design of etched features. Furthermore it is demonstrated that in order to use the oxygen flow as a control parameter for cryogenic DRIE, it is necessary to avoid or at least restrict the presence of fused silica as a dome material, because this material may release oxygen due to corrosion during operation of the plasma source. When inert dome materials like alumina are used, etching recipes can be defined for a broad variety of microstructures in the cryogenic temperature regime. Recipes with relatively low oxygen content (1-10% of the total gas volume) and ions with low kinetic energy can now be applied to observe a low lateral etch rate beneath the mask, and a high selectivity (more than 500) of silicon etching with respect to polymers and oxide mask materials is obtained. Crystallographic preference etching of silicon is observed at low wafer temperature (-120 °C). This effect is enhanced by increasing the process pressure above 10 mtorr or for low ion energies (below 20 eV). [720]

*Index Terms*—Cryogenic etching, profile control, reactive ion etching (RIE).

Manuscript received July 18, 2001; revised November 28, 2001. This work was supported by the Dutch Technology Foundation (STW), the applied division of NWO and the technology program of the Ministry of Economic Affairs. The "DEEMO" project ESPRIT nr. 20342 was supported by the European Commission. Subject Editor R. T. Howe.

M. J. de Boer, H. Jansen, E. Smulders, G. Roelofs, and M. Elwenspoek are with the Micromechanical Transducers group, MESA Research Institute, University of Twente, 7500 AE, Enschede, The Netherlands (e-mail: M.J.deboer@el.utwente.nl).

J. G. E. Gardeniers is with the Micronit Microfluidics B.V., 7500 AM Enschede, The Netherlands.

M.-J. Gilde is with the Alcatel Optronics Netherlands, 7500 AH Enschede, The Netherlands.

J. N. Sasserath is with the Market Quest Consulting, St. Petersburg, FL 33703 USA.

Publisher Item Identifier 10.1109/JMEMS.2002.800928.

# I. INTRODUCTION

THE last decades have seen an ever-increasing use of plasma etching techniques, in particular for the fabrication of miniaturized devices based on silicon. Traditionally this development has been driven by the road maps in microelectronics industry, but during the last few years the focus of the field is shifting toward the fabrication of microelectromechanical systems (MEMS). The main difference between the requirements of Integrated Circuit (IC) and MEMS fabrication is the desired structural definition: present and future IC's rely on submicron features, while most structures in MEMS are for the time being at least a few microns wide. However, compared to structure depths of only microns in conventional ICs, MEMS structures may be several hundred microns deep, even up to the thickness of a silicon wafer. Additionally, typical mask layouts of MEMS contain a large variety in feature size, shape and spacing, while IC fabrication, being a much more mature technology, generally relies on well-defined design rules with respect to feature definition. One could argue even that future MEMS technology will have to live with similarly strict design rules, and in fact several MEMS foundries are doing exactly that.

Nevertheless, for the time being the limits of the available plasma etching methods, and in particular the details of the etching mechanisms, have not been completely established. For that reason one can still observe extensive world-wide research efforts to find and optimize processes that ensure a well-defined high aspect ratio of etched features, while at the same time maintaining high etch rates (up to 10  $\mu$ m/min, for an exposed silicon area of less than 10% of the wafer surface) and high selectivity with respect to masking material (silicon versus photoresist: more than 500, silicon versus silicon dioxide: more than 1000) or other layers (e.g., an embedded silicon dioxide layer in a silicon-on-insulator, SOI, substrate, on which etching should stop without undercutting or notching of the silicon top layer exposed to the etchingmedium). In order to satisfy all the requirements generally a trade-off must be made Ultimately precise control of the profile of side walls (within 2°) can lead to fine-tuned structures that can be applied for special purposes. An example of the latter, which will be discussed in more detail below, is the development of trenches with side-walls having a slightly positive taper (ca. 5° between trench sidewall and surface normal; positive taper means that the trench narrows at a greater depth) and a smooth surface (average roughness less than 200 nm), particularly suitable for moulds used in polymer hot embossing processes [1] or for needle structures used, e.g., for the introduction of biological material in animal or plant tissue [2].

The basic idea of all of the anisotropic reactive ion etching efforts today is to find a balance between trench side-wall passivation and trench bottom etching, the latter being activated through the bombardment of ions from the plasma discharge. Two main approaches can be distinguished. The first is a method developed by Laermer and Schilp [3]. It became known as the "Bosch Process" and is a room temperature process based on continuous cycling of subsequent passivation and etching steps, therewith achieving high aspect ratio microstructures. Based on this generic approach, Surface Technology Systems [4] has developed its advanced silicon etch (ASE) technology. The aspect ratio can be over 20 and etching depths may be up to 500  $\mu$ m. A typical etch rate is 2  $\mu$ m/min, the selectivity to resist is 75:1 and to silicon dioxide 250:1 [5].

The second method was introduced by Tachi *et al.* [6] and is based on etching at cryogenic temperatures for low-bias fluorine-based high-density plasmas. The sidewall protection mechanism is a combination of formation of a blocking (inhibitor) layer and reduction of the reaction probability of radicals (the chemical contribution to etching) at the silicon surface. The latter heavily depends on temperature, in particular in the cryogenic regime. Although initially not recognized by Tachi and his co-workers, the addition of  $O_2$  gas to the plasma is required for deposition of SiO<sub>x</sub>F<sub>y</sub> as inhibitor layer to achieve directional etching.

Several workers [7]–[9] have demonstrated that the addition of  $O_2$  to  $SF_6$  using this cryogenic method is a very sensitive control parameter for the anisotropy of Si etching. The shape of the profile can easily be changed from a negative to a positive taper [10]. In this paper we shall restrict ourselves to the latter method, i.e., cryogenically controlled deep reactive ion etching or Cryo-DRIE.

Tachi *et al.* exploit  $SF_6/O_2$  high-density plasma chemistry to create directional etching. In such plasma, decomposition of  $SF_6$  produces F radicals that etch silicon spontaneously (isotropically) by formation of volatile  $SiF_4$ . The inhibitor layer is created by oxygen radicals from the plasma via the formation of a  $SiO_xF_y$  deposit [9]. Cooling the wafer to cryogenic temperatures enhances passivation by reducing the chemical reactivity, which can be explained by a reduction in the volatility of reaction product ( $SiF_4$ ) [11], [12]. However,  $SF_6$  decomposition also produces ions like  $SF_5^+$  that enhance etching of the  $SiO_xF_y$ layer locally as they strike the surface with relatively low kinetic energies. The sidewalls of the etched structures are much less exposed to ion bombardment and will be covered by the blocking layer. The bottom of the structure is exposed, and etching can proceed there, leading to anisotropic features.

In a SF<sub>6</sub>–O<sub>2</sub> plasma with a cryogenically cooled silicon substrate, as was described above, the processes of formation of the passivation layer, its removal from the bottom of a trench, and the etching of unpassivated silicon surface all occur simultaneously and are in delicate balance when directional etching is established. To complicate the matter even more, the optimal balance in conditions is different for different mask layouts. Consequently, although DRIE technology is continuously being improved, the optimization of the process for a special mask layout is still a rather time consuming affair and strongly depends on the skills and experience of the engineer. Our experience is that a great number of test runs (more than 10) have to be carried out in order to find the ideal parameter setting for a desired mask layout. This paper intends to illustrate a method that can be used to find optimized conditions with a limited number (5) of test runs. The method is based on our previous work on the so-called Black Silicon Method, BSM, an experimentation algorithm which consists of the following two primary steps: i) for the desired mask layout and a certain combination of parameters (e.g., oxygen flow and wafer temperature) that are varied continuously with all other parameters fixed, the conditions at which black silicon is observed are identified; ii) next, a small adjustment in the parameters is made toward conditions where a little more mask undercut occurs. For more details on this method and the basic principles behind it, we refer to [10].

In this paper, guidelines for profile control ("how to ...") of the Cryo-DRIE process are presented. The main parameters of the process will be evaluated and their impact on the profile result will be discussed. The treatment of the parameter influence will in general be only qualitative, i.e., we will be concerned more with trends than with exact modeling of the relations between process result and parameters. This makes our work more generally applicable, since the exact quantitative description of the relations is highly dependent on the exact configuration of the etching equipment, however the trends will be the same for most apparatus. Parameter settings of high-rate silicon bulk etching and etching structures with a sidewall with a positive taper will be given. Also equipment demands and calibration methods of this equipment will be discussed. Finally, a number of application examples will be given, which corroborate the feasibility of parameter fine-tuning for optimal design of etched features.

# II. EQUIPMENT

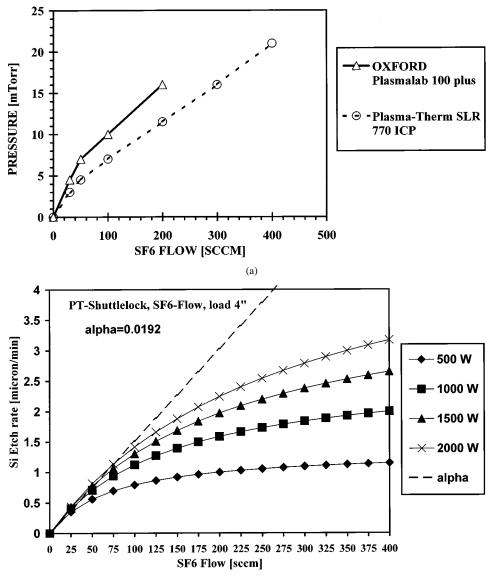

The guidelines were accomplished by evaluating, respectively, the Plasma-Therm SLR770 ICP Shuttlelock system of Unaxis USA, Inc. [13], and the Plasmalab 100 plus system of Oxford Instruments [14]. In these systems the silicon wafers are mechanically clamped to a liquid nitrogen-cooled substrate electrode. Helium backside cooling is incorporated to allow efficient temperature control of the wafer, which is indispensable for Cryo-DRIE processes. A high conductance pumping system has been installed in these systems to allow high gas flows of SF<sub>6</sub> at relatively low operating pressures [see Fig. 1(a)], thereby achieving a high etch rate (5–10  $\mu$ m/min) and profiles with straight side walls (control within 5°). All the systems are equipped with double-powered plasma sources. One is a high-density source to create a high radical and ion density. The other is a capacitively coupled plasma source (CCP) to direct the ions from the plasma glow region toward the wafer surface. This enables us to control independently the flux of radicals and ionic species of the SF<sub>6</sub> plasma. The high density source of Plasmalab 100 plus system uses a helicoil design and is power controlled, and the Plasma-Therm SLR770 ICP Shuttlelock system is equipped with a true ICP (inductively

(b)

Fig. 1. (a) Operating pressure as a function of gas flow, used to determine the maximum gas flow at a pressure of 10 mtorr for the Plasmalab 100 plus system and the Plasma-Therm SLR 770 ICP system at 1000 W ICP power and fully opened throttle valve. (b) Etch rate of silicon as a function of SF<sub>6</sub> flow for the Plasma-Therm SLR770 ICP Shuttlelock system. Parameters settings: electrode temperature 25 °C, exposed area 100% of 4-in Si-wafer, 0 W CCP power.

coupled plasma source) design, which is current controlled [15]. High-density plasma sources are generally constructed either with a fused silica or an alumina dome. A disadvantage of a fused silica dome is that the plasma etches the dome slightly, during which emission of oxygen takes place, that changes the plasma SF<sub>6</sub> chemistry during anisotropic etching of silicon. Alumina domes are chemically inert and are only etched by ion bombardment which may create black silicon on the wafer by redeposition of sputtered alumina particles. This phenomenon is only observed in the Plasmalab 100 plus system using a Prototech Helicoil high-density source. In this system we have observed a relatively high erosion rate of the fused silica at the bottom of the dome (100 nm/min), for 10 mtorr, 120 sccm SF<sub>6</sub> and 600 W ICP power. This indicates that high electric fields are present in the dome, which increase the flux and energy of ions that move toward the wall of the dome. Such a mechanism may also explain the sputtering of alumina particles as mentioned above. To study the influence

of the dome material on the etch process the fused silica dome of the Prototech ICP source of the Plasmalab 100 system was replaced with an alumina dome.

The optimization rules for tuning the equipment and guidelines for profile control were carried out at the Plasma-Therm SLR770 ICP Shuttlelock of Unaxis USA, Inc., with an alumina dome. Furthermore the Plasmalab 100 plus system with fused silica dome was used to verify the results of Plasma-Therm system by etching a number of MEMS structures (see Section IV), which demonstrate the usefulness of the guidelines.

# A. Limits of the Equipment With Respect to the Maximum Etch Rate

For optimal performance of the etching process it is necessary to know the limits in the etch rates that can be achieved with a particular etching setup. These limits are in our case determined by the number of reactive species that can be generated by the high-density plasma source and the efficiency of the vacuum

Fig. 1. (Continued.) (c) Etch rate of silicon as a function of ICP power for the Plasma-Therm SLR770 ICP Shuttlelock system. Parameters settings: electrode temperature 25 °C, exposed area 100% of 4-in Si-wafer, 0 W CCP power.

system. The efficiency of the vacuum system was studied by measuring the relation between pressure and  $SF_6$  gas flow [see Fig. 1(a)]. This was realized by opening the throttle valve completely. The pump rate of the vacuum system controls the now maximum gas flow at a certain process pressure. The  $SF_6$  gas flow measured at 10 mtorr is defined as the maximum gas flow. This is because a demand of anisotropic etching of silicon is that ions should pass the dark sheath nearly without collisions and bombard the silicon surface perpendicularly, i.e., with a small Ion Angular Distribution (IAD). At 10 mtorr or lower pressures the mean free path of the ions is larger than the thickness of the dark sheath [16]. Process pressures above 10 mtorr will make the ion bombardment less directional (larger IAD), which renders sidewall etching effects like bottling more pronounced [17].

To study the limits of silicon etching the maximum etch rate was determined as a function of  $SF_6$  flow for different ICP power settings, using the Plasma-Therm SLR770 ICP Shuttle-lock system. The etch rate of silicon was measured at bare 4 inch wafers by weight measurements on a Sartorius weighing scale with an accuracy of 0.1 mg.

In Fig. 1(b) it can be seen that for relatively low SF<sub>6</sub> flow, in particular for the higher ICP powers, the etch rate increases linearly with the SF<sub>6</sub> flow and does not depend so much on the ICP power. This can also be seen in Fig. 1(c), where the curves as a function of ICP power approach a saturation value, in particular for the lower SF<sub>6</sub> flows. The slope  $\alpha$  of the dashed line in Fig. 1(b) is approximately 0.0192 [ $\mu$ m min<sup>-1</sup> sccm<sup>-1</sup>]. In case of low ICP power or high SF<sub>6</sub> flow, the etch rate increases linearly with power and is almost independent of the SF<sub>6</sub> flow. The slope  $\beta$  of the dashed line in Fig. 1(c) is 0.0027 [ $\mu$ m min<sup>-1</sup> W<sup>-1</sup>]. In general, the etch rate  $ER_{Si}$  can be expressed as a function of ICP power and SF<sub>6</sub> flow using the empirical expression [18]

$$ER_{\rm Si}(Q,P) = \frac{\alpha Q_{\rm SF6} * \beta P_{\rm ICP}}{\alpha Q_{\rm SF6} + \beta P_{\rm ICP}}.$$

(1)

In which  $Q_{SF6}$  and  $P_{ICP}$  are the SF<sub>6</sub> flow and the ICP power, respectively. To obtain optimal performance the next rules should be noted: When the etch rate is independent of power, but a still higher etch rate is desired, this may be achieved by setting a higher gas flow. However, it has to be kept in mind that the maximum adjustable gas flow should preferably not exceed the optimal process pressure of 10 mtorr.

For the Plasma-Therm SLR770 ICP Shuttlelock system, an optimal performance is observed at a flow of 150 SCCM and ICP power of 750W for a pressure of 10 mtorr, giving an etch rate of 1.25  $\mu$ m/min for an exposed area of 100% of a 4-in silicon wafer.

# B. Survey of "Black Silicon" and Anisotropic Etching Conditions

To find the settings for anisotropic etching of silicon for any etching set-up we previously described an experimental procedure that was named "Black Silicon Method" [10], [18], since it is based on finding the conditions for which black silicon (BS) forms on a bare silicon wafer, when e.g., at different electrode temperatures oxygen is added to a defined SF<sub>6</sub> etching recipe. The amount of oxygen required to form black silicon is a function of all parameter settings (see Table I), of the design of the system (e.g., the type of dome material) and the exposed area of silicon (the loading) on the substrate. The procedure uses the fact that the parameter settings found for the formation of black silicon are close to those of anisotropic etching of silicon, where directional etching with a low lateral etching rate of less than 100 nm/min occurs. This easy and generally applicable procedure can be applied to find the anisotropic process window for etching any kind of microstructure on any type of etching set-up, without the need to carry out an extensive amount of experiments or complex calculations. Furthermore, the method is useful as a calibration tool, e.g., after maintenance or repair

#### TABLE I

Results of Centerpoint Process for Plasma-Therm SLR770 ICP Shuttlelock System With Alumina Dome. The Center Point Process is Depicted in the Dark Shaded Column With the Directional Profile. The Influence of a Parameter Change on the Profile Is Depicted in the Rows of the Table. For Instance, When the Oxygen Flow of the Center Point Process Is Decreased to 6 sccm  $O_2$  the Profile Will Show a Negative Taper

| Profile/<br>Parameter<br>range | U<br>iotrapic | U.  | 15<br>Latte | ŢŢ             | U        | Y       | Y                 | Y     |

|--------------------------------|---------------|-----|-------------|----------------|----------|---------|-------------------|-------|

| O2[sccm]<br>0-12               | 0             | 2-4 | 5           | 6              | 8-10     | 11      | 12                |       |

| CCP [Watts]<br>0-32            | 1             | ्   | 24-32       | 4-24           | 2-3      | 1       | 0                 |       |

| SF6[seem]<br>50-150            | •             | •   | •           | 125-150        | 100      | 125     | 50-75             |       |

| Electr. [°C]<br>-80,-150       | *             |     | 4           | 150-140        | 130-120  | 100-110 |                   | 90-80 |

| ICP [Watts]<br>750-2000        | 1             |     | 2000-1500   | 1150-1050      | 1050-750 |         |                   |       |

| He [Torr]<br>1.5-9.8           |               |     |             | 10             | 6.0      |         |                   | 1.5   |

| p [mTorr]<br>7-9               | +:            | -   | 8           | 3 <del>9</del> | 7-8      | 9       |                   |       |

| clamp. [Bar]<br>0.5-3.0        | 12            |     | ं           | :+             | 1.5-0.5  |         |                   |       |

| time [min]<br>5-25             | -             | •   | -           |                | 5-25     | -       | - 6 <b>1</b><br>1 |       |

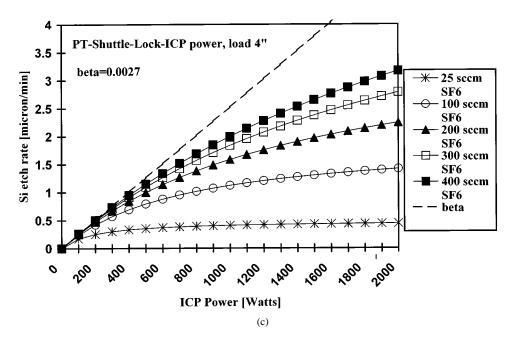

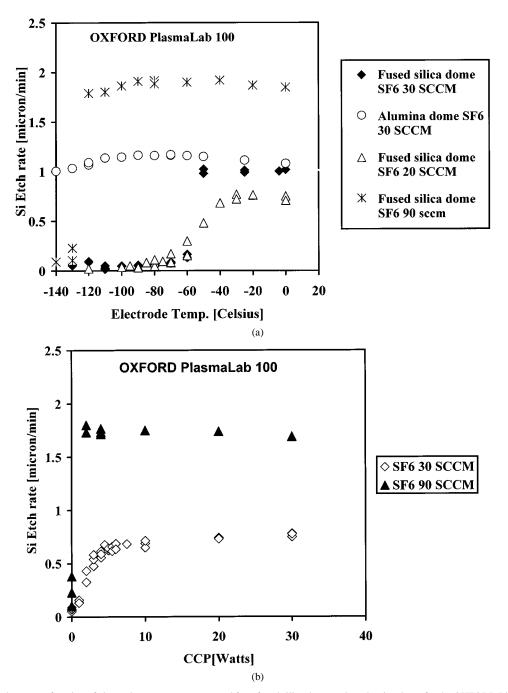

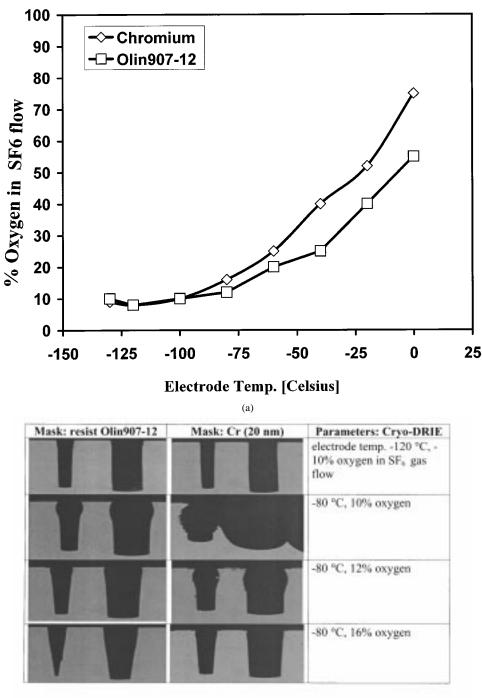

Fig. 2. Black Silicon line measured for the OXFORD Plasmalab 100 system for a fused silica dome and an alumina dome. Parameter settings: 600 W ICP, 30 sccm SF<sub>6</sub>, 0 W CCP, 10 mtorr, exposed area 100% of 3-in Si-wafer.

operations on the system or as a trouble-shooting tool to characterize improper functioning of the system.

Later, we will use the black silicon method (BSM) just described, to evaluate the relevance of several parameters for anisotropic etching of silicon, by locating the line at which BS appears in a certain parameter setting frame.

#### C. Dome Material

We will start with an investigation of the influence of the material of the dome present in the high-density plasma source. In Fig. 2 in a graph of oxygen content versus electrode temperature the BS-line is shown for experiments on bare silicon substrates performed in a Plasmalab 100-plus system with Prototech Source, equipped with either an alumina or fused silica dome. In this paper the oxygen content is defined as the percentage of oxygen gas (in sccm) that is intentionally added to the SF<sub>6</sub> gas flow into the etching chamber. For the BS line determined for etching in the presence of a fused silica dome a lower oxygen content was required than in the presence of an alumina dome, which indicates that erosion of the fused silica dome gives significant emission of oxygen, sufficient to seriously influence the etching result, as was previously suggested by Bartha *et al.* [8]. This assumption was verified by etching anisotropic profiles in silicon using a test mask with lines and spacings ranging from 1  $\mu$ m to 128  $\mu$ m, that lead to the formation of deep trenches with a varying area of silicon exposed to

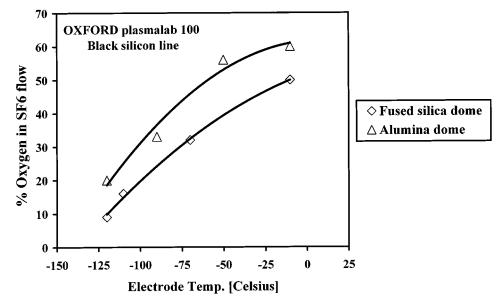

Fig. 3. (a) Silicon etch rate as a function of electrode temperature measured for a fused silica dome and an alumina dome for the OXFORD Plasmalab 100 system. Parameter settings: 600 W ICP, 10 mtorr, 0 W CCP, 0 sccm  $O_2$ , exposed area 100% of 3 inch Si-wafer. (b) Silicon etch rate as a function of CCP power and SF6 gas flow for the OXFORD Plasmalab 100 system with fused silica dome. Parameter settings: 600 W ICP, 10 mtorr, electrode temperature  $-130 \circ C$ , 0 sccm  $O_2$ , exposed area 100% of 3-in Si-wafer.

the etching medium. It was observed that, in agreement with the results of Fig. 2, in the cryogenic temperature regime the oxygen content in the SF6 gas flow for the alumina dome had to be 10% higher than with the fused silica dome.

Besides the anisotropy and therewith the trench profile, also the etch rate of silicon is influenced by the dome material. In Fig. 3(a) the etch rate, determined from weight measurements on bare 3-in low-boron-doped  $\{100\}$ -oriented silicon wafers is depicted as a function of electrode temperature. Before each experiment, the substrate surface was cleaned from native oxide by immersing the wafer for 60 s in 1% HF-solution. The CCP setting was reduced to zero watts to minimize the ion energy. Under such conditions, the etching process becomes very sensitive to the formation of black silicon, because the selectivity in etching between the silicon substrate and particles (originating from the fused silica or the alumina dome) redeposited on its surface is increased.

The etch rate of silicon at horizontal surfaces, i.e., at the top surface of the wafer and on the bottom surface of trenches, with the alumina dome present is independent of the electrode temperature, which indicates that the etch rate is not controlled by (spontaneous) thermally activated reactions, but by ion-assisted reactions. Identical results have been observed by Tsujimoto [19] and Francou [7]. According to Tsujimoto [19] the so-called "reactive spot model" [20] should be used to explain the temperature independence of the etch rate: At low temperatures, incident F atoms adsorb on the Si surface but do not react with Si atoms without ion incidence because of the low "reaction probability", by which they obviously mean, in chemical terms, that the rate of the thermally activated reaction is insignificantly low at such low temperatures. Only through ion collisions a reaction between F atoms and Si atoms is initiated, probably through a surface atom excitation process, the so-called "reactive spot". Therefore, the reaction rate at horizontal surfaces does not depend on electrode temperature. The plasma potential (of the order of 10 V) created by the ICP source now is responsible for the acceleration of ions, which gives them the kinetic energy to allow the generation of reactive spots.

We observed that the shiny surface of bare silicon wafers was hardly changed during etching, when the electrode temperature was lowered to cryogenic temperatures. Only at cryogenic temperatures below -100 °C the surface became milky, which is thought to be caused by re-deposition of alumina particles. In the Plasma-Therm SLR770 ICP Shuttlelock no milky surfaces were observed, which indicates that alumina sputtering depends on the design of the high-density source chamber. With the fused silica dome, at -60 °C the etching rate of silicon at horizontal surfaces shows a strong reduction, the surface of the blank wafers now becomes partly black. At even lower temperatures the wafer surface becomes gray and the etch rate drops to almost zero, indicating that the wafer is covered by some oxygen containing blocking layer, e.g.,  $SiO_xF_y$ , caused by the emission of oxygen from the eroding fused silica dome [8]. Also at temperatures above -60 °C it is observed that the etch rate is reduced in presence of the fused silica dome, indicating the presence of an oxygen containing blocking layer.

To verify that the silicon substrate is covered with a  $SiO_xF_u$ layer, the CCP power was increased, thereby increasing the energy of the ions. For removal of the  $SiO_xF_y$  layer an energy threshold around 10-30 eV exists, which is in the same range as that of  $SiO_2$  [9]. In Fig. 3(b) the etching rate measured at -130 °C for different CCP settings and gas flows for a fused silica dome is shown. For CCP settings above 5 W the etching rate is independent of the CCP setting. Ion bombardment is now severe enough to remove the  $SiO_xF_y$  layer completely and therewith avoid black silicon. The dc-bias setting is ca. -15 V. The actual ion energy is larger than expected on the basis of the dc-bias value alone, because ions are accelerated from the positive plasma potential region, which has a potential of ca. +10 V. The same dc-bias values were observed with the alumina dome ICP of the Plasma-Therm SLR770 ICP Shuttlelock system when oxygen was added to  $SF_6$ .

Furthermore we observed that for higher SF<sub>6</sub> flows the CCP power required to remove the passivation layer on the bottom of the trench was lower, indicating that the composition and therewith the passivation quality of the SiO<sub>x</sub>F<sub>y</sub> layer is changed by oxygen in the plasma [9], [21] (i.e., oxygen emitted from the ICP dome). For a flow of 90 sccm SF<sub>6</sub> the required CCP value was of the order of 2 W [see Fig. 3(b)].

In Fig. 3(a) it can be seen that the strong reduction in etch rate (at the BS point) at  $-60^{\circ}$ C can be altered to lower temperatures by increasing the SF<sub>6</sub> gas flow, which is in agreement with

the BS line in Fig. 2. For higher SF<sub>6</sub> flows the relative oxygen content decreases and lower temperatures are required to find BS. This is only valid when the ICP power is not altered and the emission of oxygen is constant. For example, for a flow of 90 sccm SF<sub>6</sub> the BS point was located at -120 °C [see Fig. 3(a)].

It is, therefore, concluded that to use the oxygen flow as control parameter for cryogenic DRIE it is necessary to avoid or at least restrict the presence of fused silica as dome material. For example, when low SF<sub>6</sub> gas flows or low CCP power settings are needed in order to increase the selectivity of etching of silicon versus mask material, black silicon may occur due to oxygen from the dome. An alumina dome is indispensable to be able to define etching recipes for a broad variety of microstructures in the cryogenic temperature regime ( $-90 \,^{\circ}$ C down to  $-140 \,^{\circ}$ C). Recipes with relatively low oxygen content and ions with low kinetic energy (low self-bias) can now be applied to observe a low lateral etch rate beneath the mask, and a high selectivity with respect to polymers and oxide mask materials.

# D. Mask Material

In Fig. 4(a), two etch lines with the same anisotropy are depicted, for chromium and photoresist as mask materials. The samples are etched in the Plasma-Therm SLR770 ICP Shuttlelock system with an alumina dome. The etch line shows anisotropic etching of the 2, 4, and 8  $\mu$ m trenches, without black silicon. The fixed settings are: 750 W ICP, 7 mtorr process pressure, 100 sccm SF<sub>6</sub> gas flow, 2 W CCP, and a silicon load of 60% (on a 4-in substrate). In Fig. 4(a), it can be seen that at temperatures above -90 °C for Olin907 resist a lower oxygen content is required than for the chromium mask, indicating that polymer species originating from the photoresist are deposited on the side-walls of the trenches and contribute to the blocking layer. This effect can be explained by the erosion rate of photoresist, which increases above -90 °C. An erosion rate of 100 nm/min was measured at 0 °C. In the temperature regime lower than -90 °C no difference is observed between chromium and photoresist due to a very low erosion rate (2-10 nm/min) of photoresist.

Identical results have been observed by Tsujimoto *et al.* [19], who compared the lateral etch rate under a photoresist mask and a SiO<sub>2</sub> mask. They concluded that the lateral etch rate is decreased by the presence of photoresist, and that the lateral etch rate was identical (i.e., low) for both mask materials at -120 °C.

In Fig. 4(b), 4 and 8  $\mu$ m trenches, for chromium and photoresist as mask materials, at -120 °C show identical profiles. In Fig. 4(b) the chromium mask shows extreme bottling, while the photoresist mask shows a little bottling at a temperature of -80 °C. To make the chromium profile identical to the photoresist profile, the relative oxygen content had to be increased by 4%.

# **III. CENTERPOINT PROCESS**

The relationship between the different parameters on profile control were studied by  $10 \,\Omega$ cm boron doped 4" (100) oriented silicon wafers etching with a special chromium test mask with

(b)

Fig. 4. (a) Influences of Olin907-12 resist and chromium as mask materials on directional etching of silicon for the Plasma-Therm SLR770 ICP Shuttlelock system with alumina dome. The depicted curves are determined for 8  $\mu$ m trenches [see Fig. 4(b)]. Parameter settings: 750 W ICP, 7 mtorr, 100 sccm SF<sub>6</sub>, 2 W CCP, exposed area 60% of 4-in Si-wafer. (b) Cross section of 8- $\mu$ m-etched trenches, showing profile shape as a function of mask material, oxygen percentage and electrode temperature for the Plasma-Therm SLR770 ICP Shuttlelock system with alumina dome [parameter settings, see Fig. 4(a)].

trenches that were 1, 2, 4, 8, 16, 32, 64, or 128  $\mu$ m in width. Etching is performed in the Plasma-Therm SLR770 ICP Shuttlelock system with an alumina dome. A "center point process" was defined as that process in which an anisotropic profile is obtained for the trench with a width of 8  $\mu$ m. The settings of the centerpoint process (CP) are: 750 W ICP, 7 mtorr process pressure, 100 sccm SF<sub>6</sub> gas flow, -130 °C electrode temperature, 2 W CCP, and for all experiments a silicon load of 60% was used. This center point process was used as a reference in the study of the influence of electrode temperature (which is practically the same as the wafer temperature), helium pressure of He-backside cooling,  $SF_6$  flow,  $O_2$  flow, operating pressure, ICP power, CCP power, etching time, and wafer clamping pressure, where in each experiment all parameters but one are fixed. After each etching experiment the wafer was broken and a picture was made of the profile of the cross section with an optical microscope. The result was compared with the center point process. The anisotropy can be characterized by the angle between trench sidewall and top surface, and the type and relative rate of lateral undercut.

In Table I the impact of parameter settings on the etch result is depicted. The CP process is the dark gray column with a directional profile. The oxygen content is the most important parameter for the control of the shape of the profile. It determines mainly the passivation quality (either thickness or composition [21]–[23]) of the  $SiO_xF_y$  layer on the sidewalls. For zero oxygen content spontaneous (chemical) etching of silicon was observed, which was expressed by isotropic profiles for all trench dimens. For an oxygen content of 5%, bottling with a negative taper was observed for all trenches. Bottling, i.e., a local increase in lateral etching, mostly observed directly underneath the mask, is caused by removal of a too thin blocking layer in those areas where increased impact of ions occurs due to dispersion in the directionality of the ion trajectories, the so-called Ion Angular Distribution, IAD [17]. The negative taper of the sidewalls, which is caused by a lateral etching rate which increases with the depth of the trench, can be caused by a decreasing passivation quality of the layer with the depth of the trench (e.g., due to oxygen depletion), by an increased sidewall impact by ions, which can either be the result of ion deflection due to mirror charges on the sidewall [24] or of ion back-scattering from the trench bottom [25]. Our experiments do not lead to definitive conclusions on which of the two mechanisms is responsible for the negative taper. For an oxygen content of 9-10%, directional etching was observed for the 8- $\mu$ m trenches, a positive taper for smaller dimensions and a negative taper for wider trenches. For a content of 12% of oxygen black silicon shows up and all the profiles have a positive taper, demonstrating that the blocking process is now dominating profile control.

When the SF<sub>6</sub> flow is increased with all other parameters kept constant, the passivation quality of the layer becomes less. If the ICP power is increased, with all other parameters fixed, a similar effect is observed. Both results indicate that due to an increased SF<sub>6</sub> flow or ICP power, the Fluor-concentration is enhanced. Therefore, the percentage oxygen is decreasing and, the passivation is lowered (see Table I).

A remarkable result is observed for the experiments in which the electrode temperature is varied. Compared to the directional center point process, negatively tapered profiles with crystallographic preference are observed (see Fig. 5) when the temperature is lowered, while for a higher temperature positively tapered profiles appear. This demonstrates that under circumstances the etch rate is dependent on the crystallographic orientation. The crystallographic preference of etching in deep trenches has been reported earlier [9], [18], [22], and is enhanced at higher process pressure or lower ion energies. McFeely [26] observed that the silicon surface is covered by many mono layers thick SiF<sub>2</sub> films. He reports a tendency that at Si  $\{100\}$  more SiF<sub>2</sub> species evolve compared to Si  $\{111\}$ . SiF<sub>2</sub> is considered to be the essential intermediate etching species to form the  $SiF_4$  end product. McFeely concluded that for etching of Si  $\{111\}$  via the SiF<sub>2</sub> intermediate state a Si–Si bond should be broken, with inherently a higher activation energy and thus a lower etching rate than on Si  $\{100\}$ . This situation seems to be similar to etching silicon in wet etching using HO- containing solutions.

In general, crystallographic orientation dependent etching can occur only if the surface reaction rate plays a significant role in the overall rate, as noticed by Blauw [22]. So it might be that the removal rate of atoms is dependent on the orientation of the crystal surface, but masked by relatively slow transport of active species and etching products to and from the surface. The presence of a thin film makes this interpretation doubt full because it would hinder any transport at the surface.

It is now established that in wet etching the anisotropy of the rate is related to the fact that atoms are removed from edges of steps on otherwise flat surfaces [27]–[31]. The removal rate of an atom from a {111} terrace must be must then be slower than from a step edge. Additionally, the slowly etching orientation must be a facet below its roughening transition temperature [32]. So the etch rate might become anisotropic because of a change of the surface characteristics of the {111} faces: a roughening transition, mediated by temperature, the surface adsorption of SiF<sub>2</sub> or surface reconstruction. The presence of an adsorbed thick film would rather decrease the roughening transition temperature, so this also seems an improbable option.

We are left with the chemical mechanism which might have a change. The film certainly decreases the kinetic energy of the impinging molecules, so the physical component of the etching process might essentially be eliminated by the film. At high enough energy ion may penetrate the film still with enough kinetic energy to induce the chemical reaction at the surface. This picture points to an idea that the etching in RIE is independent of crystallographic orientation mainly due to the impact energy of the ions. Only in cases were the ion energy is sufficient low, the impact is not able to create sides (possibly just dangling bonds, but also possibly kink sites on any {111} terraces) where the chemical reaction readily can take place; i.e., crystal-oriented etching.

With respect to the negative to positive profile change, it was observed that in order to achieve a directional profile at temperatures below -130 °C, a higher oxygen content is needed. It was speculated by Zijlstra that this is due to a higher fluoride content in the passivation layer, by which the passivation layer becomes less resistant to ion impact, although in our view it can not be concluded whether this effect is caused by ion deflection or ion backscattering (see above). Furthermore, bottling may show up at higher temperatures due to the reasons discussed above. In order to find the optimal etching recipe, the temperature should preferably be fixed (e.g., at -110 °C) and only be used to perform fine-tuning of the etched profile.

The helium pressure controls the heat transfer between the wafer and the cryogenically cooled electrode, while the applied clamping pressure controls the sealing of the helium backside chamber. A *small* negative taper is observed for high clamping pressures, which can be explained by a better sealing of the helium backside chamber, and is in accordance with the effects of the temperature discussed before. The heat transfer between wafer and electrode is also enhanced by a higher He pressure, which also causes a small negatively tapered profile. Both parameters should be fixed and not used to optimize recipes.

The CCP parameter controls the removal of the  $SiO_xF_y$  layer on the walls of the trench. For relatively high CCP values (i.e., higher ion energies) a negative profile with bottling is observed,

(a)

(b)

(c)

(d)

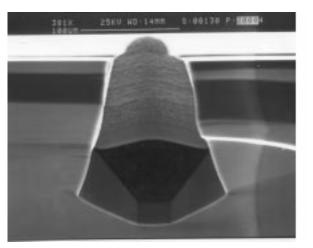

Fig. 5. Examples of crystallographically determined etching in 10  $\Omega$ cm {100}-oriented wafers. (a) {111} planes at the bottom of a trench with aspect ratio 8,

(e)

etched with OXFORD Plasmalab 100 system equipped with fused silica dome. Parameter settings: electrode temperature -120 °C, 600 W ICP, 10 mtorr, 2 W  $CCP(V_{dc} = -15 \text{ V}), 90 \text{ sccm } SF_6, 2 \text{ sccm } O_2, \text{ exposed area } 10\% \text{ of } 3\text{-in wafer. (b) Trench with square bottom, after etching of a circular hole with aspect ratio$ 4 with OXFORD Plasmalab 100 system equipped with fused silica dome for a relatively high process pressure and low CCP settings. Parameter settings: electrode temperature -120 °C, 600 W ICP, 20 mtorr, 1 W CCP ( $V_{dc} = -10$  V), 90 sccm SF<sub>6</sub> 2 sccm O<sub>2</sub>, exposed area 10% of 3-in wafer. (c) Etch pit with {111} planes after etching through circular mask openings, at relatively high pressure (30 mtorr) and zero or low CCP values. See Fig. 5(b) for other parameter settings. (d) Under etching at outside corners of freestanding structure (possibly due to differences in passivation of {111} and {100} planes) at cryogenic temperatures (-130 °C). See Fig. 5(a) for other parameter settings. (e) Crystallographic planes of undetermined orientation after needle etching, which form at low temperatures (-130 °C) and low CCP (2.5 W,  $V_{\rm dc} = -10$  V); see Table III, recipe D for other parameter setting.

(b)

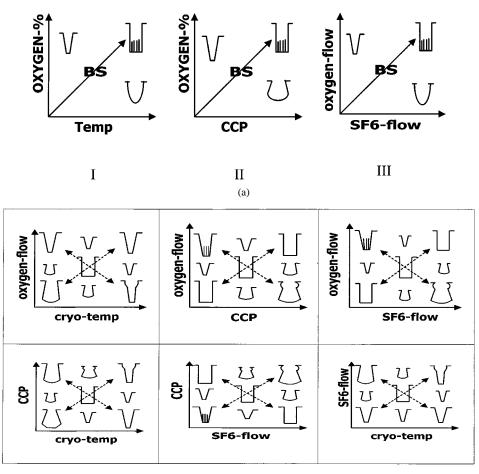

Fig. 6. (a) and (b). Trend diagrams for optimization of etched silicon profiles. The diagrams are based on the parameter ranges mentioned in Table I for the Plasma-Therm SLR770 ICP Shuttlelock system with alumina dome. In (a), diagram I is used to find the black silicon line and therewith the anisotropic region; II is used to adjust the selectivity with respect to the mask; and III to adjust the etching rate. The diagrams in (b) are used to fine-tune the profile.

TABLE II

PARAMETER SETTINGS FOR HIGH RATE ETCHING OF SILICON FOR PLASMALAB 100 PLUS SYSTEM WITH FUSED SILICA DOME. RECIPE A: BLACK SILICON AT THE BOTTOM OF THE WELL AT DEPTH 370 μm. RECIPE C: VERTICAL WELLS ARE ETCHED IN A DUMMY WAFER (SCALE 1000 μm). THE OPENING WINDOW WIDTH IS 700 μm and the Width of the Sidewall is 200 μm

| Recipe A     | Recipe B                               | Recipe C                                                              |

|--------------|----------------------------------------|-----------------------------------------------------------------------|

| 10           | 14                                     | 14                                                                    |

| 120          | 200                                    | 200                                                                   |

| 0            | 0                                      | 2                                                                     |

| 600          | 600                                    | 600                                                                   |

| 2/-16        | 2/-16                                  | 2/-16                                                                 |

| -110         | -110                                   | -110                                                                  |

| neg.<br>+ BS | TJ<br>neg.<br>bottling                 | directional                                                           |

| 1            |                                        | -                                                                     |

|              | 10<br>120<br>0<br>600<br>2/-16<br>-110 | 10 14<br>120 200<br>0 0<br>600 600<br>2/-16 2/-16<br>-110 -110<br>7 5 |

and for relatively low values a positively tapered profile is observed. This is in accordance with the observations on the negative to positive profile change described above. Black Silicon is found when the CCP is adjusted to too low values. The pressure was discussed in the section on the limits of the equipment, and is found to introduce bottling at pressures above 10 mtorr.

In conclusion, profile control is a delicate balance between etching and deposition of a  $SiO_xF_y$  layer. The passivation

| Parameters                          | Recipe A    | Recipe B      | Recipe C      | Recipe D      |

|-------------------------------------|-------------|---------------|---------------|---------------|

| p (mTorr)                           | 10          | 10            | 10            | 10            |

| SF <sub>6</sub> (sccm)              | 90          | 90            | 90            | 90            |

| $O_2$ (sccm)                        | 10          | 3             | 7             | 7             |

| ICP (Watts)                         | 600         | 600           | 600           | 600           |

| CCP (Watts)/V <sub>dc</sub> (Volts) | 3.0/-14     | 3/-14         | 3/-14         | 2.5/-10       |

| electrode temp. (°C)                | -130        | -130          | -130          | -130          |

| height (µm) /time (min)             | 2/10        | 20/10         | 29/15         | 25/15         |

| shape profile sidewall              | pos.<br>+BS | neg.<br>taper | pos.<br>taper | pos.<br>taper |

TABLE

III

PARAMETER SETTINGS FOR NEEDLE ETCHING OF SILICON FOR OXFORD PLASMALAB 100 SYSTEM WITH FUSED SILICA DOME [SEE ALSO FIG. 7(a) AND (b)]

blocking of  $SiO_xF_y$  is mainly determined by the oxygen content in the  $SF_6$  gas and the electrode temperature. Removal of the  $SiO_xF_y$  layer is mainly determined by the settings of the CCP, which adjusts the energy of the ions that bombard the etched surface.

# A. Diagrams for Profile Control

Based on the results of the CP process as explained above and in Table I, guidelines for profile control were determined and put into the trend diagrams shown in Fig. 6(a) and (b). The diagrams in Fig. 6(a) show the relations between different parameter settings for trench profile control and the conditions were anisotropic etching of silicon occurs. This is determined by locating the line of conditions at which black silicon is observed for a special mask design with a specific loading. The diagrams given in Fig. 6(b) can subsequently be used to optimize the profile of the etched structure. The ranges of the parameter settings mentioned in the diagrams are given in Table I. From the diagram oxygen-flow versus cryogenic-temperature and the diagram SF<sub>6</sub>-flow versus cryogenic- temperature it can be concluded that for high oxygen concentrations the shape of the profile is not influenced by the cryogenic temperature. Another important result is that the ratio between SF<sub>6</sub> flow-and oxygen flow and the parameter ICP and CCP give identical trends for profile control.

As was indicated in Section II-A, the ICP power can be used to change the number of fluorine species in the plasma, provided that the  $SF_6$  flow is not at such a value that it limits the etching rate, and the other way around.

Crystal-oriented etching is only observed in the diagram CCP versus cryogenic temperature, using low cryogenic temperatures and CCP values.

#### **IV. APPLICATIONS**

In this section, a couple of examples will be given to demonstrate the usefulness of the guidelines that were given in Section III. The OXFORD Plasma-lab 100-plus system with fused silica dome will be used to demonstrate the usefulness of the guidelines for certain illustrative applications.

(b)

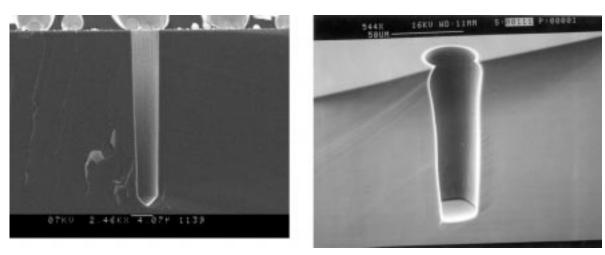

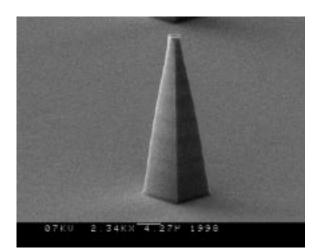

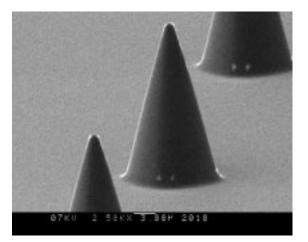

Fig. 7. (a) Scanning electron micrograph (SEM) of etched needle using recipe D (see Table III). After thermal oxidation and stripping of the oxide film a smooth and sharp (curvature less than 500 nm) needle is obtained. Angle of positive taper is ca.  $105^{\circ}$ . (b) Array of needles with a height of 50  $\mu$ m and a distance between the needles of 5  $\mu$ m. The negative tapering at the edge of the needle array is caused by incoming ions. Parameter settings: seeTable III, recipe D.

### A. High-Rate Etching of Silicon

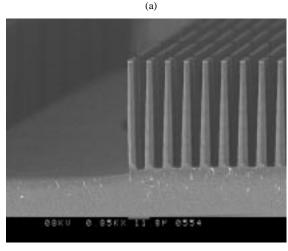

In this section the fabrication of a matrix of 700  $\mu$ m wide wells, separated by vertical silicon sidewalls are etched 500  $\mu$ m deep into a silicon-on-insulator (SOI) wafer [33]. The

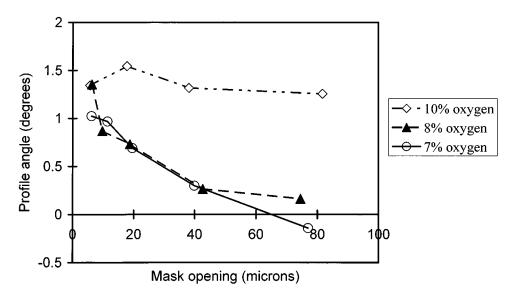

Fig. 8. Profile angle of trenches as a function of mask opening for different oxygen % in SF<sub>6</sub> for the OXFORD Plasmalab 100 system with fused silica dome. The angle is determined at a depth of 75  $\mu$ m in the trench. A value of zero at the y-axis corresponds to a perfect directional profile and a positive value to a positively tapered profile. Parameter settings: 600 W ICP, 10 mtorr, 90 sccm SF<sub>6</sub>, 7.5 W CCP ( $V_{dc} = -42$  V), mask material SiO<sub>2</sub>.

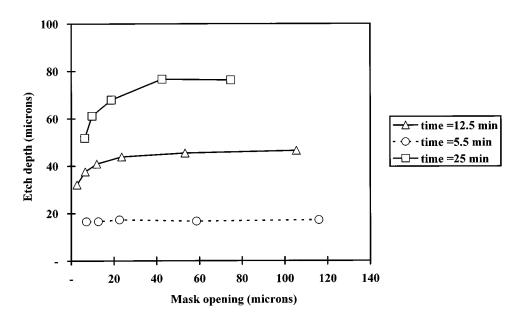

Fig. 9. Depth of etched trenches as a function of mask opening in  $\mu$ m for the OXFORD Plasmalab 100 system with fused silica dome. Parameter settings: 600 W ICP, 10 mtorr, 90 sccm SF<sub>6</sub>, 3.0 W CCP ( $V_{dc} = -30$  V), mask material SiO<sub>2</sub>. Exposed area 5% of 3-in Si-wafer.

consequence of the requirement for an etching process that should lead to steep sidewalls which are as close as possible to the normal to the substrate, and an as low as possible undercut, is the risk of the formation of black silicon, which will retard or even stop the etching. To avoid black silicon at the bottom of the trench, we decided to start with an semi-isotropic etching process and etched completely through the wafer until the oxygen layer was reached, without the formation of black silicon. Subsequently the recipe for through-the-wafer etching was tuned in order to obtain a perfect anisotropic profile. This was realized by increasing the oxygen content. This consists in fixing the parameters close to the 'black silicon region' as depicted in Fig. 6(a). A secondary criterion that has to be considered is the selectivity with respect to the oxide mask, which is 1:750. Defining Recipe A: To find the parameter settings for the Plasmalab 100-plus-system the procedure given in Section II was applied. First, the SF<sub>6</sub> gas flow was set to 100 sccm and the ICP power to 600 W to achieve a high etch rate of 5  $\mu$ m/min. The pressure has been set to a value of 10 mtorr, resulting in a small IAD, which will make the ion bombardment directional and will reduce side wall etching effects like bottling. The electrode temperature was fixed at -110 °C., because for temperatures lower than -130 °C gas condensation of SF<sub>6</sub> will take place and crystallographic oriented etching of silicon may complicate profile control. The electrode temperature should only be used for fine-tuning of the profile of the microstructure. The parameters oxygen content and CCP power are used to tune the profile and the mask selectivity. The O<sub>2</sub> gas flow has been set to 0 in order to prevent the formation of black silicon. The oxygen is now only a function of the emission of oxygen from the fused silica dome ICP, which is determined by the power settings of the ICP. The CCP power has been set to 2 W, creating a self-bias voltage of -16 V, to obtain a large etching selectivity (more than 750) between silicon and SiO<sub>2</sub>. With recipe A (Table II) we observed that the process stopped at a depth of  $\sim 370 \ \mu m$  due to the formation of black silicon. To avoid black silicon, the CCP parameter should be increased or the oxygen content of the gas mixture should be decreased. The CCP setting is no option here, because higher CCP settings create a higher erosion rate of the mask material and thereby reduce the required high selectivity. Because the flow of oxygen was already set to zero, the SF<sub>6</sub> parameter is now used to decrease the oxygen content of the gas mixture. By increasing the SF<sub>6</sub> flow from 120 to 150, 175, and 200 sccm, the etching depth reached respectively 400  $\mu$ m, 475  $\mu$ m and ca. 500  $\mu$ m, the latter being through the wafer (i.e., until the embedded oxygen layer of the SOI substrate is reached). As a result of the relatively large gas flow of 200 sccm, the pressure in the wafer chamber increased to 14 mtorr and consequently the IAD was affected, which makes sidewall etching in the form of bottling more pronounced (recipe B).

To reduce the lateral etch rate, the oxygen flow was now increased up to 2 sccm (recipe C), which resulted in through-the-wafer etching with a directional profile. The final process showed an average etch rate of 5  $\mu$ m/min and a selectivity of more than 1000 for PECVD SiO<sub>2</sub> as the mask material. The under etch is less than 10  $\mu$ m for an etch depth of 500  $\mu$ m. The under etch is defined here as the maximum lateral *deviation* in the etch profile. The surfaces of the sidewalls are relatively smooth (average roughness less than 500 nm) and the profiles of the wells show a positive tapering. These results are depicted in Table II, recipe C.

### B. Fabrication of Micro Needles

For medical applications [2] small needles were fabricated with a height of 25  $\mu$ m and base length of 20  $\mu$ m, the distance between the needles was of the order of 200  $\mu$ m [see Fig. 7(a)]. The needle was required to be mechanically robust and have positive taper  $(100^{\circ}-105^{\circ})$  with a smooth surface. The positively tapered profile of the needle was achieved by optimization of the profile by etching and adjusting the selectivity between the photoresist and silicon. Photoresist dots with a diameter of 2 micron and a thickness of 0.5 micron were hard baked at 150 °C, thereby creating a positive taper by re-flow of the photoresist during etching. The selectivity between photoresist and silicon was adjusted at 100, which was done by controlling the oxygen content and the CCP power. After etching, the needles were oxidized to increase the sharpness and the surface smoothness of the needle. In Table III the process development is summarized, which resulted in a perfect result with the final recipe. To find the settings of the directional etching of silicon for a load of 95% on a 3-in wafer, we started with recipe A in Table III and varied the oxygen content. With 10 sccm oxygen a gray surface area was observed with strongly tapered micrograss with a height of a few microns. Decreasing the oxygen flow to 3 sccm, a negatively tapered profile was observed (recipe B in Table III), an oxygen flow of 7 sccm seems to be the right value for this application. To increase the base of the needle, the CCP was re-

12KV 0.59KK 17 2F 4319

(a)

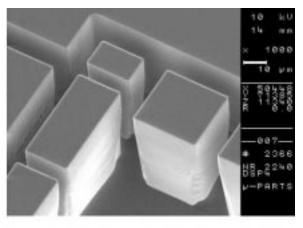

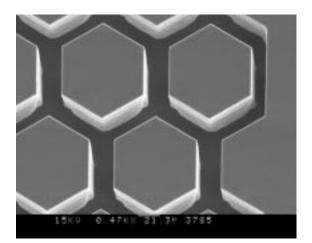

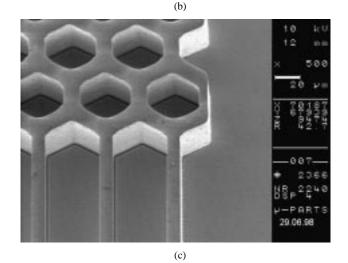

Fig. 10. (a) Etch result of recipe A (Table IV), showing a small undercut at convex corner. (b) Optimized honeycomb structure, showing positive taper for all corners (recipe D Table IV). (c) Metal mould after electroplating of Ni and stripping of Si mould.

duced to decrease the energy of the ions (recipe D in Table III). For all needles crystallographic preference during etching was observed [see Fig. 5(e)], caused by the relatively low electrode temperature  $(-130 \text{ }^{\circ}\text{C})$  and low CCP setting.

We observed that for arrays with a needle distance of 200  $\mu$ m the height of the needles is limited to 50  $\mu$ m, for higher needles the positively tapered profile changes to directional or

| Parameters                      | Recipe A    | Recipe B       | Recipe C                                                       | Recipe D                                                 |

|---------------------------------|-------------|----------------|----------------------------------------------------------------|----------------------------------------------------------|

| p (mTorr)                       | <10         | <10            | <10                                                            | <10                                                      |

| SF <sub>6</sub> (sccm)          | 90          | 90             | 90                                                             | 50                                                       |

| $O_2$ (sccm)                    | 0           | 0              | 0                                                              | 0                                                        |

| ICP (W)                         | 600         | 600            | 450                                                            | 450                                                      |

| CCP (Watts)/V <sub>dc</sub> (V) | 3.5/-16     | 3.5/-14        | 3.5/-14                                                        | 3.0/-10                                                  |

| electr. temp. (°C)              | -120        | -90            | -90                                                            | -90                                                      |

| height (µm)/<br>time (min)      | 100/30      | 103/30         | 150/60                                                         | 150/100                                                  |

| mask: hard baked (150 °C)       | S1813       | S1813          | S1818                                                          | S1818                                                    |

| shape profile                   | directional | pos.<br>taper  | directional                                                    | pos.<br>taper                                            |

| remarks                         | Fig.10a     | S1813 stripped | Higher selectivity<br>by decreasing ICP<br>(lower ion density) | Positive tapering<br>by decreasing SF<br>flow (Fig.10.b) |

TABLE IV PARAMETER SETTINGS FOR SILICON MOULD ETCHING FOR OXFORD PLASMALAB 100 SYSTEM WITH FUSED SILICA DOME [SEE ALSO FIG. 10(a) AND (b)]

negatively tapered. The reason for this effect probably is ion bowing. Ion bowing is caused by the diffraction of ions while entering a trench/needle or by the negative potential of trench walls (needle wall) with respect to the plasma glow resulting in a deflection of these ions to the wall [17], [24], [34]. In a wider needle array, ions are deflected to the walls during their trajectory resulting in a parabolic curvature of the etched wall (i.e., negatively tapered). For a smaller distance between the needles (less than 10  $\mu$ m) this phenomenon was only observed at the edge of the array [see Fig. 7(b)].

# C. Fabrication of Micromolds

Dry etching, electroplating, molding (DEEMO) is a fast and flexible production process for polymer microstructure products based on a sequence of process steps, one of which is a DRIE step [1]. The high aspect ratios, directional freedom, low roughness, high etch rates and high selectivity with respect to the mask material of DRIE allow a versatile fabrication process of micro moulds for subsequent electroplating and embossing. The feasibility of the DEEMO process has been demonstrated for feature sizes of several micrometers up to tens of micrometers [see Fig. 10(c)]. The layout of the mould inserts are etched by Cryo-DRIE into silicon, the etched structures are electroplated creating a replica of the silicon mould, and this metal replica is subsequently used for polymer embossing. In the following, design-limiting aspects of silicon mould etching will be treated by discussing examples of the DEEMO process. An important design-limiting aspect is the control over the lateral etch rate, the tapering and the depth of the structures when the mask design includes a large range of mask openings. The profile of the mould should have a slightly positive taper and no undercut to facilitate the release of the embossed microstructure. As can be seen from the profile optimization diagrams, recipes with a high oxygen content and/or low CCP settings and/or a relative high electrode temperature and/or relative low ICP power values are favored to etch profiles with a positive taper.

In Fig. 8, it is shown how the angle of the etched profiles changes with the dimension of the etched mask opening. It may

be clear from the discussion before that the range of different mask openings in a single mask design should be minimized to ensure positively tapered etching over the complete range of dimensions in the mask design. For recipes with high oxygen content the smallest deviations in the angle of the profile are observed (see Fig. 8).

Another limiting effect is the observed difference in etch depth for different mask openings, called RIE-lag. The etch rate decreases with increasing aspect ratio; large mask openings are etched deeper and faster than smaller mask openings [35] (see Fig. 9). To eliminate the RIE-lag problem, silicon-on-metal (SOM) or SOI wafers can be used, where the buried metal layer of the SOM substrate or the buried insulator of the SOI wafer is used as a planarizing etch-stop. The advantage of the use of a SOM substrate is that the buried metal layer can also be used as the contact and seed layer for electroplating and that the undercut (the so-called "notching") near the etch stop layer is smaller in SOM wafers. Availability of SOM wafers is a problem though, such substrates are to our knowledge not commercially available.

Another limiting effect is that etching at cryogenic temperatures (below -120 °C) with very low self-bias (i.e., low ion energy) may give the crystallographically determined etching in silicon, which means that circular mould shapes become impossible. This is convincingly shown in Fig. 5(b). During etching of a circular mask opening, the etched geometry has changed completely into a square.

Another example is shown in Fig. 10(a). The etched profile of the honeycomb structure tends to be more negative close to the convex corners than elsewhere in the etched structure. In this case, the local negative tapering means that demolding of plastic parts from the metal mould will become impossible. In Table IV the development of the process is summarized, which results in the desired result for 150  $\mu$ m high honeycomb structures. First the settings to obtain directional etching are defined (recipe A, Table IV) for the BSM method as described before. The process pressure should be as low as possible and below 10 mtorr to reduce lateral etching and to facilitate the release of the embossed microstructure. To create a positively tapered profile the temperature was increased to -90 °C (recipe B, Table IV). For etching times longer than 30 min the photo resist mask (S1813) was etched away. To decrease the etch rate of photoresist, the ion density was lowered by decreasing the ICP power. Also the concentration of fluorine and oxygen species are lowered by the new ICP setting thereby changing the profile to a more negative taper. The required etch depth of 150  $\mu$ m could now easily be achieved, but the etched profile of the honeycomb structure tended to be more positive close to the concave corners than elsewhere in the etched structure. To reduce the differences in etch profile the oxygen content was increased (recipe D, Table IV), thereby increasing the passivation quality of the SiO<sub>x</sub>F<sub>y</sub> layer [see Fig. 10(b)].

#### V. CONCLUSION

Guidelines for the etching of a broad variety of MEMS structures for high-density plasmas equipment at cryogenic temperatures were developed, using the black silicon method (BSM). It was demonstrated that profile control is a delicate balance between etching and deposition of an oxygen containing passivation layer, probably composed of  $SiO_xF_y$ . The passivation quality of  $SiO_xF_y$  is mainly determined by the oxygen content in the gas and the electrode temperature. Removal of the  $SiO_xF_y$ layer is mainly determined by the energy and flux of ions which bombard the surface, which can be adjusted by choosing the proper CCP settings. Parameter settings for high rate silicon bulk etching, and the fabrication of microneedles and micromoulds were given, which demonstrate the usefulness of trend diagrams for an optimal design of etched features. Also equipment limitations with respect to the maximum etch rate and anisotropic etching conditions were evaluated. It is concluded that to make use of the oxygen flow as a control parameter for cryogenic DRIE, it is necessary to avoid or restrict the presence of fused silica as the ICP dome material. For example, when low SF<sub>6</sub> gas flows or low CCP power settings are needed in order to increase the selectivity of etching of silicon versus mask material, black silicon may occur. An alumina dome allows etching recipes for a broad variety of microstructures in the cryogenic temperature regime ( $-90^{\circ}$ C down to  $-140^{\circ}$ C). Recipes with relatively low oxygen content and ions with low energy (i.e., low self-bias) can now be applied to observe a low lateral etch rate under a mask, and a high selectivity (above 500) with respect to polymers and silicon oxide mask materials.

Preferential crystallographic etching of silicon was observed, and became more prominent when a low wafer temperature was used, an effect that was enhance even more when the process pressure was increased above 10 mtorr or when lower ion energies (ca. 20 eV) were adjusted.

#### ACKNOWLEDGMENT

The authors would like to thank J. Viotty and J. Bijen, both of Alcatel Optronics Netherlands, and the staff of the MESA+ clean room for assistance.

#### References

- J. Elders and H. V. Jansen, "DEEMO: A new technology for the fabrication of microstructures," in *Proc. IEEE Workshop Micro Electro Mech. Syst.*, Amsterdam, The Netherlands, 1995, pp. 238–243.

- [2] S. Henry, D. V. McAllister, M. G. Allen, and M. R. Prausnitz, "Micromachined needles for the transdermal delivery of drugs," in *Proc. IEEE Workshop Micro Electro Mech. Syst.*, Heidelberg, Germany, 1998, pp. 464–498.

- [3] F. Laermer and D. Schilp, "Method of anisotropically etching silicon," U.S. Pat. 5 501 893.

- [4] [Online]. Available: http://www.stsystems.com

- [5] J. K. Bhardwaj and H. Ashraf, "Advanced silicon etching using high density plasmas," in *Proc. SPIE-Micromachining Microfabrication Process Technology*, vol. 2639, Austin, TX, 1995, pp. 224–233.

- [6] Tachi, K. Tsujimoto, and S. Okudaira, "Low temperature reactive ion etching and microwave plasma etching of silicon," *Appl. Phys.Lett.*, vol. 52, pp. 616–618, 1988.

- [7] M. Francou, J. S. Danel, and L. Pecoud, "Deep and fast plasma etching for silicon micromachining," *Sens. Actuators, Phys. A*, vol. 46–47, pp. 17–21, 1991.

- [8] J. W. Bartha, J. Greschner, M. Puech, and P. Maquin, "Low temperature etching of Si in high density plasma using SF<sub>6</sub>/O<sub>2</sub>," *Micro and Nano Engineering*, vol. 27, pp. 453–456, 1995.

- [9] T. Zijlstra and E. van der Drift, "Fabrication of two-dimensional photonic crystal wave guides for 1.5 μm in silicon by deep anisotropic dry etching," J. Vac. Sci Technol. B, vol. 17, pp. 2734–2739, 1999.

- [10] H. V. Jansen, M. J. de Boer, R. Legtenberg, and M. C. Elwenspoek, "The black silicon method: A universal method for determining the parameter setting of a fluorine based reactive ion etcher in deep silicon trench etching with profile control," *J. Micromech. Microeng.*, vol. 5, pp. 115–120, 1995.

- [11] M. J. M. Vugts, "Reaction Layer Dynamics in Silicon Etching," Ph.D., Physics Department, Eindhoven University of Technology, The Netherlands.

- [12] M. J. M. Vugts, L. J. F. Hermans, and H. C. W. Beijerinck, "Ion-assisted Si-XeF<sub>2</sub> etching: Temperature dependence in the range 100–1000 K," *J. Vac. Sci. Technol. A*, vol. 14, pp. 2820–2820, 1996.

- [13] , Unaxis USA, Inc., Petersburg, FL.

- [14] [Online]. Available: http://www.oxford-instruments.com/

- [15] J. T. C. Lee, N. Layadi, K. V. Guinn, H. L. Maynard, F. P. Klemens, D. E. Ibbotson, and I. Tepermeister, "Comparison of advanced plasma sources for etching applications," *J. Vac. Sci. Technol. B*, vol. 14, pp. 2510–2518, 1996.

- [16] A. Manenschijn and W. J. Goedheer, "Angular ion and neutral energy distribution in a collisional rf sheath," J. Appl. Phys., vol. 69, pp. 2923–2930, 1991.

- [17] H. V. Jansen and M. J. de Boer, "High aspect ratio trench etching for MEMS applications," in *Proc. IEEE, The Ninth Ann. Int. Workshop Micro Elec. Mech. Syst.*, San Diego, CA, 1996, pp. 250–257.

- [18] H. Jansen, M. de Boer, H. Wensink, B. Kloeck, and M. Elwenspoek, "A study of the performance of etching silicon using SF<sub>6</sub>/O<sub>2</sub>-based chemistry with cryogenically wafer cooling and a high density ICP source," *Microelectron. J.*, vol. 31, pp. 769–778, 2001.

- [19] K. Tsujimoto, S. Okudaira, and S. Tachi, "Low temperature microwave plasma etching of crystalline silicon," *Jpn. J. Appl. Phys.*, vol. 30, pp. 3319–3319, 1991.

- [20] U. Gerlach-meyer, J. W. Coburn, and E. Kay, "Ion-enhanced gas-surface chemistry of the mass of the incident ion," *Surf. Sci.*, vol. 103, pp. 177–177, 1981.

- [21] G. S. Oehrlein, S. W. Robey, and J. L. Linström, "Surface processes in CF<sub>4</sub>/O<sub>2</sub> reactive etching of silicon," *Appl. Phys. Lett*, vol. 52, pp. 1170–1172, 1998.

- [22] M. A. Blauw, T. Zijlstra, R. A. Bakker, and E. van der Drift, "Kinetics and crystal orientation dependence in high aspect ratio silicon dry etching," *J. Vac. Sci. Technol. B*, vol. 18, pp. 3453–3461, 2000.

- [23] G. Craciun, M. A. Blauw, E. van der Drift, and P. J. French, "Aspect ratio and crystallographic orientation dependence in deep dry silicon etching at cryogenic temperatures," in *Proc. The 11th Int. Conf. Solid-State Sensors Actuators*, Munich, Germany, June 10–14, 2001, pp. 612–615.

- [24] J. C. Arnold and H. H. Sawin, "Charging of pattern features during plasma etching," J. Appl. Phys., vol. 70, pp. 5314–5314, 1991.

- [25] K. Tsutsui, E. L. Hu, and C. D. W. Wilkinson, "Controlling the profile of nano structures," J. Vac. Sci. Technol. B, vol. 11, p. 2233, 1993.

- [26] F. R. McFeely, J. F. Morar, and F. J. Himpsel, "Soft X-ray photo-emission study of the silicon-fluorine etching reaction," *Surface Sci.*, vol. 165, pp. 277–287, 1986.

401

- [27] P. Allongue, V. Costa-Kieling, and H. Gerischer, "Etching of silicon in NaOH solutions," J. Electrochem. Soc., vol. 140, pp. 1009–1018, 1993.

- [28] R. A. Wind and M. A. Hines, "Macroscopic etch anisotropies and microscopic reaction mechanisms: A micro machined structure for the rapid assay of etchant anisotropy," *Surface Sci.*, vol. 460, pp. 21–38, 2000.

- [29] F. C. Frank, Growth and Perfection of Crystals, R. H. Doremus, B. W. Roberts, and D. Turnbull, Eds. New York: Wiley, 1958, p. 411.

- [30] M. Elwenspoek, "On the mechanism of anisotropic etching of silicon," J. Electrochem. Soc., vol. 140, p. 2075, 1993.

- [31] E. van Veenendaal, A. J. Nijdam, J. van Suchtelen, K. Sato, J. G. E. Gardeniers, W. J. P. van Enckevort, and M. Elwenspoek, "Simulation of anisotropic wet chemical etching using a physical model," *Sens. Actuators*, vol. 84, pp. 324–329, 2000.

- [32] E. van Veenendaal, "From an Atomistic to a continuum Description of Crystal Growth," Ph.D., University of Nijmegen, 2001.

- [33] C. P. Allier, R. W. Hollander, C. W. E van Eijk, P. M. Sarro, M. de Boer, J. B. Czirr, J. P. Chaminade, and C. Fouassier, "Thin photodiodes for a neutron scintillator-silicon well detector," *IEEE Trans. Nuclear Sci.*, vol. 48, pp. 1154–1157, 2001.

- [34] M. Elwenspoek and H. Jansen, *Silicon Micromachining*. Cambridge, U.K.: Cambridge University Press, 1998.

- [35] H. V. Jansen, M. J. de Boer, R. Wiegerink, N. Tas, E. Smulders, C. Neagu, and M. Elwenspoek, "RIE lag in high aspect ratio trench etching of silicon," *Microelectron. Eng.*, vol. 35, pp. 45–50, 1997.

Meint J. de Boer joined the Company SENTRON in 1982 as a Process Engineer, where he worked in the field of pH-sensors and pressure sensors for medical applications. In 1988, he joined the University of Groningen at the Department of Applied Physics. He focused on nano-engineering for fundamental research on superconductivity. In 1992, he joined the Transducer Science Technology Group at the University of Twente, The Netherlands. His current research interests include micromachining fabrication technology and dry-etching techniques.

**J. G. E. ("Han") Gardeniers** was born on October 15, 1960, in Valkenburg aan de Geul, The Netherlands. He received the B.Sc. and M.Sc. degrees in chemistry and the Ph.D. degree in physics from the University of Nijmegen, The Netherlands, in 1982, 1985, and 1990, respectively.

In 1990, he joined the Department of Electrical Engineering at the University of Twente, The Netherlands, as an Assistant Professor. After a short period as a Project Leader of MEMS at Kymata Netherlands B.V. (currently, Alcatel Optronics Netherlands), he

joined Micronit Microfluidics B.V. in September 2001, where he is responsible for R&D projects related to miniaturized chemical analysis and synthesis systems.

**Henri V. Jansen** received the M.Sc. and Ph.D. degrees in electronic engineering from the University of Twente, The Netherlands, in 1991 and 1996, respectively.

After working for half a year at CSEM, Neuchâtel, Switzerland, as a Plasma Engineer, he rejoined the Department of Electrical Engineering at the University of Twente, The Netherlands, as a Postdoctoral Fellow. In 2000, he joined IMEC in Leuven, Belgium, to assist in the development of RF MEMS to be used in cellular phones. Since September 2001,

he has been an Assistant Professor at the Department of Electrical Engineering at the University of Twente, The Netherlands. His main research expertise is in silicon-based micromachining, in general, and plasma engineering, in particular, with applications in the field of miniaturized sensor and actuator systems.

**Edwin Smulders** was born in 1966 in Tilburg, The Netherlands. He received the M.Sc. degree in experimental physics at Utrecht State University, The Netherlands, in 1991 and became fascinated by microsystems during a postgraduate course at the University of Twente, The Netherlands, in 1994.

After a number of years as a scientific worker at this university, he has continued his career in commercial companies and currently works at JDS Uniphase (Eindhoven, NL) on the manufacturing automation of optical network components.

**Melis-Jan Gilde** was born in 1968 and received the degree in chemical process technology from Utrecht Polytechnic, The Netherlands.

From 1992 to 1998, he worked as Technical Assistant for different research groups in the fields of inorganic materials science, integrated optics, and microsystem technology. These groups were all related to the MESA+ Research Institute of the Twente University. In 1997, he joined Twente Micro Products, which in 2000, was acquired by Kymata, Ltd., of Scotland and in 2001 by Alcatel Optronics,

where he is a Senior Process Engineer.

Gerard Roelofs was born in June 1959. He studied chemical technology at the polytechnic in Enschede and graduated in 1985.

From 1985 to 1987, he worked at Philips Eindhoven as a Technical Assistant. Since 1987, he has been employed at the University of Twente, first as a Technical Assistant, and since 1998, as MESA+ Clean Room Lab Coordinator. He is responsible for the technical part of the dry-etch equipment of MESA+.

**Jay N. Sasserath** received the B.S. degree in chemical engineering, Rensselaer Polytechnic Institute, Troy, NY, in May 1984 and the M.S. and Ph.D. degrees in materials science, SUNY Stony Brook, Stony Brook, NY, in May 1987 and May 1990, respectively.

He is a Principal with Market Quest Consulting, a marketing consulting firm that focuses on strategic and tactical marketing issues related to high-technology products. Prior to this, he was Vice President and Business Unit Director for Unaxis' MEMS and Compound Semiconductor Business Unit. Here, he had profit and loss responsibility for this Business Unit, which has operations in the United States and Europe. Previously, he held management positions in Marketing, Engineering, Customer Service, and Process Applications at Materials Research Corporation. Prior to Materials Research Corporation, he worked in various semiconductor fabrication facilities as a process engineer at both Hypres, Inc., and Standard Microsystems Corporation.

**Miko Elwenspoek** (M'94–A'95) was born on December 9, 1948 in Eutin, Germany. He received the degree in physics from the Free University of Berlin (West), Germany. His Master thesis dealt with Raleigh scattering from liquid glycerol using light coming from a Mössbauer source. From 1977 to 1979, he worked with Prof. Helfrich on lipid double layers. In 1979, he began his Ph.D. work with Prof. Quitmann on the subject: relaxation measurements on liquid metals and alloys, in particular alkali metal alloys. In 1983, he received the Ph.D. degree from

the Freie Universität Berlin.