# Hardware Acceleration of the Robust Header Compression (RoHC) Algorithm

Mohammed Al-Obaidi, aso10mma@student.lu.se Harshavardhan Kittur, aso10hki@student.lu.se

August 28, 2012

This Page is Intentionally Left Blank

#### Preface

This Masters thesis summarizes our research work carried out at Ericsson AB, Linkoping, in close collaboration with Product Development Unit LTE. The main contributions for this thesis are:

- Hardwaware-Software Codesign of RoHC by Harshavardhan Kittur.

- Full Hardware Design of RoHC by Mohammed Al-Obaidi.

#### Acknowledgements

This thesis was made available and financially supported by Ericsson AB in Linköping. We are grateful to Stefan Backlund, who gave us the opportunity to do this thesis, and provided us with all the needful to make our work in Ericsson AB smooth and pleasant.

The writing of this thesis was one of the most significant challenge in our academic life. Without the support, guidance, and patience of the following people it would not have been done at this quality. Our deepest gratitude to all the people who helped us throughout this thesis.

- Our two supervisors, Håkan Anderson in Ericsson AB-Linköping and Professor Viktor Öwall in Lund university, who helped us to hurdle all the obstacles during this thesis. We appreciate their time and patience in correcting the writing of this report. We are so happy for getting the chance to work with them in this project and we will never forget their sincere concern and patience.

- Bo Eriksson and Niclas Hallqwist in Ericsson AB-Linköping, who attended our weekly supervision meetings, provided us with their advices, and were always confident of our work.

- John Fong and Adrian Turcanu from Ericsson AB-Ottawa, who helped us getting familiar with the RoHC algorithm, and patiently answered our questions.

- Göran Westerlund and Adam Ashby from Altera, who provided us with the FPGA board.

- Orges Balla and Johan Karlsson, whose feedbacks on the report were highly appreciated.

- Last but not the least, many thanks to our families and friends for their support, inspiration, and love.

#### Abstract

With the proliferation of Long Term Evolution (LTE) networks, many cellular carriers are embracing the emerging field of mobile Voice over Internet Protocol (VoIP). The robust header compression (RoHC) framework was introduced as a part of the LTE Layer 2 stack to compress the large headers of the VoIP packets before transmitted over LTE IP-based architectures. The headers, which are encapsulated Real-time Transport Protocol (RTP)/User Datagram Protocol (UDP)/Internet Protocol (IP) stack, are large compared to the small payload. This header-compression scheme is especially useful for efficient utilization of the radio bandwidth and network resources.

In an LTE base-station implementation, RoHC is a processing-intensive algorithm that may be the bottleneck of the system, and thus, may be the limiting factor when it comes to number of users served. In this thesis, a hardware-software and a full-hardware solution are proposed, targeting LTE base-stations to accelerate this computationally intensive algorithm and enhance the throughput and the capacity of the system. The results of both solutions are discussed and compared with respect to design metrics like throughput, capacity, power consumption, chip area and flexibility. This comparison is instrumental in taking architectural level trade-off decisions in-order to meet the present day requirements and also be ready to support future evolution.

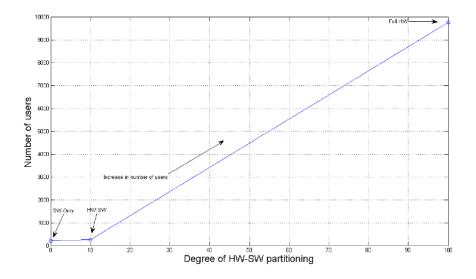

In terms of throughput, a gain of 20% (6250 packets/sec can be processed at a frequency of 150 MHz) is achieved in the HW-SW solution compared to the SW-Only solution by implementing the Cyclic Redundancy Check (CRC) and the Least Significant Bit (LSB) encoding blocks as hardware accelerators . Whereas, a Full-HW implementation leads to a throughput of 45 times (244000 packets/sec can be processed at a frequency of 100 MHz) the throughput of the SW-Only solution. However, the full-HW solution consumes more Lookup Tables (LUTs) when it is synthesized on an Field-Programmable Gate Array (FPGA) platform compared to the HW-SW solution. In Arria II GX, the HW-SW and the full-HW solutions use 2578 and 7477 LUTs and consume 1.5 and 0.9 Watts, respectively. Finally, both solutions are synthesized and verified on Altera's Arria II GX FPGA.

## Contents

| 1        | Intr                                     | roduction                                                                                                                                            | 1  |  |  |  |

|----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| <b>2</b> | Background of RoHC in LTE System         |                                                                                                                                                      |    |  |  |  |

| 3        | Summary of RoHC Framework Specifications |                                                                                                                                                      |    |  |  |  |

|          | 3.1                                      | Classification of Header Fields                                                                                                                      | 6  |  |  |  |

|          | 3.2                                      | Profiles                                                                                                                                             | 7  |  |  |  |

|          | 3.3                                      | Compressor and Decompressor                                                                                                                          | 8  |  |  |  |

|          | 3.4                                      | Modes                                                                                                                                                | 8  |  |  |  |

|          |                                          | 3.4.1 Unidirectional Mode (U-mode)                                                                                                                   | 9  |  |  |  |

|          |                                          | 3.4.2 Bidirectional Optimistic Mode (O-mode)                                                                                                         | 9  |  |  |  |

|          |                                          | 3.4.3 Bidirectional Reliable Mode (R-mode)                                                                                                           | 10 |  |  |  |

|          | 3.5                                      | Compressor States                                                                                                                                    | 10 |  |  |  |

|          | 3.6                                      | Decompressor States                                                                                                                                  | 11 |  |  |  |

|          | 3.7                                      | Encoding Methods                                                                                                                                     | 12 |  |  |  |

|          |                                          | 3.7.1 LSB Encoding                                                                                                                                   | 12 |  |  |  |

|          |                                          | 3.7.2 Scaled RTP Timestamp Encoding                                                                                                                  | 13 |  |  |  |

|          |                                          | 3.7.3 Timer-based RTP Timestamp Compression                                                                                                          | 14 |  |  |  |

|          |                                          | 3.7.4 IP-ID Offset Encoding                                                                                                                          | 14 |  |  |  |

|          |                                          | 3.7.5 Self-Describing Variable Length Code (SDVL) Encoding                                                                                           | 15 |  |  |  |

|          | 3.8                                      | CRC                                                                                                                                                  | 15 |  |  |  |

|          | 3.9                                      | Major RoHC Packet Types                                                                                                                              | 16 |  |  |  |

| <b>4</b> | Des                                      | ign of RoHC Hardware Accelerators                                                                                                                    | 18 |  |  |  |

|          | 4.1                                      | CRC Hardware Accelerator                                                                                                                             | 18 |  |  |  |

|          |                                          | 4.1.1 Design of Parallel CRCs                                                                                                                        | 20 |  |  |  |

|          | 4.2                                      | Least Significant Bit Encoding (LSB Encoding)                                                                                                        | 21 |  |  |  |

|          |                                          | 4.2.1 Case 1 when $(value < vref) \dots \dots$ | 23 |  |  |  |

|          |                                          | 4.2.2 Case 2 when $(value > vref)$                                                                                                                   | 24 |  |  |  |

|          |                                          | 4.2.3 Hardware Implementation of LSB Encoding                                                                                                        | 25 |  |  |  |

| <b>5</b> | нм                                       | 7-SW Solution                                                                                                                                        | 29 |  |  |  |

|          | 5.1                                      | Introduction                                                                                                                                         | 29 |  |  |  |

|   | 5.2  | Portin  | g of RoHC to FPGA 30                                                                                                        |

|---|------|---------|-----------------------------------------------------------------------------------------------------------------------------|

|   | 5.3  | Profili | ng                                                                                                                          |

|   |      | 5.3.1   | Valgrid                                                                                                                     |

|   |      | 5.3.2   | Altera based Performance Counters                                                                                           |

|   | 5.4  | Algori  | thmic Partitioning between Hardware and Software                                                                            |

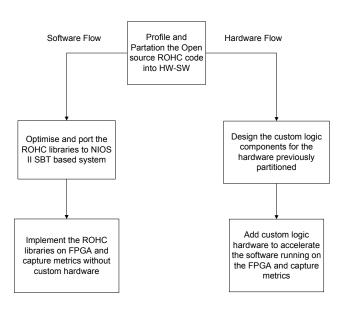

|   | 5.5  | HW-S    | W co-design flow for a RoHC system                                                                                          |

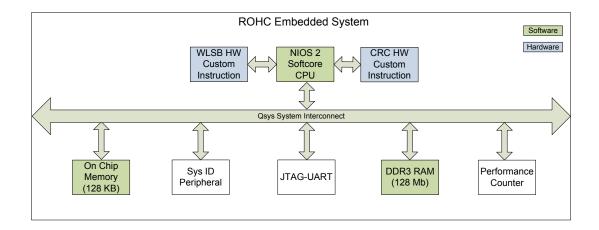

|   | 5.6  | RoHC    | Embedded System                                                                                                             |

|   | 5.7  | Qsys S  | ystem Interconnect                                                                                                          |

|   | 5.8  | Custor  | n Logic Instructions vs Custom Logic Peripherals                                                                            |

|   | 5.9  |         | are Accelerators in RoHC System                                                                                             |

|   |      | 5.9.1   | Mixed data-width CRC Hardware Accelerator                                                                                   |

|   |      | 5.9.2   | CRC Hardware Accelerator Architecture                                                                                       |

|   |      | 5.9.3   | WLSB Hardware Accelerator                                                                                                   |

|   | 5.10 | Fast p  | rototyping on an FPGA                                                                                                       |

|   |      |         | W co-verification                                                                                                           |

|   |      |         | s                                                                                                                           |

|   |      | 5.12.1  | RoHC Throughput                                                                                                             |

|   |      |         | RoHC Capacity                                                                                                               |

|   |      | 5.12.3  | Memory                                                                                                                      |

|   |      |         | Area                                                                                                                        |

|   |      | 5.12.5  | Power Consumption                                                                                                           |

|   | 5.13 | Observ  | vations                                                                                                                     |

|   |      |         |                                                                                                                             |

| 6 |      |         | Solution 46                                                                                                                 |

|   | 6.1  |         | uction $\ldots \ldots 46$ |

|   | 6.2  |         | Implementation-Specific Parameters                                                                                          |

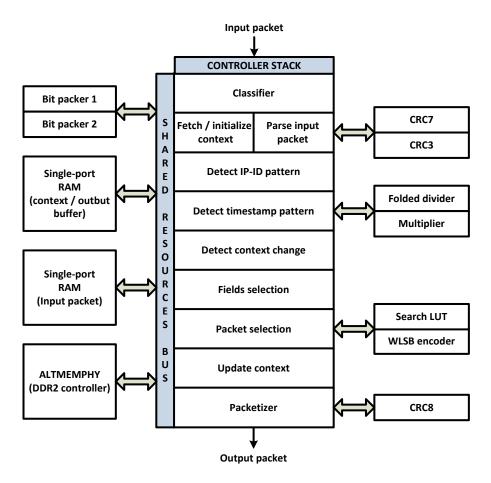

|   | 6.3  |         | vel Architecture of the One-Stage Full-HW Implementation 47                                                                 |

|   |      | 6.3.1   | Classifier                                                                                                                  |

|   |      | 6.3.2   | Fetching or Initializing The Context                                                                                        |

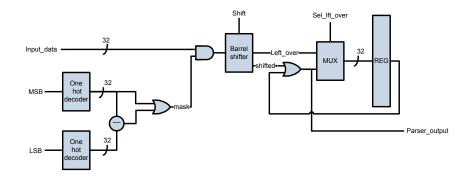

|   |      | 6.3.3   | Parsing The Input Packet                                                                                                    |

|   |      | 6.3.4   | Detecting IP-ID Pattern                                                                                                     |

|   |      | 6.3.5   | Detecting RTP Pattern                                                                                                       |

|   |      | 6.3.6   | Detecting Context Change                                                                                                    |

|   |      | 6.3.7   | Fields Selection                                                                                                            |

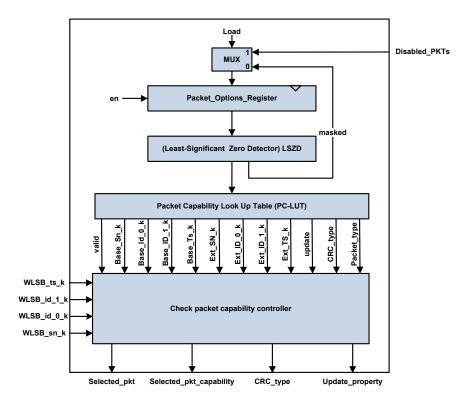

|   |      | 6.3.8   | Packet Selection                                                                                                            |

|   |      | 6.3.9   | Update Context                                                                                                              |

|   |      |         | Packetizer                                                                                                                  |

|   | 6.4  |         | tages Pipeline Architecture                                                                                                 |

|   | 6.5  |         | s65                                                                                                                         |

|   |      | 6.5.1   | Throughput and Capacity                                                                                                     |

|   |      | 6.5.2   | Memory Bandwidth                                                                                                            |

|   |      | 6.5.3   | Area                                                                                                                        |

|   |      | 6.5.4   | Power Consumption                                                                                                           |

|   | 6.5.5     | Execution Time                      | 67 |

|---|-----------|-------------------------------------|----|

| 7 | Comparise | on between Different RoHC Solutions | 69 |

| 8 | Conclusio | ns                                  | 71 |

# List of Figures

| 2.1                                                                   | RoHC in the LTE protocol architecture          | 3                                                                                                         |

|-----------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                | VoIP packet header fields                      | 7<br>8<br>9<br>10<br>11<br>13                                                                             |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array} $             | Parallel CRC                                   | 18<br>19<br>21<br>28                                                                                      |

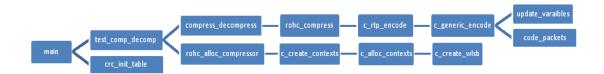

| 5.12                                                                  | Software function tree                         | $\begin{array}{c} 31 \\ 32 \\ 33 \\ 33 \\ 34 \\ 35 \\ 36 \\ 37 \\ 38 \\ 39 \\ 41 \\ 41 \\ 42 \end{array}$ |

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \end{array}$ | Top-level architecture of the full-HW solution | 48<br>51<br>53<br>56<br>60<br>61                                                                          |

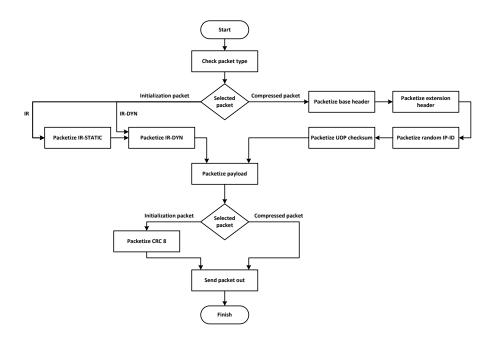

| 6.7  | Packetizer flow chart                                                      | 63 |

|------|----------------------------------------------------------------------------|----|

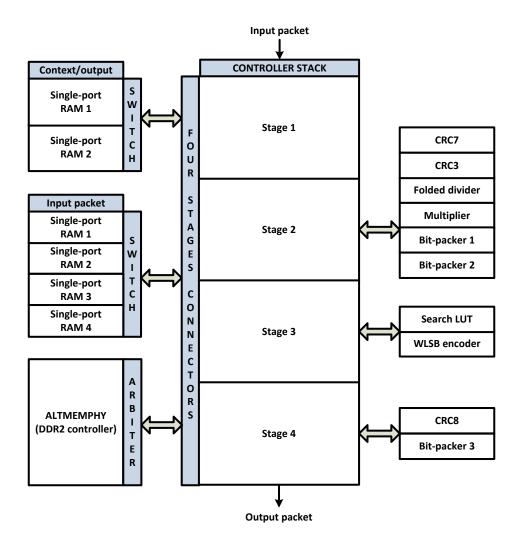

| 6.8  | Four stage pipeline architecture                                           | 64 |

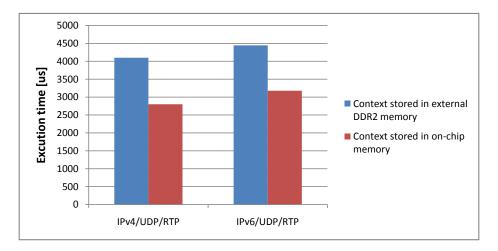

| 6.9  | Effects of external DDR2 memory on the execution time of different pro-    |    |

|      | tocol stacks                                                               | 66 |

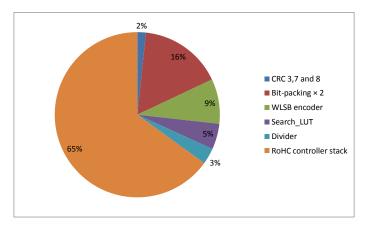

| 6.10 | Analysis of area, power consumption, and execution-time results $\ldots$ . | 68 |

| 7.1  | Comparison between different full-HW designs with respect to one packet    |    |

|      | execution time.                                                            | 70 |

| 8.1  | RoHC Performance Graph with respect to the HW-SW partitioning degree       | 71 |

# List of Tables

| 2.1 | RoHC compression gain                                           | 4  |

|-----|-----------------------------------------------------------------|----|

| 3.1 | SVDL Encoding                                                   | 15 |

| 3.2 | RoHC packets and their capabilities                             | 17 |

| 4.1 | Different CRC Methods                                           | 19 |

| 4.2 | H1 Matrix                                                       | 20 |

| 4.3 | H2 Matrix                                                       | 20 |

| 4.4 | Parametrization of the shifting value $p$                       | 22 |

| 5.1 | HW-SW implementation features                                   | 30 |

| 5.2 | Logic utilization of components of RoHC embedded system         | 44 |

| 5.3 | Power consumption of components of RoHC embedded system         | 45 |

| 6.1 | Full-HW implementation features                                 | 46 |

| 6.2 | RoHC implementation parameters                                  | 47 |

| 6.3 | Initialization of context fields                                | 52 |

| 6.4 | One-stage Full-HW implementation results of RoHC compressor     | 65 |

| 7.1 | Comparsion between one-stage full-HW, HW-SW, and SW-only imple- |    |

|     | mentations                                                      | 70 |

# List of Abbreviations

| 3GPP          | 3rd Generation Partnership Project |

|---------------|------------------------------------|

| ALMs          | Adaptive Logic Modules             |

| ALUT          | Altera Lookup Table                |

| BER           | Bit Error Rates                    |

| CISC          | Complex Instruction Set Computer   |

| CRC           | Cyclic Redundancy Check            |

| CSRC          | Contributing Source Identifier     |

| FIFO          | First-In First-Out                 |

| FO            | First Order                        |

| FPGA          | Field-Programmable Gate Array      |

| $\mathbf{FS}$ | Field Selection                    |

| HAL           | Hardware-Abstraction Layer         |

| IETF          | Internet Engineering Task Force    |

| IP            | Intellectual Property              |

| IP            | Internet Protocol                  |

| IP-ID         | Internet Protocol-Identification   |

| IR            | Initialization and Refresh         |

| LOD           | Leading-One Detector               |

| LSB           | Least Significant Bit              |

| LSZD          | Least Significant Zero Detector    |

| LTE           | Long Term Evolution                |

| LUT           | Lookup Table                       |

|               |                                    |

| MM            | Avalon Memory Maped                          |

|---------------|----------------------------------------------|

| NBO           | Network Byte Order                           |

| O-mode        | Bidirectional Optimistic Mode                |

| PDCP          | Packet Data Convergence Protocol             |

| R-mode        | Bidirectional Reliable Mode                  |

| RoHC          | Robust Header Compression                    |

| RR            | Receiver Report                              |

| RTCP          | RTP Control Protocol                         |

| RTP           | Real-time Transport Protocol                 |

| RTP-SN        | Real-time Transport Protocol-Sequence Number |

| RTP-TS        | Real-time Transport Protocol-Timestamp       |

| SBT           | Software Build Tools                         |

| SDVL          | Self-Describing Variable Length              |

| SN            | Sequence Number                              |

| SO            | Second Order                                 |

| SR            | Sender Report                                |

| SSRC          | Synchronization Source Identifier            |

| $\mathbf{ST}$ | Avalon streaming                             |

| SW            | Sliding-Window                               |

| TS            | Timestamp                                    |

| U-mode        | Unidirectional Mode                          |

| UDP           | User Datagram Protocol                       |

| UID           | User ID                                      |

| VoIP          | Voice over Internet Protocol                 |

| vref          | Reference value                              |

| WLSB          | Window-based LSB                             |

This Page is Intentionally Left Blank

# Chapter 1

## Introduction

With many cellular carriers following the evolution of telephony over the internet, they are now seriously considering transmission of voice over all IP based LTE networks via VoIP. It is a known problem that VoIP packets transmitted via the RTP/UDP/IP stack, have relatively small payloads compared to the overhead of the packet headers enclosed by the respective protocol stack. The header overhead is about 40-60 bytes (depending on IPv4 or IPv6 respectively) while the minimum size payload is 20 bytes, which creates 200-300% overhead. This overhead is expensive, especially on radio links that are affected by high Bit Error Rates (BER). Here, efficient utilization of the sparse radio bandwidth for useful payload data is of utmost importance. Redundant packet-header data in the stream is a waste of resources. This creates a need for some kind of header-compression technique for efficient utilization of the bandwidth and network resources to deliver a unit of payload data.

The RoHC framework was introduced by the Internet Engineering Task Force (IETF) in [1] and adopted by the 3rd Generation Partnership Project (3GPP) as a solution to this problem. This header-compression method is based on the principle that there is a significant redundancy between the headers of packets belonging to the same stream. By sending the static information of the header fields initially and then continuously sending only the dynamic parts of the headers, the size of the headers can be compressed significantly. The major advantage of RoHC over other header-compression techniques is its robustness. It can tolerate packet loss and residual errors on the link without losing additional packets or introducing additional errors.

Traditional base-stations have implementations in software, with some parts accelerated in hardware. In [2], a profiling of the most complex algorithms in LTE layer 2 was done using an ARM-based mobile hardware platform and with LTE data rates of about 100 Mbps. It was shown that the traditional hardware-software partitioning is not a tractable solution anymore and a new, sophisticated partitioning is needed. It was shown that the Packet Data Convergence Protocol (PDCP) sub-layer was the most computationally intensive in LTE Layer 2. Moreover, it was shown that the RoHC algorithm is taking most of the processing power (71%) in this sub-layer, which makes it a suitable target for hardware acceleration. In [3], an analysis of the memory bandwidth requirements was done and the hardware implementation of some RoHC functions was proposed. The authors showed that, in the next generation of mobile networks, network processors need to be augmented with more hardware in order to support the processing complexity of the RoHC algorithm.

Also, for base stations to support high capacity (number of users), there is a hard deadline on the computation of different algorithms. RoHC can be considered one of the performance-critical algorithms in the LTE stack. In this thesis, a Hardware-Software codesign and a Full Hardware-based solution are proposed to determine the improvement in the performance with respect to the degree of the HW-SW partitioning. Both solutions are targeting the RoHC algorithm in the LTE base stations.

The rest of this report is organized into eight chapters. In chapter 2, RoHC is discussed with respect to the LTE protocol stack and in chapter 3, the RoHC framework is briefly reviewed. In chapter 4, the design of hardware accelerators that are used in both solutions are discussed. In chapter 5, the HW-SW co-design of RoHC and the corresponding results are discussed. In chapter 6, the full hardware implementation of this algorithm is presented. Subsequently, results from both solutions are compared and presented in chapter 7. Finally, the conclusions are drawn in chapter 8.

## Chapter 2

## Background of RoHC in LTE System

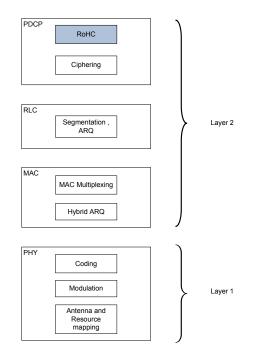

Figure 2.1: RoHC in the LTE protocol architecture

LTE is the fourth generation of high-speed and high-capacity wireless communication standards for mobile and data terminals specified by the release of the 3GPP standard [4]. The protocol architecture is bifurcated into control-plane which deals with signaling and control functions, and data-plane, which deals with the actual user data transmission. RoHC is the standard for header compression as proposed by IETF [1]. RoHC resides

#### Table 2.1: RoHC compression gain

| Protocol stack | Uncompressed header size (bytes) | Min. Compressed header size (bytes) | Compression gain(%) |

|----------------|----------------------------------|-------------------------------------|---------------------|

| IPv4/TCP       | 40                               | 4                                   | 90                  |

| IPv4/UDP       | 28                               | 1                                   | 96                  |

| IPv4/UDP/RTP   | 40                               | 1                                   | 97.5                |

| IPv6/TCP       | 60                               | 4                                   | 93                  |

| IPv6/UDP       | 48                               | 3                                   | 93                  |

| IPv6/UDP/RTP   | 60                               | 3                                   | 95                  |

in the PDCP sub-layer 2 in the data-plane of the LTE protocol architecture, as shown in Figure 2.1 [5].

The major use of the RoHC framework is to compress the relatively large packet header, which would be a big overhead especially for small packets like VoIP packets, in-order to ensure efficient use of the radio interface and the available bandwidth. LTE is an all IP-based system where data are transmitted over a packet-switched networks to support a wide range of services in mobile handsets, VOIP is one of these services. IP-based traffic on radio links suffers high packet losses because of high bit error rates. Since the RoHC algorithm is designed to robustly handle the bad channel conditions, it is specifically useful in the wireless IP-based networks.

Real-time traffic like voice in VoIP packets, which are encapsulated in the IP/UDP/RTP protocol stack, has header sizes of 40 bytes (20 bytes for IPv4, 8 bytes for UDP, 12 bytes for RTP) to 60 bytes (40 bytes for IPv6, 8 bytes for UDP, 12 bytes for RTP) and the pavload size is about 20 bytes (G.729 @ 8 Kbps) to 160 bytes (G.711 @ 64 Kbps)  $^1$ depending on the type of encoding used. Thus, the header creates a large overhead but by using RoHC, the 40-60 byte header can be reduced down-to 1-3 bytes and thereby considerably reducing the overhead. The typical compression ratios for different protocol header is as shown in Table 2.1. We see that RoHC is most beneficial to compress VoIP packets encapsulated in IP/UDP/RTP headers.

RoHC is a new emerging field that has been studied recently after it was adopted by the LTE system. In [2], the LTE layer 2 protocols was processed on an ARM based mobile architecture to identify the most time critical algorithms. A single ARM1176 core processor was used to implement most of the layer 2 protocols in software whereas only the ciphering algorithm is accelerated in hardware. This hardware-software partitioning is a traditional implementation in current mobile handset architectures. It was shown by [2] that the layer 2 performance was limited by the computation power of the single-core processor and this traditional partitioning need to be changed to cope with the LTE requirements of layer 2 in next generation mobile devices. Moreover, It was shown that a major part of the computation power (71%) in LTE L2 protocol stack is consumed by the PDCP sub-layer. In the PDCP sub-layer, RoHC is identified as the major consumer of the computation power (71%) when the encryption in the PDCP

<sup>&</sup>lt;sup>1</sup>http://www.cisco.com/en/US/tech/tk652/tk698/technologies\_tech\_note09186a0080094ae2. shtml

sub-layer is disabled.

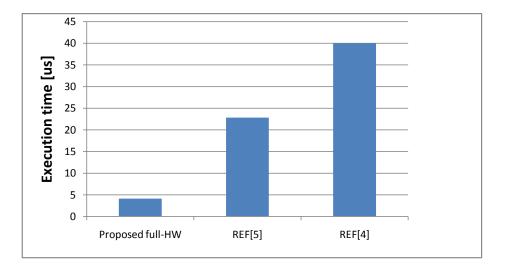

In [6], two implementations of RoHC, hardware and software, are presented by the same authors as in [2]. The effects of different cache sizes on the execution time of both solutions were studied. It was shown in [6] that the maximum performance and power saving were achieved with an instruction and data cache size of 16 kB in the embedded processor. Whereas, an improvement of 80% was achieved when the dedicated hardware accelerator is used with a relatively small cache compared to the software solution. The best execution time achieved by the dedicated hardware is around 40  $\mu s$  whereas the software solution can process one packet in 80 $\mu s$ .

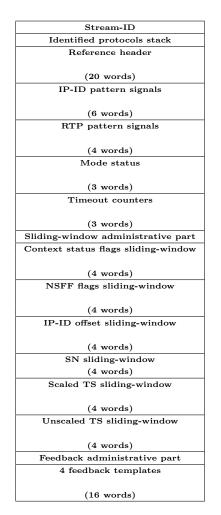

In [3], a hardware acceleration of the main encoding method used in RoHC, LSB Encoding, is proposed. An analysis of the memory bandwidth requirement and its implication on the performance of the next generation network processors is studied. It was shown that a memory size of almost 264 bytes are required in the compressor side for each user. The analysis in [3] showed that in order to support a link speed of 2.5 Gbps, a memory bandwidth of 42 Gbps is needed. This bring the attention to the memory-bandwidth as one of the limiting factors in supporting high speed links.

Although many authors, such as in [2] and [3], have concluded that RoHC is needed to be accelerated in hardware, the industrial market for RoHC is still in pure software. In [7], a software implementation of RoHC is presented based on Intel microprocessor. Even with the use of a powerful Complex Instruction Set computer(CISC) such as Pentium 4, the number of flows that can be processed in [7] with a 100% processor load did not exceed the 13k packet flows. Thus we can expect that the industrial market of RoHC will follow the scientific recommendations soon, at least from the base station side which has to cater to a full capacity and support a large number of users.

## Chapter 3

## Summary of RoHC Framework Specifications

#### 3.1 Classification of Header Fields

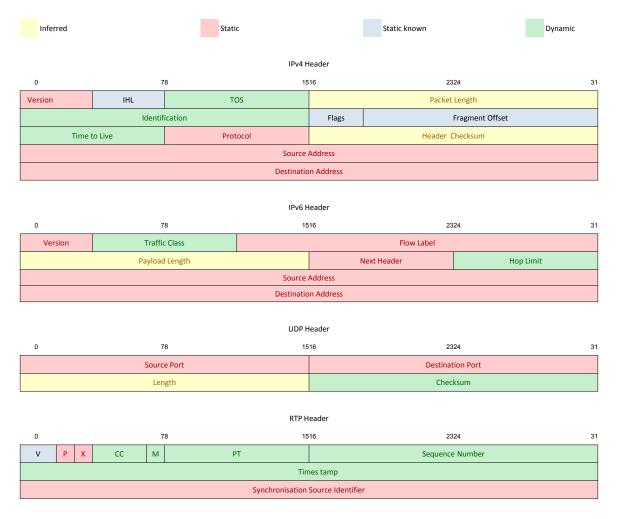

The basic principle of RoHC is that only a few header fields change randomly across a packet stream, while most of the fields change in a predictable way or not change at all. This makes header compression plausible. The header fields of a typical VoIP stack of IP/UDP/RTP are as shown in Figure 3.1. They can be classified into four different categories:

- 1. **Inferred**: These fields are never sent within a RoHC packet and can be inferred by the decompressor from the other fields or with the support of lower layers in the network stack.

- 2. **Static**: These fields are seldom sent within a RoHC packet since they never change during the lifetime of a packet stream.

- 3. **Static known**: These fields are never sent since they are constant in any packet stream.

- 4. **Dynamic**: These fields are of prime importance to RoHC to compress efficiently. They either change within a pattern or randomly.

The dynamic fields, which are of fundamental importance, have to be communicated either directly or derived from other fields for every packet. For RoHC based on the VoIP framework, the RTP Sequence Number (RTP-SN) is used to establish functions to other dynamic fields such as IP Identification (IP-ID), RTP Timestamp (RTP-TS). Hence, only RTP-SN needs to be reliably communicated while the other fields are derived from the RTP-SN functions. Other dynamic fields are changing in general but are expected to be constant during the lifetime of the packet stream. The static fields are

Figure 3.1: VoIP packet header fields

communicated using the uncompressed RoHC initialisation packets. Hence, all the fields of the IP/UDP/RTP headers are communicated either implicitly or explicitly during the packet flow.

### 3.2 Profiles

The RoHC profiles specify the schemes of both compression and decompression for a packet stream. In the RFC3095 specification [1], four different profiles are defined for different protocol stacks. These profiles are given below:

• **Profile 0**: For sending uncompressed packets. (This is the default scheme when the packets fail to fall within predefined RoHC profiles).

- **Profile 1**: This is for RTP/UDP/RTP compression.

- **Profile 2**: This is for UDP/IP compression.

- Profile 3: This is for ESP/IP compression.

#### **3.3** Compressor and Decompressor

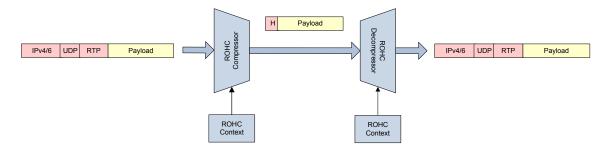

Figure 3.2: Compressor and decompressor blocks in a RoHC system

The major components of the RoHC framework are the compressor and decompressor as shown in Figure 3.2, which are present in PDCP Layer 2 of an LTE system. The compressor processes the incoming IP/UDP/RTP headers of the VoIP packet stream and compresses them. The compressed header is transmitted with the payload along the wireless link while the decompressor does the opposite for its decompression. Both the compressor and the decompressor use recently stored information from previous packets for a particular stream for the compression and the decompression processes. The stored information in the compressor or decompressor is referred to as the context of that compressor or decompressor, respectively. The contexts of the compressor and the decompressor must be consistent, to ensure a successful uninterrupted sequence of compression and decompression.

#### 3.4 Modes

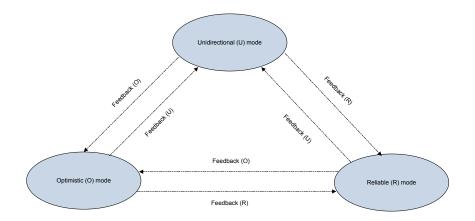

There are three modes of operation as shown in Figure 3.3 which determine the logic of state transitions and state actions. Depending on the existence of a feedback channel and the amount of feedback sent by the decompressor to the compressor, three modes are defined in the RFC3095 specification [1]. These modes: Unidirectional mode, Bidirectional optimistic mode, and Bidirectional reliable mode are briefly explained below. Transition between modes is possible and occurs when the decompressor triggers the change with the help of feedback packets.

Figure 3.3: Modes of operation in a RoHC system

#### 3.4.1 Unidirectional Mode (U-mode)

- This mode is for simplex channels which have no feedback capability; packets are sent in one direction from the compressor to the decompressor.

- In this mode, state transitions occur because of periodic timeouts and retransmissions because of irregularities in the header fields in the compressed packet streams from the compressor to the decompressor.

- The compressor in RoHC must start in this mode as the feedback capability of the channel is not known.

- In case of a packet loss or an unrecoverable error in the received compressed packet, the context of the decompressor might get invalidated and the sequence of decompression fails. In this mode, the decompressor waits for an uncompressed packet to resynchronize the context. The uncompressed packets are sent periodically and if the compressor detects a change in one of the static fields in the packet to be compressed.

#### 3.4.2 Bidirectional Optimistic Mode (O-mode)

• This mode is similar to the unidirectional mode, but instead of the periodic timeout and the retransmission of uncompressed packets the feedback channel is used sparingly by the decompressor to send error recovery requests and acknowledgements of significant context updates.

#### 3.4.3 Bidirectional Reliable Mode (R-mode)

- In this mode the feedback channel is used more often to acknowledge all the context updates. This mode employs stricter logic to maintain context synchronization between the compressor and decompressor.

- This mode maximizes robustness against loss propagation and damage propagation.

#### 3.5 Compressor States

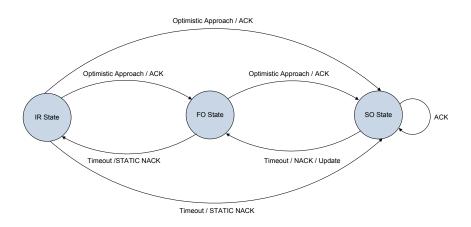

Figure 3.4: Compressor state machine

The compressor has three states as shown in Figure 3.4 - IR (Initialization and Refresh), FO (First order) and SO (second order) states. The compressor starts from the lowest compression state (IR) and gradually transits to higher-order states.

A forward state transition occurs when the compressor is confident that the decompressor has correctly updated the context. The confidence is achieved by either sending the header information more than once (optimistic approach) or by an ACK feedback from the decompressor. The optimistic approach is only used in the unidirectional mode and bidirectional optimistic mode. The number of times the same header information is (re)transmitted in the optimistic approach is an implementation-dependent variable.

A backward state transition occurs when one of the timeout counters are reset, a NACK or STATIC NACK feedback is received from the decompressor, or the packet to be compressed encounters a change in the static fields or the pattern of the dynamic fields. The two timeout counters are used to transit to IR or FO states and they are implementation-dependent variables. The timeout counters are only used in the unidirectional mode and the bidirectional optimistic mode.

**IR state:** It is used to initialize or to recover the context of the decompressor's static and dynamic fields. In this state, the compressor sends the entire header information by IR packets. The compressor stays in this state until it is fairly confident that the decompressor has established or updated the context correctly.

**FO state:** The purpose of this state is to effectively communicate the irregularities in the packet headers especially related to the dynamic parts of the context. The compressor transits to and from the FO state by forward/backward transitions discussed earlier, if there are changes in the static context. It enters this state from the IR state after transmitting static context or from the SO state after changes occur in a dynamic field (non-conformity of the previous pattern). FO packets carry context-updating information and are therefore protected by a CRC.

**SO state:** The compressor transits to this state when compression is optimal, and the compressor is sufficiently confident that the decompressor has all the context fields including the parameters of functions from SN to derive fields like IP-ID and TS to ensure correct decompression. In this state only a few bits are required for TS/IP-ID to be transmitted. The compressor changes from the SO to the IR or FO state with forward/backward transitions discussed earlier when the header pattern changes and it can no longer be compressed with present context. SO state packets are also protected by CRC.

#### **3.6** Decompressor States

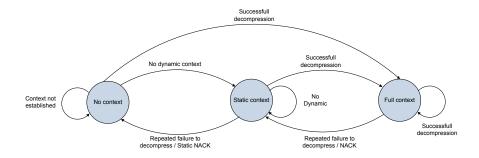

Figure 3.5: Decompressor state machine

The decompressor has three states as shown in Figure 3.5 which are independent of the modes: No context, static context and full context. It starts from the lowest compression state, no context, and gradually transits to higher order states.

**No context:** The decompressor will be in this state at the start of transmission when the decompressor context has not yet been established. In this state only IR packets are allowed to be received. Only after a successful decompression involving a CRC check the decompressor transits to the full context state. **Static context:** In this state the decompressor is assumed to have the static information but not the dynamic information or it may have changed. In this state only IR, IR-DYN, UOR-2 packets described in section 3.9, are decompressed (carrying either an 8 bit or 7 bit CRC). Transitions to No context state from this state are triggered by repeated errors (unidirectional mode) or NACK/Static-NACK feedback (bidirectional mode).

**Full context:** Successful reception of any packet in the FO state of the compressor enables a transition to Full context. In this state, the decompressor has full context information. Once it enters this state it never leaves unless there are repeated unsuccessful decompression attempts (failure of CRC check, in unidirectional mode) or NACK/STATIC-NACK feedback (in bidirectional mode). Only then does it transit to the static context.

#### 3.7 Encoding Methods

There are several encoding methods as specified in the RoHC framework employed for different dynamic fields of an IP/UDP/RTP header stack. These are:

#### 3.7.1 LSB Encoding

As the name indicates, the LSB encoding is used to transmit the change that occurs in the least significant bits of a field when compared to a reference value stored in the context. The decompressor derives the original value from the received LSBs and the previously received reference value (vref) such that the value falls within the interpretation interval as defined by the function given in equation 3.1. The k received LSBs are enough to uniquely define the value within the interpretation interval.

$$f(vref,k) = [vref - p, vref + (2^k - 1) - p].$$

(3.1)

$$\begin{array}{c|c} & & \\ & & \\ \hline & & \\ vref - p \end{array} \\ \hline & vref + (2^k - 1) - p \end{array}$$

The selection function is referred to as g(vref, v) such that k = g(vref, v).

Here p is an integer used to shift the interpretation interval depending on the typical behaviour of different header fields like IP-ID, RTP-SN, or RTP-TS.

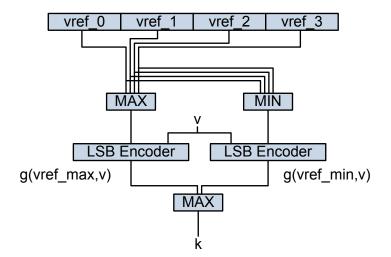

Figure 3.6: WLSB encoder

#### Window-based LSB (WLSB) Encoding

The compressor may not be able to determine the exact reference value at the decompressor side. Therefore, it maintains a sliding-window for candidates of reference values ranging from  $vref_{min}$  to  $vref_{max}$ . The compressor chooses the maximum number of bits(k) to uniquely identify a value v using the equation:

$$k = max(g(vref_{min}, v), g(vref_{max}, v)).$$

(3.2)

The sliding-window is advanced by either a CRC confirmation, in case of U or O mode, and ACK, in case of R mode. WLSB modifies LSB encoding to achieve robustness by calculating k for a window of the stored field values and selecting the appropriate k. Figure 3.6 shows a block diagram of the WLSB method which explains how it is related to the LSB method.

#### 3.7.2 Scaled RTP Timestamp Encoding

Common audio and video codecs have fixed sampling rates. For this reason and since an RTP packet transmits a constant number of these samples per unit time, the timestamp in successive RTP packets is usually increased by an integral multiple of some constant number called *ts\_stride*. This property can be used to efficiently compress the timestamp of an RTP packet by sending a downscaled timestamp. The scaled timestamp can be expressed using less number of bits than the original timestamp and hence a first order compression can be achieved. A second order compression can be achieved by compressing the scaled timestamp using the WLSB encoding method discussed earlier.

The down-scaling of the timestamp follows equation 3.3 below:

$$ts = ts\_scaled \times ts\_stride + ts\_offset.$$

(3.3)

The  $ts\_stride$  is communicated explicitly and  $ts\_offset$  is communicated implicitly, as discussed in the following stages.

- **During initialization:** The compressor sends *ts\_stride* and absolute value of *ts*. The decompressor initializes *ts\_offset* using (*ts* modulo *ts\_stride*).

- During compression: Only WLSB or Timer-based encoded ts\_scaled is sent.

- **During decompression:** Original RTP-TS value is calculated using compressed *ts\_scaled* and *ts\_stride*, which are communicated at initialization using equation 3.3.

- At wraparound: The compressor does not reinitialize *ts\_offset* at wraparound but the decompressor detects wraparound of unscaled *ts* and updates *ts\_offset*.

#### 3.7.3 Timer-based RTP Timestamp Compression

With fixed sampling intervals employed by audio and video applications and packets that are transmitted in lockstep with the sampling, RTP-TS is increased by an integral multiple. It can also be approximated by a linear function of the time of day taking into account the delay jitter between the compressor and decompressor. By using the local clock the decompressor can obtain an approximation of  $ts\_scaled$  in the header considering its arrival time. This method is discussed in detail in [1], but is not used in this implementation.

#### 3.7.4 IP-ID Offset Encoding

For IPv4, the IP-ID will increase by the same amount as RTP-SN. Therefore, it is more efficient to compress only the IP-ID offset relative to RTP-SN by WLSB encoding with p=0, using the formula

$$Offset = IP \ ID - RTP \ SN. \tag{3.4}$$

At the decompressor side, the IP-ID is calculated from the reference header (correctly verified by CRC) using the formula

$$IP - ID = Offset\_ref + RTP \ SN\_ref.$$

(3.5)

Some stacks do not use a counter to generate IP-ID values but instead they are generated randomly using a pseudo-random number generator, in such case IP-ID offset encoding cannot be used.

#### Table 3.1: SVDL Encoding

| First bit/bits | No. of octets | No. of bits transferred |

|----------------|---------------|-------------------------|

| 1              | 1             | 7                       |

| 10             | 2             | 14                      |

| 110            | 3             | 21                      |

| 111            | 4             | 29                      |

### 3.7.5 Self-Describing Variable Length Code (SDVL) Encoding

Parameters like *ts\_stride* and some others vary widely. For optimal transfer of such values SDVL is used to encode them. The first few bits of the first octet determine the number of octets used as shown in the Table 3.1.

#### **3.8** CRC

Cyclic redundancy checks are used by RoHC as the primary means for detecting erroneous decompression, just as in many other communication systems. CRCs play an important role in providing means for verification, especially in U/O mode where feedback is absent. Incorrect context update and prevention of residual errors from lower layer are mitigated by the CRC information carried by the RoHC packets. This adds to the robustness of the system.

Uncompressed packets like IR and IR-DYN carry an 8-bit CRC computed based on all the RoHC packet fields excluding the payload. As these are context-updating packets a larger size of CRC assures the context validation. Also for feedback type 2, as discussed in section 3.9, an 8-bit CRC is used.

Compressed packets like UO-0 and UO-1 contain 3-bit CRCs and packets like UO-2 contain a 7-bit CRC. For the compressed packets CRCs are computed on STATIC fields and DYNAMIC header fields of the original IP packets. The 3-bit, 7-bit and 8-bit CRCs are computed using the following polynomials.

3-bit CRC:  $C(x) = 1 + x + x^3$

7-bit CRC:  $C(x) = 1 + x + x^2 + x^3 + x^6 + x^7$

8-bit CRC:  $C(x) = 1 + x + x^2 + x^8$

More details about the polynomials and the CRC calculations can be found in [8].

#### 3.9 Major RoHC Packet Types

The RoHC framework defines several kinds of packets; they are discussed in brief below.

- 1. RoHC packets :

- IR and IR-DYN packets: These are uncompressed RoHC packets used to initialize/communicate the static and/or dynamic parts of the context. IR-DYN is used to initialize/communicate only the dynamic part of the context.

- Type 0 packets (Ex: UO-0): These packets are of smallest size (1 byte), hence, the most efficient. They are used when the decompressor can derive the necessary fields as a function of RTP-SN.

- Type 1 packets (Ex: UO-1-\*): These packets are used when WLSB encoded bits of RTP-SN exceed those available for Type 0 or when the parameters to the SN functions for deriving the TS or IP-ID fields change.

- Type 2 packets (Ex: UO-2-\*): These packets are used when the WLSB encoded bits of the RTP-SN exceed those available for Type 0 and Type 1, or when the parameters to the SN functions for deriving the TS or IP-ID fields change.

- 2. Extension Packets: Extension packets are used to convey information other than what is contained by lower compressed packets (like UO-1, UOR-2) without having to send uncompressed packets (IR, IR-Dyn). There are three types of extensions used in combination with base packets of type 1 and 2.

- 3. Feedback Packets: For RoHC modes that use feedback, they are sent either in separate RoHC packets or piggybacked on forward packets from the decompressor to the compressor. There are two types of feedback packets FEEDBACK 1 packets, which are used to send ACK, and FEEDBACK 2 packets, which are used to send NACK or STATIC-NACK along with mode information.

Table 3.2 shows the main properties of the RoHC packets such as the CRC type, the updating capability, and the number of bits that the packet can carry for each of SN, IP-ID, and TS. The update column in the table specifies whether the packet can update the context or not. Further information about the structure of the packets and their properties is given in details in RFC3095 [1].

| Packet type   | SN | IP-ID-1 | IP-ID-2 | TS                                  | Update<br>context | CRC<br>type | Static<br>fields |

|---------------|----|---------|---------|-------------------------------------|-------------------|-------------|------------------|

|               | 6  | 0       | 0       | 0                                   | No                | 0           | No               |

| R-0-CRC       | 7  | 0       | 0       | 0                                   | Yes               | 7           | No               |

| R-1-ID        | 6  | 5       | 0       | 0                                   | No                | 0           | No               |

| R-1-TS        | 6  | 0       | 0       | 5                                   | No                | 0           | No               |

| <u>UO-0</u>   | 4  | 0       | 0       | 0                                   | Yes               | 3           | No               |

| UO-1-ID       | 4  | 5       | 0       | 0                                   | Yes               | 3           | No               |

| UO-1-TS       | 4  | 0       | 0       | 5                                   | Yes               | 3           | No               |

| UOR-2-ID      | 6  | 5       | 0       | $\begin{array}{c} 0 \\ \end{array}$ | Yes               |             | No               |

| R-1-ID-EXT0   |    | 8       |         |                                     | No                |             | No               |

|               | 9  |         | 0       | 0                                   |                   | 0           |                  |

| UO-1-ID-EXT0  | 7  | 8       | 0       | 0                                   | Yes               | 3           | No               |

| UOR-2-TS      | 6  | 0       | 0       | 5                                   | Yes               | 7           | No               |

| R-1-TS-EXT0   | 9  | 0       | 0       | 8                                   | No                | 0           | No               |

| UOR-2-ID-EXT0 | 9  | 8       | 0       | 0                                   | Yes               | 7           | No               |

| UOR-2-TS-EXT0 | 9  | 0       | 0       | 8                                   | Yes               | 7           | No               |

| R-1-TS-EXT1   | 9  | 8       | 0       | 8                                   | No                | 0           | No               |

| UO-1-ID-EXT1  | 7  | 8       | 0       | 8                                   | Yes               | 3           | No               |

| UO-1-ID-EXT2  | 7  | 16      | 0       | 8                                   | Yes               | 3           | No               |

| UOR-2-TS-EXT1 | 9  | 8       | 0       | 8                                   | Yes               | 7           | No               |

| R-1-ID-EXT2   | 9  | 16      | 0       | 8                                   | No                | 0           | No               |

| R-1-TS-EXT2   | 9  | 8       | 0       | 16                                  | No                | 0           | No               |

| UOR-2-ID-EXT2 | 9  | 16      | 0       | 8                                   | Yes               | 7           | No               |

| UOR-2-TS-EXT2 | 9  | 8       | 0       | 16                                  | Yes               | 7           | No               |

| R-1-ID-EXT3   | 14 | 16      | 16      | 29                                  | No                | 0           | No               |

| UO-1-ID-EXT3  | 12 | 16      | 16      | 29                                  | Yes               | 3           | No               |

| UOR-2-ID-EXT3 | 14 | 16      | 16      | 29                                  | Yes               | 7           | No               |

| R-1-TS-EXT3   | 14 | 16      | 16      | 32                                  | No                | 0           | No               |

| UOR-2-TS-EXT3 | 14 | 16      | 16      | 32                                  | Yes               | 7           | No               |

| UO-1          | 4  | 0       | 0       | 6                                   | Yes               | 3           | No               |

| R-1           | 6  | 0       | 0       | 6                                   | No                | 0           | No               |

| UOR-2         | 6  | 0       | 0       | 6                                   | Yes               | 7           | No               |

| R-1-EXT0      | 9  | 0       | 0       | 9                                   | No                | 0           | No               |

| UOR-2-EXT0    | 9  | 0       | 0       | 9                                   | Yes               | 7           | No               |

| R-1-EXT1      | 9  | 0       | 0       | 17                                  | No                | 0           | No               |

| UOR-2-EXT1    | 9  | 0       | 0       | 17                                  | Yes               | 7           | No               |

| R-1-EXT2      | 9  | 0       | 0       | 25                                  | No                | 0           | No               |

| UOR-2-EXT2    | 9  | 0       | 0       | 25                                  | Yes               | 7           | No               |

| R-1-EXT3      | 14 | 0       | 0       | 32                                  | No                | 0           | No               |

| UOR-2-EXT3    | 14 | 16      | 16      | 32                                  | Yes               | 7           | No               |

| IR-DYN        | 16 | 16      | 16      | 32                                  | Yes               | 8           | No               |

| IR            | 16 | 16      | 16      | 32                                  | Yes               | 8           | Yes              |

Table 3.2: RoHC packets and their capabilities

## Chapter 4

## Design of RoHC Hardware Accelerators

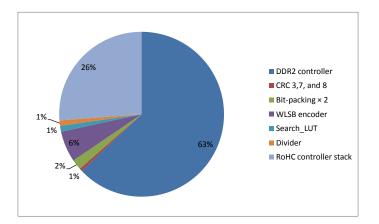

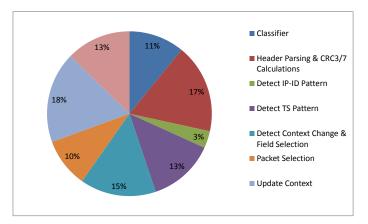

Here certain hardware accelerators are designed to be used to accelerate the RoHC algorithm and are chosen based on profiling results of RoHC software discussed in section 5.3. These accelerators are used for both HW-SW and Full HW implementation of RoHC.

#### 4.1 CRC Hardware Accelerator

There are different methods of computing CRCs based on both software and hardware implementations. The choice between hardware and software methods is application-dependent and is based on parameters such as speed, throughput, memory usage, and design time. These methods along with their advantages and disadvantages are tabulated in the Table 4.1.

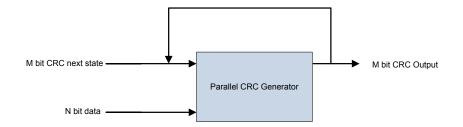

Figure 4.1: Parallel CRC

CRC computation requires bit level manipulations which are more efficient and fast in hardware, therefore CRC blocks are partitioned into hardware accelerators. For the

| CRC Implementations                         | Remarks                                                                                                                                                                                                    | Advantages                                                           | Disadvantages                                                                                                 |  |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Software - based, naive<br>add-shift method | Software-based add-shift<br>method emulates LFSR as<br>shown in [8]                                                                                                                                        | Quick design and prototyp-<br>ing time.                              | Large execution time and<br>inefficient for real-time<br>data                                                 |  |  |

| Software - based CRC ta-<br>ble method      | Data is used to index<br>the CRCs which are pre-<br>calculated and stored in a<br>table                                                                                                                    | Faster execution time and greater throughput.                        | For an N-bit input and an M-bit CRC a large look-up table of size $M \times 2^N$ must be stored in the memory |  |  |

| Hardware - based LFSR method                | Shift registers with linear<br>feedback from XOR gates<br>are used as per the polyno-<br>mial to construct the CRC                                                                                         | Quick Design and proto-<br>typing time.                              | Low throughput and a la-<br>tency of n clock cycles for<br>calculation of n-bit CRC                           |  |  |

| Hardware - based parallel<br>CRC method     | CRC is calculated on data<br>in parallel by performing<br>necessary logic operations<br>and by emulating the state<br>transitions in the LFSR<br>with the incoming parallel<br>data as shown in Figure 4.1 | Fastest CRC method with<br>a throughput of 1 CRC per<br>clock cycle. | More design and prototyp-<br>ing time.                                                                        |  |  |

Table 4.1: Different CRC Methods

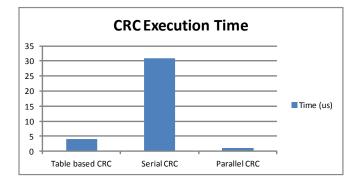

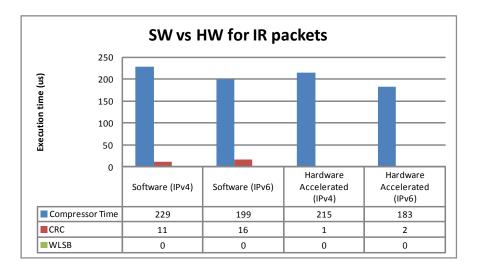

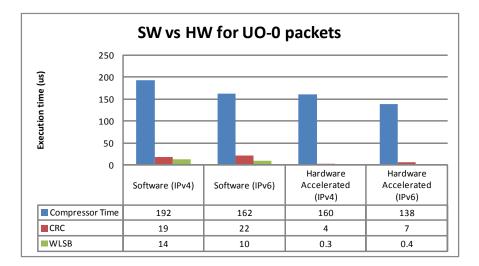

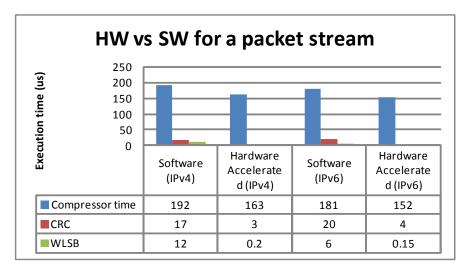

RoHC system, the hardware based parallel CRC method is chosen as this gives the highest throughput. This is also experimentally proven on a NIOS II-based system with a sample data set of 50 bytes. The execution time for different CRC methods on a NIOS-based system is as plotted in Figure 4.2, and it can be seen that the hardware-based parallel CRC method has the fastest execution time.

Figure 4.2: Execution time of different CRCs

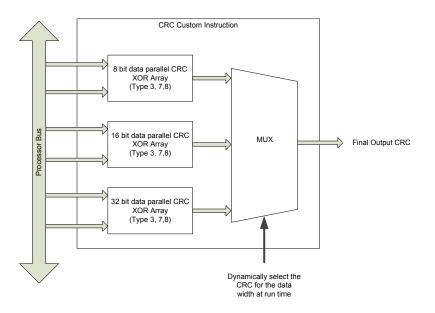

In conclusion, we use parallel CRCs as designed by a method described in section 4.1.1, for both the HW-SW case and the full-HW case. However, in the case of a HW-SW parallel CRC block, the hardware is used in tandem with software to calculate the CRC of different data widths ranging from 32 bits to 8 bits as described in section 5.9.1.

| $crc\_out = f_{crc}(crc\_in = 0, din)$ | $crc\_out[0]$ | $crc\_out[1]$ | $crc\_out[2]$ |            |

|----------------------------------------|---------------|---------------|---------------|------------|

| din[0]                                 | 1             | 1             | 0             | din[0] = 1 |

| din[1]                                 | 0             | 0             | 1             | din[1] = 1 |

| din[2]                                 | 0             | 1             | 0             | din[2] = 1 |

| din[3]                                 | 1             | 0             | 0             | din[3] = 1 |

| din[4]                                 | 1             | 0             | 1             | din[4] = 1 |

| din[5]                                 | 1             | 1             | 1             | din[5] = 1 |

| din[6]                                 | 0             | 1             | 1             | din[6] = 1 |

| din[7]                                 | 1             | 1             | 0             | din[7] = 1 |

Table 4.2: H1 Matrix

#### Table 4.3: H2 Matrix

| $crc\_out = f_{crc}(crc\_in, din = 0)$ | $crc\_out[0]$ | $crc\_out[1]$ | $crc\_out[2]$ |                  |

|----------------------------------------|---------------|---------------|---------------|------------------|

| crc_in[0]                              | 1             | 1             | 0             | $crc\_in[0] = 1$ |

| $crc\_in[1]$                           | 0             | 0             | 1             | $crc\_in[1] = 1$ |

| $crc\_in[2]$                           | 0             | 1             | 0             | $crc\_in[2] = 1$ |

#### 4.1.1 Design of Parallel CRCs

The design of a parallel CRC block is done as per the method proposed in [9], which leverages the serial CRC generator and discrete-time linear-system properties of CRCs to generate parallel CRCs. The parallel CRC generator block is as shown in Figure 4.1. The design process involves the following steps:

- 1. First a C-based serial CRC simulator is implemented. The logic works on 8-bit data and CRC initialization values to produce an M-bit CRC. For 16 and 32 bit data, the same logic is used in cascade iteratively 2 or 4 times, respectively. And the CRC initialization value being updated with the 8-bit CRC output with each iteration.

- 2. Then an H1 matrix is formed based on the equation  $crc_out = f_{crc}(crc_in = 0, din)$  for 1-shot high values of din like 1, 2, 4, 8, 16..., and neglecting  $crc_in$ , using the CRC simulator developed in 1.

- 3. Then an H2 matrix is formed based on the equation  $crc_out = f_{crc}(crc_in, din = 0)$  for 1-shot high values of  $crc_in$  like 1, 2, 4, 8, 16..., and neglecting din, using the CRC simulator developed in 1.

- 4. Then the logical equations from the H1 and H2 matrices are combined by logical modulo-2 arithmetic to generate parallel CRC equations for 8-bit, 16-bit and 32-bit data.

For example, the H1 and H2 matrices for 3-bit CRC  $(1 + x + x^3)$  and 8-bit data are as shown in Table 4.2 and Table 4.3. The XOR equations for parallel CRCs based on the H1 and H2 matrices are as shown in equations 4.1.

| H2 matrix                                    | H1 matrix                                                               |       |

|----------------------------------------------|-------------------------------------------------------------------------|-------|

| $crc\_out[0] = \overbrace{crc\_in[0]}$       | $\oplus din[0] \oplus din[3] \oplus din[4] \oplus din[5] \oplus din[7]$ |       |

| $crc\_out[1] = crc\_in[0] \oplus crc\_in[2]$ | $]\oplus din[0]\oplus din[2]\oplus din[5]\oplus din[6]\oplus din[7]$    | (4.1) |

| $crc\_out[2] = crc\_in[1]$                   | $\oplus din[1] \oplus din[4] \oplus din[5] \oplus din[6]$               |       |

#### 4.2 Least Significant Bit Encoding (LSB Encoding)

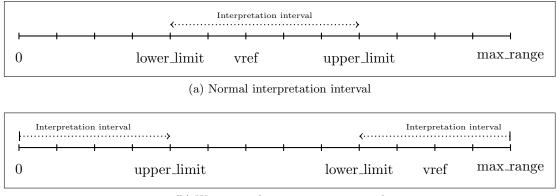

As explained earlier in subsection 3.7.1, LSB encoding makes use of the interpretation interval technique to efficiently encode a field with respect to a reference value stored in the context. The decompression of the LSB bits is guaranteed if both the compressor and the decompressor use the same interpretation interval. An illustration of the interpretation interval is shown in Figure 4.3a below. Since the header fields have finite number of bits to describe their values, the interpretation interval might wrap around as shown in Figure 4.3b.

(b) Wraparound interpretation interval

Figure 4.3: Different interpretation interval cases

The terms  $upper\_limit$  and  $lower\_limit$  are defined in equations 4.2 and 4.3 respectively as

$$upper\_limit = vref + 2^k - 1 - p \tag{4.2}$$

and

$$lower\_limit = vref - p. \tag{4.3}$$

In equation 4.2, k is defined as the least number of bits such that the field value lies inside the interpretation interval below:

$$lower\_limit \leq value \leq upper\_limit.$$

If the interpretation interval is wrapped around,  $upper\_limit < lower\_limit$ , then the condition is changed to :

$lower\_limit \leq value \quad or \quad value \leq upper\_limit.$

In equation 4.2, p is defined as the shifting value that shift the interpretation interval and it differs from one field to another. Below are the p values for the Sequence Number (SN), the Internet Protocol Identification (IP-ID), and the Time Stamp (TS) as specified in [1]:

$$p(sn) = \begin{cases} 1 & ifk \le 4\\ 2^{k-5} - 1 & otherwise \end{cases},$$

(4.4)

$$p(ip - id) = 0, (4.5)$$

and

$$p(ts) = 2^{k-2} - 1. (4.6)$$

To find k, equation 4.4, 4.5 and 4.6 parameterize the shifting value p as follows :

$$p = a2^{k-b} - c,$$

where a, b and c are shown in Table 4.4.

| Table 4.4:         Parametrization | of the | shifting | value $p$ | Ø |

|------------------------------------|--------|----------|-----------|---|

|------------------------------------|--------|----------|-----------|---|

| Field | a | b | c  | Condition     |

|-------|---|---|----|---------------|

| SN    | 0 | 0 | -1 | if $k \leq 4$ |

| SIN   | 1 | 5 | 1  | if $k > 4$    |

| IP-ID | 0 | 0 | 0  | -             |

| TS    | 1 | 2 | 1  | -             |

By setting  $value = upper\_limit$  and  $value = lower\_limit$ ,  $k_1$  and  $k_2$  are found respectively.  $k_1$  and  $k_2$  are calculated in equations 4.7 and 4.8 respectively as

$$k_1 = \lceil log_2(R_{fd} - c + 1) + b - log_2(2^b - a) \rceil,$$

(4.7)

and

$$k_2 = \lceil \log_2(R_{bk} + c) + \log_2(2^b) \rceil.$$

(4.8)

To find the least number of bits, k is calculated as

$$k = \min(k_1, k_2). \tag{4.9}$$

where

$R_{fd}$ : is the absolute forward distance between value and vref

and

$R_{bk}$ : is the absolute backward distance between value and vref.

In [3], k1 is always assumed less than k2 and hence considered as the solution of k. In this work, it is shown that any of k1 or k2 can be a solution of k and the earlier assumption by [3] is not correct and cannot cover all cases.

Since p value is different from one field to another, some special cases are exist. For instance, the value of p for IP-ID is zero and there are two values of p for the SN. Since p is equal to zero for IP-ID, k is calculated from equation 4.7 only. Unlike [3], in which k(sn) is always calculated first for p = 1, k(sn) is considered equal to 4 bits (the least number of bits that a RoHC packet can transmit) if  $R_{fd} \leq 14$  or  $R_{bk} \leq 1$ . This will avoid an unnecessary iteration of trying different p values.

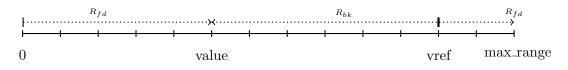

The rest of this section focuses on how to find which equation, k1 or k2, is the correct solution for k without the need to calculate both equations in an attempt to reduce both processing power and hardware. By looking at the position of *value* and *vref*, two cases are found as follows:

## 4.2.1 Case 1 when (value < vref)

The least number of bits is calculated in equation 4.10 as

$$k = \begin{cases} k2 & \text{if } R_{bk} \le R_{bk\_max} \\ k1 & \text{otherwise} \end{cases}, \tag{4.10}$$

where  $R_{bk\_max}$  is the maximum backward distance.  $R_{bk\_max}$  is calculated in equation 4.11 as

$$R_{bk\_max} = 2^{k_{max}-b} - c, (4.11)$$

where  $k_{max}$  is defined as the maximum number of bits that can describe a field i.e.  $k_{max}$  is equal to 16 bits for both SN and IP-ID and it is equal to 32 bits for TS.

$R_{bk}$  and  $R_{fd}$  are calculated from the graph as follows:

$$R_{bk} = vref - value, \tag{4.12}$$

and

$$R_{fd} = max\_range + value - vref + 1.$$

(4.13)

Thus,

$$R_{fd} = max\_range - R_{bk} + 1. \tag{4.14}$$

To prove equation 4.10, substituting equation 4.14 when  $R_{bk} = R_{bk\_max}$  in equation 4.7 yields:

$$k_1 = \log_2(2^{k_{max}} \cdot \frac{(2^b - 1)}{2^b} + 1) + b - \log_2(2^b - 1) \qquad \text{(since a=1)}.$$

(4.15)

By underestimating

$$log_2(2^{k_{max}} \cdot \frac{(2^b - 1)}{2^b} + 1) \simeq log_2(2^{k_{max}} \cdot \frac{(2^b - 1)}{2^b}),$$

this yields

$k_1 \simeq k_{max}.$

By substituting  $R_{bk} = R_{bk\_max}$  in equation 4.8

$$k_2 = k_{max}$$

Since an underestimation of the first term in equation 4.15 is done,  $k_2 < k_1$  when  $R_{bk}$  is less than or equal  $R_{bk\_max}$ . Otherwise,  $k_1$  is less than  $k_2$ . Therefore, using this condition there is no need to calculate both  $k_1$  and  $k_2$  in order to find k and the processing power is reduced by half.

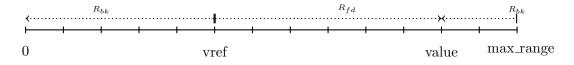

#### 4.2.2 Case 2 when (value > vref)

The least number of bits is calculated in equation 4.16 as

$$k = \begin{cases} k2 & \text{if } R_{bk} \le R_{bk\_max} \\ k1 & \text{otherwise} \end{cases}, \tag{4.16}$$

where  $R_{fd}$  and  $R_{bk}$  are calculated as

$$R_{fd} = value - vref, \tag{4.17}$$

and

$$R_{bk} = max\_range + vref + 1 - value.$$

$$(4.18)$$

Similar to subsection 4.2.1, equation 4.16 can be proved by substituting equation 4.14 when  $R_{bk} = R_{bk\_max}$  in equation 4.7 and  $R_{bk} = R_{bk\_max}$  in equation 4.8.

#### 4.2.3 Hardware Implementation of LSB Encoding

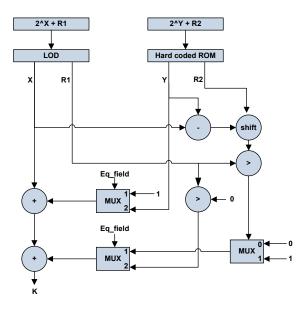

The hardware complexity of equation 4.7 and 4.8 resides in the logarithmic terms. Since K should be an integral number of bits, the  $log_2$  implementation can be reduced to a Leading One Detector (LOD) for calculating the integer part of the logarithm.

The improvements in this implementation of the LSB encoder over the one presented in [3] include accounting for all possible cases with no extra hardware cost, introducing a zero-error implementation of the logarithmic equations without the need for floating point logarithm hardware, and reducing the need of calculating k(SN) using two shifting values p.

In order to find the value of k in [3], the result of equation 4.7 is ceiled only if the integer remainder of the first logarithmic term  $(R_{fd} - c + 1)$  is larger than the integer remainder of the second logarithmic term  $(2^b - a)$ . Using this method, an error of positive one might be induced to k. Although sending an extra bit will not lead to a decompression failure, it definitely influences the decision of which packet to send. Sending a different packet rather than the optimal one might mean sending more bits for other fields as well leading to an inefficient compression.

The error induced from using the ceiling operation on the integer remainder comparison in [3] is related to the fact that the integer remainders might describe fractions on different binary logarithmic scale. In other words, if the integer parts of both logarithms are not equal, the comparison is invalid. This is a very typical case.

In this work, a zero-error LSB function is proposed by adding an extra step to the integer remainder comparison. The remainder of one term should first be shifted to the same binary logarithmic scale as the other, and then the ceiling is done based on the comparison. The example below shows the difference between the proposed method and the original in [3].

#### Example:

Assume the first and the second logarithmic terms in equation 4.7 are 1058 and 31, as shown below:

$$(1058)_2 = 10000100010 \qquad floor(log_2(1058)) = 10$$

(31)<sub>2</sub> = 11111 \qquad floor(log\_2(31)) = 4

1. Using the integer remainder comparison method as in [3],

$$remainder_1 = 34$$

$remainder_2 = 15$

k = 10+5-4+1 (since remainder<sub>1</sub> > remainder<sub>2</sub>)  $\implies$  k = 12 (k should be 11)

2. Using the zero-error proposed method

$$remainder_2 = 15 \times (\lfloor log_2(1058) \rfloor) - \lfloor (log_2(31) \rfloor) \\ = 960$$

$$k = 10 + 5 - 4 + 0$$

(since  $34 < 960$ ))  $k = 11(correct)$ .

Below is a mathematical proof that the error is always zero in this approach. Any positive integer number N can be described in its binary form as:

$$N = \sum_{i=0}^{x} 2^{i} . N(i).$$

(4.19)

$$N = 2^{x} + \sum_{i=0}^{x-1} 2^{i} N(i).$$

(4.20)

Let

$$r = \sum_{i=0}^{x-1} 2^i . N(i).$$

(4.21)

$$N = 2^x + r \tag{4.22}$$

$$log_2(N) = x + log_2(2^x + r) - \lfloor log_2(2^x + r) \rfloor.$$

(4.23)

Let

$$R = log_2(2^x + r) - \lfloor log_2(2^x + r) \rfloor.$$

(4.24)

In the proposed zero-error comparison method, the integer remainder of one of the logarithmic terms (N1) is shifted to same binary logarithmic scale of the second term (N2). The value of the shifting (n) is the difference between the integer results of the two logarithmic terms i.e. n = x1 - x2. R' is defined as the shifted integer remainder and it is calculated as in the equation below:

Let

$$R' = log_2\{2^n \cdot (2^x + r)\} - \lfloor log_2\{2^n \cdot (2^x + r)\}\rfloor.$$

(4.25)

If the error of shifting the remainder is zero, R must equal R'

$$\begin{aligned} R' &= \log_2\{2^n \cdot (2^x + r)\} - \lfloor \log_2\{2^n \cdot (2^x + r)\} \rfloor \\ &= n + \log_2\{(2^x + r)\} - n - \lfloor \log_2\{2^n \cdot (2^x + r)\} \rfloor \\ &= \log_2(2^x + r) - \lfloor \log_2(2^x + r) \rfloor \end{aligned}$$

Thus  $R' = R$

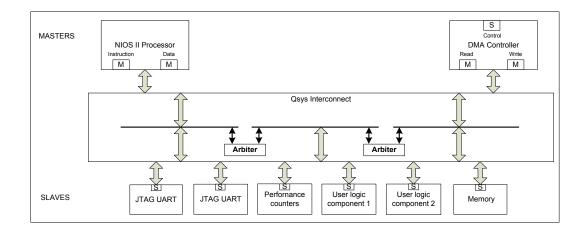

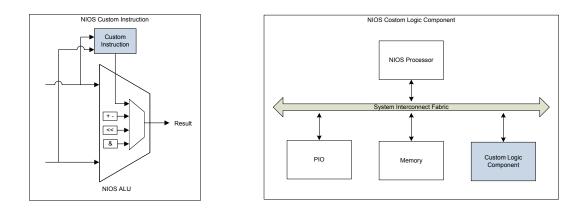

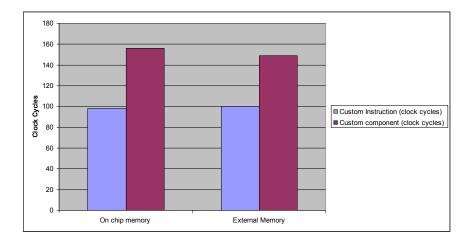

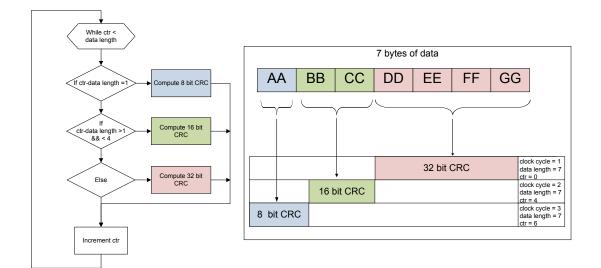

Figure 4.4 shows a block diagram of a common hardware for calculating either k1 or k2 equation. After finding which one of the equations is the solution of k, all of the parameters shown in Figure 4.2 - X, Y, R1 and R2 - are calculated and sent to the LSB hardware to calculate the final k. X, Y, R1 and R2 are inner terms in equations 4.7 and 4.8 as follows: