Rochester Institute of Technology RIT Scholar Works

Theses

8-1-2007

# Hardware and software optimization of fourier transform infrared spectrometry on hybrid-FPGAs

Dmitriy Bekker

Follow this and additional works at: https://scholarworks.rit.edu/theses

#### **Recommended Citation**

Bekker, Dmitriy, "Hardware and software optimization of fourier transform infrared spectrometry on hybrid-FPGAs" (2007). Thesis. Rochester Institute of Technology. Accessed from

This Thesis is brought to you for free and open access by RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact ritscholarworks@rit.edu.

### Hardware and Software Optimization of Fourier Transform Infrared Spectrometry on Hybrid-FPGAs

by

Dmitriy L. Bekker

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering

Supervised by

Dr. Marcin Lukowiak Assistant Professor Department of Computer Engineering Kate Gleason College of Engineering Rochester Institute of Technology Rochester, New York August 2007

Approved By:

Dr. Marcin Lukowiak Assistant Professor, Department of Computer Engineering Rochester Institute of Technology

Dr. Muhammad Shaaban Associate Professor, Department of Computer Engineering Rochester Institute of Technology

Dr. Jean-Francois Blavier Science Division NASA Jet Propulsion Laboratory (Caltech)

### Thesis Release Permission Form

Rochester Institute of Technology Kate Gleason College of Engineering

Title: Hardware and Software Optimization of Fourier Transform Infrared Spectrometry on Hybrid-FPGAs

I, Dmitriy L. Bekker, hereby grant permission to the Wallace Memorial Library to reproduce my thesis in whole or in part.

Dmitriy L. Bekker

Date

# Dedication

To my family and friends, for their love and support.

### Acknowledgments

I would like to thank my RIT advisers, Dr. Lukowiak and Dr. Shabaan, for teaching me most of what I know in Computer Engineering and for their help and support on this thesis. They made sure I had everything necessary to carry out this work, including top of the line development hardware and software rarely seen in universities yet. I would also like to thank Dr. Blavier from JPL for working with me on this project from the very start and for his dedicated help on the FTIR spectrometry algorithm and the system requirements. I also thank Paula Pingree, Gary Block, Charles Norton, and Abdullah Aljabri from Instrument and Science Data Systems Division at JPL who got me involved with hybrid-FPGAs and their applications to space flight, and Ben Jones from Xilinx for his support on the APU-FPU and co-processor integration.

### Abstract

With the increasing complexity of today's spacecrafts, there exists a concern that the on-board flight computer may be overburdened with various processing tasks. Currently available processors used by NASA are struggling to meet the requirements of scientific experiments [1, 2]. A new computational platform will soon be needed to contend with the increasing demands of future space missions.

Recently developed hybrid field-programmable gate arrays (FPGA) offer the versatility of running diverse software applications on embedded processors while at the same time taking advantage of reconfigurable hardware resources, all on the same chip package. These tightly coupled HW/SW systems consume less power than general-purpose single-board computers (SBC) and promise breakthrough performance previously impossible with traditional processors and reconfigurable devices.

This thesis takes an existing floating-point intensive data processing algorithm, used for on-board spacecraft Fourier transform infrared (FTIR) spectrometry, ports it into the embedded PowerPC 405 (PPC405) processor, and evaluates system performance after applying different hardware and software optimizations and architectural configurations of the hybrid-FPGA. The hardware optimizations include Xilinx's floating-point unit (FPU) for efficient single-precision floating-point calculations and a dedicated single-precision dot-product co-processor assembled from basic floating-point operator cores. The software optimizations include utilizing a non-ANSI single-precision math library as well as IBM's PowerPC performance libraries recompiled for double-precision arithmetic only.

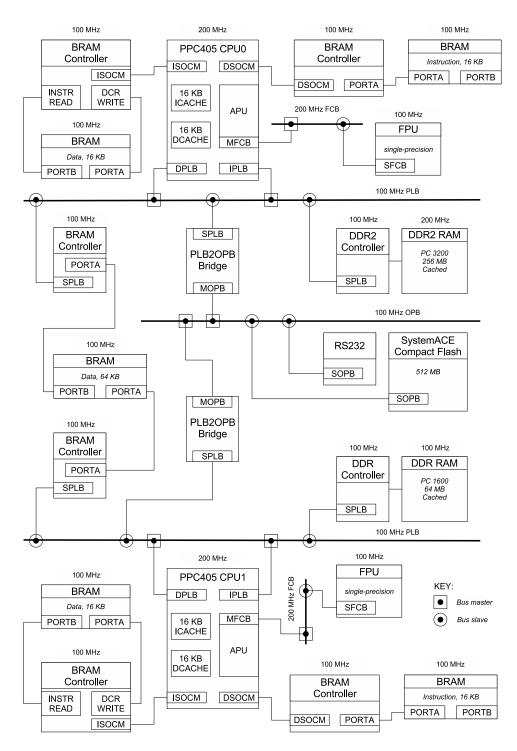

The outcome of this thesis is a fully functional, optimized FTIR spectrometry algorithm implemented on a hybrid-FPGA. The computational and power performance of this system is evaluated and compared to a general-purpose SBC currently used for spacecraft data processing. Suggestions for future work, including a dual-processor concept, are given.

# Contents

| D  | edica | ution                                     | iii  |

|----|-------|-------------------------------------------|------|

| A  | ckno  | wledgments                                | iv   |

| Al | ostra | <b>ct</b>                                 | v    |

| A  | ssum  | ptions                                    | xiii |

| A  | crony | ym Glossary                               | xiv  |

| 1  | Intr  | roduction                                 | 1    |

|    | 1.1   | Background and Motivation                 | 1    |

|    | 1.2   | Thesis Description                        | 3    |

|    | 1.3   | Overview                                  | 5    |

| 2  | Fou   | rier Transform Infrared Spectrometry      | 6    |

|    | 2.1   | Data Collection                           | 6    |

|    | 2.2   | Data Processing Steps                     | 8    |

|    | 2.3   | First Evaluation on FPGAs                 | 10   |

| 3  | Xili  | nx Virtex-4 FX Hybrid-FPGA                | 13   |

|    | 3.1   | Xilinx Virtex-4 FPGA Overview             | 13   |

|    | 3.2   | The Hybrid-FPGA Concept                   | 14   |

|    |       | 3.2.1 Motivation                          | 14   |

|    |       | 3.2.2 Previous Work                       | 15   |

|    | 3.3   | Virtex-4 FX Hybrid-FPGA                   | 16   |

|    |       | 3.3.1 PowerPC 405 Embedded Hard Processor | 17   |

|    |       | 3.3.2 MicroBlaze Soft Processor           | 19   |

|    |       | 3.3.3 System Interfaces                   | 20   |

|    |       | 3.3.4 Auxiliary Processor Unit Controller | 22   |

|    | 3.4   | ML410 Development Board                   | 25   |

| 4 | FTI  | R Base System                                              | 28 |

|---|------|------------------------------------------------------------|----|

|   | 4.1  | Generating a Hardware Platform                             | 28 |

|   | 4.2  | Configuring Software                                       | 33 |

|   |      | 4.2.1 Software Structure                                   | 33 |

|   |      | 4.2.2 Porting FORTRAN to C for PPC405 Embedded Processor   | 35 |

|   |      | 4.2.3 Modifying Converted Code                             | 36 |

|   | 4.3  | Checking Processing Results                                | 37 |

|   | 4.4  | Initial Performance Evaluation                             | 38 |

| 5 | Soft | tware Optimizations                                        | 41 |

|   | 5.1  | Removing Double-precision Math Library Calls               | 41 |

|   |      | Linking IBM PowerPC Performance Libraries                  | 42 |

|   | 5.3  | V2P SW Optimization Results                                | 45 |

| 6 | Har  | dware Optimizations                                        | 46 |

|   | 6.1  | Xilinx APU Floating-point Unit                             | 46 |

|   |      | 6.1.1 F2C Compatibility                                    | 49 |

|   |      | 6.1.2 Recompiling <i>Perflib</i> for Double-precision Only | 49 |

|   |      | 6.1.3 Accuracy and Performance Evaluation                  | 52 |

|   | 6.2  | Dot-product Hardware Co-processor                          | 53 |

|   |      | 6.2.1 Concept                                              | 53 |

|   |      | 6.2.2 Load/Store Unit Design                               | 55 |

|   |      | 6.2.3 Dot-product Core Design                              | 57 |

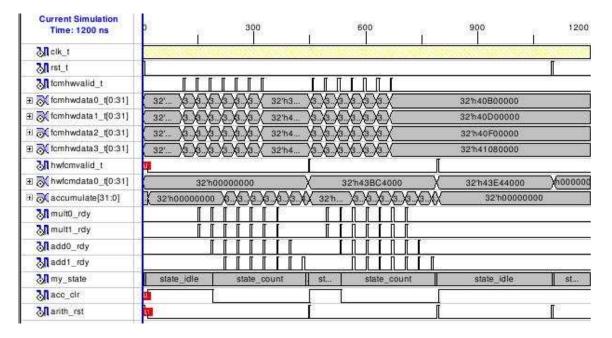

|   |      | 6.2.4 Behavioral Simulation                                | 60 |

|   |      | 6.2.5 System Deployment                                    | 61 |

|   |      | 6.2.6 Software Considerations                              | 62 |

|   |      | 6.2.7 Accuracy and Performance Evaluation                  | 66 |

|   | 6.3  | FPU / Dot-product Compatibility and Integration            | 67 |

|   |      | 6.3.1 Hardware Issues                                      | 67 |

|   |      | 6.3.2 Accuracy and Performance Evaluation                  | 71 |

|   | 6.4  | Increased FPU System Frequencies                           | 73 |

|   |      | 6.4.1 Motivation                                           | 74 |

|   |      | 6.4.2 Meeting Timing                                       | 75 |

|   |      | 6.4.3 Accuracy and Performance Evaluation                  | 77 |

| 7  | Result Analysis                                                             | 78  |

|----|-----------------------------------------------------------------------------|-----|

|    | 7.1 Performance Evaluation                                                  | 78  |

|    | 7.2 Power Estimation                                                        | 80  |

| 8  | Conclusions and Future Work                                                 | 82  |

| Bi | ibliography                                                                 | 86  |

| A  | Building f2c for EDK                                                        | 89  |

| B  | Recompiling IBM PowerPC Perflib for Double-precision Optimization Only      | 92  |

| С  | Select Code Listings                                                        | 94  |

|    | C.1 Makefile for <i>libf2c</i>                                              | 94  |

|    | C.2 Makefile (main) for Double-precision Only <i>Perflib</i>                | 98  |

|    | C.3 Makefile (fpopt) for Double-precision Only <i>Perflib</i>               | 100 |

|    | C.4 Original Top-level FTIR Spectrometry Source (matmos-ipp.f)              | 103 |

|    | C.5 No I/O Top-level FTIR Spectrometry Source (matmos-ipp-chk-noio.f)       | 106 |

|    | C.6 Partial FTIR Spectrometry C-source (xilinx-matmos-ipp-chk_orig.c)       | 109 |

|    | C.7 The <i>dotprod</i> Function (from <i>xilinx-matmos-ipp-chk_orig.c</i> ) | 117 |

|    | C.8 The <i>dotprod</i> Function with HW Support ( <i>dotprod.c</i> )        | 119 |

|    | C.9 FCM Load/Store Module ( <i>apu_fcm_ldst.v</i> )                         | 121 |

|    | C.10Dot-product Module ( <i>fp_dot_prod.vhd</i> )                           | 131 |

# List of Figures

| 1.1 | A conceptual drawing of the MARVEL spacecraft [1] with the MATMOS in-        |    |

|-----|------------------------------------------------------------------------------|----|

|     | strument [3] gathering data through the Martian atmosphere as it points      |    |

|     | towards the Sun                                                              | 2  |

| 1.2 | Solar occultation observations [1, 2]                                        | 2  |

| 2.1 | Simulated Mars occultation spectra [2]                                       | 7  |

|     | An ideal Fourier Transform Spectrometer with only the axial rays shown [1]   | 7  |

|     | The time-domain-sampled interferogram is re-sampled to the path-difference   |    |

|     | domain [1]                                                                   | 9  |

| 2.4 | The BAE RAD750 SBC and the Xilinx V2P board [2]                              | 11 |

| 3.1 | Spatial vs. temporal computing [15]                                          | 15 |

| 3.2 | GARP block diagram [17]                                                      | 16 |

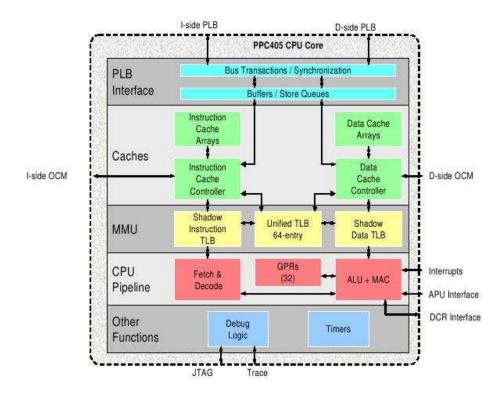

| 3.3 | PPC405 core inside a V4FX hybrid-FPGA [19]                                   | 17 |

| 3.4 | PPC405 pipeline utilization by instruction type [19]                         | 18 |

| 3.5 | MicroBlaze core block diagram [21]                                           | 19 |

| 3.6 | The APU integrates directly into the processor pipeline and decodes soft co- |    |

|     | processor supported instructions [30]                                        | 24 |

| 3.7 | The ML410 development board [32]                                             | 26 |

| 3.8 | ML410 interfaces block diagram [32]                                          | 27 |

| 4.1 | Simulated time-domain interferograms used as input data [2]                  | 29 |

| 4.2 | PPC405 base system configuration                                             | 29 |

| 4.3 | FTIR base system diagram (main components only)                              | 31 |

| 4.4 | The spectrum produced from simulated interferogram data [2]                  | 34 |

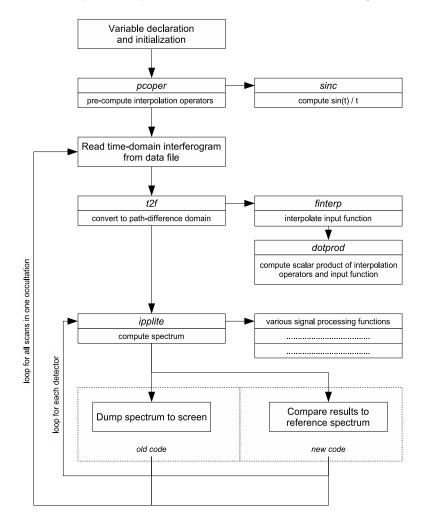

| 4.5 | Software flow of the FTIR spectrometry algorithm                             | 34 |

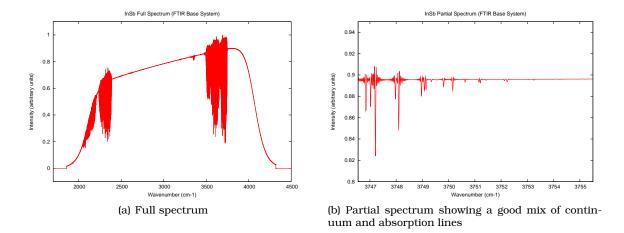

| 4.6 | The spectrum produced by the FTIR base system on the ML410 board $\ .$       | 37 |

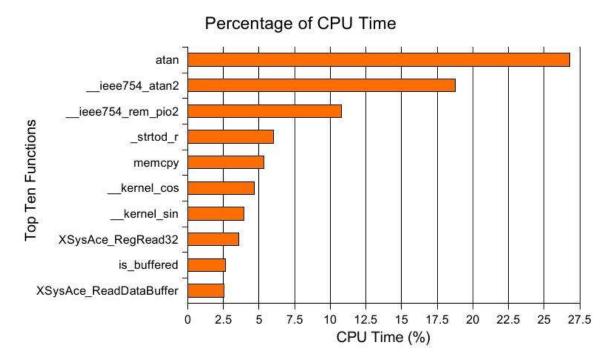

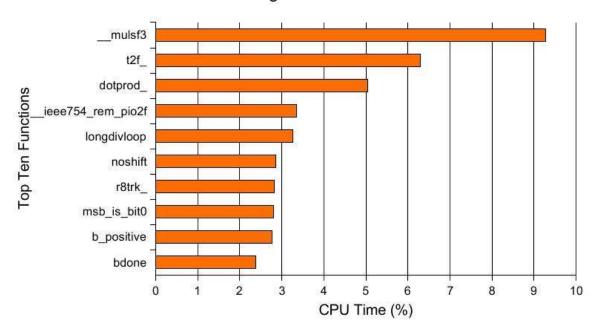

| 4.7 | Profiling results for FTIR base system                                       | 39 |

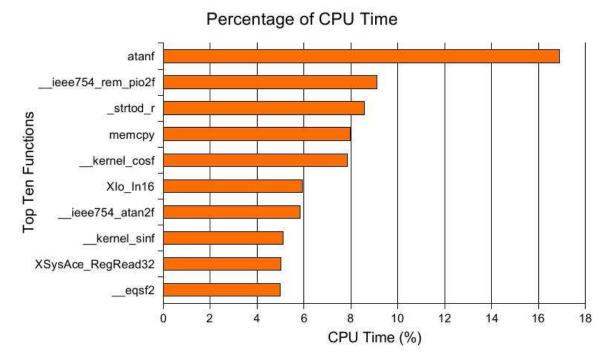

| 5.1 | Profiling results after single-precision math functions optimization         | 42 |

| 5.2  | Profiling results for system with SP math functions and <i>Perflib</i>             | 44 |

|------|------------------------------------------------------------------------------------|----|

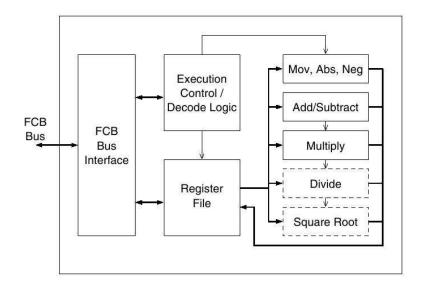

| 6.1  | System diagram of the APU floating-point unit co-processor [34]                    | 47 |

| 6.2  | FTIR system with FPU co-processor                                                  | 48 |

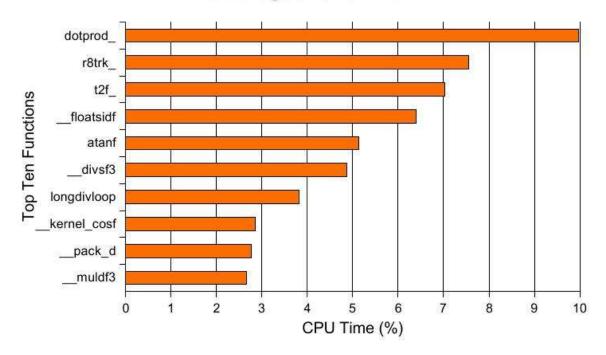

| 6.3  | Profiling results for system with APU-FPU, SP math functions, and DP Perflib       | 52 |

| 6.4  | Cycles needed to complete one iteration of dot-product loop $\ldots \ldots \ldots$ | 55 |

| 6.5  | FCM load/store unit interface to FCB and dot-product co-processor                  | 55 |

| 6.6  | FCM load/store unit state machine                                                  | 56 |

| 6.7  | Resource usage vs. latency for the multiply and add floating-point operators       | 58 |

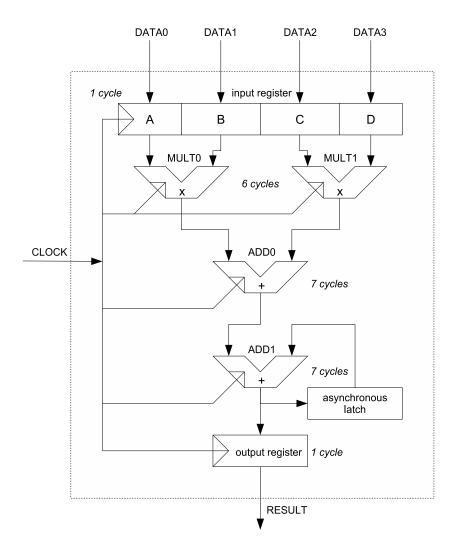

| 6.8  | Dot-product core block diagram                                                     | 59 |

| 6.9  | Dot-product core state machine                                                     | 60 |

| 6.10 | Dot-product core behavioral simulation                                             | 61 |

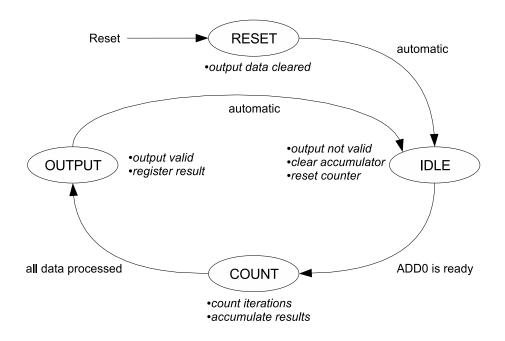

| 6.11 | FTIR system with dot-product co-processor                                          | 63 |

| 6.12 | 2 FTIR system with dot-product and FPU co-processors                               | 68 |

| 6.13 | Profiling results for system with dot-product and FPU co-processors, SP            |    |

|      | math functions, and DP <i>Perflib</i>                                              | 73 |

| 6.14 | DCM configuration for a 266.67 $MHz$ system $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 74 |

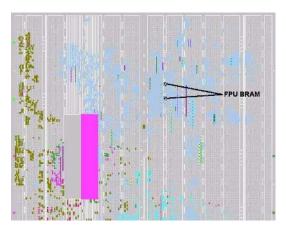

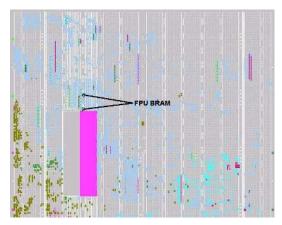

| 6.15 | FPU core placement before $(a,c)$ and after $(b,d)$ manual constraining $\ldots$   | 76 |

| 6.16 | The spectrum produced by the high-frequency FTIR system on the ML410               |    |

|      | board                                                                              | 77 |

| 8.1  | Dual-core concept targeting ML410 development board                                | 84 |

# List of Tables

| 2.1  | Reduction in data volume due to on-board data processing                     | 10 |

|------|------------------------------------------------------------------------------|----|

| 2.2  | Results of NASA JPL research task comparing FTIR spectrometry execution      |    |

|      | times between the BAE RAD750 SBC and the Xilinx V2P board [2] $\ldots$ .     | 11 |

| 3.1  | MicroBlaze Performance for Xilinx FPGAs (with multiplier and barrel shifter) |    |

|      | [20]                                                                         | 19 |

| 3.2  | Most common buses used in Xilinx embedded processor systems [28]             | 23 |

| 4.1  | Device utilization summary for FTIR base system                              | 32 |

| 4.2  | Execution times for FTIR base system on ML410 board and comparison to        |    |

|      | NASA JPL V2P research                                                        | 38 |

| 5.1  | Execution times for system with single-precision math functions              | 41 |

| 5.2  | Execution times for system with SP math functions and <i>Perflib</i>         | 43 |

| 5.3  | Comparison of V4FX and V2P results for system with SP math functions and     |    |

|      | Perflib                                                                      | 45 |

| 6.1  | Xilinx's APU floating-point unit v3.0 [34].                                  | 47 |

| 6.2  | Device utilization summary for FTIR system with FPU co-processor $\ldots$ .  | 50 |

| 6.3  | Optimized floating-point routines provided by <i>Perflib</i>                 | 51 |

| 6.4  | Execution times for system with APU-FPU, SP math functions, and DP Perflib   | 51 |

| 6.5  | Dot-product Core Summary                                                     | 62 |

| 6.6  | Device utilization summary for FTIR system with dot-product co-processor     | 64 |

| 6.7  | Execution times for system with dot-product co-processor, SP math func-      |    |

|      | tions, and <i>Perflib</i>                                                    | 67 |

| 6.8  | Instruction op-codes decoded by the APU controller [25]                      | 69 |

| 6.9  | Device utilization summary for FTIR system with dot-product and FPU co-      |    |

|      | processors                                                                   | 70 |

| 6.10 | DExecution times for system with dot-product and FPU co-processor, SP math   |    |

|      | functions, and DP <i>Perflib</i>                                             | 72 |

| 6.11 | Dot-product core testing with smaller data set                            | 72 |

|------|---------------------------------------------------------------------------|----|

| 6.12 | 2 Execution times for a high-frequency system with APU-FPU, SP math func- |    |

|      | tions, and DP <i>Perflib</i>                                              | 77 |

| 7.1  | Execution times for all V4FX FTIR system builds                           | 78 |

| 7.2  | Execution times for high-frequency FTIR system on ML410 board and com-    |    |

|      | parison to NASA JPL V2P board                                             | 79 |

| 7.3  | Execution times for high-frequency FTIR system on ML410 board and com-    |    |

|      | parison to BAE RAD750 SBC                                                 | 80 |

| 7.4  | Estimated power consumption of V4FX60, V2P, and BAE RAD750                | 81 |

# Assumptions

The target environment is Windows XP Service Pack 2. The development software used is:

- Xilinx ISE 9.1.03i with IP Update 3

- Xilinx Platform Studio (XPS) 9.1.02i (includes EDK and SDK) with GNU-GCC 4.1.1 compiler (Xilinx edition)

- Xilinx ChipScope Pro 9.1.03i

- FORTRAN to C Translator (f2c) version 20060506

- IBM PowerPC Perflib version 1.1

Windows<sup>TM</sup> is trademark of Microsoft Corp. ISE<sup>TM</sup>, ChipScope<sup>TM</sup>, and Virtex<sup>TM</sup> are trademarks of Xilinx Inc. PowerPC<sup>TM</sup> is trademark of IBM.

# **Acronym Glossary**

| APU                                                                                                                                                                              | (V4FX only) that manages FCB-connected co-processors. See subsection 3 on page 22 for a complete description.                          |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ASIC                                                                                                                                                                             | Application Specific Integrated Circuit. An integrated circuit that is cus-<br>tomized for a particular use.                           |  |  |  |  |

| BRAM                                                                                                                                                                             | Block RAM. On-chip memory inside Xilinx FPGAs.                                                                                         |  |  |  |  |

| DCR                                                                                                                                                                              | Device Control Register. See subsection 3.3.3 on page 20.                                                                              |  |  |  |  |

| DMIPS                                                                                                                                                                            | Dhrystone MIPS. A common representation of the Dhrystone benchmark.                                                                    |  |  |  |  |

| EDK                                                                                                                                                                              | Embedded Development Kit. Xilinx design tool for developing processor-<br>based FPGA systems.                                          |  |  |  |  |

| F2C                                                                                                                                                                              | FORTRAN-to-C Converter. A tool for automatic conversion of FORTRAN code to C code. Its use is detailed in subsection 4.2.2 on page 35. |  |  |  |  |

| FCB                                                                                                                                                                              | Fabric Co-processor Bus. See subsection 3.3.3 on page 20.                                                                              |  |  |  |  |

| <b>FTIR</b> Fourier Transform Infrared. Refers to IR spectroscopy, dealing with the frared region of the electromagnetic spectrum. See Chapter 2 on page a complete description. |                                                                                                                                        |  |  |  |  |

| FPGA                                                                                                                                                                             | Field Programmable Gate Array. A programmable device with reconfigurable hardware resources.                                           |  |  |  |  |

| FPU                                                                                                                                                                              | Floating Point Unit. A dedicated hardware co-processor that handles floating-<br>point arithmetic.                                     |  |  |  |  |

| FSL                                                                                                                                                                              | Fast Simplex Link. See subsection 3.3.3 on page 20.                                                                                    |  |  |  |  |

| GCC                                                                                                                                                                              | GNU Compiler Collection. The C compiler used in this thesis.                                                                           |  |  |  |  |

| GMACS                                                                                                                                                                            | Giga multiply-accumulate operations per second.                                                                                        |  |  |  |  |

**ISA** Instruction set architecture.

**LMB** Local Memory Bus. See subsection 3.3.3 on page 20.

- **MARVEL** Mars Volcanic Emissions and Life. A proposed Mars Scout mission. See section 1.1 on page 1 for a complete description.

- **MATMOS** Mars Atmospheric Trace Molecule Spectroscopy. A Fourier transform spectrometer; the primary science instrument on the MARVEL spacecraft. See section 1.1 on page 1 for a complete description.

- **OCM** On-chip Memory. See subsection 3.3.3 on page 20.

- **OPB** On-chip Peripheral Bus. See subsection 3.3.3 on page 20.

- **Perflib** IBM Performance Libraries. A set of floating-point and string manipulation routines that significantly outperform those supplied in GCC.

- **PLB** Processor Local Bus. See subsection 3.3.3 on page 20.

- **PPC405** The PowerPC 405 embedded processor inside the V2P and V4FX hybrid-FPGAs. See subsection 3.3.1 on page 17 for a complete overview.

- **PPC750** The PowerPC 750 processor inside the BAE RAD750 SBC.

- **RAD750** A radiation-hardened SBC developed by BAE. It utilized the PPC750 processor.

- **SBC** Single-board computer.

- **SDK** Software Development Kit. An Eclipse-based Xilinx design tool for developing embedded software.

- **XCL** Xilinx Cache Link. See subsection 3.3.3 on page 20.

- **XPS** Xilinx Platform Studio. Contains EDK, SDK, and a Xilinx version of GCC.

### Chapter 1

### Introduction

### 1.1 Background and Motivation

From the dawn of the Space Age, on-board flight computers have played an ever increasing role in the exploration of the universe. Although constantly improving, the performance of computers used for space flight typically falls a decade or more behind that of modern PCs. This is due to the stringent requirements imposed on space-bound processors and computer peripherals for tolerating the higher dose of radiation that is present outside the Earth's atmosphere. Radiation hardening requires special fabrication and packaging techniques that adversely affects the performance of these components. Although necessary, such measures can limit the scope of scientific experiments to be carried out by the spacecraft.

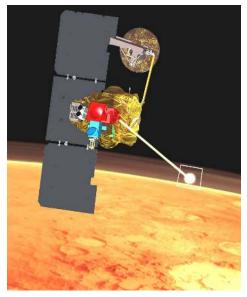

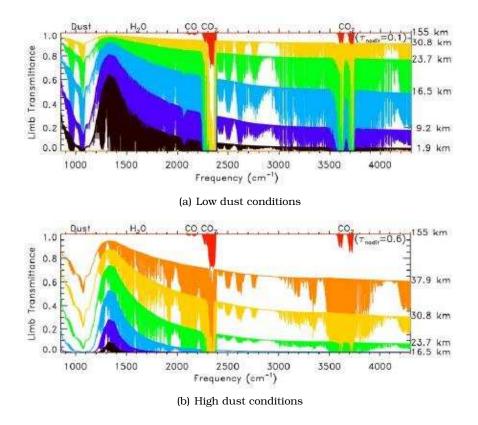

The proposed Mars Scout Mission known as MARVEL<sup>1</sup> is a prime example where data processing demands really push the limits of currently available radiation hardened processors. The goal of this mission is to find evidence of active Martian volcanism and life [3]. Although not funded past the proposal stage, the instruments and scientific experiments from MARVEL are applicable to many similar missions that intend to analyze the chemical composition of an atmosphere. The primary science instrument on the MARVEL spacecraft is a solar occultation Fourier Transform Spectrometer (FTS) called MATMOS<sup>2</sup> used for very sensitive detection of trace gases such as  $CH_4$  and  $N_2O$  that might be produced by life or volcanism (see Figure 1.1 on the following page) [2].

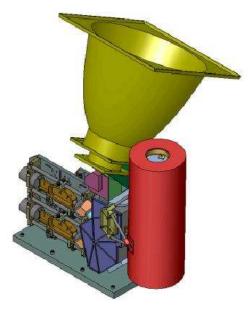

The MATMOS instrument will measure the infra-red spectrum of direct sunlight and produce large volumes of data in two short, 3-minute bursts during its on-orbit observations of sunrise and sunset (see Figure 1.2 on the next page). The remaining orbit time of 112 minutes is available for on-board data processing to reduce data volume prior to down-link. The steps involved in the data processing are computationally intensive and

<sup>&</sup>lt;sup>1</sup>Mars Volcanic Emissions and Life (MARVEL)

<sup>&</sup>lt;sup>2</sup>Mars Atmospheric Trace Molecule Spectroscopy (MATMOS)

(a) MARVEL spacecraft

(b) MATMOS instrument

Figure 1.1: A conceptual drawing of the MARVEL spacecraft [1] with the MATMOS instrument [3] gathering data through the Martian atmosphere as it points towards the Sun

carry a heavy emphasis on floating-point calculations. Currently, two BAE RAD750 (radiation hardened) processors are required to perform such processing. Although these processors have flown successfully on numerous NASA missions, they consume significant power (20 W in a SBC package), and require extensive interface logic [1, 2].

As missions become more complex with more demanding requirements, the traditional approach of using radiation hardened SBCs will no longer be the optimal. MATMOS requires two processors, but other missions may require six or eight, all working simultaneously, all consuming power and adding to the net weight of the spacecraft. A new,

Figure 1.2: Solar occultation observations [1, 2]

more efficient computational platform is urgently needed; one that can execute complex software and at the same time efficiently implement algorithms in hardware like an application-specific integrated circuit (ASIC). Hybrid-FPGAs fit this description as they typically have one or more embedded processor cores immersed in a sea of reconfigurable logic. Although not yet radiation hardened, strong efforts are currently being made to qualify these devices for space flight [4, 5].

In 2005, NASA Jet Propulsion Laboratory looked into the possibility of using the Xilinx Virtex-II Pro (V2P) hybrid-FPGA as the computational platform for MATMOS. That study concluded that the V2P could not keep up with the data processing when performed in software on the embedded PPC405 processor core. The study further suggested that the lack of a hardware FPU on the V2P is responsible for its slow processing times as all floating-point calculations are emulated in the software [2].

In recent years, hybrid-FPGAs have evolved significantly. Currently, the Xilinx Virtex-4FX (V4FX) hybrid-FPGA is the most advanced of its kind that is available commercially. The V4FX brings with it new capabilities for custom co-processor integration, including a soft core single precision FPU with full compiler support. This, along with other improvements, warrants that MATMOS data processing be evaluated again on this new platform with optimizations not tried in the past.

### **1.2 Thesis Description**

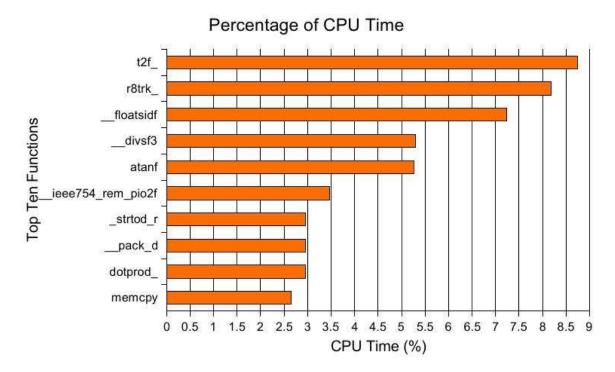

This thesis takes the MATMOS data processing software for FTIR spectrometry and, after porting it to the PPC405 processor, implements various hardware and software optimizations that reduce the overall execution time. Although the main focus is on the V4FX FPGA, the older V2P is also targeted for comparison. The results presented are actual run times on fully functional hybrid-FPGA systems built with Xilinx's Embedded Development Kit (EDK)<sup>3</sup>.

The FTIR spectrometry software is written entirely in FORTRAN and is ported to the PPC405 processor with the help of the FORTRAN-to-C Converter (f2c) and its supporting libraries [6]. Configuring f2c and its libraries to generate valid PPC405 code requires a specific set of compilation and linking options which are discussed in this thesis. Once ported, the FTIR spectrometry software is carefully studied in order to identify areas of

<sup>&</sup>lt;sup>3</sup>This thesis developed out of an internship in the summer of 2006 with the Instrument and Science Data Systems Division at NASA Jet Propulsion Laboratory and continues the work presented in [1].

improvement. Profiling tools are used to locate bottlenecks and computationally intensive portions of the algorithm.

Two software optimizations are evaluated as part of this work:

- Use of non-ANSI single-precision math library functions

- Use of IBM Performance Libraries (Perflib)

The techniques above are compatible with both the V2P and the V4FX. The first technique requires modification of the FTIR spectrometry code to use single-precision math function calls where acceptable. Single-precision arithmetic is performed much faster than double-precision thus reducing the overall execution time. *Perflib* is a set of libraries that replaces string manipulation functions and standard floating-point emulation with hand-optimized routines written specifically for the PPC405 processor [7]. Xilinx EDK provides a version of *Perflib* compiled for string, single, and double-precision optimization. This thesis additionally provides a build of *Perflib* that only optimizes double-precision floating-point arithmetic and discusses where it is applicable.

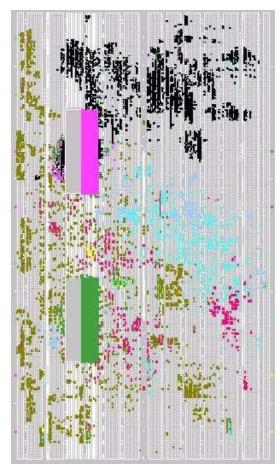

Most of the work, however, deals exclusively with the V4FX and is focused on hardware optimizations, their integration with the system, and compatibility with the software. Different system architectures, memory configurations, and bus frequencies are evaluated to find the optimal solution. The new soft-core single-precision Xilinx FPU and its integration with the auxiliary processor unit (APU) controller is studied extensively. Additionally, a custom HW accelerator that optimizes single-precision dot-product calculations is presented and implemented alongside the FPU thus demonstrating multiple co-processors sharing the same physical hardware interface - a capability not previously tested by Xilinx.

Overall, this thesis achieves a 10x reduction in execution time of the FTIR spectrometry algorithm when compared to a software-only implementation on the V4FX60 FPGA. Only one of two available PPC405 cores is utilized and with minimal changes to the FTIR spectrometry software. This is the fastest implementation of the algorithm on an FPGA platform to date. Although, in its current form, incapable to meet the data processing requirements for MATMOS, future improvements to the software as a well as a dual-core design (presented in this thesis) will come very close.

### 1.3 Overview

This thesis starts with an overview of Fourier transform infrared spectrometry and its past implementation on an FPGA, presented in Chapter 2. Chapter 3 introduces the Virtex-4 FX hybrid-FPGA with a detailed explanation of its main architectural features. Chapter 4 presents an all-software implementation of the FTIR spectrometry algorithm on the V4FX60 FPGA and analyzes the initial performance results. Chapters 5 and 6 describe software and hardware optimizations that reduce the execution time of the FTIR base system, presenting and analyzing performance results along the way. Chapter 7 takes a look at all of the implementations done in this thesis and compares their computational and power performance to that of a general-purpose SBC used for spacecraft data processing. Finally, Chapter 8 concludes the thesis with a brief overview of the work accomplished and presents suggestions for future research in this area.

### **Chapter 2**

## Fourier Transform Infrared Spectrometry

This chapter introduces Fourier transform infrared (FTIR) spectrometry as it is applied to the MATMOS instrument and the MARVEL mission. A description is given of how the solar occultation data is collected, the steps involved in the data processing after collection, and the necessary memory requirements. The results of past work done with the FTIR spectrometry algorithm and the V2P FPGA are also presented.

### **2.1 Data Collection**

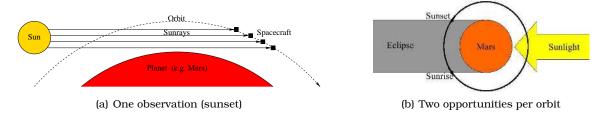

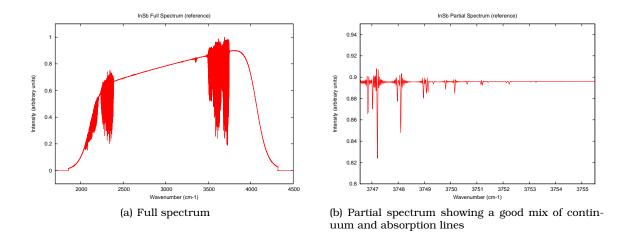

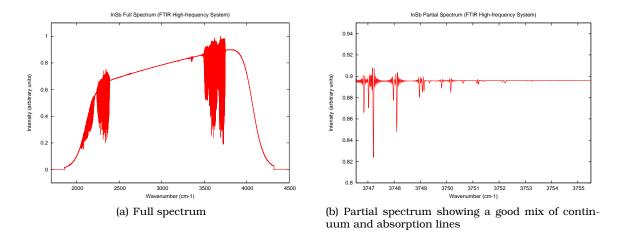

The MATMOS instrument measures the 850-4300  $cm^{-1}$  region of the infra-red spectrum of sunlight as it shines through the Martian atmosphere. This measurement is done at a high 0.02  $cm^{-1}$  spectral resolution necessary to identify certain trace gases. MATMOS records roughly 26 spectra per occultation, with each containing 172,500 spectral elements (see Figure 2.1 on the following page). The duration of an occultation is between 78 and 169 seconds, thus requiring that each spectrum be collected in 3.0 to 6.5 seconds [1].

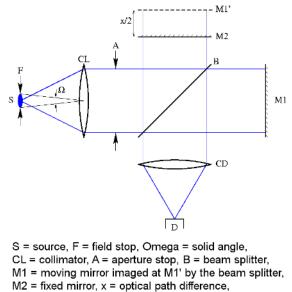

The spectrum is recorded with a Fourier Transform Spectrometer (FTS), a Michelson interferometer in which the optical path difference of light rays is continuously varied with moving mirrors (see Figure 2.2 on the next page). Using photovoltaic detectors, this modulated light is converted to an electric signal known as an interferogram. To attain the high  $0.02 \ cm^{-1}$  spectral resolution, the FTS needs a maximum optical path difference (MOPD) of 25 cm. However, for the best quality, velocity of the scanner moving the mirrors should be constant at the point of zero path difference (ZPD). Thus, for MATMOS, the optical path is increased to 50 cm and a dual-sided interferogram is recorded, with the ZPD in the middle of the scan [1].

Given that the shortest spectrum collection time is 3 seconds, and estimating that the

Figure 2.1: Simulated Mars occultation spectra [2]

CD = condenser, D = detector

Figure 2.2: An ideal Fourier Transform Spectrometer with only the axial rays shown [1]

scanner turn-around time is 0.5 seconds (to reverse direction), the velocity with which the mirror must travel the 50 cm distance is 20 cm/s. Given this velocity, v, and an optical wavenumber, s, the corresponding frequency, f, recorded at the detector is calculated as:

$$f = s \times v \tag{2.1}$$

With the equation above, the highest detectable wavenumber (4300  $cm^{-1}$ ) corresponds to the frequency of 86 kHz. The frequency of the reference laser (internal to the FTS) used to measure the path difference is 129 kHz, given that its wavenumber is 6450  $cm^{-1}$ . Thus, in accordance with the Nyquist Theorem, the minimum sampling frequencies of Analog-to-Digital Converters (ADC) used to record each interferogram are 172 kHz for the solar data and 258 kHz for the laser signal. Oversampling factors of 1.1 and 1.5 are used for the MATMOS FTS in order to improve the quality of the sampled signal. This sets the sampling frequencies to 192 kHz and 384 kHz, respectively [1].

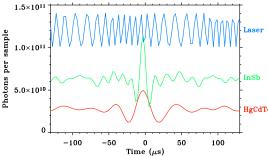

The MATMOS FTS utilizes three separate detectors in the process of collecting occultation spectra. An *HgCdTe* detector is used to collect longer wavelengths ( $12 \ \mu m - 5 \ \mu m$ ) and an *InSb* detector collects shorter wavelengths ( $5 \ \mu m - 2 \ \mu m$ ). An *Ge* detector is used to collect the reference laser interferogram. The *HgCdTe* and *InSb* detectors use 24-bit ADCs while the *Ge* detector uses a 16-bit ADC. Data from the 24-bit ADCs is stored in 32-bit format to match common computer architectures [1].

Thus, given that there are two detectors which output 32-bit data at 192 kHz, a detector that outputs 16-bit data at 384 kHz, a scanner duty cycle of 5/6 (mirror moves for 2.5 out of 3.0 seconds with 0.5 seconds turn-around time), and two 3-minute occultations to observe, the amount of data collected on every orbit is:

$$((2 \times 32bit \times 192000 \frac{samples}{sec}) + (16bit \times 384000 \frac{samples}{sec})) \times (5/6) \times 2 \times (3min \times 60 \frac{sec}{min}) = 5.53Gbit \times 10000 \times 10^{-10} \times 10^{-10}$$

That is equivalent to 659 Mbytes. This will fit in the MATMOS memory bank which has the capacity of 2 Gbytes [1].

### 2.2 Data Processing Steps

The amount of data collected by the MATMOS FTS cannot be transmitted to Earth in its entirety. The data must first be processed by the on-board instrument computer and

Photons per sample HøCdTe 0 -10 -5 0 5 Optical Path Difference ( $\mu$ m)

1.5×10<sup>11</sup>

1.0×10<sup>11</sup>

5.0×10<sup>10</sup>

(a) Frequency modulation can be seen in the timedomain signal

(b) Re-sampling to the path difference domain removes the frequency modulation

InSt

HgCdTe

10

Figure 2.3: The time-domain-sampled interferogram is re-sampled to the path-difference domain [1]

compressed to a reasonable amount for transmission. The steps involved in this process are summarized in this section.

The ADCs used to convert solar data from the HgCdTe and InSb detectors cannot be triggered externally. The conversion process runs continuously and produces a timedomain data stream with each value corresponding to a point in time. Through resampling, this data stream must be converted to the path-difference domain in order to remove frequency modulation in the time-domain caused by variations of the mirror velocity (see Figure 2.3) [1, 8].

Re-sampling reduces the number of points from  $192kHz \times 2.5sec = 480,000$  for each solar detector to  $2^{18} = 262,144$  points for the *HgCdTe* detector and  $2^{19} = 524,288$  for the InSb detector. Additionally, laser interferogram data is no longer needed after re-sampling and can be freed from memory. This data accounts for 1/3 of all raw data, as shown in the calculation below [1].

$$\frac{16bit \times 384000 \frac{sample}{sec}}{(2 \times 32bit \times 192000 \frac{samples}{sec}) + (16bit \times 384000 \frac{sample}{sec})} = \frac{1}{3}$$

Thus, removing the laser interferogram data reduces data volume by 3/2. From the initial raw interferogram data, the net reduction due to re-sampling is:

$$\frac{2 \times 480000}{262144 + 524288} \times \frac{3}{2} = 1.83$$

Next, phase correction (using convolution) is performed in order to make the interferogram symmetrical about the ZPD. Being symmetrical, the two halves of the interferogram

| DATA PROCESSING STEP        | <b>REDUCTION FACTOR</b> | DATA SIZE (MBYTES) |

|-----------------------------|-------------------------|--------------------|

| Raw Interferogram           |                         | 659.18             |

| Interferogram Re-sampling   | 1.83                    | 360.21             |

| Phase Correction            | 2.00                    | 180.10             |

| Fast Fourier Transformation | 6.10                    | 29.53              |

| Spectra Averaging           | 2.00                    | 14.76              |

| Lossless Compression        | 1.80                    | 8.20               |

| NET DATA REDUCTION          | 80.37                   | 8.20               |

Table 2.1: Reduction in data volume due to on-board data processing

can be averaged together further reducing the amount of data by a factor of 2. Following this step, the spectrum is computed with a fast Fourier transform (FFT) which produces an output with a smaller dynamic range than the interferogram. This resulting data can be represented with 16 bits instead of the 32 bits originally used for the interferogram (2x data reduction). Additional data reduction is attained from reducing the spectral range. The computed spectrum has a range of 5243  $cm^{-1}$ for each solar detector, yet the data desired is in the 850-4300  $cm^{-1}$  range and combined into one channel. Altogether, for the two solar detectors, the FFT reduces data volume by the factor computed below [1].

$$2 \times 2 \times \frac{5243 cm^{-1}}{(4300 cm^{-1} - 850 cm^{-1})} = 6.1$$

The final two steps in reducing the data volume are spectra averaging and compression. Averaging scans taken above the atmosphere reduces data volume by a factor of 2. Lossless compression achieves a 1.8 reduction in the data volume. The combined reduction in the volume of data to be transmitted to Earth is summarized in Table 2.1[1].

### 2.3 First Evaluation on FPGAs

In 2005, NASA Jet Propulsion Laboratory evaluated the performance of the FTIR spectrometry algorithm on the V2P FPGA and compared it to the radiation hardened BAE RAD750 SBC. The FPGA hosted a PPC405 CPU implementation of the algorithm without putting any portions in the reconfigurable hardware. Figure 2.4 on the following page gives a brief overview of the two processing platforms. Table 2.2 on the next page presents the results from that research task. The results clearly indicate that the V2P falls far behind the RAD750. Furthermore, not even the RAD750 can process the data fast enough to meet the time requirement of 112 minutes. Thus, not one but two RAD750 SBCs are required for the MATMOS instrument.

###

Figure 2.4: The BAE RAD750 SBC and the Xilinx V2P board [2]

| Lossless Compression Total (112 min available) | 1<br>130 min | 1<br>4200 min | 1<br>1020 min |

|------------------------------------------------|--------------|---------------|---------------|

| Spectra Averaging                              | 2            | (10)          | (3)           |

| Fast Fourier Transformation                    | 15           | 272           | 90            |

| Phase Correction                               | 42           | 488           | 142           |

| Non-Linearity Correction                       | 1            | 14            | 4             |

| Interferogram Re-sampling                      | 69           | 3404          | 780           |

| Reject Dark Interferograms                     | <1           | <1            | <1            |

| Software Component                             |              |               | w/Perflib     |

| Memory:                                        | 128 MB       | 128 MB        | 128 MB        |

| Clock Speed:                                   | 133 MHz      | 300 MHz       | 300 MHz       |

| <b>Operating System:</b>                       | VxWorks      | Linux         | Linux         |

| Processor:                                     | RAD750       | Xilinx        | Xilinx        |

Table 2.2: Results of NASA JPL research task comparing FTIR spectrometry execution times between the BAE RAD750 SBC and the Xilinx V2P board [2]

There are a couple of reasons why the V2P takes so much longer to process the data, namely cache size, instruction issue rate, and hardware floating-point support. The RAD750 SBC contains a variant of the PowerPC750 (PPC750) processor with 32 Kbytes data and 32 Kbytes instruction L1 cache [9]. The V2P has a PPC405 processor with 16 Kbytes data and 16 Kbytes instruction L1 cache [10]. In an application such as this, the tremendous data processing requires frequent accesses to external memory. A larger L1 cache means that more data can fit in this high speed memory resulting in fewer cache misses and fewer accesses to main memory, which carries with it a high latency [1].

Another reason for the RAD750 performing so much better is the instruction issue rate of the PPC750 processor. As this processor is a superscalar, multiple instructions can be fetched, dispatched, and executed in one cycle. In particular, the PPC750 can fetch up to four instructions, dispatch up to two instructions, and execute up to six instructions per clock cycle. The PPC405 processor is a scalar processor with a single issue execution pipeline [11, 12].

The lack of a hardware floating-point unit in the V2P, however, is an even larger performance hit than the size of the cache or the instruction issue rate. The RAD750 has a hardware floating-point unit which performs all floating-point operations and reports the results back to the processor. The V2P FPGA does not have a hardware floating-point unit requiring that all floating-point operations be emulated in the software. Software emulation is inherently slower than computation done with dedicated hardware. The steps in the FTIR spectrometry algorithm require significant floating point calculations. Even with its higher processor frequency ( $300 \ MHz \ vs. 133 \ MHz$ ) and special optimization library (IBM *Perflib*), the V2P still lags far behind the RAD750. Although its small size/weight and low power consumption is very favorable for future space flight, in its basic configuration the V2P does not meet MATMOS's data processing requirements [1].

The only way a hybrid-FPGA solution could come close to the performance of the RAD750 is by integrating a dedicated floating-point unit, implementing certain portions of the algorithm in the FPGA fabric, and optimizing the code to make the best use of the hardware resources on the FPGA. This, along with the advanced capabilities of the Xilinx Virtex-4FX FPGA (described in the next chapter), is the motivation for this thesis.

# Chapter 3 Xilinx Virtex-4 FX Hybrid-FPGA

New innovations in the field of reconfigurable computing have recently led to the development of FPGAs with multiple embedded processors. Such a computing platform, known as a hybrid-FPGA, offers the versatility of running diverse software applications on embedded processors while at the same time taking advantage of tightly coupled reconfigurable hardware resources. This allows for the exploitation of coarse-grain data-parallelism via the software as well as fine-grain data-parallelism via the reconfigurable hardware. The recently released Virtex-4 FX (V4FX) FPGA is a true hybrid-FPGA with up to two embedded PPC405 processors. Additionally, the auxiliary processor unit (APU) controller inside each PPC405 core can interface to custom hardware co-processors implemented in the FPGA fabric. This efficient, high speed, low latency interface feeds directly into the processor instruction pipeline, allowing for the extension of the instruction set architecture with user defined instructions (instruction augmentation). With these and other features, the Xilinx Virtex-4 FX FPGA delivers breakthrough performance previously impossible with traditional processors and reconfigurable devices.

This chapter introduces the Virtex-4 FPGA, describes the architecture of the V4FX hybrid-FPGA, and provides an overview of its main features. In particular, processor choices, system buses, and the new auxiliary processor unit controller are described in detail. The chapter concludes with an overview of the target platform for this thesis - the Xilinx ML410 development board.

### 3.1 Xilinx Virtex-4 FPGA Overview

Devices in Xilinx's Virtex family of FPGAs are known as Platform FPGAs because of the features they deliver for use in system-on-chip (SoC) applications. Built in low power, 90 *nm* technology, the Virtex-4 comes in three flavors that are tailored to specific applications.

The three Virtex-4 platforms, in the order of release, are:

- LX: Logic optimized

- SX: Signal processing optimized

- FX: Full-featured, with embedded processors

The LX platform has the most general purpose logic resources and is targeted at logicintensive applications, such as complex interfaces and advanced digital systems. The SX platform has the largest amount of specialized digital signal processing (DSP) blocks, making it ideal for signal processing applications such as filter design or digital image processing. The full-featured FX platform has the highest amount of on-chip memory resources and comes with up to two embedded processors, making it a true hybrid-FPGA. This is a great platform for implementing complete embedded systems that require a robust interface between software and custom hardware [13].

In all three platforms, the Virtex-4 FPGA comes with a rich set of common features, including:

- 500 *MHz* system clocking

- 1+ Gbps IOBs (input/output blocks)

- 256 giga multiply-accumulate operations per second (GMACS) DSP circuitry (18x18)

- Block RAM with built-in error checking and correction (ECC)

The features above, and others not listed, make the Virtex-4 a very powerful FPGA platform that is suitable for a wide range of applications. According to Xilinx, this FPGA consumes much less power than other competing 90 *nm* FPGAs, making it ideal for lowpower designs [14].

### 3.2 The Hybrid-FPGA Concept

A hybrid-FPGA is a device that contains one or more processor cores inside a sea of reconfigurable logic resources. The Virtex-4 FX FPGA is a true hybrid-FPGA as it contains up to two PowerPC 405 processor cores embedded inside the FPGA fabric.

#### **3.2.1** Motivation

The hybrid-FPGA concept emerged from the trade-off that developers had to make when selecting a computing platform to meet their processing requirements. The trade-off was

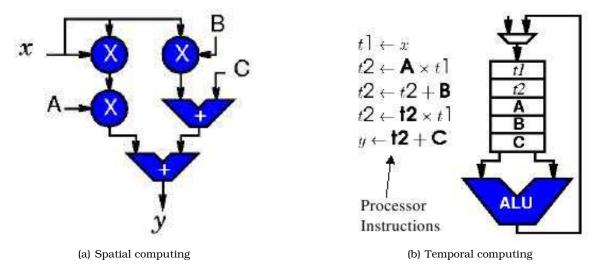

Figure 3.1: Spatial vs. temporal computing [15]

between using FPGAs that took advantage of spatial computing and general-purpose processors (GPPs) that took advantage of temporal computing (see Figure 3.1). Under spatial computing, the functionality and connectivity of hardware elements is fixed. Under temporal computing, a processor runs a fixed set of instructions while sharing a functional unit. While spatial computing may offer more efficient implementations of certain algorithms (due to dedicated hardware), temporal computing is more flexible and can accommodate complex, irregular tasks [15].

The hybrid-FPGA offers the benefits of both spatial and temporal computing by including a processor core among the reconfigurable logic and providing an interface between the software and hardware domains. This is an ideal platform for high performance computing applications that are characterized by complex software tasks which interface with algorithms implemented in hardware.

#### **3.2.2 Previous Work**

A distant relative of the hybrid-FPGA concept is the RISC4005/R16 FPGA processor implementation by Philip Freidin (Fliptronics) in 1991 [13]. The RISC4005/R16 features a 16 bit RISC processor core implemented on Xilinx's XC4005 FPGA. The instruction set architecture (ISA) is similar to AMD 29000 RISC and can be extended. This design, however, uses 75% of the available resources on the FPGA and leaves little room for other hardware components [16]. The V2P and the V4FX FPGAs feature embedded processors that do not take additional logic resources, thus leaving much room for custom hardware

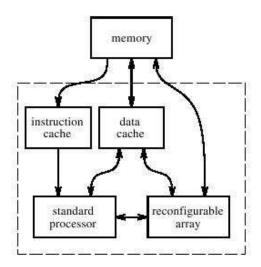

Figure 3.2: GARP block diagram [17]

designs.

The GARP processor (Berkeley, 1997) is architecturally very similar to the V2P and the V4FX. GARP contains a MIPS-II-based processor and a reconfigurable array all on one chip (see Figure 3.2). Both the processor and the reconfigurable array have independent access to the off-chip memory. GARP's reconfigurable array consists of blocks similar to the CLBs of the Xilinx 4000 series. By today's standards, such reconfigurable logic is rather simplistic as it does not offer some of the more sophisticated features such as DSP blocks, dedicated multipliers, and multi-gigabit transceivers (MGTs). Furthermore, GARP was never actual built and exists only on paper (although the full layout has been done). However, GARP does offer some features that the V2P and the V4FX do not have, the most notable being fast, on-the-fly reconfiguration. The main processor in GARP can issue a command to very quickly reconfigure the hardware. The V2P and the V4FX may need seconds to do a full reconfiguration [17].

### 3.3 Virtex-4 FX Hybrid-FPGA

The V4FX FPGA is a relatively new device and is considered a true hybrid-FPGA as it comes with up to two embedded PowerPC 405 processor cores. In addition to the standard features on all Virtex-4 FPGAs, the V4FX also includes:

- 450 MHz, 680 DMIPS PowerPC 405 processing

- 622 Mbps 6.5 Gbps multi-gigabit transceivers (RocketIO MGTs)

Figure 3.3: PPC405 core inside a V4FX hybrid-FPGA [19]

• Auxiliary processing unit (APU) controller

The following sections will discuss V4FX architecture, including the processing choices (hard PowerPC 405 or soft MicroBlaze), the system interfaces, and the APU controller. The APU controller is a key component in the V4FX hybrid-FPGA as it provides an efficient interface to HW accelerators in the FPGA fabric and supports ISA extension (instruction augmentation) [18].

#### 3.3.1 PowerPC 405 Embedded Hard Processor

Developed by IBM, up to two PPC405 processors are embedded in the V4FX hybrid-FPGA as hard IP cores (do not take additional resources). Natively, the PPC405 is a big-endian processor although it can switch to the little-endian mode. The PPC405 features (as shown in Figure 3.3) [19]:

- Up to 450 *MHz* operation

- 32-bit Harvard architecture (RISC, separate data and instruction caches / interfaces)

| Pipeline Stage<br>Instruction Type | Instruction<br>Fetch<br>Buffer | Decode /<br>Dispatch              | Execute        | Write-Back  | Load Write<br>Back |

|------------------------------------|--------------------------------|-----------------------------------|----------------|-------------|--------------------|

| Integer / Logical                  | Fetch                          | Decode /<br>Dispatch              | Execute        | Write GPR   |                    |

| Branch                             | Fetch                          | Predict /<br>Decode /<br>Dispatch | Execute        |             |                    |

| Store                              | Fetch                          | Decode /<br>Dispatch              | Address<br>Gen | Cache write |                    |

| Load                               | Fetch                          | Decode /<br>Dispatch              | Address<br>Gen | Cache read  | Write GPR          |

Figure 3.4: PPC405 pipeline utilization by instruction type [19]

- Five-stage single issue execution pipeline

- 32 general-purpose registers (GPRs)

- 16 KB 2-way set-associative instruction and data caches

- Write-back (default) or write-through policy for data cache

- 64-entry unified HW TLB memory management unit (MMU)

- Variable page sizes (1KB 16KB)

- Block RAM (BRAM) interface via on-chip memory (OCM) controllers

The PPC405 five-stage pipeline consists of a fetch, decode, execute, write-back, and load write-back stages (see Figure 3.4). The fetch and decode stages ensure a well fed instruction pipeline with up to two instructions in the fetch queue. The single execute unit contains the GPR register file, the arithmetic logic unit (ALU), and the multiplyaccumulate (MAC) unit, but it does not include a floating-point unit (FPU). The PPC405 can natively handle 32-bit PowerPC integer instructions only. However, the APU controller provides an interface to execute instructions that are not part of the PPC405 ISA in custom co-processors, which may include a FPU in the FPGA fabric [19].

| FPGA                    | SIZE       | CLOCK FREQ.    | DMIPS | PERFORMANCE     |

|-------------------------|------------|----------------|-------|-----------------|

| Virtex-5                | 1,010 LUTs | <b>210</b> MHz | 240   | 1.15  DMIPS/MHz |

| Virtex-4                | 1,809 LUTs | 160 MHz        | 184   | 1.15  DMIPS/MHz |

| Spartan-3 (Performance) | 1,843 LUTs | 100 <i>MHz</i> | 115   | 1.15  DMIPS/MHz |

| Spartan-3 (Size)        | 1,350 LUTs | 100 MHz        | 92    | 0.92  DMIPS/MHz |

Table 3.1: MicroBlaze Performance for Xilinx FPGAs (with multiplier and barrel shifter) [20]

Figure 1-1: MicroBlaze Core Block Diagram

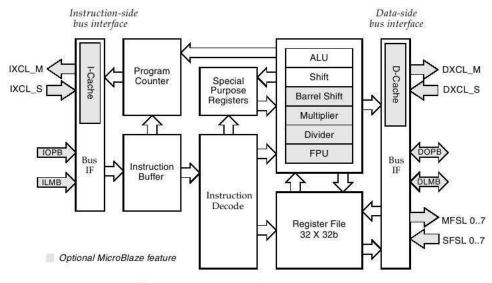

Figure 3.5: MicroBlaze core block diagram [21]

#### 3.3.2 MicroBlaze Soft Processor

An alternative to the hard PPC405 processor is the soft MicroBlaze core. Soft cores are implemented from reconfigurable resources and are thus very portable between different FPGA families. Table 3.1 shows the size and performance of the MicroBlaze processor on different Xilinx FPGAs. As a reference, the V4FX60 FPGA (targeted in this thesis) has 50,560 LUTs.

Like the PPC405, the MicroBlaze is a 32-bit RISC processor. Except for the amount of FPGA resources, there is no limit to how many MicroBlaze processors can be instantiated on a single FPGA. The MicroBlaze is a big-endian processor with the features listed below [21]. The MicroBlaze core block diagram is shown in Figure 3.5.

• 32-bit Harvard architecture (RISC, separate data and instruction caches / interfaces)

- Three-stage (area optimized) or five-stage (performance optimized) single issue execution pipeline

- 32 general-purpose registers (GPRs)

- Up to 64 KB 1-way associative instruction and data caches via Xilinx CacheLink (XCL) interface

- Write-through policy for data cache

- Block RAM (BRAM) interface via local memory bus (LMB) controllers

- Optional features (selectable by user):

- Hardware barrel shifter

- Hardware multiplier

- Hardware divider

- Single-precision FPU

The depth of the pipeline can be configured as either three-stage (area optimized) or fivestage (performance optimized). The three-stage pipeline has only the fetch, decode, and execute stages. The five-stage pipeline has the fetch, decode, execute, access memory, and write-back stages. The optional FPU is a very popular features as it provides seamless support for single-precision floating-point operations and delivers up to 50 MFLOPs peak performance. The MicroBlaze processor also support hardware co-processor integration via the fast simplex link (FSL) interface (also available on PPC405 systems). The FSL channels provide unidirectional high speed data streams and interface directly into the processor pipeline. In a PPC405 system, the APU controller with the fabric co-processor bus (FCB) is a better choice for communicating with hardware co-processors as this interface supports instruction decoding and larger data transfers. The MicroBlaze processor can host up to eight FSL channels (each with one input and output port) [21].

#### **3.3.3 System Interfaces**

This section describes the system interfaces that are typical to a SoC implementation on a Xilinx V4FX FPGA. Both PPC405 and MicroBlaze interfaces are presented. As both processors are in Harvard architecture, the interfaces listed below (except DCR, FCB, and FSL) have an instruction and data side denoted with the letters 'I' and 'D', respectively, in front of the interface name (for example, IPLB, DPLB, IOPB, DOPB, etc...). Master and slave interfaces are denoted with the letters 'M' and 'S', respectively, in front of the interface name (for example, MOPB, SOPB, etc...).

- **PLB** (Processor Local Bus PPC405 only). This bus is for high speed and high performance peripherals, such as memory. The processor accesses this bus through the instruction and data cache controllers. Separate 32-bit address and 64-bit data buses are provided. The PLB interface can have up to 16 masters and 16 slaves, with arbitration [19, 22].

- **OPB** (On-chip Peripheral Bus PPC405 and MicroBlaze). This bus is for less demanding peripherals that do not need to communicate with the processor very frequently and do not need high bandwidth (for example, UART controller). Peripherals on the OPB communicate with the processor either directly (for MicroBlaze) or via a bridge to the PLB (for PPC405). The OPB can have up to 16 masters and 16 slaves, with arbitration. This bus supports 32-bit transactions [19, 23].

- **DCR** (Device Control Register PPC405 only). This 32-bit data, 10-bit address bus is for accessing on-chip configuration and IP control registers. Through this bus, the processor can control IP cores directly. Multiple IPs are connected to this bus in a daisy-chain fashion (up to 16 IPs in a chain) [19, 24].

- **OCM** (On-chip Memory PPC405 only). This bus is for connecting local on-chip memory to the processor. Non-cacheable access to this memory usually occurs in a 1:1 or 2:1 time frame ratio compared to access to cached memory through the cache controllers (depending on processor frequency and amount of memory). This bus supports 32-bit bi-directional data-side memory transfers and 64-bit uni-directional instruction-side memory transfers. There is no bus arbitration, so one processor master/slave pair is allowed. On-chip memory connected through the OCM interface often holds interrupt routines that require low-latency access or frequently used data arrays such as filter coefficients in DSP applications. Being non-cacheable, such usage of on-chip memory reduces cache pollution and thrashing [19, 25].

- **FCB** (Fabric Co-processor Bus PPC405 only). This 32-bit bus is used for connecting fabric co-processor modules (FCM) to the auxiliary processor unit (APU) controller. There is no bus arbitration, so one processor master / multiple slaves are allowed. Each slave must decode a unique set of instructions presented on the FCB. This

interface provides a high bandwidth and low latency connection that integrates directly into the processor pipeline. The FCB is the primary choice for integrating high performance co-processors to the PowerPC system as it provides a mechanism for instruction decoding and allows for larger data transfers (quad word load/store) [26].

- **FSL** (Fast Simplex Link PPC405 and MicroBlaze). This 32-bit bus provides a unidirectional point-to-point communication interface (FIFO-based) between any two elements on the FPGA. The MicroBlaze processor can communicate with up to eight FSL channels (in each direction). The PPC405 supports up to 32 FSL channels through the APU controller [27].

- **LMB** (Local Memory Bus MicroBlaze only). This local 32-bit bus is used to connect BRAM memory to the MicroBlaze processor. Separate read and write ports are provided. There is no arbitration, so one processor master and up to 16 slaves are allowed [28].

- **XCL** (Xilinx Cache Link MicroBlaze only). This is the MicroBlaze cache interface, providing a point-to-point link between main memory and cache implemented out of on-chip memory. Up to two MicroBlaze processors can use the XCL interface as main memory controllers have only 4 XCL ports (each processor requires one port for data and one for instruction) [29].

Table 3.2 on the following page provides an overview of the five most common buses in a Xilinx embedded processor system (PLB, OPB, DCR, OCM, and LMB).

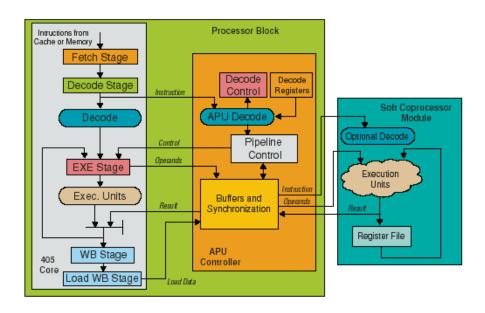

#### 3.3.4 Auxiliary Processor Unit Controller

Arguably the most notable feature of the V4FX is the auxiliary processor unit (APU) controller that tightly couples custom co-processors built in the FPGA fabric to the PPC405 core. It is the APU that sets the V4FX apart from its predecessor, the V2P.

The APU provides accelerated system performance by managing the interface between a fabric co-processor module (FCM) and the processor core. As seen in Figure 3.6 on page 24, the APU connects into the PPC405 instruction pipeline and is able to negotiate the transfer of particular instructions and data to the appropriate FCMs that support such operations. This high bandwidth and low latency direct interface to HW accelerators makes it possible to extend the native PowerPC 405 instruction set with certain special instructions as well as with completely custom, user-defined instructions [30].

|                                    | Co       | reConnect Bu          | ses      | Other Buses |            |

|------------------------------------|----------|-----------------------|----------|-------------|------------|

| Feature                            | PLB      | OPB                   | DCR      | ОСМ         | LMB        |

| Processor family                   | PPC405   | PPC405,<br>MicroBlaze | PPC405   | PPC405      | MicroBlaze |

| Data bus width                     | 64       | 32                    | 32       | 32          | 32         |

| Address bus width                  | 32       | 32                    | 10       | 32          | 32         |

| Clock rate, MHz (max) <sup>1</sup> | 100      | 125                   | 125      | 375         | 125        |

| Masters (max)                      | 16       | 16                    | 1        | 1           | 1          |

| Masters (typical)                  | 2-8      | 2-8                   | 1.       | t           | ti:        |

| Slaves (max) <sup>2</sup>          | 16       | 16                    | 16       | Ť           | 16         |

| Slaves (typical)                   | 2-6      | 2-8                   | 1-8      | t           | 10         |

| Data rate (peak) <sup>3</sup>      | 800 MB/s | 500 MB/s              | 500 MB/s | 1500 MB/s   | 500 MB/s   |

| Concurrent read/write              | Yes      | No                    | No       | No          | No         |

| Address pipelining                 | Yes      | No                    | No       | No          | No         |

| Bus locking                        | Yes      | Yes                   | No       | No          | No         |

| Retry                              | Yes      | Yes                   | No       | No          | No         |

| Timeout                            | Yes      | Yes                   | No       | No          | No         |

| Fixed burst                        | Yes      | No                    | No       | No          | No         |

| Variable burst                     | Yes      | No                    | No       | No          | No         |

| Cache fill                         | Yes      | No                    | No       | No          | No         |

| Target word first                  | Yes      | No                    | No       | No          | No         |

| FPGA resource usage                | High     | Medium                | Low      | Low         | Low        |

| Compiler support for load/store    | Yes      | Yes                   | No       | Yes         | Yes        |

Notes:

Maximum clock rates are estimates and are presented for comparison only. The actual maximum clock rate for each bus is dependent on device family, device speed grade, design complexity, and other factors.

2. Maximum value set by maximum allowed parameter value specified in the core. Actual bus specification does not limit this value.

3. Peak data rate is the maximum theoretical data transfer rate at the clock rate shown for each bus.

Table 3.2: Most common buses used in Xilinx embedded processor systems [28]

Figure 3.6: The APU integrates directly into the processor pipeline and decodes soft coprocessor supported instructions [30]

The APU supports three types of instructions:

- APU load/store (direct to hardware, up to 16 bytes, quadword)

- PPC floating-point instructions

- User-defined instructions (UDIs)

To determine whether an instruction is CPU-bound or APU-bound, both the CPU and the APU simultaneously attempt to decode the instruction. If the instruction is found to be a CPU-bound instruction, execution continues as normal and the APU does not get involved further. If the instruction is found to be an APU-bound instruction, the CPU waits for a response back from the APU, which determines whether this instruction is a supported (valid) or unsupported (invalid). An exception is generated if the CPU does not get a response within one cycle. If the APU responds that the instruction is indeed a valid one, operands are fetched from the CPU to the APU and passed to the hardware co-processor for execution. The result from the hardware co-processing is delivered back to the CPU (via the APU) into the write-back stage [30].

Since the CPU typically runs at a higher frequency than the custom FCMs, a synchronization mechanism is necessary to handle the transfer of data between the two units. The APU manages this synchronization completely independently. The APU knows when to read operands from the CPU and when to return with the results. The developer never needs to get involved in managing the CPU-APU interface, thus streamlining the design process [30].

The APU supports both autonomous and non-autonomous instructions. Autonomous instructions do not require the CPU to stall and wait for the result while the instruction is being executed. Non-autonomous instructions do require the CPU to stall and wait for the result. These instructions can be further broken down into blocking and non-blocking instructions. Blocking instructions suppress all asynchronous exceptions and interrupts which may be generated while the instruction is being executed. Non-blocking instructions allow for exceptions and interrupt to be serviced, but in effect must flush the HW co-processor [30].

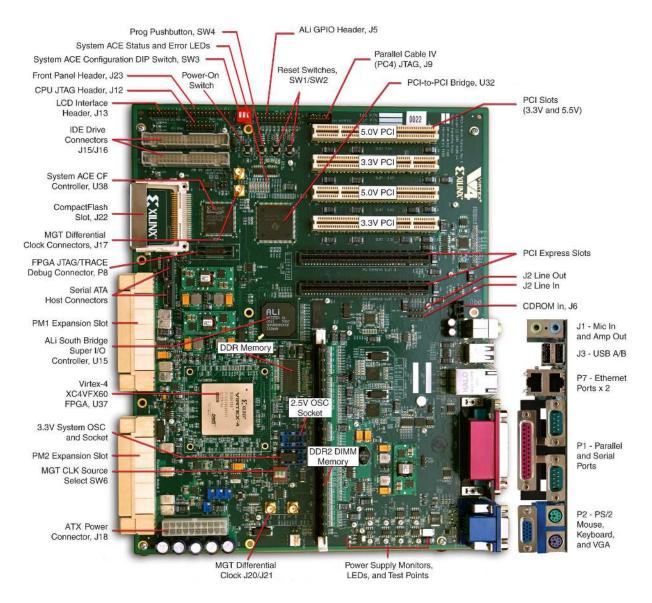

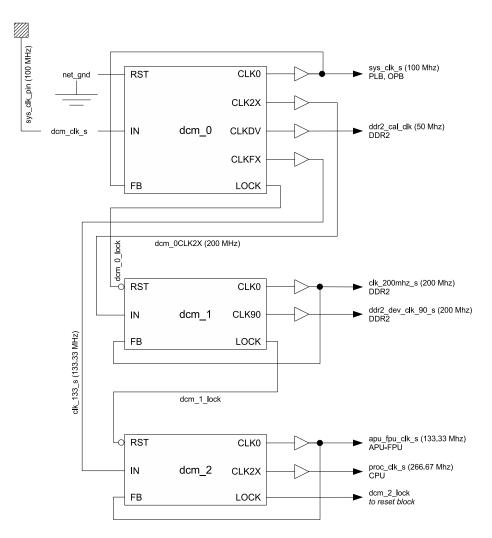

## 3.4 ML410 Development Board

The target platform for this thesis is the Xilinx ML410 Development Board which features the V4FX60 FPGA. This FPGA is in the -11 speed grade thus allowing the dual embedded PPC405 cores to operate at up to 400 MHz when the APU controller is not in use or up to 275 MHz when the APU controller is in use (as is the case for much of the work in this thesis) [31].

This board comes in a standard ATX form factor with 64 Mbytes of component DDR memory (32-bit) and 256 Mbytes DDR2 DIMM memory (64-bit). The DDR memory is capable of running at up to 266 MHz, however the available memory controller IP core operates at 100 MHz, thus delivering PC-1600 performance (1.6 Gbytes/sec). In the case of DDR2, the controller IP core can integrate with a 266 MHz memory module, however, the module supplied with the board is capable of running at up to 200 MHz, thus delivering PC2-3200 performance (3.2 Gbytes/sec) [32].

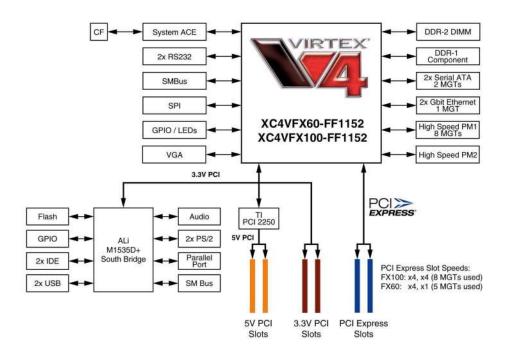

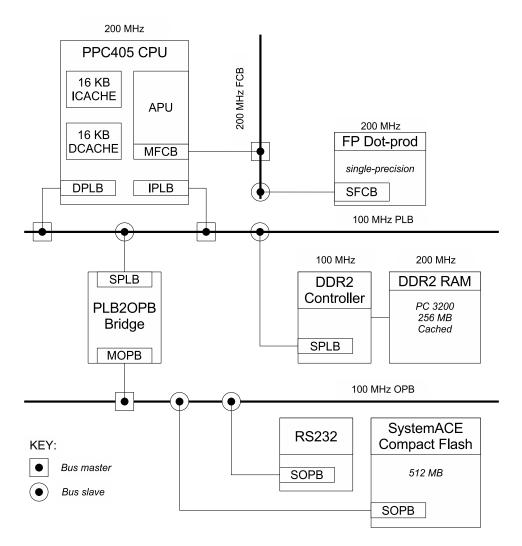

The board also features a SystemACE compact flash controller, dual Ethernet PHYs, PCI and PCI express interfaces, VGA interface, USB ports, and much more. The SystemACE controller can be used to access data on a compact flash card (non-volatile storage) and also has the ability to configure the FPGA with hardware bitstreams and software object codes stored in one of eight configuration locations on the card. A compete listing of all the features on the ML410 board is presented in Figure 3.7 on the following page. A block diagram of the interconnection between peripherals is shown in Figure 3.8 on page 27 [32].

Figure 3.7: The ML410 development board [32]

Figure 3.8: ML410 interfaces block diagram [32]

# Chapter 4

## **FTIR Base System**

This chapter presents the hardware generation and software configuration of the FTIR base system. The starting point for this work is FORTRAN source code and simulated interferograms provided by NASA Jet Propulsion Laboratory as a result of the V2P research task [2]. The software contains only the three most time consuming data processing steps in Table 2.2 on page 11 - interferogram re-sampling, phase correction and fast Fourier transformation. The base system, implemented on the ML410 development board, must have adequate hardware resources to execute the software, which must first be ported to the PowerPC processor.

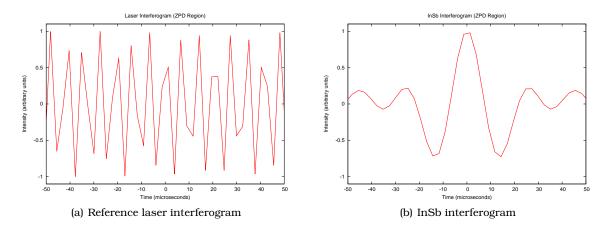

The input data represents simulated time-domain interferograms from the reference laser (*Ge* detector) and the *InSb* detector (see Figure 4.1 on the next page). Note that the reference laser interferogram is just a sine wave modulated in frequency by the scanner velocity fluctuations. An *HgCdTe* interferogram is not included as its processing is very similar to that of the *InSb* interferogram. The input data is stored in two columns of single-precision floating-point numbers in ASCII format and represents the number of photons striking the detector in the sample time. The first column is the reference laser interferogram and the second column is the *InSb* interferogram. The file size is roughly 38 Mbytes.

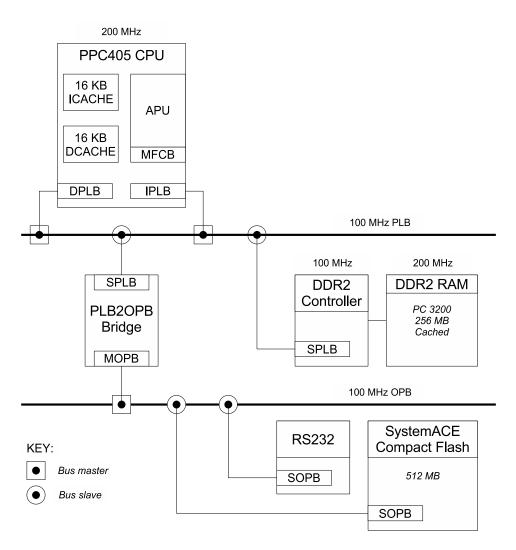

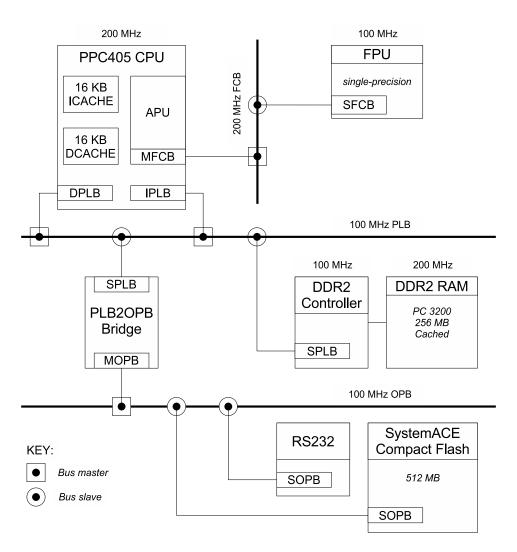

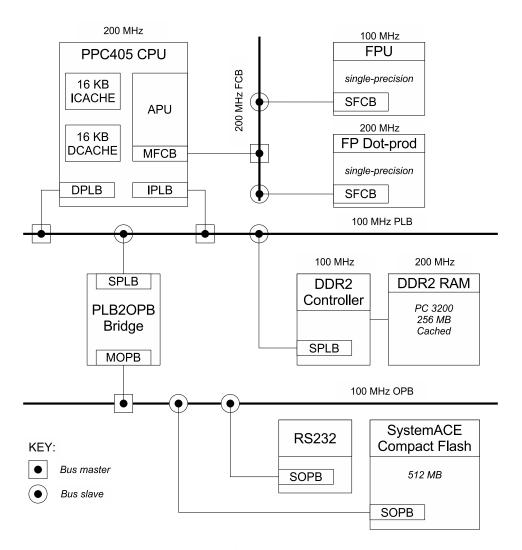

## 4.1 Generating a Hardware Platform

The FTIR base system hardware platform is built from scratch using the Xilinx Platform Studio (XPS) and the Base System Builder (BSB) in the Embedded Development Kit (EDK). A system diagram, showing the main buses and system components, is presented in Figure 4.3 on page 31 while a detailed description follows below.

First, it is necessary to select and configure the processor and its system interfaces. The hard PPC405 processor is selected for FTIR data processing as it delivers much higher performance than the soft MicroBlaze processor. Next it is configured with the following

Figure 4.1: Simulated time-domain interferograms used as input data [2]

| <u>R</u> eference clock          | Processor clock      | Bus clock frequency: |

|----------------------------------|----------------------|----------------------|

| frequency:<br>100.00 MHz         | frequency:           | MHz 100.00 MHz       |

| Reset polarity:                  | ctive LOW 🕑          |                      |

| Processor configuration          | ň                    |                      |

| Debug I/F                        |                      |                      |

| ● FPGA <u>J</u> TAG              |                      |                      |

| CPU debug <u>u</u> se            | r pins only          |                      |

| 🚫 CPU debug and                  | l <u>t</u> race pins |                      |

| 🔿 No debug                       |                      |                      |

|                                  |                      | On-chip memory (OCM) |

| - L                              |                      | (Use BRAM)<br>Data:  |

| Barren                           | The TH               | NONE                 |

| Power                            |                      | Instruction:         |

|                                  |                      | NONE                 |

|                                  |                      |                      |

| - Cache setun                    |                      |                      |

| Cache setup                      |                      |                      |

| ☑ Enable                         | nce enable burst     |                      |

|                                  |                      |                      |

| ☑ Enable<br>For optimal performa | 1 memory             |                      |

Figure 4.2: PPC405 base system configuration

options (see Figure 4.2 on the previous page):

- 100 *MHz* (max) PLB and OPB bus clock frequency for highest possible transfer rates on system buses

- 200 *MHz* processor clock frequency<sup>1</sup>

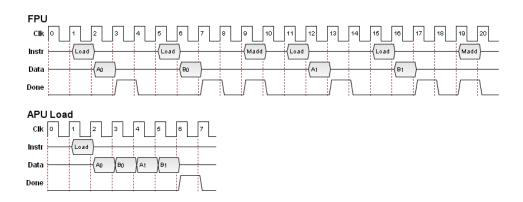

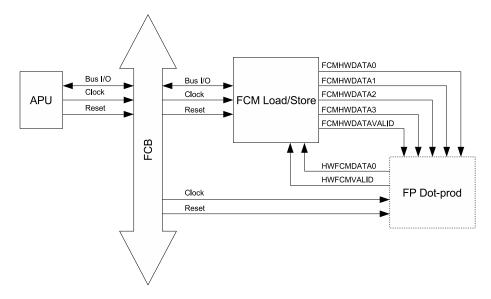

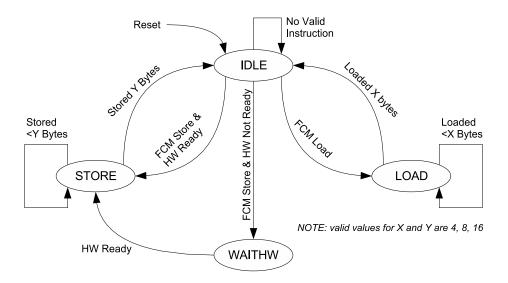

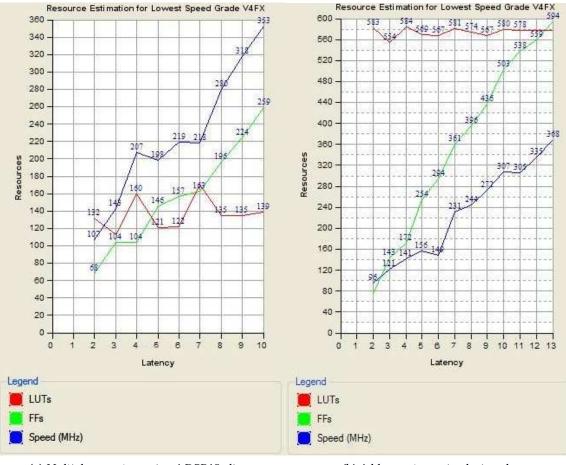

- Cache enabled for maximum performance (instruction and data, burst and/or cacheline)