# Hardware Mechanisms for Distributed Dynamic Software Analysis

by

#### **Joseph Lee Greathouse**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2012

#### **Doctoral Committee:**

Professor Todd M. Austin, Chair Professor Scott Mahlke Associate Professor Robert Dick Associate Professor Jason Nelson Flinn © Joseph Lee Greathouse

All Rights Reserved 2012

To my parents, Gail and Russell Greathouse. Without their support throughout my life, I would never have made it this far.

# Acknowledgments

First and foremost, I must thank my advisor, Professor Todd Austin, for his help and guidance throughout my graduate career. I started graduate school with the broad desire to "research computer architecture," but under Professor Austin's watch, I have been able to hone this into work that interests us both and has real applications. His spot-on advice about choosing topics, performing research, writing papers, and giving talks has been an invaluable introduction to the research world.

The members of my committee, Professors Robert Dick, Jason Flinn, and Scott Mahlke, also deserve special gratitude. Their insights, comments, and suggestions have immeasurably improved this dissertation. Together their expertise spans low-level hardware to systems software and beyond. This meant that I needed to ensure that any of my ideas were defensible from all sides.

I have been fortunate enough to collaborate with numerous co-authors. I have often published with Professor Valeria Bertacco, who, much like Professor Austin, has given me invaluable advice during my time at Michigan. I am extremely lucky to have had the chance to work closely with Ilya Wagner, David Ramos, and Andrea Pellegrini, all of whom have continued to be good friends even after the high-stress publication process. My other Michigan co-authors are Professor Seth Pettie, Gautam Bhatnagar, Chelsea LeBlanc, Yixin Luo, and Hongyi Xin, each of whom has significantly contributed to my graduate career and whose help I greatly appreciate.

I was also fortunate to have spent five months doing research at Intel. This opportunity broadened my research into concurrency bugs and helped break me out of my post-quals slump. Matt Frank, Zhiqiang Ma, and Ramesh Peri were co-authors on the paper that resulted from this work, and I heartily thank them for all of their help. I also wish to thank the entire Inspector XE team, whose product was amazing to work with. Matt Braun, especially, was always available to help keep my project moving forward.

Matt Frank also aided me immensely when I was an undergraduate at the University of Illinois. He and Professors Sanjay Patel and Donna Brown were instrumental in convincing me to go to graduate school in the first place. I am certain that their recommendation letters

were the main reason I was admitted into Michigan. I am also thankful to Nick Carter, who was a faculty member at UIUC at the time, for allowing me to do research with his group during my senior year. I failed completely at the tasks he assigned me, but it was an incomparable learning experience.

I doubt I would have been able to complete this dissertation without the support of the other graduate students in my lab. I'm extremely lucky to have had such amazing people in close proximity, which has really proven to me the power of a good group of motivated people. Thanks to all of you for being great: Bill Arthur, Adam Bauserman, Kai-hui Chang, Debapriya Chatterjee, Jason Clemons, Kypros Constantinides, Shamik Ganguly, Jeff Hao, Andrew Jones, Rawan Khalek, Shashank Mahajan, Biruk Mammo, Jinsub Moon, Andreas Moustakas, Ritesh Parikh, Robert Perricone, Steve Plaza, Shobana Sudhakar, and Dan Zhang.

There are also loads of people in the department that have been an inspiration. Michigan's CSE program is strong because of people like you: Professor Tom Wenisch, Timur Alperovich, Bashar Al-Rawi, Héctor Garcia, Anthony Gutierrez, Jin Hu, Anoushe Jamshidi, Daya Khudia, Dave Meisner, Jarrod Roy, Korey Sewell, and Ken Zick. I think it's also important to acknowledge everyone who has volunteered to help out with the ACAL reading group.

Andrew DeOrio deserves special thanks for putting up with me as a labmate for five years and as a roommate for three. We started at nearly the same time and are finishing at nearly the same time, even if our day-to-day schedules almost never overlap.

My friends in Illinois were also a big help in making it through this process. Paul Mathewson, especially, kept me focused on things besides engineering (and let me crash on his couch during my internship). Dan Bassett and Dan Baker both kept me grounded in reality in their own ways.

Finally, my family is the biggest reason that I've been able to do this work. Without their constant support throughout childhood, college, and graduate school, I would've stopped a hundred times along the way. My parents and grandparents have always encouraged me in any decision I've made. I couldn't ask for anything more.

# **Table of Contents**

| Dedicat   | ion .         |                                           | i   |

|-----------|---------------|-------------------------------------------|-----|

| Acknov    | vledgme       | ents                                      | ii  |

| List of   | <b>Fables</b> |                                           | /ii |

| List of l | Figures       |                                           | ix  |

| Abstrac   | et            |                                           | X   |

| Chapte    |               | troduction                                |     |

| 1.1       | Comp          | lexity Causes Software Errors             | 2   |

| 1.2       |               | vare Plays a Role in the Problem          |     |

| 1.3       | Attem         | pts to Alleviate the Problem              | 7   |

| 1.4       | Analy         | sis Yields Better Software                | 8   |

|           | 1.4.1         | Static Software Analysis                  | 8   |

|           | 1.4.2         | Dynamic Software Analysis                 | 9   |

| 1.5       | Contri        | butions of this Work                      | 12  |

| Chapte    | r 2 Di        | stributed Dynamic Dataflow Analysis       | 15  |

| 2.1       | Introd        | uction to Sampling                        | 16  |

|           | 2.1.1         | Sampling for Performance Analysis         | 17  |

|           | 2.1.2         | Sampling for Assertion Checking           | 17  |

|           | 2.1.3         |                                           | 18  |

|           | 2.1.4         | Sampling for Dynamic Dataflow Analyses    | 18  |

| 2.2       | Backg         |                                           | 20  |

|           | 2.2.1         | Dynamic Dataflow Analysis                 | 20  |

|           | 2.2.2         |                                           | 23  |

|           | 2.2.3         |                                           | 23  |

| 2.3       | Effecti       | ively Sampling Dataflow Analyses          |     |

|           | 2.3.1         |                                           | 28  |

|           | 2.3.2         | Overhead Control                          |     |

|           | 2.3.3         | Variable Probability of Stopping Analysis |     |

| 2.4       | Protot        | ype System Implementation                 |     |

|         | 2.4.1  | Enabling Efficient User Interaction               | 36 |

|---------|--------|---------------------------------------------------|----|

| 2.5     | Experi | imental Evaluation                                | 37 |

|         | 2.5.1  | Benchmarks and Real-World Vulnerabilities         | 38 |

|         | 2.5.2  | Controlling Dataflow Analysis Overheads           | 40 |

|         | 2.5.3  | Accuracy of Sampling Taint Analysis               | 43 |

|         | 2.5.4  | Exploring Fine-Grained Performance Controls       | 46 |

| 2.6     | Chapte | er Conclusion                                     | 49 |

| Chanter | · 3 Te | studo: Hardware-Based Dataflow Sampling           | 50 |

| 3.1     |        | ations of Software Sampling                       |    |

| 3.2     |        | vare-Based Dynamic Dataflow Analysis              |    |

| 3.2     | 3.2.1  | Limitations of Hardware DDA                       | 55 |

|         | 3.2.2  | Contributions of this Chapter                     | 56 |

| 3.3     |        | vare for Dataflow Sampling                        | 57 |

| 3.3     | 3.3.1  | Baseline Support for Dataflow Analysis            | 58 |

|         | 3.3.1  | Limiting Overheads with a Sample Cache            | 59 |

|         | 3.3.3  | Intra-flow Selection Policy                       | 61 |

|         | 3.3.4  |                                                   | 61 |

|         | 3.3.5  | Inter-flow Selection Policy                       | 62 |

| 2.4     |        | Testudo Sampling Example                          |    |

| 3.4     |        | nalytical Model of Dataflow Coverage              | 63 |

|         | 3.4.1  | Analytical Model Overview                         | 63 |

|         | 3.4.2  | Analytical Model Derivation                       | 64 |

| 2.5     | 3.4.3  | On the Relation to the Coupon Collector's Problem | 65 |

| 3.5     | _      | imental Evaluation                                | 66 |

|         | 3.5.1  | System Simulation Framework                       | 66 |

|         | 3.5.2  | Taint Analysis Coverage and Performance           | 68 |

|         | 3.5.3  | Worst Case Analytical Bounds                      | 70 |

|         | 3.5.4  | Beyond Taint Analysis                             | 71 |

|         | 3.5.5  | Sample Cache Hardware Overheads                   | 71 |

| 3.6     | Chapte | er Conclusion                                     | 73 |

| Chapter | 4 De   | emand-Driven Data Race Detection                  | 75 |

| 4.1     | Introd | uction                                            | 76 |

|         | 4.1.1  | Contributions of this Chapter                     | 77 |

| 4.2     | Data F | Race Detection Background                         | 79 |

| 4.3     | Demai  | nd-Driven Data Race Detection                     | 80 |

|         | 4.3.1  | Unsynchronized Sharing Causes Races               | 81 |

|         | 4.3.2  | Performing Race Detection When Sharing Data       | 82 |

| 4.4     | Monit  | oring Data Sharing in Hardware                    | 84 |

|         | 4.4.1  | Cache Events                                      | 85 |

|         | 4.4.2  | Performance Counters                              | 87 |

| 4.5     | Demai  | nd-Driven Race Detector Design                    | 88 |

| 4.6     |        | imental Evaluation                                | 90 |

|         | 4.6.1  | Experimental Setup                                | 90 |

|         | 462    | Performance Improvement                           | 92 |

|            | 4.6.3       | Accuracy of Demand-Driven Data Race Detection        | 9    | 95  |

|------------|-------------|------------------------------------------------------|------|-----|

|            | 4.6.4       | Races Missed by the Demand-Driven Data Race Detector | 9    | 96  |

|            | 4.6.5       | Observing more W→W Data Sharing                      | 9    | )7  |

|            | 4.6.6       | Negating the Limited Cache Size                      |      | 7   |

| 4.7        | Relate      | ed Work                                              | 9    | 8   |

|            | 4.7.1       | Data Race Detection                                  |      | 8   |

|            | 4.7.2       | Software Acceleration Methods                        | 9    | 9   |

|            | 4.7.3       | Hardware Race Detection                              | 10   | 0   |

|            | 4.7.4       | Observing Hardware Events                            | . 10 | 0   |

| 4.8        | Chapte      | er Conclusion                                        |      |     |

| CI 4       | <b>7</b> 11 |                                                      | 1.0  |     |

| Chapter    |             | ardware Support for Unlimited Watchpoints            |      |     |

| 5.1        |             | uction                                               |      |     |

| <i>7</i> 0 | 5.1.1       |                                                      |      |     |

| 5.2        |             | Unlimited Watchpoints                                |      |     |

|            | 5.2.1       | Existing HW Watchpoint Support                       |      |     |

|            | 5.2.2       | Unlimited Watchpoint Requirements                    |      |     |

|            | 5.2.3       | Efficient Watchpoint Hardware                        |      |     |

| 5.3        |             | point Applications                                   |      |     |

|            | 5.3.1       | Dynamic Dataflow Analysis                            |      |     |

|            | 5.3.2       | Deterministic Concurrent Execution                   |      |     |

|            | 5.3.3       | Data Race Detection                                  |      |     |

| 5.4        | -           | imental Evaluation                                   |      |     |

|            | 5.4.1       | Experimental Setup                                   | 12   | 21  |

|            | 5.4.2       | Results for Taint Analysis                           | 12   | 24  |

|            | 5.4.3       | Results for Deterministic Execution                  | 12   | 26  |

|            | 5.4.4       | Results for Data Race Detection                      | . 12 | 27  |

|            | 5.4.5       | Experimental Takeaways                               | . 12 | 28  |

| 5.5        | Relate      | ed Work                                              | 12   | 29  |

|            | 5.5.1       | Memory Protection Systems                            | 12   | 29  |

|            | 5.5.2       | Other Uses for Watchpoints                           | 13   | 31  |

| 5.6        | Chapte      | er Conclusion                                        | 13   | 2   |

| Chapter    | . 6 C       | onclusion                                            | 12   | 21  |

| 6.1        |             | S Summary                                            |      |     |

| 6.2        |             | Research Directions                                  |      |     |

|            |             |                                                      |      |     |

| 6.3        | Conch       | usion                                                | . 13 | ) / |

| Bibliogr   | aphy        |                                                      | 13   | 8   |

# **List of Tables**

| <b>Table</b>             |                                                      |

|--------------------------|------------------------------------------------------|

| 2.1<br>2.2<br>2.3        | Overheads from a Selection of Dynamic Analyses       |

| 3.1                      | Benchmarks for Testudo                               |

| 4.1<br>4.2<br>4.3        | The Concurrency Bugs from RADBench Used in this Work |

| 5.1<br>5.2<br>5.3<br>5.4 | Hardware Watchpoint Support in Modern ISAs           |

| 5.5                      | Pipelined Events for Hardware Watchpoint Evaluation  |

# **List of Figures**

|   | •  |     |    |

|---|----|-----|----|

| н | 10 | ווו | re |

| • |    | u   |    |

| 1.1  | Lines of Source Code in Windows and Linux Increasing Over Time         | 2  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Number of Windows Developers Increasing Over Time                      | 3  |

| 1.3  | Number of Security Vulnerabilities Increasing Over Time                | 3  |

| 1.4  | A Data Race Causing a Software Bug                                     | 5  |

| 1.5  | Concurrency Bugs Causing Security Errors                               | 6  |

| 1.6  | Dynamic Analyses May Not Always Catch Bugs                             | 11 |

| 2.1  | Sampling for Assertion Analyses                                        | 17 |

| 2.2  | Example Dataflow Analysis                                              | 21 |

| 2.3  | Traditional Demand-Driven Analysis                                     | 22 |

| 2.4  | Code-Based Sampling Fails for Dataflow Analysis                        | 24 |

| 2.5  | Uncoordinated Distributed Dataflow Analysis                            | 26 |

| 2.6  | Dynamic Dataflow Sampling                                              | 26 |

| 2.7  | Dataflow Sampling May Also Miss Errors                                 | 27 |

| 2.8  | Dataflow Sampling Prevents False Positives                             | 28 |

| 2.9  | Variable Probability of Stopping Analysis                              | 32 |

| 2.10 | Prototype Dataflow Sampling System                                     | 35 |

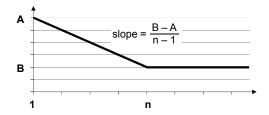

|      | Worst-Case Synthetic Benchmark                                         | 38 |

|      | Synthetic Accuracy Benchmarks                                          | 38 |

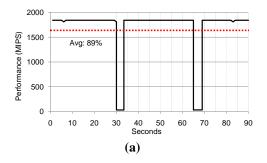

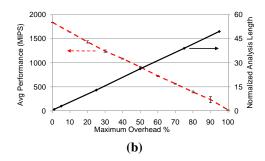

|      | Synthetic Benchmarks: Performance and Analysis Accuracy                | 41 |

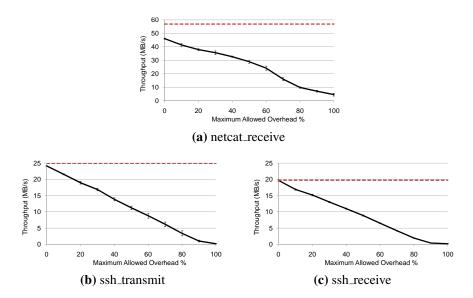

| 2.14 | Dataflow Sampling Increases Network Throughput                         | 42 |

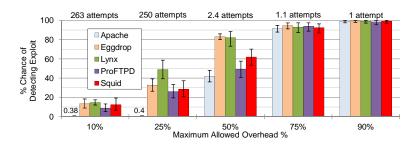

| 2.15 | Exploit Observation with Netcat Background Execution                   | 44 |

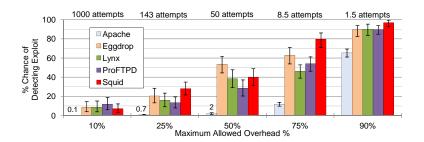

|      | Exploit Observation with SSH Background Execution                      | 45 |

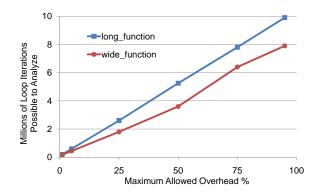

|      | Maximum Analysis Possible Before the First Sampling Event              | 46 |

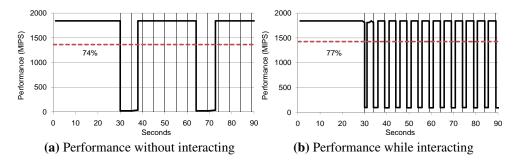

|      | Changing the Interactive Performance                                   | 47 |

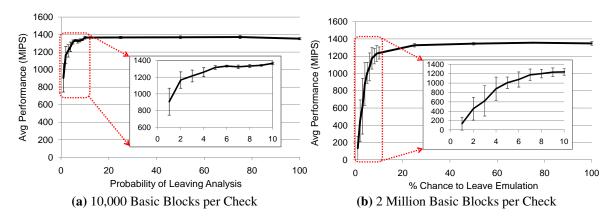

| 2.19 | Changing the Probability of Removing Dataflows Affects Overhead        | 48 |

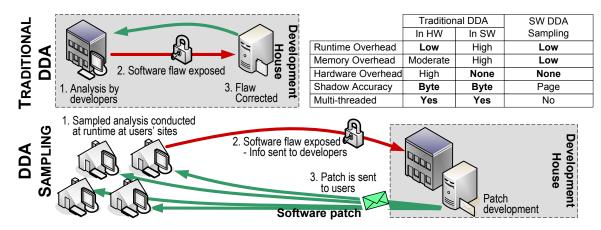

| 3.1  | Comparison of Dynamic Dataflow Analysis Methods                        | 55 |

| 3.2  | The Life of a Tainted Variable                                         |    |

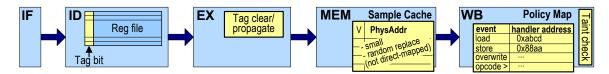

| 3.3  | Testudo Hardware Implementation                                        |    |

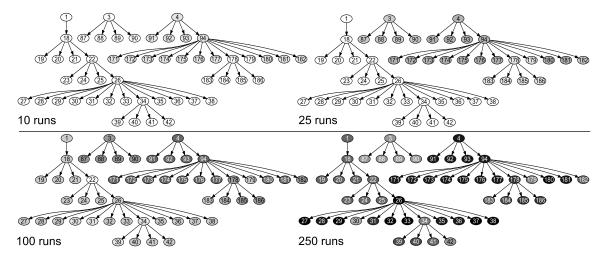

| 3.4  | Testudo's Dataflow Sampling Coverage on Three Dataflows                | 62 |

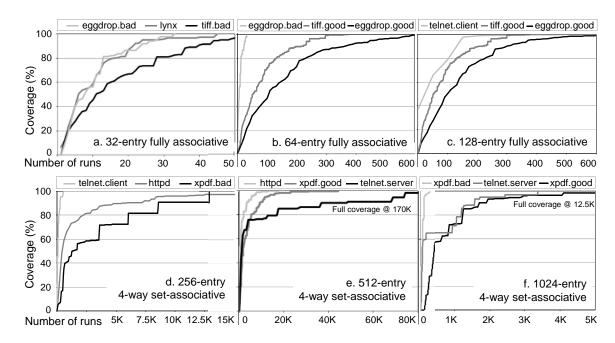

| 3.5  | Dataflow Coverage vs. Execution Count for Various Sample Cache Sizes . | 69 |

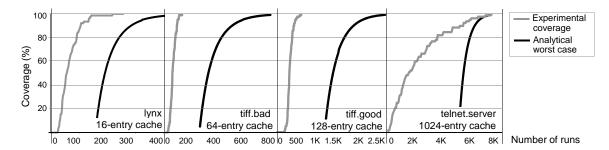

| 3.6  | Experimental Dataflow Coverage and Analytical Upper Bound                 | 70 |

|------|---------------------------------------------------------------------------|----|

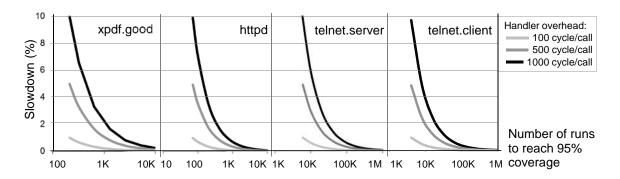

| 3.7  | Performance Overhead for Software-Handled Analyses                        | 72 |

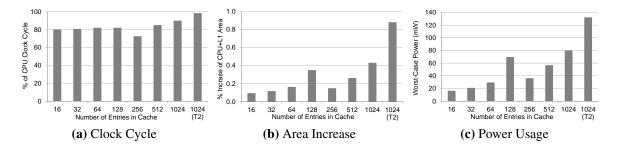

| 3.8  | Delay, Area, and Power Overheads of the Sample Cache                      | 73 |

| 4.1  | A Data Race Resulting in a Security Flaw                                  | 79 |

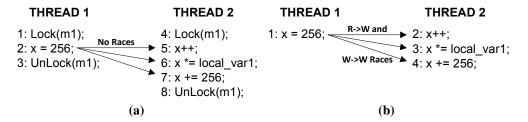

| 4.2  | Multiple Data Race Checks Yielding the Same Answers                       | 81 |

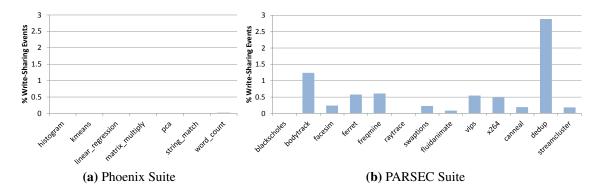

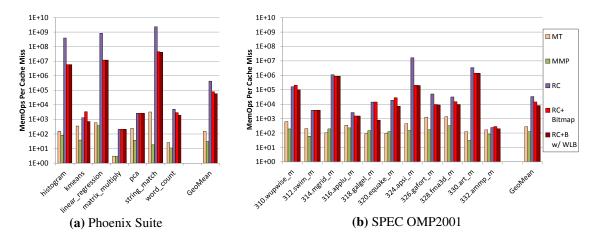

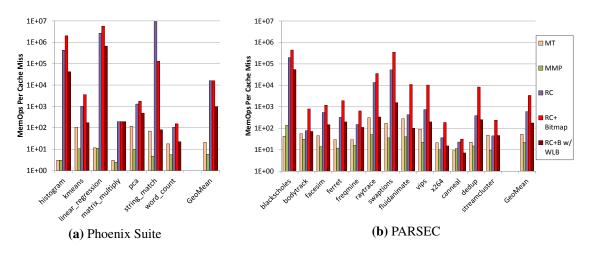

| 4.3  | Dynamic Write-Sharing Events in Two Parallel Benchmark Suites             | 82 |

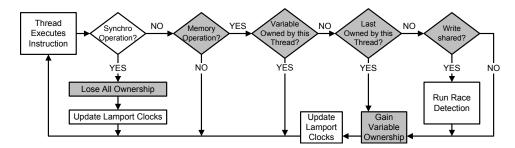

| 4.4  | Ideal Hardware-Assisted Demand-Driven Software Data Race Detector         | 83 |

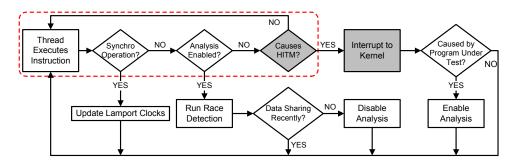

| 4.5  | HITM-Based Demand-Driven Data Race Detector                               | 89 |

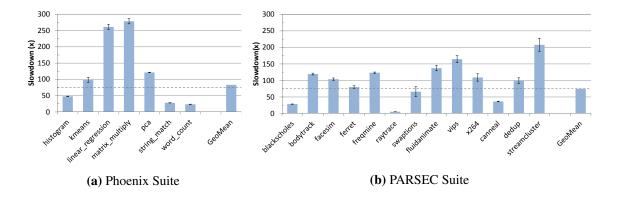

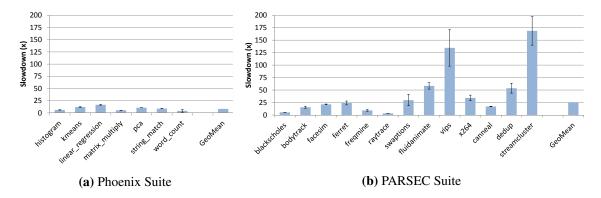

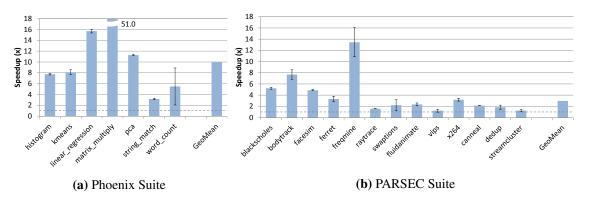

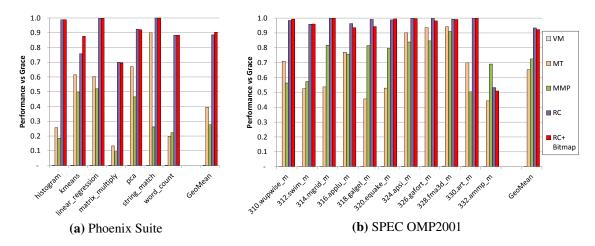

| 4.6  | Continuous-Analysis Data Race Detection Slowdowns                         | 93 |

| 4.7  | Total Overhead of the Demand-Driven Data Race Detector                    | 94 |

| 4.8  | Speedups of Demand-Driven over Continuous-Analysis Data Race Detection    | 94 |

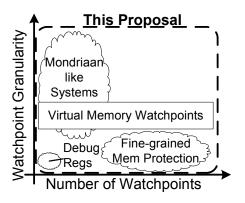

| 5.1  | Qualitative Comparison of Existing Watchpoint Systems                     |    |

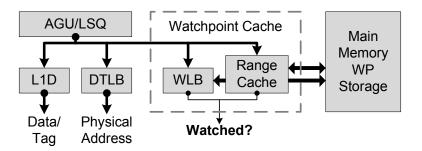

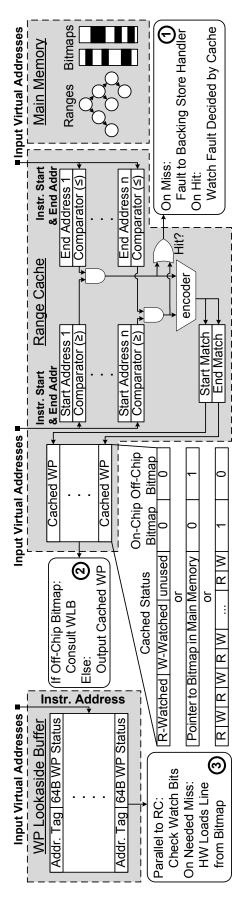

| 5.2  | Watchpoint Unit in the Pipeline                                           | 10 |

| 5.3  | Unlimited Watchpoint Architecture                                         | 12 |

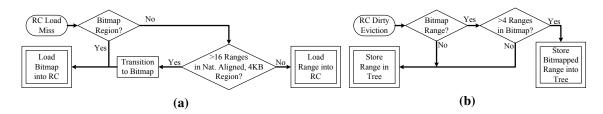

| 5.4  | Different Watchpoint Storage Methods                                      | 14 |

| 5.5  | Software Algorithm for Bitmapped Ranges                                   | 14 |

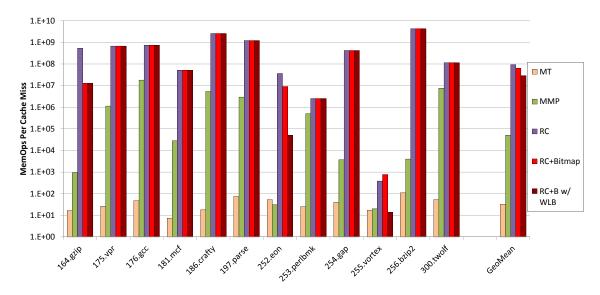

| 5.6  | Memory Operations per Watchpoint Cache Miss for Taint Analysis 1          | 24 |

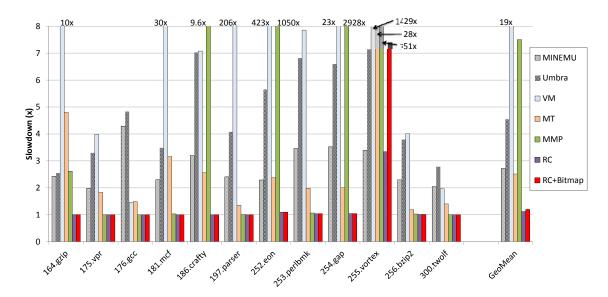

| 5.7  | Performance of Demand-Driven Taint Analysis                               | 25 |

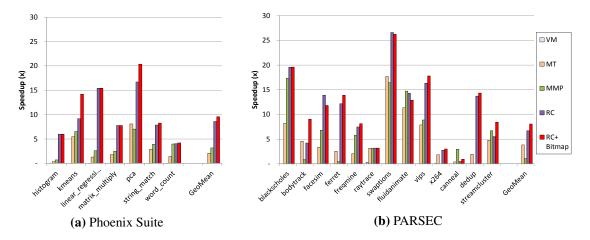

| 5.8  | Memory Operations per Watchpoint Cache Miss for Deterministic Execution 1 | 26 |

| 5.9  | Deterministic Execution Performance: Cache Line vs. Page Granularity      |    |

|      | Watchpoints                                                               | 27 |

| 5.10 | Memory Operations per Watchpoint Cache Miss for Data Race Detection . 1   | 27 |

| 5.11 | Performance of Demand-Driven Data Race Detection vs. Binary Instrumen-    |    |

|      | tation                                                                    | 28 |

### **Abstract**

The complexity of modern software makes it difficult to ship correct programs. Errors can cost money and lives, so developers often use automated software analysis tools to hunt for bugs. By automatically analyzing a program's runtime operation, dynamic analysis tools can find subtle errors that would normally escape the notice of even careful human testers.

These dynamic analyses are more likely to find errors if they observe the program under numerous and varied runtime situations, so, ideally, users would analyze programs as they run them. Regrettably, these tests cause orders-of-magnitude slowdowns, which few users would tolerate.

This dissertation presents methods of accelerating dynamic software analyses in order to distribute these trials to users. It begins by observing that the overhead that any individual observes can be lowered by allowing each user to analyze a small, random sample of the program's operations. It then describes a sampling mechanism for dynamic dataflow analyses that only requires access to the virtual memory system.

Other dynamic software analyses cannot use this technique, so the remainder of this dissertation focuses on novel hardware-based acceleration mechanisms. The first, Testudo, allows faster and more accurate dataflow analysis sampling by storing meta-data in an on-chip cache and stochastically removing these values whenever it overflows.

Next, a method for performing demand-driven data race detection using existing hardware performance counters is detailed. These counters make inter-cache sharing events visible to software, allowing the data race detector to be enabled only when needed.

Finally, fine-grained memory monitoring is a crucial for every analysis studied in this work. This dissertation closes by examining a hardware mechanism for allowing unlimited fine-grained watchpoints, which can be used to reduce the overheads of many analyses.

In total, this dissertation demonstrates that hardware designers can play a role in mitigating software bugs, as many of the acceleration mechanisms explored in this work require hardware support in one form or another. Taken together, these works represent a step forward for accelerating dynamic software analyses and distributing them to end-users.

# Chapter 1

### Introduction

It was on one of my journeys between the EDSAC room and the punching equipment that "hestitating at the angles of stairs" the realization came over me with full force that a good part of the remainder of my life was going to be spent in finding errors in my own programs.

Memoirs of a Computer Pioneer

Maurice V. Wilkes

High-quality software is difficult to create. Complex applications not only require optimized algorithms underlying their logical structure, but they must also be implemented efficiently and correctly. As programs increase in complexity, this correctness and efficiency are more difficult to attain, leading to bug-ridden software that, even when working, is disagreeably slow.

Billions of dollars and millions of man-hours are spent each year attempting to build, modify, and maintain innumerable programs. Though the field of software engineering exists to formalize methods of creating high-quality software [1], our ability to accurately build such complex artifacts lags behind our appetite for new features and speedier results. On the whole, this leads to modern applications that are riddled with errors that often frustrate their users and developers. As Bessey *et al.* state, "Assuming you have a reasonable [software analysis] tool, if you run it over a large, previously unchecked system, you will always find bugs" [23].

Such bugs can lead to significant hardships for both users and designers. The National Institute of Standards and Technology estimated that, nearly a decade ago, software errors cost the United States economy up to \$59.5 billion per year [212]. These errors can also result in security-related problems, such as the thousands of exploitable vulnerabilities publicly disclosed yearly by the National Vulnerability Database [152] or sold to criminals and government agencies through gray and black markets [82, 140]. Vulnerabilities like these contributed to an estimated \$67 billion lost by American companies in 2005 due to

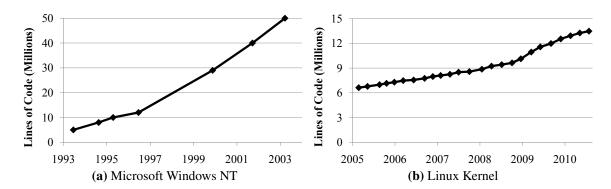

**Figure 1.1** Lines of Source Code in Windows and Linux Increasing Over Time. As software becomes more mature, it has a tendency to increase in size and complexity. New features are added and old features remain for backwards compatibility. (a) shows the number of lines of source code in the Microsoft Windows NT operating system from 3.1 up to Server 2003. (b) lists the number of source code lines in the Linux kernel from version 2.6.11 to 2.6.35.

computer crime [222]. It has also been speculated that they are used for espionage and cyberwarfare attacks [193].

### 1.1 Complexity Causes Software Errors

One factor leading to such errors is the tendency for software to become more complex over time. Figure 1.1 illustrates the increase in lines of code within two popular pieces of software. Figure 1.1a shows the number of source code lines in the Microsoft Windows NT operating system from its initial public release in 1993 to Windows Server 2003 [130, p. XXI]. Over the course of this decade, the operating system (including both kernel and user-level code) increased in size by  $10\times$ , from 5 million to 50 million lines of code. Figure 1.1b graphs the same data for the Linux kernel from version 2.6.11, released in March, 2005, to version 2.6.35, release in August, 2010 [48]. This five year period saw the code base double from 6.6 million lines of code to 13.4 million.

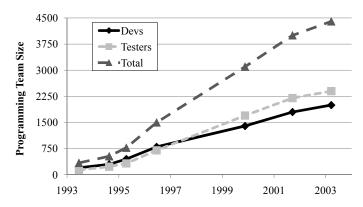

While lines of code is not a quantitative metric of complexity, Maraia also listed a second indication of the increased complexity of the Windows operating system: the number of developers working on the product, as shown in Figure 1.2, increased at an even faster rate than the code [130, p. XXI]. Over the course of that decade, the programming team increased from 340 to 4400 people, a 13× jump. As Brooks points out (as have many others), the time spent developing software grows faster than linearly as team size increases, because many more interactions must take place between developers [73]. In short, the complexity of a system such as Microsoft Windows increased rapidly over time.

Figure 1.2 Number of Windows Developers Increasing Over Time. Not only did the Microsoft Windows code size increase by  $10 \times$  between NT 3.1 and Server 2003, the total development team increased by almost  $13 \times$ . This supports the assertion that the software has become more complicated over time.

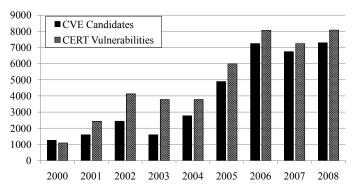

**Figure 1.3** Number of Security Vulnerabilities Increasing Over Time. These numbers come from two general security vulnerability databases, the Mitre Corporation's CVE list and the CERT vulnerability database. As software has proliferated, its complexity has resulted in more total vulnerabilities reported each year, growing  $7-8\times$  in eight years.

This data, of course, only shows that individual programs or software releases get larger over time. Upon its completion in 1957, barely a decade after the invention of the modern digital computer, the SAGE project already had more than 100,000 instructions and five hundred programmers [102, pp. 105–108]; IBM's System/360 used over 5 million lines of code by 1968 (similar to the amount seen 25 years later in Windows NT 3.1) [179, p. 66]. Nonetheless, we can see the negative effects of increasing complexity on the software corpus by studying bug reports. Figure 1.3 shows the number of security vulnerabilities reported to Mitre Corporation's Common Vulnerability and Exposures (CVE) list [49] and the number of general software vulnerabilities cataloged by CERT [99] from the years 2000 to 2008 (the last year with currently available statistics). Over this eight year period, the number of security vulnerabilities publicly reported each year increased by 8×, another indication of complexity that corroborates the assertion that complex high-quality software is difficult to create.

A simple example of the type of bug that can lead to such security flaws is the buffer overflow. This common problem can result from an unexpected input forcing a function to modify memory far beyond the end of an array. Such inputs can be used to insert and execute malicious code into an unsuspecting program [4]. This can occur in large applications when functions written by different programmers expect contrary things of a shared buffer. An example of this can be seen in a 2005 security flaw in the Lynx newsgroup reader [155]. This exploit attacks a function, HTrjis(), that adds escaped characters to an existing string while moving it between two buffers. HTrjis() assumed that the destination buffer was large enough to contain strings with multiple new characters, while the function that calls HTrjis() instead assumed that both buffers could be the same size. Such implicit assumptions are difficult to curtail in large software projects can cause obscure errors.

While the use of safer languages such as Java and C# have reduced the occurrences of some types of errors in user-level code, flaws in the highly complex runtime environments of such languages are still a source of dangerous errors. Adobe Flash is a widely deployed platform for running ActionScript programs, yet bugs in the underlying scripting engine are frequently exploited to allow these programs to attack the host computer [71]. Additionally, complex applications can still suffer from numerous non-security bugs, despite running in more constrained environments.

### 1.2 Hardware Plays a Role in the Problem

The increasing complexity of the underlying hardware is another cause of software bugs. Hardware architects often add intricate features to increase the maximum performance of their product. The inattentive programmer may find that these features hurt performance if used haphazardly, as complicated out-of-order execution engines, branch predictors, prefetch units, and similar features require a great deal of effort to effectively utilize. Beyond first-order estimations, it is often difficult to conceptualize the performance that will result from a particular implementation of an application. Many software developers instead rely on profiling to observe the true efficiency of a piece of software, since keeping track of every possible hardware feature is a mind-bending proposition.

To this end, they often use mechanisms such as hardware performance counters when optimizing their code [208]. These devices count hardware events that can reduce software performance, such as branch mispredictions and prefetch misses, and can be used to pinpoint sections of code that are not operating efficiently on the underlying hardware. Over the last 15 years, Intel has quadrupled the number of countable events in their commercial x86 line

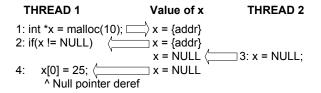

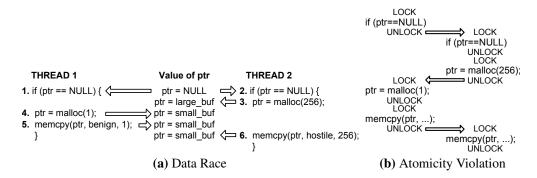

**Figure 1.4** A Data Race Causing a Software Bug. This concurrency bug example demonstrates how a data race can cause a non-intuitive program error. The code in thread 1 should be safe, but because another thread can change the shared pointer between the check and dereference, thread 1 might crash.

of processors, indicating that it is becoming more difficult to optimize code for the myriad of new and complex hardware features [58].

Besides making performance optimizations more difficult, complicated hardware features can also lead to correctness and security problems. A hardware feature that undoubtedly falls in this class is shared-memory parallel processing. Originally proposed in the 1990s [86, 176, 224], single-chip multiprocessors were studied further in the early part of the following decade [16, 85, 213]. Consumer-level CPUs have since advanced from mostly single-core devices to chips with two or more cores, starting with the releases such as AMD's Athlon 64 X2 [143], IBM's PowerPC 970MP [98], Intel's Pentium D [90], and Sun's UltraSPARC T1 [113] in 2005. In the years since, commodity processors have increased their core counts up to 12 [5], server chips up to 16 [201], and some embedded chips up to 100 [3]. Besides these homogeneous multicore systems, there is also a push for heterogeneous multiprocessors, or multicore chips where each core can have a different ISA or microarchitecture [114].

Because developers need to worry about problems such as data races, deadlocks, atomicity violations, memory consistency errors, and non-deterministic execution in parallel code, it is much more difficult to program the concurrent software needed by these systems than serial programs that perform the same task [135]. Such difficulties have been noted numerous times over the years; from the Cray X-MP supercomputer [150] to the Sega Saturn video game console [171], scores of developers have found programming parallel processors difficult. Heterogeneous systems, such as IBM's Cell processor, are similarly notorious for their difficulty to program [192]. Despite these issues, architects now rely primarily on increasingly parallel processors to deliver further performance gains, as those from Dennard scaling have dropped off in the last decade due to power density concerns [175, pp. 1–5].

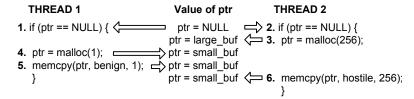

Taken in total, multiprocessors have entered the mainstream, bringing parallel programming and its associated concurrency bugs with them. Figure 1.4 shows a simple example of a concurrency bug that causes a program to crash because of a null pointer exception. When these two threads access a shared pointer without appropriate locking, the interleaving

**Figure 1.5** Concurrency Bugs Causing Security Errors. These examples show that concurrency bugs can cause more than just program crashes. In (a), both threads attempt to initialize a shared pointer. Due to the lack of synchronization, thread 1 allocates a small buffer, and thread 2 copies a large amount of data into it. The version of the code in (b), has locks around every access to the shared pointer. There is no data race, but it is still possible to order the threads incorrectly. In both cases, the incorrect parallel execution can cause buffer overflows.

of the accesses may cause the first thread to crash when dereferencing a pointer, even if it appropriately checked that the pointer was not NULL immediately beforehand.

Figure 1.5 shows an example concurrency bug modeled after CVE-2010-3864, a security flaw found in recent versions of the OpenSSL TLS library, which also allowed two threads to access a shared pointer without synchronization [160]. In some circumstances, each thread may attempt to initialize the pointer to a different heap object and subsequently attempt to copy data into the object. If, however, the accesses to the pointer are interleaved (as shown in Figure 1.5a), one thread may attempt to copy a large amount of data into a small heap object, causing a potentially dangerous heap overflow [180]. Similarly, Figure 1.5b demonstrates how atomicity violations, much like data races, could result in similar software problems. Even though the accesses to the shared pointer have locks surrounding them, meaning that there are technically no data races, the threads can still be ordered in such a way that the buffer overflow exists

Other decisions by hardware manufacturers have led to different kinds of software errors. Though there were pushes in the 1970s and 1980s for capability-based architectures, systems that would only allow areas of memory to be accessed by code with appropriate permissions, most of these architectures had limited market penetration [122]. As such, most current architectures leave poorly written software vulnerable to memory errors. Similarly, though most security attacks can still be carried out on Harvard architecture systems [72], the prevalence of von Neumann architectures makes these attacks simpler.

#### 1.3 Attempts to Alleviate the Problem

Unfortunately, while current processors provide facilities such as performance counters and branch recorders to allow engineers to tune software performance [121], few analogous features exist to help correctness. What features *do* exist are primarily focused on a small class of security issues. The UltraSPARC T2, for instance, includes hardware support for RSA, DSA, RC4, 3DES, and AES encryptions algorithms [75]. Intel's processors now also contain hardware support for AES [187]. These features are primarily used to increase performance, but also offer some protection against side-channel attacks.

There are proposals from the industry for mechanisms like transactional memory [88], in an attempt to make parallel programming easier. However, efforts from processor manufacturers to help software developers find other problems, such as buffer overflows, are limited primarily to the research community. Nonetheless, whether hardware developers help or not, though, those in the software realm must attempt to solve these problems if they are to release working programs. To that end, software engineers have built a number of systems to help themselves.

One of the first techniques that the software development community took to heart when attempting to more accurately build their programs was the concept of software engineering [94]. In essence, this means that the programmers should follow structured design principles, based on well-researched theoretical concepts, rather than building their products solely from experiences learned through trial-and-error. Professional societies such as the ACM and IEEE have pushed such methods into educational curricula in an attempt to train stronger developers [1]. Other efforts, such as coding standards, list rules that programmers should follow in order to avoid common mistakes [198]. While such efforts are laudable and helpful, they do not completely solve the problem, as outlined earlier.

Another direction the software community has taken to reduce errors in their code is the introduction of newer, more powerful programming languages. This can be seen with the original introduction of high-level languages, which allowed developers to more succinctly describe their algorithms and hid the complexities of the underlying hardware compared to machine code [111]. Managed languages such as Java remove many of the memory problems found in programs written in languages like C or C++, while scripting languages such as JavaScript and Python hide even more low-level complexity from designers.

For a number of reasons, this dissertation will not focus on this method of reducing software errors. First, though newer languages can make it more difficult to cause certain types of errors, they often open up new styles of bugs. Errors in modern web scripts, for instance, frequently result in SQL injection attacks, even if they don't suffer from buffer

overflow attacks. As Zeev Suraski stated when discussing security features in PHP, the scripting language he helps develop, "[s]ecurity bugs are out there, in fact in web apps they're pretty much a plague (irregardless of the language)" [211]. Beyond the ability of careless programmers to create bugs in any language, it is also the case both that legacy software continues to exist and increase in size (as discussed earlier) and that new software is still created in older languages [110].

Instead, this work will look at another mechanism that developers use to improve their code: software analysis tools. That is, programs that look at other pieces of software and help developers find errors, mistakes, and misconfigurations after they already exist, but hopefully before they can cause problems.

### 1.4 Analysis Yields Better Software

Software analysis tools are programs designed to inspect other pieces of software in order to find errors. These can be as simple as searches for insecure functions, such as calls to memcpy(), or may be as complex as attempting to walk the program through every reachable path in its control structure. In general, software analyses tools focus on finding particular classes of errors and require a number of tradeoffs to meet these goals. Perhaps the most common way of classifying an analysis tool is by whether it tests the software without running it, or whether it does so alongside the execution of the program. The former are called *static analyses*, while the latter, which are the focus of most of this dissertation, are referred to as *dynamic analyses*.

#### 1.4.1 Static Software Analysis

Static analysis tools automatically reason about a program's correctness by testing the source code for certain formal properties. One of the most famous tools in this area is *lint*, a tool that searches C code for constructs that, while not technically illegal under the language specification, are likely to cause runtime errors [107]. Such tools are more powerful than simple string searches, but may have problems finding complex errors that involve logical mistakes or correct code used in incorrect ways. Some researchers have therefore looked at formal analysis methods, where a tool tries to perform rigorous mathematical deductions to see if the software under test can reach an erroneous output [63].

Static analysis tools have been used to find numerous bugs [23], but may not work under all circumstances. Formal methods can have problems analyzing large programs due

to the computational complexity of the underlying algorithms. The CompCert project to formally verify a compiler chain that goes from a subset of C (excluding, for instance, goto statements) to PowerPC assembly code took multiple person-years of effort. In addition, it produced enough unique ideas that simply completing it yielded a string of publications in venues as prestigious as the Communications of the ACM [120]. Performing such an effort on complicated programs with less formal grounding than compilers may prove very difficult indeed.

Static analyses may also have problems with false positives, as the developers of the Clang static analyzer point out [8]. Because the tests may make assumptions about how the program will be used at runtime, they may falsely flag errors that could never occur on a real system. This lack of dynamic information can also lead to false negatives.

#### **1.4.2** Dynamic Software Analysis

Some errors can only be found by using knowledge about how the software runs. Therefore, dynamic software analysis tools monitor the runtime state of a program and observe situations that may only arise during actual execution. Because they work alongside the executing program, and are therefore able to check any executed path, these tests can observe situations that static analyses have difficulty checking. An added benefit is the ability to run in conjunction with static analyses, making their design decisions largely orthogonal. This section reviews a series of dynamic analyses, as well as their benefits and disadvantages.

Assertion Checking. Some analysis systems begin their search for errors by statically analyzing the code for operations that can be proven to be either secure or insecure. The tool can then insert dynamic checks around the remaining operations to ensure their correctness at runtime. CCured, for example, uses this combination to ensure type safety [67] and find memory errors such as buffer overflows [162]. The overheads observed with these tools depend both of the complexity of the assertions and the power of the static analysis. The simple memory assertions inserted by CCured slow a selection of computationally-intensive applications up to 87% [47].

**Dynamic Dataflow Analysis.** Dynamic dataflow analyses associate shadow values with memory locations, propagate them alongside the execution of the program, and check them to find errors. Valgrind's Memcheck tool, perhaps the most widely used of this type of analysis, keeps track of whether a value has been initialized (or is derived from an initialized location), and can find memory leaks and other such errors [167]. Similarly, dynamic heap

bounds checkers, such as Valgrind's Annelid tool, associate pointers with heap allocations and verify that every dereferenced value points to a location within the valid range of its region [165]. Taint analysis follows "untrusted" data through a process to determine whether it is used without being properly validated [170].

The performances of these systems can vary widely and depend on the type of analysis, the optimizations applied, the system used to construct the tool, and the inputs given to the particular execution of the program under test. Memcheck has overheads of about  $20\times$ , while Dr. Memory, a similar tool built using a different instrumentation tool, has overheads of about  $10\times[28]$ . Overheads for taint analysis tools range from 50% [27] to upwards of  $150\times[93]$ , and greatly depend on the accuracy and portability of the analysis and instrumentation tools.

Data Race Detection. Data races occur when two parallel threads of execution access a single shared memory location without a guaranteed order of operations between them. More formally, a data race occurs when two or more threads access a single memory location, at least one access is a write, and there is no enforced order between the accesses [168]. These situations can introduce unintended, and sometimes dangerous, values into the program. Because statically finding all data races in a program is NP-hard [169], most race detectors only attempt to find some data races. Dynamic data race detectors search for these problems through methods such finding violations of Lamport's happens-before relation [116], a subset of this called the lockset algorithm [191], or a hybrid combination of the two [173].

Their performance depends heavily on the tool and its optimizations, as well as the amount of sharing seen within any particular dynamic execution of the program. Tests done for this dissertation put current versions of Helgrind, a race detector built using Valgrind, at about a  $100 \times$  slowdown, while Serebryany and Iskhodzhanov list slowdowns of between  $20 \times$  and  $50 \times$  for Google ThreadSanitizer, a commercial data race detector also built using Valgrind [199].

**Atomicity Violation Detection.** Atomicity violations are concurrency errors that are similar to, yet distinct from, data races. In parallel code, a programmer may desire that some collection of variables be accessed atomically (i.e. no other thread accesses any of the variables until the first thread finishes working on them). However, even if variables are locked in a way that prevents data races, this atomicity is not guaranteed [68]. Lu *et al.* looked at a number of concurrency bugs in large open-source programs and found that atomicity violations were quite common [125].

**Figure 1.6 Dynamic Analyses May Not Always Catch Bugs**. This is a control flow diagram with weighted random probabilities at each branch. It takes an average of 10,000 executions to run the code within basic block **D**. If an bug exists there, a dynamic analysis will only find it 0.01% of the time.

Atomicity violations are difficult to automatically detect, as they are a disconnect between what the programmer *wants* and what she *commands*. While the designer may assume that two regions are executed atomically, a tool cannot learn this assumption from the code. As such, current tools that find these errors focus on training over many known-good executions, recording the observed atomic regions, and later verifying that these regions are always accessed atomically. The online detection mechanisms for these tools have slowdowns that range from  $25 \times [126]$  to upwards of  $400 \times [146]$ .

**Symbolic Execution.** Symbolic execution follows a program as it runs and, rather than working with concrete values for any particular variable, attempts to calculate what *possible* values could exist in the program. As the program calls functions with known return values, passes conditional statements, and uses concrete values, the limits on any particular variable can be constrained. These symbolic values can be checked to find inputs that could cause errors such as memory corruption [118].

The system by Larson and Austin looks only at the control path executed on any particular run, constraining symbolic variables to match the bounds that are imposed by the current path. It tests memory accesses along the executed path to find if they could be corrupted by slightly different inputs that still made it to this state [118]. Tools like DART and KLEE, on the other hand, start with completely unconstrained inputs and systematically search for bugs in all possible control paths [30, 74]. Godefroid *et al.* claim that their symbolic execution is "many times slower than [running] ... a program", while Larson and Austin show overheads between  $13 \times$  and  $220 \times$ .

The powers of these dynamic analysis tools have limitations, of course: only the portions of an application observed during a particular execution can be analyzed, meaning they are unable to catch errors that lie on unexecuted paths. Consequently, dynamic analyses benefit from seeing large numbers of executions with a variety of inputs, allowing them to test more paths. Figure 1.6 demonstrates a simple example of this. If an error existed in basic block

D of this control flow graph, a dynamic analysis would be unable to observe it until the program executed the code within that block. In this case, it would take an average of 10,000 executions of the program before the tool would observe the problem. Unfortunately, the performance overheads introduced by these approaches make it difficult to observe many different executions. These large overheads lead to myopic analyses because they limit the number and quality of test inputs that a developer can execute before shipping a piece of software, reducing the tool's effectiveness.

#### 1.5 Contributions of this Work

Ideally, end-users would run these dynamic software analyses, as they execute the program more often than developers and use inputs that test engineers may not think to examine. Unfortunately, it is unlikely that end-users would be willing to use programs that have been modified to be  $2\times$ , let alone  $200\times$ , slower. Few would purchase a faster computer to run software analyses, and it is doubtful that users who pay for CPU time (such as cloud computing customers) would wish to centuple their costs in order to find errors.

This dissertation will present methods for accelerating dynamic software analyses so that they can be distributed to large populations of end-users. This enables a form of crowd-sourcing for these tests, where users would combine their efforts to find previously unknown bugs. Test distribution could be done by allowing users to opt into testing the program at acceptable overheads, or perhaps requiring that beta versions of the software include analyses. In either case, these users would report potential errors found by the analyses in a similar manner to current crash reports, such as with Breakpad [76] or Windows Error Reporting technologies [32]. This dissertation will not go into details of the mechanisms for bug triage in a system of this type. However, Liblit and others have done a great deal of work designing mechanisms for pinpointing the cause of errors using the numerous reports sent from highly distributed bug detection systems [40, 124], and software such as Socorro is used in commercial software to consolidate crash reports from distributed sites [77].

The first technique that will be discussed in this dissertation takes advantage of the fact that complex software systems, those that are most likely to have difficult-to-find bugs, are also likely to have large user populations. Apache httpd, for instance, runs on over 82 million servers [164], and Microsoft's Office XP sold over 60 million licenses in its first year on the market [138].

As previously mentioned, if the overheads of individual analyses were low enough, these large populations could test this software at runtime. If these users were all running

dynamic analyses, each user could analyze a small portion of the program and still help attain high aggregate bug coverage. The slowdowns that each user experiences can therefore be reduced, as the analysis tool need not be enabled at all times. Chapter 2 presents an argument for sampling dynamic analyses in order to reduce their overheads. In other words, the slowdowns seen by any individual user are reduced by analyzing only limited portions of the program at any one time. That chapter then details a novel mechanism for sampling of dynamic dataflow analyses using only the virtual memory hardware available on modern microprocessors.

Hardware should also change to make program analysis easier, in an attempt to reduce the programming burden caused by complex hardware facilities. It is in the processor vendors' best interests to make systems that help software analyses, as users may otherwise migrate to other, more easily programmable systems. The remainder of this dissertation therefore describes new hardware features can help in this regard. Chapter 3 discusses a hardware design that can perform dynamic dataflow analysis sampling more accurately and at lower runtime overheads than the software-only system. By including taint analysis propagation hardware in the pipeline and an on-chip meta-data storage system known as a sample cache, this system can sample a variety of dataflow analyses in a byte-accurate manner and can perform taint analysis sampling at no overhead whatsoever.

While sampling can reduce the overheads of some tests, accelerating others require new hardware features. Chapter 4 details a method of significantly accelerating another type of dynamic analysis, data race detection, by utilizing hardware performance counters that are available on modern microprocessors.

The systems described in Chapters 3 and 4 are relatively application specific. The former looks at dataflow analyses, while the latter works only on data race detection. For a hardware design to have a strong change of existing in modern commercial processors, it should be as general as possible. The more potential users a new hardware feature has, the more likely it will be worth the design and verification effort. Along these lines, Chapter 5 discusses a generic hardware addition, virtually unlimited fine-grained watchpoints, which can be used to accelerate many dynamic software analyses. By allowing the hardware to inform software that is touching "interesting" data, a large runtime overhead can be removed from many analysis tools

Finally, Chapter 6 concludes the work and discusses future research directions that could continue down the path of exploring hardware to make better software.

In a concise statement, this dissertation will argue that we must design appropriate software analysis techniques to ensure that future software is robust and secure. The high overhead and relatively low accuracy of some dynamic software analyses can be mitigated

by using sampling techniques to spread these tests over large user populations. Novel hardware techniques can be used to further refine these tests into useful, low-overhead tools in the software development chain. Because different analyses require different hardware support, this dissertation investigates the many different mechanisms that hardware can present to software analysis tools. It looks at application-specific mechanisms designed to accelerate distributed analyses, existing hardware used in novel ways, and new designed meant to speed up many different analysis tools.

# Chapter 2

# **Distributed Dynamic Dataflow Analysis**

Software debugging has emerged from a Victorian era in which it was done, but not talked about much.

Some Requirements for Architectural Support of Software Debugging

Mark Scott Johnson

As discussed in Chapter 1, dynamic tests such as taint analysis and data race detection can help create robust software. Because they are unable to catch errors that lie on unexecuted paths, these analyses benefit from seeing large numbers of executions with a variety of inputs. End-users could run these tests, then, checking the abundant situations they encounter.

Unfortunately, these systems suffer from very high runtime overheads, as reiterated in Table 2.1. Such large overheads present a twofold problem: they limit the number of test inputs that a developer can execute before shipping a piece of software, and they severely reduce the number of users willing to run the analyses. In both cases, high overheads hamper the tool's effectiveness.

Researchers have proposed numerous solutions to help combat this problem. Zhao *et al.*, for instance, showed mechanisms to accelerate shadow variable accesses [234]. There have also been works on parallelizing analyses [172] and decoupling them from the original execution [44, 189]. Unfortunately, these techniques do not completely eliminate slowdowns. Umbra reduced the overhead of shadow data accesses from  $8-12\times$  to  $2-4\times$  [234], but this is still more than most users would tolerate.

This chapter will make the argument that an excellent solution to this overhead problem is to sample the analyses, analyzing a limited portion of the program during any individual execution. Ideally, the tool's ability to detect errors will be proportional to the slowdown, which would allow users to control the overheads they experience while finding some percentage of the program's errors.

Table 2.1 Overheads from a Selection of Dynamic Analyses. Dynamic analyses cause extremely high overheads because they insert extra instructions into the runtime of the program under analysis. If each original instruction in the program required only one extra instruction for the analysis, there would hypthetically be a  $2\times$  slowdown. Analyses such as symbolic execution, which must perform numerous heavyweight calculations, see overheads of over  $200\times$ .

| Analysis                  | Slowdown                |

|---------------------------|-------------------------|

| Assertion Checking        | 5% – 2×                 |

| Dynamic Dataflow Analysis | 50% – 150×              |

| Data Race Detection       | $8 \times -100 \times$  |

| Atomicity Checking        | $25 \times -400 \times$ |

| Symbolic Execution        | $10 \times -200 \times$ |

Because the entire dynamic execution will not be analyzed while sampling, no test is guaranteed to find all observable errors. However, distributing these sampled analyses across large end-user populations can offset the lower error detection rate. This larger population will also see many more inputs and dynamic states than a developer running a small test suite, further increasing the power of distributed bug-hunting systems.

### 2.1 Introduction to Sampling

Sampling and distributed debugging are not new topics. In such systems, small portions of the program are analyzed during each run, allowing performance increases over a system that constantly checks the program. In a well-designed sampling system, the ability to observe errors is related to both the sampling rate and the performance; lowering the sampling rate will increase the performance but subsequently lower the probability of finding any particular error.

This accuracy reduction can potentially be offset by the large increase in the number of testers. As a simple example: if a sampling analysis catches 10% of the executed errors in a program, and were used to test the example in Figure 1.6, it would catch the error once in every 100,000 executions on average. If 5000 users were to run these analyses, each would only need to run the program an average of 20 (rather than 10,000 or 100,000) times before the error would be observed somewhere, and a report could be returned to the developer. This increase in population not only offsets the accuracy loss due to sampling, but alleviates some of the problem of only observing errors on executed paths.

The remainder of this section reviews some of the previous works in this research area that have informed the contents of this dissertation.

```

randomly_assert(x!=NULL);

x\rightarrow data = 5;

assert(x!=NULL);

x\rightarrow data = 5;

assert(y!=NULL);

x\rightarrow data = 5;

x\rightarrow data = 5;

randomly_assert(y!=NULL);

y \rightarrow data = x \rightarrow data2;

y\rightarrow data = x\rightarrow data2;

y \rightarrow data = x \rightarrow data2;

y \rightarrow data = x \rightarrow data2;

(a) Static Code

(b) Dynamic Run 1

(c) Dynamic Run 2

(d) Dynamic Run 3

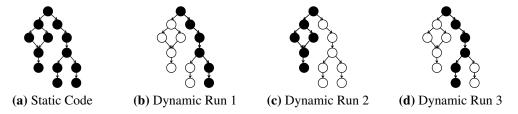

```

**Figure 2.1** Sampling for Assertion Analyses. This system has a random probability of performing any particular test. It is possible that x==NULL in, e.g., (b). However, with a large population, errors will be caught proportional to the percent of time each assertion is enabled.

#### 2.1.1 Sampling for Performance Analysis

While performance analysis is not the same as bug-finding, it is educational to review the works on sampling in this area. Arnold and Ryder showed software mechanisms for sampling performance analyses [9], as did Hirzel and Chilimbi [92]. These mechanisms, in a broad sense, enter the analysis on certain software conditions, profile some instructions, and then leave analysis until the next condition. Hirzel and Chilimbi showed that they were able to gather accurate performance profiles at overheads as low as 3-18% (compared to  $30\%-10\times$  for non-sampled analysis).

The concept of sampling is so well ingrained into the performance analysis community that commodity processors have dedicated performance sampling hardware. While taking interrupts on performance counter rollover is one of the most common ways of analyzing samples of events [208], modern processors also include dedicated performance sampling facilities such as Intel's Precise Event Based Sampling (PEBS) [100] and AMD's Instruction-Based Sampling (IBS) [62]. Such mechanisms amortize interrupt costs by automatically storing information about a subset of instructions or events into physical memory buffers without involving software.

#### 2.1.2 Sampling for Assertion Checking

Liblit *et al.* described an instruction-based method of sampling assertion tests, as demonstrated in Figure 2.1 [123]. As long as the checks are not related to one another, it is possible to perform sampling by only enabling a random subset of the assertions during each execution. They showed that performing this type of sampling was able to lower the maximum overhead of their analysis from  $2.81 \times$  to 26% when sampling one out of every thousand checks. They demonstrate that such sampling rates can find uncommon errors with user populations of moderate size.

Hauswirth and Chilimbi performed similar types of sampling in order to do memory leak detection [89]. Their sampling mechanism enables checks for groups of instructions

so as to reduce the overhead of deciding when to enable the tool. They also showed that sampling reduces overheads (from an estimated  $5 \times$  to 5%), unfortunately, about 7% of their error reports falsely identified active pages as leaked because their tool was disabled during a period where a page was actually used.

#### 2.1.3 Sampling for Concurrency Tests

LiteRace logs memory accesses and synchronization operations and performs offline data race detection on them. As Marino *et al.* point out, logging a small, random sample of the memory accesses will allow many races to be detected while significantly reducing the logging overhead. All synchronization points must still be logged, or the sampling system may cause false positives. By choosing to log cold-path code at a much higher rate, they were able to reduce the runtime overhead from 651% to 28%, while still detecting about 70% of the observable data races [131].

PACER performs online race detection sampling, but enables the detector for long intervals. When the analysis is later disabled, each variable is sent through one last check when it is next accessed. In doing so, Bond *et al.* showed that it is possible to find races in rough proportion to the sampling rate while still allowing control over performance [26].

Finally, Erickson *et al.* described DataCollider, a system that samples a small number of variables in the Windows kernel and sets hardware watchpoints on them. By waiting for the hardware to tell them that some thread has accessed the variable, they are able to significantly reduce the amount overhead that their analysis tool causes. However, because current hardware has an extremely limited number of these watchpoint registers (as will be described in Section 5.2.1), this system *must* use sampling [65].

There is little work on sampling atomicity violation detection in the classic sense. Rather than attempting to sample previous atomicity violation mechanisms, Jin *et al.* instead looked at a new way of detecting atomicity violations by keeping track of samples of data sharing statistics from many user runs. They then traced program crashes back to these errors using statistical analyses, finding both data races and atomicity violations [105]. This type of analysis would not be possible without sampling.

#### 2.1.4 Sampling for Dynamic Dataflow Analyses

There is little previous work on sampling dynamic dataflow analyses. Unfortunately, as will be described in Section 2.2.3, the instruction-based sampling mechanisms used for performance analysis, assertion checking, and concurrency bug testing do not work with dynamic

dataflow analyses. Because these methods of sampling do not maintain knowledge of the underlying shadow dataflows, they can lead to extraneous false negatives and undesired false positives.

Arnold *et al.* showed an object-based analysis sampling method that used the extensive program information available to a Java virtual machine to avoid these problems. Instead of checking a subset of dynamic tests, as instruction-based sampling systems do, their system only performed analyses (ranging from assertion checks to typestate checking) on a subset of instantiated objects [10]. Unfortunately, this method of sampling would be difficult to do, if not impossible, in a system with less access to language-level constructs than a JVM.

This chapter presents a novel software-based dynamic dataflow analysis sampling technique that works on unmodified binaries compiled from any language. It uses an overhead manager that observes the runtime impact of the analysis procedures and can constrain the analysis to a set of stochastically chosen shadow dataflows if performance degrades below a user-specified threshold. This allows developers to run larger tests, and lets users cap the slowdown they experience, which permits large end-user populations to run analyses that were formerly restricted to a development setting. Beta testers, production servers, and even mainstream users can then analyze programs in the background.

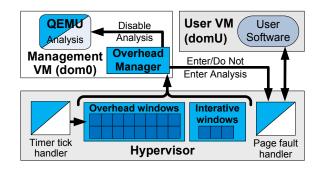

We built a prototype of this distributed dataflow analysis system by modifying the Xen hypervisor [15] to work with an augmented version of the emulator QEMU [20]. This modified emulator implements a taint analysis system, which was used to run experiments that demonstrate how sampling provides fine-grained control of overheads while still delivering high-quality dataflow analyses. Experiments with real-world security exploits show that this solution easily exposed the security flaws in test applications with a small population of users while significantly reducing the performance overhead that individual users experienced.

This work, much of which was originally published in the 2011 paper "Highly Scalable Distributed Dataflow Analysis" [78], makes the following contributions:

- It shows that previous code-based dynamic sampling systems are inadequate for dynamic dataflow analyses. They sample programs' instructions and thus do not take into account the effects of disabling the analysis on shadow dataflows. This leads to both false positives and a large number of false negatives.

- It presents a new technique for performing sampling in dynamic dataflow analysis systems. By sampling dataflows, rather than instructions, it is able to effectively control analysis overheads while avoiding many of the inaccuracies of previous sampling systems.

By allowing individual users to control the sampling rate, this technique enables the

distribution of dynamic analyses to large populations. This chapter will show that

this sampling system is able to observe a large fraction of the errors that a traditional

analysis can discover, but at much lower performance overhead.

The remainder of this chapter is organized as follows: Pertinent background works are reviewed in Section 2.2. Section 2.3 presents a method of dataflow-oriented sampling and Section 2.4 details an implementation of this algorithm. Section 2.5 presents an evaluation of this implementation and demonstrates that it can enable strong analyses while controlling performance overheads. Finally, this chapter is concluded with recommendations for future work, in Section 2.6.

### 2.2 Background

This section presents background concepts that are leveraged in this dynamic dataflow sampling system. It first summarizes how dynamic dataflow analyses operate and then looks at demand-driven analysis, a technique that offers, but does not guarantee, lower performance overhead when performing dynamic dataflow analyses. Finally, it discusses previous works on sampling dynamic analyses and shows how they are inadequate for dataflow sampling.

#### 2.2.1 Dynamic Dataflow Analysis

Dynamic dataflow analyses are tests that associate shadow values with memory locations, propagate them alongside the execution of the program, and check them to find errors. Nethercote and Seward built Valgrind, a popular dynamic binary instrumentation tool that is the basis for a number of dynamic dataflow tools because of its strong support for shadow memory [166, 167]. Memcheck is used to find runtime memory errors, such as uses of undefined variables and memory leaks [200], while Annelid is the preliminary design of a dynamic bounds checker [165]. TaintCheck, one of the first software-only taint analysis systems, is also implemented using Valgrind [170].

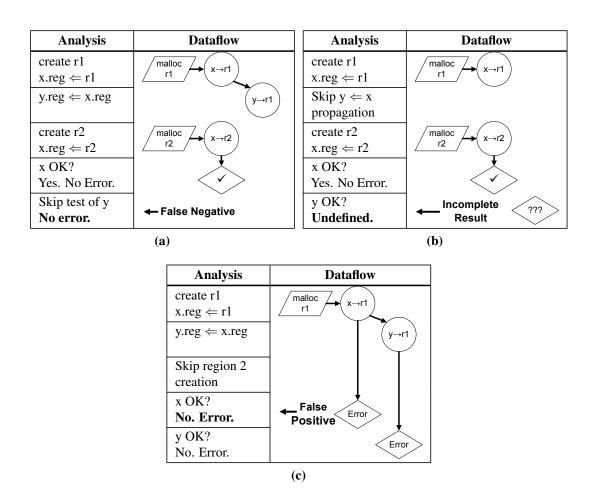

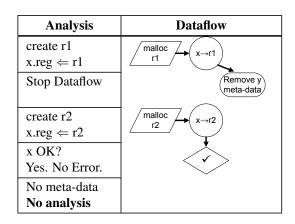

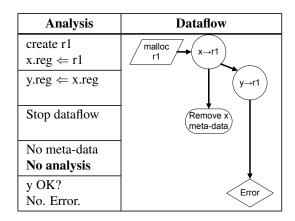

Figure 2.2 shows an example of dynamic dataflow analysis as performed by a heap bounds checker, a mechanism that associates heap meta-data with pointers. The meta-data details the heap objects to which each pointer refers, and it is moved throughout the program along with the pointers and their derived values. When a pointer is dereferenced, the checker verifies that it correctly points within its associated object.

| Dynamic<br>Instructions | Analysis Operations                                                    | Data<br>Values  | Shadow Values                                                               | Dataflow                                                    |

|-------------------------|------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------|

| ptr x = malloc(10);     | create r1<br>x.region ← r1                                             | x: a            | r1.lo: a, r1.hi: a+9<br>x.region: r1                                        | malloc r1 x→r1                                              |

| ptr $y = x + 15$ ;      | $y.region \Leftarrow x.region$                                         | x: a<br>y: a+15 | r1.lo: a, r1.hi: a+9<br>x.region: r1, y.region: r1                          | y→r1                                                        |

| x = malloc(20);         | create r2<br>x.region ← r2                                             | x: b<br>y: a+15 | r1.lo: a, r1.hi: a+9<br>r2.lo: b, r2.hi: b+19<br>x.region: r2, y.region: r1 | $ \begin{array}{c} \text{malloc} \\ \text{r2} \end{array} $ |

| dereference(x);         | $x.region.lo \le x \le x.region.hi?$ Yes. No Error.                    | "               | "                                                                           |                                                             |

| dereference(y);         | y.region.lo $\leq$ y $\leq$ y.region.hi?<br><b>No. Boundary Error.</b> | "               | "                                                                           | Error                                                       |

**Figure 2.2** Example Dataflow Analysis. The figure illustrates how a dynamic bounds checker associates allocated memory regions with pointers and, by propagating the association to derived pointers, builds a dataflow that connects pointers to regions. By checking a dereferenced pointer's address against the bounds of its region, it is possible to find heap errors such as overflows.

In the figure, parallelograms represent points that allocate memory from the heap. These calls to malloc() normally only return pointers to the allocated regions. In this heap analysis system, they also produce meta-data that describe the regions and associations between pointers and these regions (represented in the figure by circles that list their region associations). As pointers are copied, the shadow values associating pointers with regions are also copied into the destination variables; this flow of shadow data is represented by arrows between two circles. Finally, diamonds represent the validity checks that take place when a pointer is dereferenced. A checkmark means that a pointer correctly addressed its associated region, while an error means it did not.

In the example, a 10-byte memory region, r1, is first allocated from the heap, and its start address, a, is stored into the pointer x. The shadow values of this memory region list this start address and the end address of the region, a+9. The pointer x also has a shadow value indicating that x is associated with r1. The pointer x is next used in an arithmetic operation that stores the value a+15 into another pointer, y. Because x was used as the source value for the operation, the shadow value associated with y receives the same region association as x, r1.

The pointer x is then changed to point to a newly associated 20-byte memory region, r2. This region begins at address b and has its own meta-data storing its start and end addresses. This also means that the shadow value for x now associates it with r2.

When the next instruction dereferences x, the analysis system checks that its value, b, is between b and b+19, the start and end addresses of r2. This address is within the region, so the dereference is considered safe. The last instruction attempts to dereference y, leading

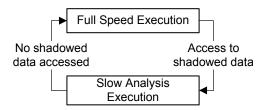

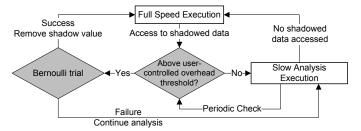

**Figure 2.3** Traditional Demand-Driven Analysis. This technique attempts to execute the program normally and enables slow analysis only when shadowed data is encountered.

the analysis system to compare its value, a + 15, to the limits of its associated region, r1. Because the end of rI is at a + 9, the dereference is not safe and an error is raised.

Heap bounds checking can, as shown, be used to verify that accesses to memory regions are correct, a commonly desired security feature in type-unsafe languages [165]. A number of other powerful tools also use dynamic dataflow analyses.

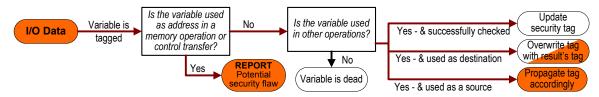

Taint analyses, for instance, associate simple shadow values, or taint bits, with memory locations and propagate them throughout the program. One of the most commonly studied taint analyses is control flow attack detection, which marks memory locations as untrusted when their values originate from unsafe sources [170, 184, 210].

Other examples of this type of analysis include memory corruption detection [38], confidentiality verification [45, 133], malware analysis [231], and error tracing [11]. There is contention in the literature about the efficacy of some types of taint analysis [54, 206, 207], but we note that this does not affect the concept of taint analysis in general. As Schwartz *et al.* point out, the differences in these analyses are the particular semantics of their tainting policies and the desired security gains [197].

Strong dataflow security analyses will sometimes check implicit flows of information which arise because particular control flow paths can yield information about underlying data. The accuracy of taint analyses, for example, can be undermined in certain situations if this information is ignored [33]. However, following such information at runtime requires either costly static analyses before execution [108] or significant and slow extra instrumentation [218]. In either case, this chapter does not focus on sampling such control flow analyses because of the significant difficulties in building the underlying analysis itself.