# Hardware Verification of a Hyper-Efficient (98%) and Super-Compact (2.2kW/dm<sup>3</sup>) Isolated AC/DC Telecom Power Supply Module based on Multi-Cell Converter Approach

Matthias Kasper\*, Cheng-Wei Chen<sup>†</sup>, Dominik Bortis\*, Johann W. Kolar\* and Gerald Deboy<sup>‡</sup>

\* Power Electronic Systems Laboratory, ETH Zurich, Switzerland, Email: kasper@lem.ee.ethz.ch

<sup>†</sup> Electric Energy Processing Laboratory, National Taiwan University, Taipei, Taiwan

<sup>‡</sup> Infineon Technologies Austria AG, Villach, Austria

Abstract—Due to the increasing electricity demand of data centers driven by the emergence of cloud computing and big data, the focus on the development of telecom and data center power supplies is shifted towards high efficiencies. In this paper, a multi-cell converter approach for a telecom rectifier module breaking through the efficiency and power density barriers of traditional single-cell converter systems is shown. The comprehensive optimization of the entire system with respect to efficiency and volume is described and the applied component loss models are explained. Furthermore, the design of a hardware demonstrator based on the optimization results is presented and several important design aspects are explained in detail.

# I. INTRODUCTION

Due to the increasing popularity of cloud based internet services and the trend around big data, the electricity consumption of data centers has grown tremendously in the past decade and is projected to grow in the future even further, e.g. around 70% from 2013 to 2020 in the US alone [1]. As a consequence, data centers are now one of the largest consumers of electricity and therefore also under a growing financial and political pressure to increase their energy efficiency.

Nowadays, conventional single-phase telecom power supplies typically consist of a PFC rectifier stage in connection with an isolated DC-DC converter stage in order to generate an output voltage of 48 V for the subsequent conversion stages. The rectifier stage is usually a boost-type PFC converter with a full bridge diode rectifier, that creates considerable conduction losses due to the forward voltage drops of the employed diodes. This has initiated a trend towards bridgeless topologies as an alternative topology [2], [3]. One example of a highly efficient power supply for telecom applications is a triple-parallel-interleaved TCM PFC rectifier system [4] in combination with a double-parallel-interleaved phase-shifted full-bridge isolated DC-DC converter (rated power  $P_{out}$  =  $3.3 \,\mathrm{kW}$ , output voltage  $V_{\mathrm{out}} = 48 \,\mathrm{V}$ ) featuring a power density of  $\rho = 3.3 \, \mathrm{kW/dm^3}$  and an efficiency of  $\eta = 97 \, \%$ at half of the rated power. As shown in [5], this concept currently presents the leading edge technology for telecom power supplies.

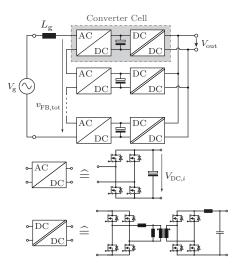

A new and very different approach towards a hyper-efficient

**Fig. 1:** Multi-cell telecom power supply module with input-series output-parallel connection of the converter cells. Each cell consists of a full bridge AC-DC rectifier input stage and an isolated DC-DC converter comprising a phase-shifted full-bridge converter.

and super-compact telecom rectifier design beyond the barriers of traditional converter concepts has been presented in [6]. The approach is based on a multi-cell converter concept with series connection of the converter cells at the input side and parallel connection at the output side (i.e. ISOP), as shown in Fig. 1. Each converter cell formed by an AC-DC rectifier stages which is operated with a Totem-Pole modulation and an isolated DC-DC converter stage consisting of phase-shifted full bridge converter. This multi-cell ISOP configuration allows to share the input voltage among the converter cells and thus enables the use of low-voltage rated semiconductors throughout the converter cells. According to the scaling laws of [7] with this approach significant benefits in terms of reduced conduction and switching losses and smaller volume of inductive components and heat sinks, among others, can be achieved. Based on the specification of Tab. I the system performance targets that should be reached by utilizing the advantages of the multi-cell converter topology are an output power of  $P_{\text{out}} = 3.3 \,\text{kW}$  with

Tab. I: Specifications of the multi-cell telecom rectifier module.

| Parameter                | Variable       | Value                             |

|--------------------------|----------------|-----------------------------------|

| Nominal grid voltage     | Vgrid,RMS,nom  | $230\mathrm{V}$ / $50\mathrm{Hz}$ |

| Grid voltage range       | Vgrid,RMS      | $180\mathrm{V}$ - $270\mathrm{V}$ |

| Rated output power       | Pout           | $3.3\mathrm{kW}$                  |

| Nominal output voltage   | Vout,nom       | $48\mathrm{V}$                    |

| Output voltage range     | Vout           | $40\mathrm{V}$ - $60\mathrm{V}$   |

| Total DC-link voltage    | $V_{\rm DC}$   | $400\mathrm{V}$                   |

| Hold-up time             | $T_{\rm hold}$ | $10\mathrm{ms}$ @ rated power     |

| Switching freq. per cell | $f_{ m sw}$    | $\geq 18\mathrm{kHz}$             |

| EMI standards            |                | CISPR Class A and B               |

a conversion efficiency of 98% at part load operation and a power density of  $\rho = 2.2 \, \mathrm{kW/dm^3}$ .

In this paper, at first the optimization and of the system is discussed in detail and the results are analyzed in **Sec. II**. Afterwards, the realization of the hardware demonstrator is described in **Sec. III** and different design aspects are addressed. Finally, conclusions are drawn in **Sec. IV**.

# II. SYSTEM OPTIMIZATION AND RESULTS

In [7] a comprehensive system modeling and optimization in terms of efficiency and power density of the ISOP multicell telecom rectifier module has been presented. In this optimization all available degrees of freedom for the design of the AC-DC and the DC-DC converter stages have been considered such as

- Switching frequency: The effective switching frequency of the AC-DC rectifier stage equals the switching frequency of a single cell multiplied by the number of cells due the interleaved operation of the rectifier stages, i.e.  $f_{sw,eff} = N_{cells} \cdot f_{sw}$ . A natural lower limit of the switching frequency of a single cell can be deducted from the range of audible frequency which should be avoided by choosing  $f_{sw} \ge 18 \text{ kHz}$ . The upper boundary of feasible switching frequencies can be derived by the CISPR EMI standards that impose limits on harmonics at frequencies above  $f_{\rm EMI} \ge 150 \text{ kHz}$  [8]. As a consequence the switching frequency per cell should be limited to  $f_{sw} < f_{\rm EMI}/N_{cells}$ . This applies only to the AC-DC stages. The switching frequency of the DC-DC converter stages was swept over a wide frequency range (50 – 500 kHz).

- Design of inductive components: The optimization of inductive components represents a Pareto trade-off on its own as several degrees of freedom for the design of the inductor and transformer, respectively, are given, like the core size, core material, conductor type, number of turns and air gap. With core and winding loss models the  $\eta$ - $\rho$  Pareto-optimal designs can be found [9].

- *MOSFET chip size and junction temperature*: The chip size of the MOSFETs is an important parameter for the trade-off between conduction and switching losses [4], as given for the AC-DC stage which is operated under hard-switching. Furthermore, the thermal resistance between the junction and the case of the semiconductor changes with the chip size, which also influences the design and volume of the heat sink.

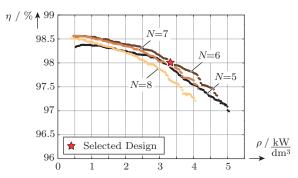

Fig. 2: Pareto-optimal (efficiency / power-density) designs of the multi-cell telecom power supply module for different numbers of converter cells and a drop of the DC-link voltage during the hold-up time of  $k_{\text{DC,drop}} = 20\%$ .

• *DC-link capacitor realization*: The size and type of the employed DC-link capacitors offers an trade-off between the overall volume of the DC-link capacitors and the losses caused by the equivalent series resistance (ESR).

These parameters, among others, are subject to a trade-off between the power-density and the efficiency of the entire system. Therefore, for all combinations of design parameters the system performance has to be determined by employing component loss and volume models.

The volumes of the converter designs have been determined by considering the sum of all component boxed volumes, such as the volume of the

- DC-link capacitors

- Inductive components

- EMI filter components

- Heat sink.

The volume of PCBs and control electronics have not been considered since they are layout dependent and thus not available for the optimization. For the calculation of the conversion efficiency following losses have been included:

- AC-DC Full-bridge MOSFETs

- Switching losses

- Conduction losses

- Gate drive losses

- Phase-shifted Full-bridge MOSFETs

- Conduction losses

- Gate drive losses

- Synchronous rectifier MOSFETs

- Conduction losses

- Reverse recovery losses

- Gate drive losses

- Inductive components

- Core losses

- Winding losses (incl. HF-losses).

In addition, the losses caused by the equivalent series resistance of the electrolytic capacitors and constant losses caused by auxiliary and control electronics have been included. Design specific losses such as the conduction losses of the PCB have been omitted in the calculation as they vary with the layout. As a result of this comprehensive system optimization a clear

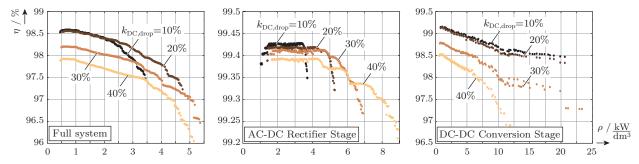

Fig. 3: Impact of different values of the maximum permissible drop of the DC-link voltage during the hold-up time,  $k_{DC,drop}$ , on the achievable Pareto-optimal results of the entire system, the AC-DC rectifier stages and the DC-DC converter stages.

optimum can be found for the number of employed converter cells at  $N_{\rm opt} = 6$ . Even though the scaling laws derived in [7] predict a better performance with increasing number of cells, external and other practical constraints outweigh the benefits of a larger cell number, such as EMI limiting standards beginning at  $f_{\rm EMI} = 150 \, \rm kHz$ , the package resistance of MOSFETs, and communication and control overhead.

The telecom supply is required to feature a hold-up time of  $T_{\rm hold} = 10 \, {\rm ms}$  (cf. **Tab. I** for the full set of specifications) which necessitates electrolytic capacitors within each cell. The voltage drop of these capacitors during the hold-up time was found to be another optimization parameters that exhibits an optimum at a value of  $k_{\rm DC,drop} = 20\%$ .

The Pareto-optimal results of the system optimization are shown in **Fig. 2** for full load operation at the nominal operating point for different numbers of converter cells and a maximum permissible drop of the DC-link voltage during the hold-up time of  $k_{\text{DC,drop}} = 20\%$ .

The influence of  $k_{DC,drop}$  on the achievable system performance is depicted in **Fig. 3(a)** for the entire system and in **Fig. 3(b)** and (c) for the AC-DC and DC-DC stage, respectively. In the calculations the electrolytic DC link capacitors have been allocated to the AC-DC converter.

## III. HARDWARE DEMONSTRATOR DESIGN

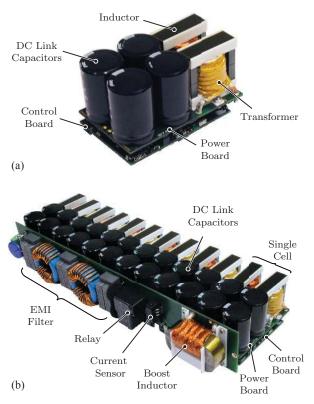

The design which is selected for the hardware demonstrator with a calculated maximum efficiency of  $\eta = 98\%$  at 75% of the rated output power and a power density above  $\rho_{calc} = 3 \,\text{kW/dm}^3$  is marked in **Fig. 2**. The main system parameters of the selected design are listed in **Tab. II**. A picture of the assembled prototype is shown in **Fig. 4** which features a volume of Vol = 30.4 cm·4.5 cm·11 cm = 1.504 dm<sup>3</sup> and thus an overall power density of  $\rho_{sys} = 2.2 \,\text{kW/dm}^3$ . The power density of the prototype is lower than the calculated value since the space between the components adversely affects the achievable power density and the volume of the PCB and the control boards have not been included in the calculations.

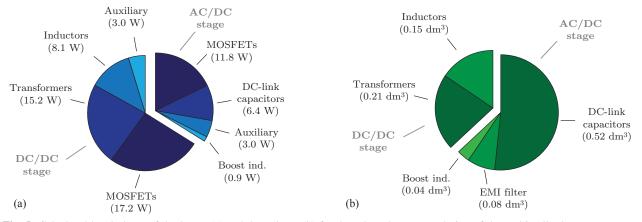

A detailed break down of the calculated losses and volumes is provided in **Fig. 5** for full load operation.

In the following paragraphs different design aspects of the converter system are described in detail.

**Tab. II:** Main system parameters of the selected design for the hardware demonstrator with N = 6 converter cells. (All values given per component, e.g. parallel MOSFETs, if not otherwise noted.)

| AC-DC rectifier     |                                                        |  |

|---------------------|--------------------------------------------------------|--|

| Switching frequency | $f_{ m sw,cell} = 20  m kHz$                           |  |

| Boost inductance    | AMCC-4, 2605SA1, 36 µH, 5 turns                        |  |

| MOSFETs             | 2xBSC046N10NS3G, 100 V, $4.6 \mathrm{m}\Omega$         |  |

| DC-link cap.        | 4xPanasonic ECO-S1KA222CA, alum. elect.,               |  |

|                     | $80 \mathrm{V},  2.2 \mathrm{mF}$                      |  |

| EMI filter          | 3 stages, 2x common mode chokes                        |  |

|                     | (EPCOS R40 cores T38, 10 turns), 3x680 nF              |  |

| DC-DC converter     |                                                        |  |

| Switching frequency | $f_{\rm sw} = 200  \rm kHz$                            |  |

| Transformer         | turns ratio 7:7, ETD34/17/11, N87, EPCOS               |  |

|                     | litz wire $(600x71 \mu\text{m})$                       |  |

| Inductance          | ETD34/17/11, N87, EPCOS, 20.5 μH                       |  |

| Prim. MOSFETs       | BSC046N10NS3G, $100 \text{ V}$ , $4.6 \text{ m}\Omega$ |  |

| Sec. MOSFETs        | BSC046N10NS3G, $100 \text{ V}$ , $4.6 \text{ m}\Omega$ |  |

#### Phase-shifted full bridge converter

The phase-shifted full bridge converter (PSFB) with full bridge synchronous rectification (SR) is chosen for the isolated DC-DC converter stage since it allows to achieve a comparably high efficiency by operating the semiconductors under zerovoltage switching (ZVS) and still provides an easy way to control the power flow by means of the phase shift between the bridge legs on the primary side at a constant switching frequency. For a proper operation of the converter, however, certain design guidelines have to be considered [10]. While ZVS can be achieved for the lagging leg of the primary full bridge easily by utilizing both the energy stored in the output inductor and in the leakage inductor of the transformer, the operation of the leading leg with ZVS relies solely on the energy stored in the leakage inductance during the freewheeling phase

$$E_{\rm L\sigma} = \frac{1}{2} L_{\sigma} \left( I_{\rm Load} \cdot n_{\rm tr} + I_{\rm mag} \right)^2 \tag{1}$$

This energy has to be sufficient to charge/discharge the parasitic output capacitances of the MOSFETs in the leading bridge leg. An energy analysis reveals that soft switching can only be achieved if the energy  $E_{L\sigma}$  is larger than the energy which is fed back into the DC input voltage during discharge

Fig. 4: Multi-cell single-phase AC-DC telecom rectifier prototype with 6 converter cells in ISOP configuration for a rated power of 3.3 kW and a power density of  $\rho = 2.2 \text{ kW/dm}^3$ : (a) single cell and (b) full system ( $30.4 \text{ cm} \cdot 11 \text{ cm} \cdot 4.5 \text{ cm} / 12 \text{ in} \cdot 4.3 \text{ in} \cdot 1.8 \text{ in}$ ).

of the charge equivalent capacitance of a MOSFET, i.e.

$$E_{\rm C,sw} = C_{\rm oss,Qeq} \cdot V_{\rm DC}^2. \tag{2}$$

In the prototype at hand, the leakage inductance of the transformer was selected to be  $L_{\sigma} = 1 \,\mu\text{H}$  by adjusting the winding arrangement. This allows to achieve soft-switching in the leading leg at levels of the output current above  $I_{\text{Load}} \ge 3.4 \,\text{A}$ (i.e. 30%) according to (1) and (2). Increasing the leakage inductance even further for a broader range of load currents for soft switching would introduce the drawback of a larger duty cycle loss caused by the time required to reverse the current in the leakage inductance from  $(-I_{\text{Load}} \cdot n_{\text{trafo}})$  to  $(+I_{\text{Load}} \cdot n_{\text{trafo}})$  or vice versa, thus rendering it as an unpractical solution.

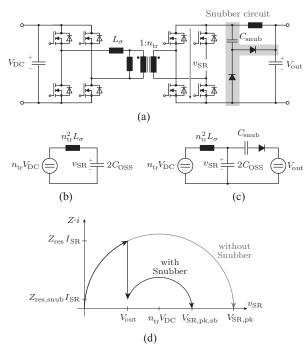

Another issue in the operation of the PSFB is the voltage ringing at the secondary rectifier MOSFETs after the freewheeling phase. The ringing is caused by the resonant circuit comprising the leakage inductance  $L_{\sigma}$  of the transformer and the parasitic capacitances of the rectifier MOSFETs ( $2 \cdot C_{OSS}$ ) since the voltage across the output rectifier is decoupled by the output inductor from the output voltage and therefore not clamped to a fixed voltage (cf. **Fig. 6(b)**). The resonant frequency of this resonant circuit equals

$$\omega_{\rm res} = 1/\sqrt{2C_{\rm oss}L_{\sigma}n_{\rm tr}^2} \tag{3}$$

and the characteristic impedance amounts to

$$Z_{\rm res} = \sqrt{L_\sigma n_{\rm tr}^2 / (2C_{\rm oss})}.$$

(4)

The worst case voltage overshoot can reach the value of twice the transformed primary voltage  $V_{\text{SR,peak}} = 2V_{\text{sec}} = 2n_{\text{tr}}V_{\text{DC}}$ , as shown in **Fig. 6(d)**. In the case at the hand, the DC-bus voltage in each cell equals  $V_{\text{DC}} = V_{\text{DC,tot}}/N_{\text{cells}} = 400 \text{ V}/6 =$ 66 V and with a transfomer turns ratio of  $n_{\text{tr}} = 1$  the worst case voltage spike could reach around  $V_{\text{SR,peak}} = 133 \text{ V}$  which would lead to the destruction of the synchronous rectification MOSFETs with a voltage rating of  $V_{\text{DS,max}} = 100 \text{ V}$ . Since the diodes in the rectifier MOSFETs are prone to reverse recovery effects, the voltage spike increases depending on the peak reverse recovery current  $I_{\text{RR}}$  and can be calculated as

$$V_{\rm SR,pk} = V_{\rm DC} n_{\rm tr} + \sqrt{(V_{\rm DC} n_{\rm tr})^2 + (Z_{\rm res} I_{\rm RR})^2}$$

(5)

In order limit the voltage spike a loss-less snubber circuit consisting of a snubber capacitor  $C_{\text{Snub}}$  and two diodes is added to the converter [11]. An alternative snubber that works with an additional transformer winding can be found in [12]. By introducing the snubber the equivalent circuit of

Fig. 5: Calculated break-down of the losses (a) and the volume (b) for the selected converter design of the multi-cell telecom power supply module at full load.

**Fig. 6:** Phase-shifted full bridge converter with over-voltage limiting loss-less snubber circuit [11] for the secondary rectifier MOSFETs: (a) application of the snubber circuit to the converter; (b) equivalent circuit of the resonant network for the case without snubber; (c) modified resonant network for case with snubber elements; (d) comparison of the resonant trajectories for the cases with and without snubber elements and their resulting voltage peaks  $V_{SR,pk,sb}$  and  $V_{SR,pk}$ , respectively. (The influence of the reverse recovery current of the MOSFET body diodes is not shown.)

the resonant network changes as shown in **Fig.** 6(c) and the resonant frequency becomes

$$f_{\rm res,snub} = 1/\sqrt{L_{\sigma} n_{\rm tr}^2 (2C_{\rm oss} + C_{\rm snub})} \tag{6}$$

while the resonant impedance becomes

$$Z_{\rm res,snub} = \sqrt{L_{\sigma} n_{\rm tr}^2 / (2C_{\rm oss} + C_{\rm snub})}$$

(7)

after the voltage  $v_{SR}$  has risen above the level of the output voltag  $V_{out}$ . This is also depicted in **Fig. 6(d)** where the sudden change of the resonant impedance leads to a drop in the  $v_{SR} - Z \cdot i$  plane. The maximum voltage spike can then be derived as a function of the output voltage to be

$$V_{\rm SR,pk,sb} = V_{\rm DC} n_{\rm tr} + \sqrt{(V_{\rm DC} n_{\rm tr} - V_{\rm out})^2 + (Z_{\rm res,snub} I_{\rm SR})^2}.$$

(8)

The snubber capacitor is chosen to have a value of  $C_{\text{Snub}} = 15 \text{ nF}$  which limits the worst case voltage spike at the lowest output voltage of  $V_{\text{out,min}} = 40 \text{ V}$  to  $V_{\text{SR,peak,snub}} = 92 \text{ V}$  without considering the influence of the reverse recovery current. For the material of the ceramic snubber capacitors the COG (NP0) dielectric is chosen since it provides a stable capacitance value under varying temperature and voltage. In order minimize the reverse recovery currents of the diodes, the conduction time of the diodes in the SR MOSFETs is kept to a minimum (around 10 ns) by adjustments of the timings of the gate signals [13].

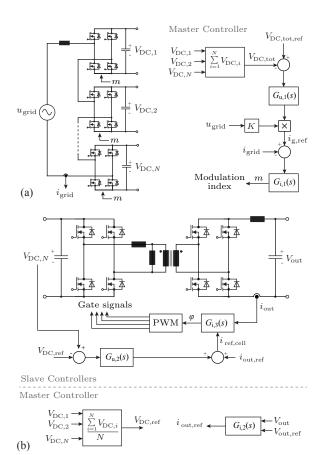

**Fig. 7:** Control implementation of the multi-cell telecom rectifier: (a) total DC-bus voltage controller and input current controller; (b) output current controller and DC-link voltage controller.

#### Control implementation

One of the main challenges regarding the control of multicell converters in general is the unbalance of the DC-link voltages of the cell. In order to overcome this problem different control strategies have been proposed [14]-[18]. The basic idea behind those concepts is to perform voltage balancing control either by the cascaded H-bridge rectifier or the isolated DC-DC converters. In [14] a voltage balance control is presented which is based on the single-phase dq-control for the rectifier, and a power balance control method to regulate the power transferred through the DC-DC converter that are connected in parallel at their outputs. This allows to individually adjust the power transfer from each DC-link to the output in order to balance the DC-link voltages. In contrast, [15] presents a method to control and balance the voltage of the DC-links by operating the rectifier stages with a mixture of low and high frequency PWM. However, both of the aforementioned methods result in rather complicated controller implementations since the voltage balancing requires additional control loops. A simpler way to operate the ISOP system is presented in [16] which uses a common-duty-ratio control method which relies on the natural balancing behavior of ISOP multi-cell converters [17]. However, this method is not actively balancing the DC-link voltages. Therefore, any mismatch between the converters,

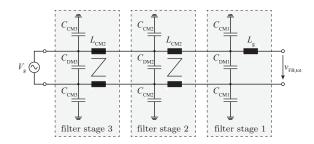

Fig. 8: Schematic of the employed 3-stage common-mode and differential-mode EMI filter.

such as e.g. slightly different transformer terminal behaviors, will lead to different AC voltage ripples on the DC-link capacitors caused by the pulsating power of the mains. These differences in the DC-link voltages will generate circulating currents at the parallel connected converter outputs which decreases the efficiency of the system. Thus, the control scheme which is selected for the implementation in the prototype has a total dc-link voltage regulator on the rectifier side in order to have a constant total dc-link voltage (i.e. the sum of all DClink voltages). In addition, each cell possesses individual DClink voltage and load current control for the isolated DC-DC converters [18]. Fig. 7 shows the control block implementation of the entire system. The control loops can be implemented as a master-slave control regime where the slower outer voltage control loops are processed by the master cell and the faster inner control loops like the current controllers are computed locally on each cell. The communication between the cells is realized by the serial peripheral interface (SPI).

#### EMI Filter Design

For the design of the EMI filter the influence of the differential-mode and the common-mode noise have to be considered. The filter design can be performed individually for the common-mode and the differential-mode noise if the required attentuation for each case is calculated with a margin of around  $16 \,\mathrm{dB}$  to the limits, i.e.  $6 \,\mathrm{dB}$  for the worst case addition of the two noise signals and  $10 \,\mathrm{dB}$  to account for component tolerances.

In order to calculate the required attenuation for the differential-mode noise, the first harmonic that falls into the EMI constrained spectrum ( $f_{\rm EMI} \ge 150 \, \rm kHz$ ) is considered, since the amplitude of the harmonic spectrum of square wave voltage decreases with  $-20 \,\mathrm{dB}$  per frequency decade, whereas the filter attenuation increases with  $-40 \cdot N_s \,\mathrm{dB}$  with  $N_s$  being the number of filter stages. For the case at hand, the first harmonic in the constrained frequency range is at twice the effective switching frequency  $f_{\rm sw,eff} = 120 \, \rm kHz$  of the interleaved AC-DC stages, i.e.  $f_{\text{filt}} = 240 \,\text{kHz}$ . The compliance with EMI standards is evaluated by determining the quasipeak emission levels of the converter. The quasi-peak voltage of the harmonic at  $f_{\text{filt}} = 240 \,\text{kHz}$  is calculated by considering a 9 kHz band around that harmonic and by synthesizing a time domain signal which is fed into the non-linear quasipeak detection network [19] and results in a quasi-peak noise voltage of the converter at  $f_{\rm filt} = 240 \,\rm kHz}$  of  $V_{\rm filt,qp} = 17.2 \,\rm V$ and/or a required attenuation of 92.8 dB including the margin previously mentioned. Following the filter volume optimization guidelines presented in [20] the number of filter stages for a minimum volume and its associated volume can be found at  $n_{\rm filt} = 3$  as shown in **Fig. 8**. The maximum value of the total differential mode capacitance is limited by the maximum allowable reactive power consumption of the filter. The limit was set such that a power factor of  $\cos\phi = 0.9$  can be reached above 10% of the nominal power. This leads to total differential mode capacitance of  $C_{\rm DM,tot} = 2 \,\mu\rm F$ , which means each differential mode capacitance amounts to  $C_{\rm DM} = 660 \,\rm nF$ . This leads to differential mode inductances of  $L_{\rm DM} = 18 \,\mu\rm H$ in order to achieve the required attenuation in combination with the boost inductor  $L_{\rm g}$ .

The precise modeling of the common-mode noise is challenging since it requires the exact knowledge of the stray capacitances of all electric nodes in the converter cells to the ground. Since this is practically impossible to determine for multi-cell converter systems, an approach as presented in [21] was followed which deduces an equivalent circuit for the common-mode noise. By applying a worst-case approximation and neglecting small capacitances compared to larger ones, it can be found that due to the nature of the series connection of the converter inputs the measured common-mode voltage at the line impedance stabilization network (LISN) depends on which cell of the series stack is switching. So, for example each time the lowest cell of the series stack switches, all upper cells are also moved in respect to their potential to ground. Since the cells are operated interleaved, the common-mode voltage resembles a staircase like voltage waveform with the levels being

$$v_{\rm CM}(i) = \frac{N_{\rm cells} - i}{N_{\rm cells}} \cdot V_{\rm DC} \tag{9}$$

for  $i \in [1, N_{cells}]$  where i = 1 means that the lowest cell of the stack is switched and  $i = N_{cells}$  means the uppermost cell is switched. Based on that voltage waveform the quasipeak voltage spectrum can be derived by means of simulations and the required common-mode filter attenuation can be determined to be 78 dB. The maximum allowable total common-mode filter capacitance is limited by the maximum total leakage current to earth (e.g. 3.5 mA RMS) which leads to  $C_{\rm CM,tot} = 36\,{\rm nF}$  and thus the value for each commonmode capacitor is selected as  $C_{\rm CM} = 4.7 \, {\rm nF}$ . Usually, the smallest common-mode filter volume is obtained by utilizing the maximum allowable amount of common-mode filter capacitance [22]. As a result, the common-mode inductances can be determined to be  $L_{\rm CM} = 1.6 \,\mathrm{mH}$ . In the protoype, the leakage inductance of the common-mode chokes is utilized as differential-mode filter inductances.

### **IV. CONCLUSION**

A new approach towards a highly efficient and very compact telecom recitifier module beyond the limits of state-of-the-art systems is presented. The degrees of freedom in the design procedure of a multi-cell telecom power supply module in ISOP configuration are outlined and the optimization process is described in detail. The optimization results show that a converter design with an efficiency of  $\eta = 98\%$  and a power density of  $\rho = 2.2 \,\mathrm{kW/dm^3}$  can be achieved. The results also reveal an optimum value of N = 6 for the number of converter cells and an optimum maximum permissible drop of 20% the DC-link voltage during the hold-up time. Based on the optimization results a hardware demonstrator realization is presented and specific design aspects are explained. First measurement results verify the operation of the system and will be summarized in future publication.

## REFERENCES

- National Resources Defense Counsil, "Data Center Efficiency Assement - Scaling Up Energy Efficiency Across the Data Center Industry: Evaluating Key Drivers and Barriers," August 2014.

- [2] L. Huber, Y. Jang, and M. M. Jovanovic, "Performance Evaluation of Bridgeless PFC Boost Rectifiers," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1381–1390, 2008.

- [3] D. Bortis, L. Faessler, and J. W. Kolar, "Comprehensive Analysis and Comparative Evaluation of the Isolated True Bridgeless Cuk Single-Phase PFC Rectifier System," in *Proc. of the 14th Workshop* on Control and Modeling for Power Electronics (COMPEL), pp. 1–9, 2013.

- [4] J. W. Kolar, F. Krismer, Y. Lobsiger, J. Muehlethaler, T. Nussbaumer, and J. Minibock, "Extreme Efficiency Power Electronics," in *Proc. of the 7th Int. Conf. of Integrated Power Electronics Systems (CIPS)*, pp. 1–22, 2012.

- [5] G. Deboy, "Challenges and System Solutions for Maximizing Energy Efficiency in SMPS and PV Applications," in *Proc. of the 39th Annual Conf. of the IEEE Industrial Electronics Society (IECON) Keynote Presentation*, 2013.

- [6] M. Kasper, D. Bortis, J. W. Kolar, and G. Deboy, "Hyper-Efficient (98%) and Super-Compact (3.3kW/dm<sup>3</sup>) Isolated AC/DC Telecom Power Supply Module based on Multi-Cell Converter Approach," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, pp. 150–157, 2014.

- [7] M. Kasper, D. Bortis, and J. Kolar, "Scaling and Balancing of Multi-Cell Converters," in *Proc. of the International Power Electronics Conference* (*IPEC*), 2014.

- [8] J. Muehlethaler, H. Uemura, and J. W. Kolar, "Optimal Design of EMI Filters for Single-Phase Boost PFC Circuits," in *Proc. of the 38th Annual Conf. of the IEEE Industrial Electronics Society (IECON)*, pp. 632–638, 2012.

- [9] R. Burkart, H. Uemura, and J. W. Kolar, "Optimal Inductor Design for 3-Phase Voltage-Source PWM Converters Considering Different Magnetic Materials and a Wide Switching Frequency Range," in *Proc. of the International Power Electronics Conference (IPEC)*, 2014.

- [10] J. Sabate, V. Vlatkovic, R. Ridley, F. Lee, and B. Cho, "Design Considerations for High-Voltage High-Power Full-Bridge Zero-Voltage-Switched PWM Converter," in *Proc. of the 5th Annual Applied Power Electronics Conference and Exposition (APEC)*, pp. 275–284, 1990.

- [11] J.-G. Cho, J.-W. Baek, C.-Y. Jeong, and G.-H. Rim, "Novel Zero-Voltage and Zero-Current-Switching Full-Bridge PWM Converter Using a Simple Auxiliary Circuit," *IEEE Trans. Ind. Appl.*, vol. 35, no. 1, pp. 15–20, 1999.

- [12] U. Badstuebner, "Ultra-high Performance Telecom DC-DC Converter," Ph.D. dissertation, Power Electronic Systems Laboratory, ETH Zurich, 2012.

- [13] D. Polenov, T. Reiter, R. Baburske, H. Probstle, and J. Lutz, "The Influence of Turn-Off Dead Time on the Reverse-Recovery Behaviour of Synchronous Rectifiers in Automotive DC/DC-Converters," in *Proc. of the 13th European Conference on Power Electronics and Applications (EPE)*, pp. 1–8, 2009.

- [14] T. Zhao, G. Wang, S. Bhattacharya, and A. Q. Huang, "Voltage and Power Balance Control for a Cascaded H-Bridge Converter-Based Solid-State Transformer," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1523–1532, 2013.

- [15] H. Iman-Eini, J.-L. Schanen, S. Farhangi, and J. Roudet, "A Modular Strategy for Control and Voltage Balancing of Cascaded H-Bridge Rectifiers," *IEEE Trans. Power Electron.*, vol. 23, no. 5, pp. 2428–2442, 2008.

- [16] R. Giri, V. Choudhary, R. Ayyanar, and N. Mohan, "Common-Duty-Ratio Control of Input-Series Connected Modular DC-DC Converters with Active Input Voltage and Load-Current Sharing," *IEEE Trans. Ind. Appl.*, vol. 42, no. 4, pp. 1101–1111, 2006.

- [17] W. van der Merwe and T. Mouton, "Natural Balancing of the Two-Cell Back-to-Back Multilevel Converter with Specific Application to the Solid-State Transformer Concept," in *Proc. of the 4th IEEE Conf. on Industrial Electronics and Applications (ICIEA)*, pp. 2955–2960, 2009.

- [18] R. Ayyanar, R. Giri, and N. Mohan, "Active Input-Voltage and Load-Current Sharing in Input-Series and Output-Parallel Connected Modular DC-DC Converters Using Dynamic Input-Voltage Reference Scheme," *IEEE Trans. Power Electron.*, vol. 19, no. 6, pp. 1462–1473, 2004.

- [19] R. Burkart and J. W. Kolar, "Low-Complexity Analytical Approximation of Switching Frequency Harmonics of 3-Phase N-Level Voltage-Source PWM Converters," in *Proc. of the International Power Electronics Conference (IPEC)*, 2014.

- [20] K. Raggl, T. Nussbaumer, and J. Kolar, "Guideline for a Simplified Differential-Mode EMI Filter Design," *IEEE Trans. Ind. Electron.*, vol. 57, no. 3, pp. 1031–1040, 2010.

- [21] H. Ye, Z. Yang, J. Dai, C. Yan, X. Xin, and J. Ying, "Common-Mode Noise Modeling and Analysis of Dual Boost PFC Circuit," in *Proc. of* the 26th Annual International Telecommunications Energy Conference (INTELEC), pp. 575–582, 2004.

- [22] K. Raggl, T. Nussbaumer, and J. Kolar, "Model-Based Optimization of EMC Input Filters," in 11th Workshop on Control and Modeling for Power Electronics (COMPEL), pp. 1–6, 2008.