#### HARMONIC-FREE UTILITY/DC POWER CONDITIONING INTERFACES

by

#### MARTIN FREDERICK SCHLECHT

- S.B., Massachusetts Institute of Technology (EE 1977, ME 1977)

- S.M., Massachusetts Institute of Technology (1980)

- E.E., Massachusetts Institute of Technology (1980)

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

SEPTEMBER, 1982

© Massachusetts Institute of Technology 1982

Signature redacted

EECS Department, 7 September, 1982

Signature redacted

Certified by

Prof. John 'd. Kassakian, Thesis Supervisor

Signature redacted

Accepted by

MASSACHUSETTE INSTITUTE

OF TECHNOLOGY

OCT 20 1982

1 Archives

LIBRARIES

#### HARMONIC-FREE UTILITY/DC POWER CONDITIONING INTERFACES

bу

#### MARTIN FREDERICK SCHLECHT

Submitted to the Department of Electrical Engineering and Computer Science on 7 September, 1982 in partial fulfillment of the requirements for the degree of Doctor of Science.

#### ABSTRACT

The typical design of a power circuit now used to interface a de system to the electric utility is such that a heavily distorted current is drawn from the utility. The harmonic currents generated in this manner create harmonic voltages as they flow through the impedances of the utility's network. If the distortion of the utility's waveforms becomes great enough, it is possible that components of both the utility and the load will be adversely affected. Although such detrimental effects are not yet prevalent, there is concern that the rapidly growing number of power circuits connected to the utility will eventually cause intolerable levels of distortion to be reached. At some point, corrective measures will be needed.

This thesis proposes and develops one possible corrective measure: a utility/dc power conditioning interface that draws very little harmonic current from the utility system. Active waveshaping techniques are used to achieve this effect. The appropriateness and the applicability of this approach to the harmonic distortion problem of the future are first argued. The design and control of such an interface is then discussed. Finally, the power circuit's feasibility in the medium-power range is demonstrated with a 6 kW, harmonic-free rectifier.

Compared to the interfaces it is intended to replace, the harmonic-free utility/dc power conditioning interface presented in this work has a more complicated power circuit and control system. The added cost of this complexity is offset by several additional advantages that the harmonic-free interface offers, however. These advantages include 1)unity power factor operation at all power levels without compensating capacitors; 2)the reduction, by a factor of ten or more in some cases, of the peak energy storage required in the power circuit; and 3)a corresponding increase in the rate at which the power level can be changed.

Thesis Supervisor: Dr. John G. Kassakian

Title: Associate Professor of Electrical Engineering

I believe in the mentor/protégé relationship. Knowledge is an essential part of a person's being, and its transfer is therefore a very personal experience. True teachers exist to give a part of themselves to their pupils, and true pupils, in the search for growth, open themselves to their teachers. Both need the attention of the other; both profit from the exchange that takes place. It is, however, only through a close and lasting interaction between a teacher and a pupil that the two can fully realize the product of their efforts. Those fortunate enough to take part in such an interaction provide, to each other, a continual reminder of where they started, how they got where they are, and why it was important to do so. Of all that is to be taught and learned, none is as valuable as the perspective this reminder offers.

I have two mentors. One, my father, has taught me to aspire, to be productive, and to be discerning in my life. The other, Professor John Kassakian, has done the same for my view of my professional career. To both I owe a gratitude that can not be measured.

A true pupil, in turn, becomes a true teacher. I look forward to this role, and I hope that, as a mentor, I might begin to repay, in a somewhat indirect but very appropriate way, the debt I owe to those who have given me so much.

#### **ACKNOWLEDGEMENTS**

The members of my committee, Prof R.D. Thornton, Dr. A. Kusko, and Prof. G. Verghese, have provided knowledge, experience, support, and guidance throughout my years as a doctoral student. To them I owe a special appreciation for the contributions they have made. Prof. Verghese, in particular, has, due to his availability and his skill in fields for which I am only moderately trained, played an important role in the development and presentation of this work.

This research effort was sponsored, in part, by the Electric Energy Systems Division of the Department of Energy under the supervision of Mr. D.J. Roesler, Program Manager (Contract No. EX-76-A-01-2295 T.O. 47H).

# TABLE OF CONTENTS

| age                                        |

|--------------------------------------------|

| 7                                          |

| 10                                         |

| 11                                         |

| 14                                         |

| 16<br>19<br>22<br>24                       |

| 28                                         |

| 31<br>34<br>36                             |

| 39                                         |

| 40                                         |

| 43                                         |

| 58                                         |

| 68                                         |

| 73                                         |

| 77                                         |

| 78<br>87<br>97<br>115<br>120<br>126<br>128 |

|                                            |

|             |                                                          | <u>Page</u> |  |

|-------------|----------------------------------------------------------|-------------|--|

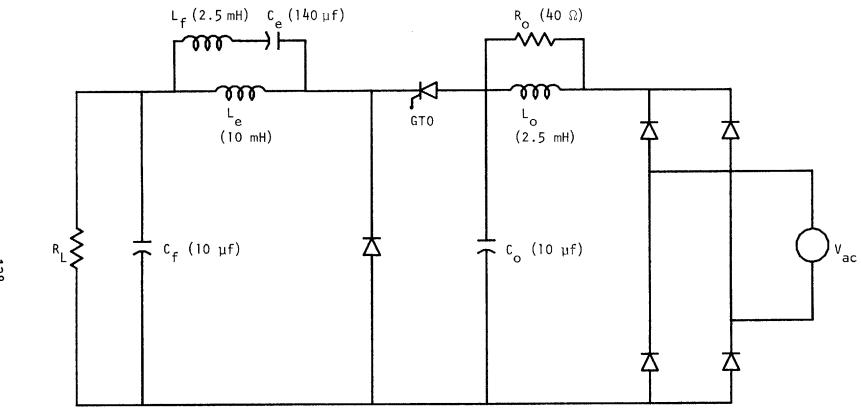

| Chapter VI  | A 6 kW Single-Phase Active Utility/DC Interface          | 136         |  |

|             | a. The Power Circuit                                     | 136         |  |

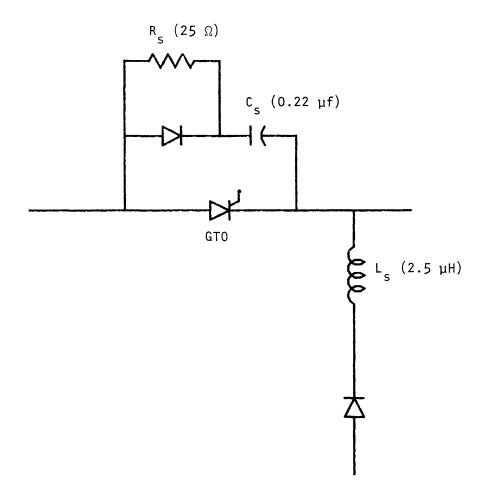

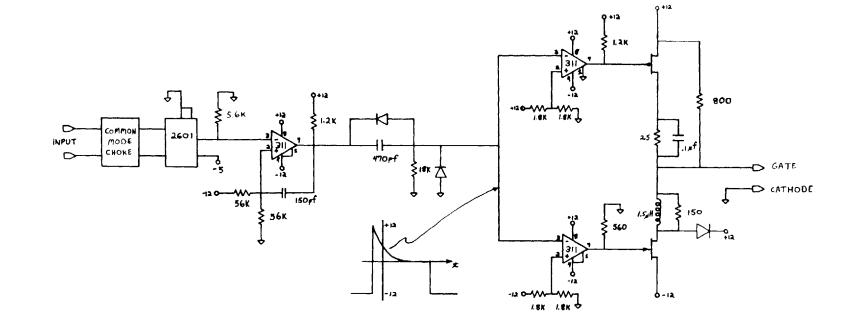

|             | b. The Gate Drive Circuit                                | 142         |  |

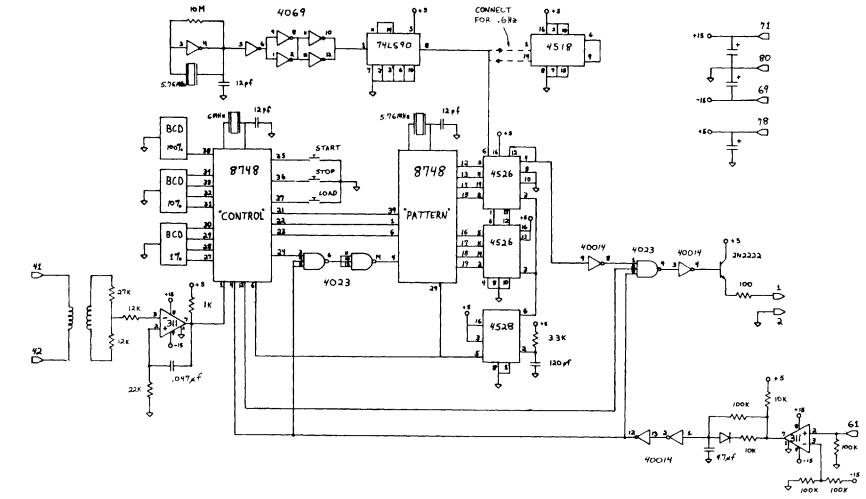

|             | c. The Control Circuit                                   | 147         |  |

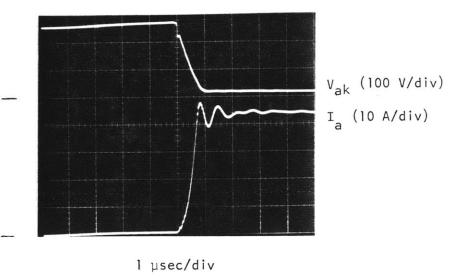

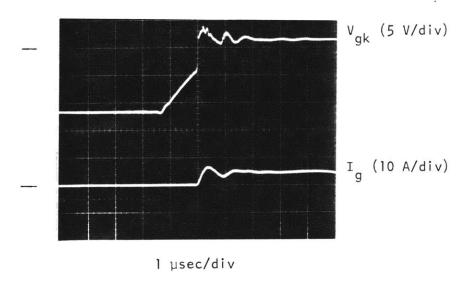

|             | d. GTO Switch Transistions                               | 152         |  |

|             | e. Interface Performance                                 | 152         |  |

| Chapter VII | Conclusions                                              | 171         |  |

| Appendix    | Software Programs for Control Circuit<br>Microprocessors | 175         |  |

| References  |                                                          | 202         |  |

# LIST OF FIGURES

| Figure |                                                                                              | Page       |

|--------|----------------------------------------------------------------------------------------------|------------|

| 4-1    | The Ideal Interface                                                                          | 42         |

| 4-2    | The General Waveform Transformer                                                             | 44         |

| 4-3    | The Waveform Transformer for a Two Quadrant DC System                                        | 46         |

| 4-4    | Waveform Transformer for a One Quadrant DC Current Source                                    | 48         |

| 4-5    | Waveform Transformer for a One Quadrant DC Voltage Source                                    | 49         |

| 4-6    | A Separated Waveform Transformer for a DC Current Source                                     | 51         |

| 4-7    | A Separated Waveform Transformer for a DC Voltage Source                                     | 51         |

| 4-8    | A One Quadrant Waveform Transformer Capable of a Transformation Factor Greater Than Unity    | 53         |

| 4-9    | A Two Quadrant Waveform Transformer Capable of a<br>Transformation Factor Greater Than Unity | 54         |

| 4-10   | A Separated Waveform Transformer with a 60 Hz Isolation<br>Transformer in the Bridge         | 56         |

| 4-11   | A Waveform Transformer with a High Frequency Isolation<br>Transformer                        | 57         |

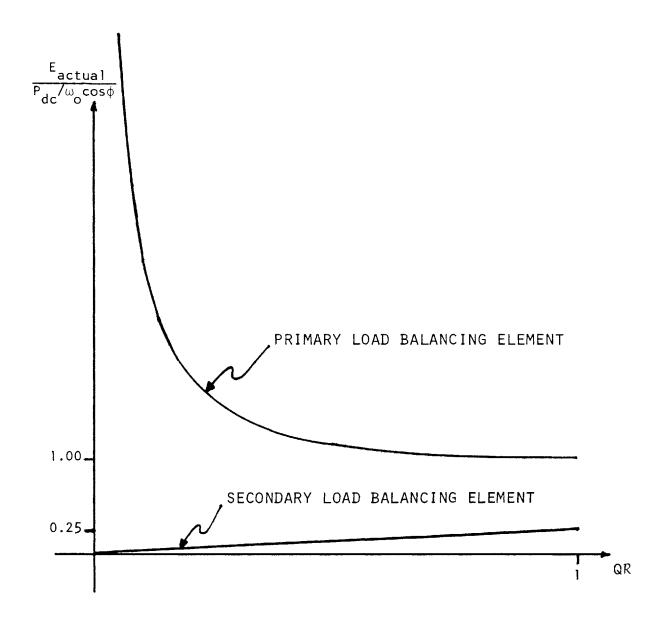

| 4-12   | Load Balancing Element Specifies DC Load Characteristic                                      | 61         |

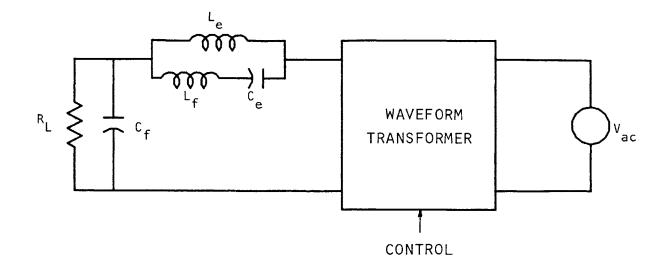

| 4-13   | Load Balancing with a 120 Hz Tuned Filter                                                    | 64         |

| 4-14   | Peak Energy Storage Requirements of the Load Balancing Elements                              | 66         |

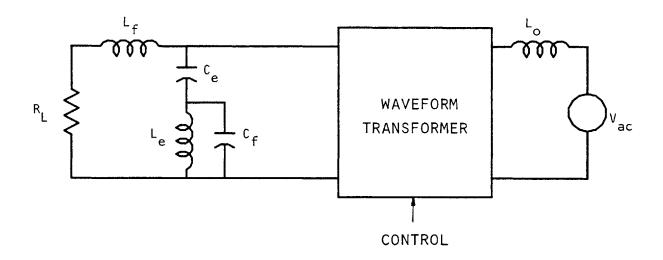

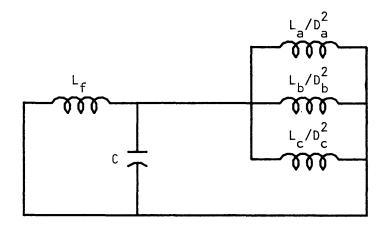

| 4-15   | High Frequency Filter for the DC System                                                      | 72         |

| 4-16   | Waveform Transformer for Three-Phase Bidirectional Power Flow                                | 74         |

| 4-17   | Ideal Interface for Three-Phase Unidirectional Power Flow                                    | <b>7</b> 5 |

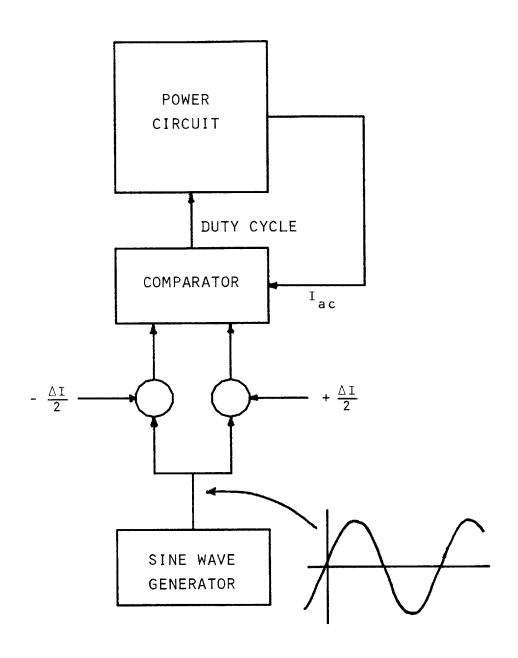

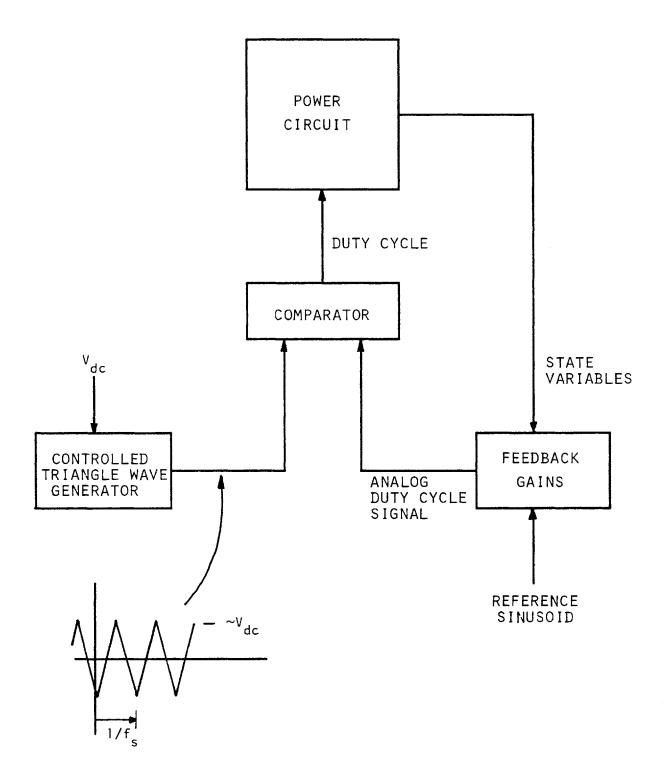

| 5-1    | Simple Control Circuit for Open-Loop Control Scheme                                          | 79         |

| 5-2    | Possible Positions for the Damping Resistor                                                  | 82         |

| 5-3    | Oscillations Caused by the AC Filter: Change of Damping                                      | 85         |

| 5-4    | Oscillations Caused by the AC Filter: Change of Characteristic Impedance                     | 86         |

| Figure       |                                                                         | Page |

|--------------|-------------------------------------------------------------------------|------|

| 5 <b>-</b> 5 | Synchronous Control Scheme                                              | 88   |

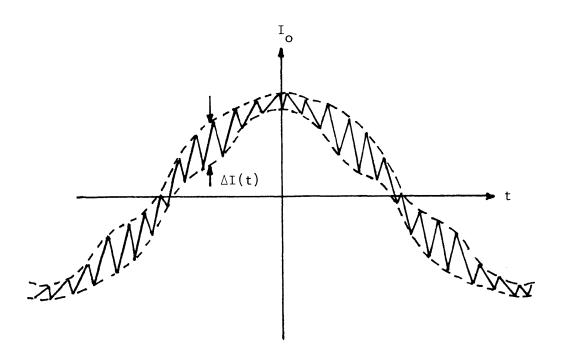

| 5-6          | Natural Oscillator Control Scheme                                       | 92   |

| 5-7          | Varied Width of Band gives Constant Switch Frequency                    | 94   |

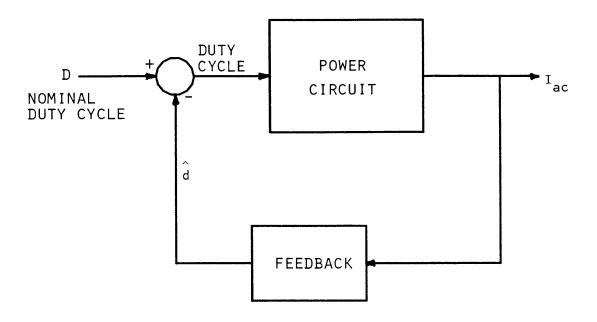

| 5-8          | Linear Control Scheme                                                   | 96   |

| 5 <b>-</b> 9 | Ideal Interface for One Quadrant DC Voltage Source                      | 99   |

| 5-10         | Ideal Interface with Third-Order AC Filter                              | 101  |

| 5-11         | Root Locus of Closed-Loop System Poles                                  | 103  |

| 5-12         | Ideal Interface Capable of Transformation Factors<br>Greater Than Unity | 105  |

| 5-13         | Root Locus of Closed-Loop System Poles                                  | 106  |

| 5-14         | High Frequency Filter on DC Side of Waveform Transformer                | 109  |

| 5-15         | Ideal Interface with DC Side High Frequency Filter                      | 110  |

| 5-16         | Root Locus of Closed-Loop System Poles                                  | 112  |

| 5-17         | Ideal Interface with Resistive Load for DC System                       | 114  |

| 5-18         | Control System for Minor-Loop/Major-Loop Feedback                       | 118  |

| 5-19         | Root Locus of Minor-Loop/Major-Loop Control System                      | 119  |

| 5-20         | Simulation Results Showing Oscillations in the AC Current               | 121  |

| 5-21         | Feedback Gains Inversely Proportional to $V_{\hbox{\scriptsize dc}}$    | 124  |

| 5-22         | Simulation Results Showing Performance of Time-Varying Feedback System  | 127  |

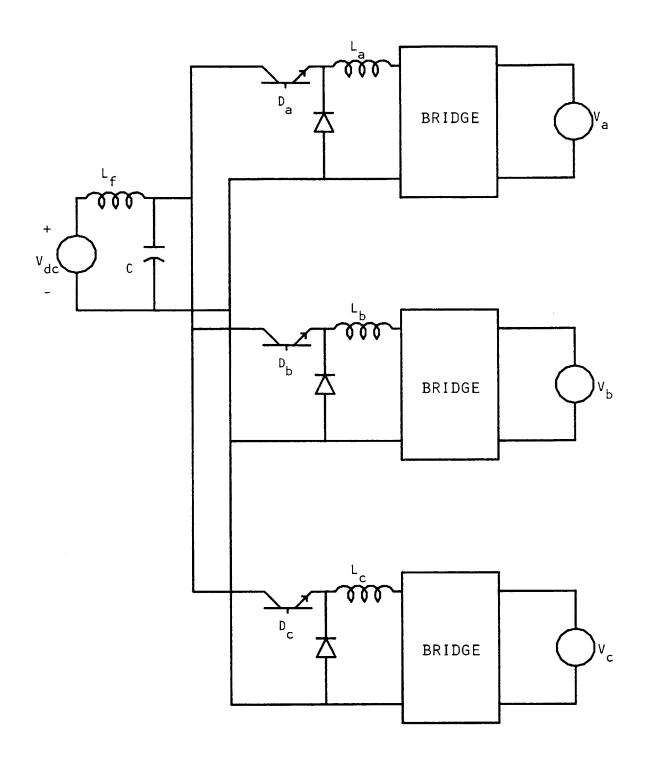

| 5-23         | A Three-Phase Ideal Interface                                           | 131  |

| 5-24         | Equivalent Circuit to Determine the A Matrix                            | 133  |

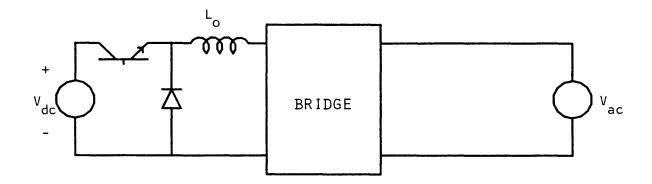

| 6-1          | A 6 kW Ideal Utility/DC Interface                                       | 137  |

| 6-2          | The Power Circuit                                                       | 138  |

| 6-3          | The Turn-On and Turn-Off Snubbers                                       | 143  |

| 6-4          | The Gate Drive Circuit                                                  | 144  |

| <u>Figure</u> |                                                         | Page |

|---------------|---------------------------------------------------------|------|

| 6 <b>-</b> 5  | The Control Circuit                                     | 148  |

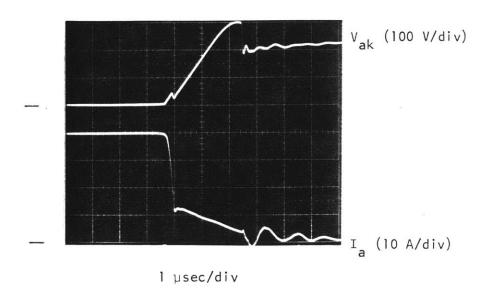

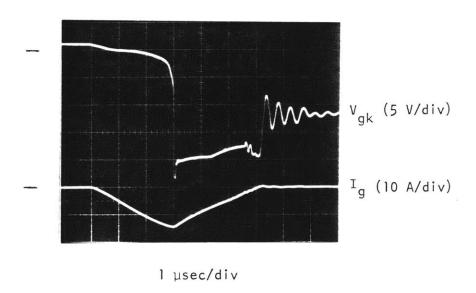

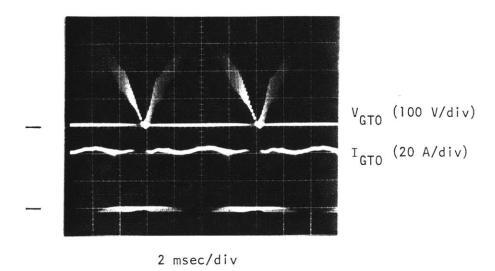

| 6-6           | GTO Turn-On Transition                                  | 153  |

| 6-7           | GTO Turn-Off Transition                                 | 154  |

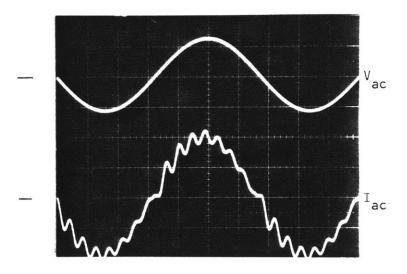

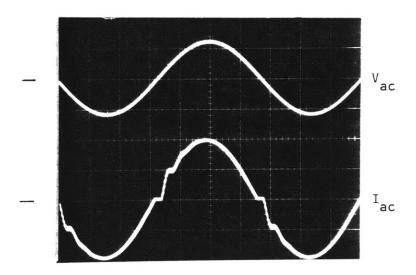

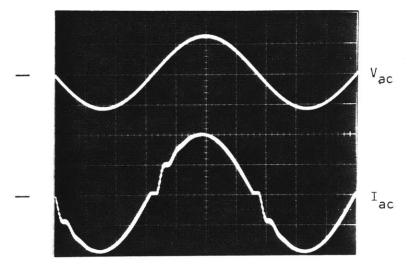

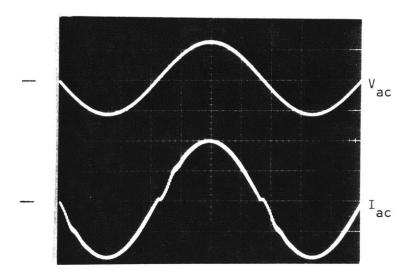

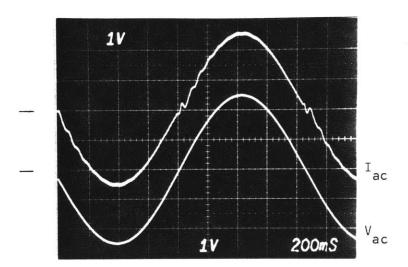

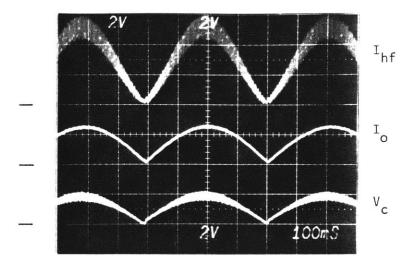

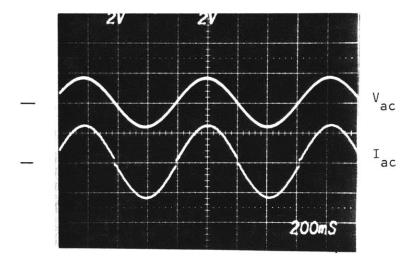

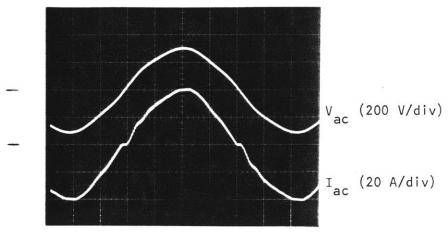

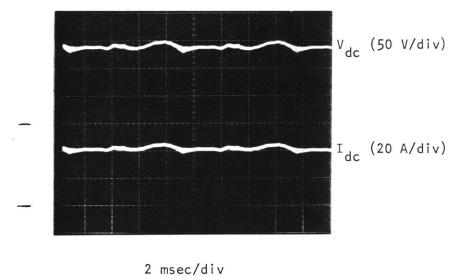

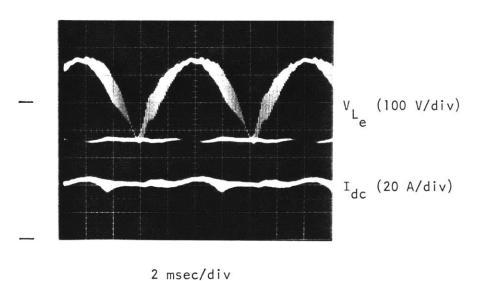

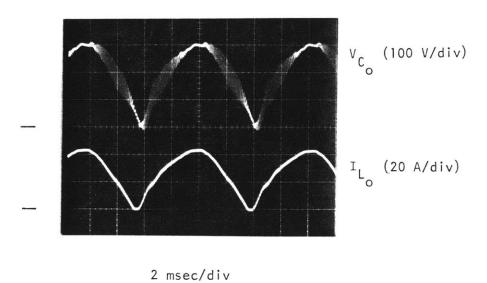

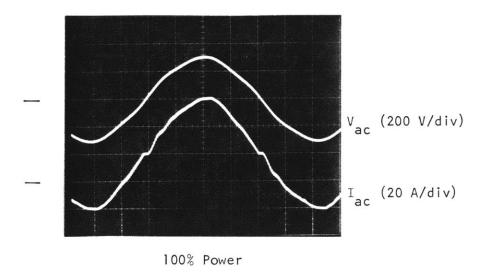

| 6-8           | Waveforms Showing Full Power Operation                  | 155  |

| 6-9           | Effect On Utility Voltage Waveform                      | 159  |

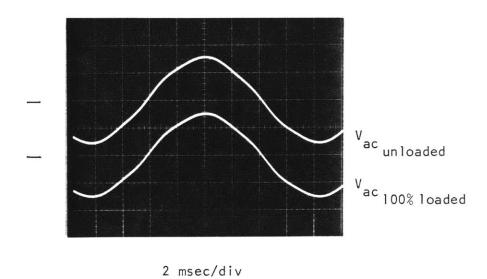

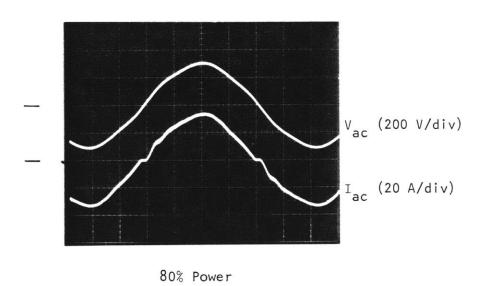

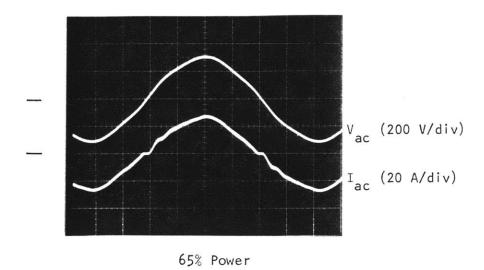

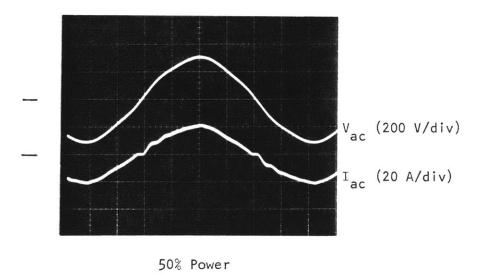

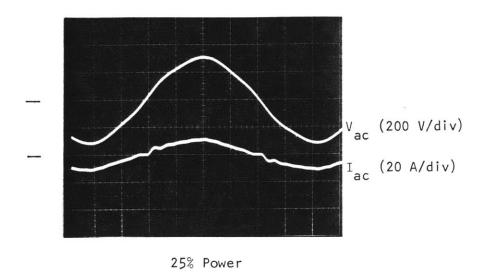

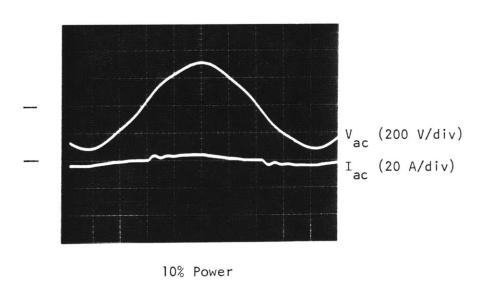

| 6-10          | Waveforms Comparing Operation at Different Power Levels | 160  |

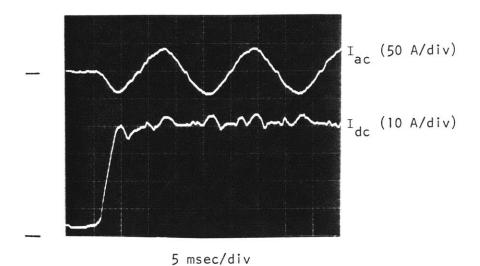

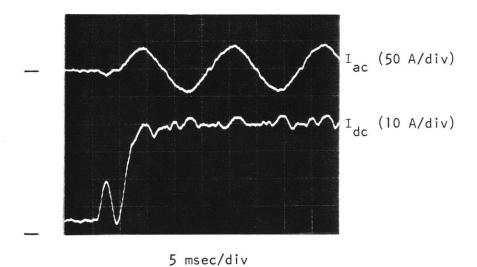

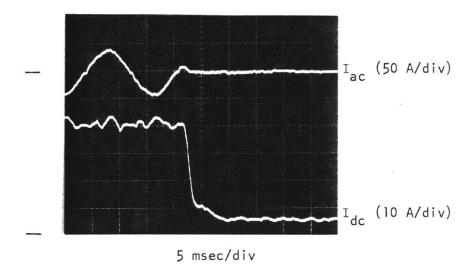

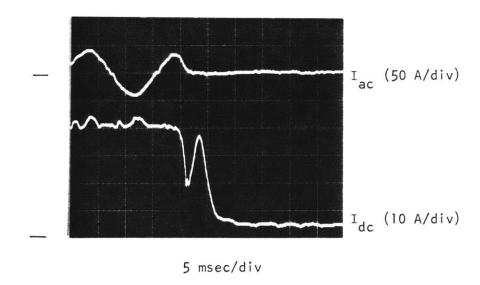

| 6-11          | Response to a Large Step Change in Power Level          | 164  |

# LIST OF TABLES

| <u>Table</u> |                                                   | Page |

|--------------|---------------------------------------------------|------|

| 6-1          | The Twelve Table Entries in the Pattern Processor | 166  |

| 6-2          | The Harmonic Content of the AC Current            | 167  |

| 6-3          | AC Current Distortion for Various Power Levels    | 168  |

| 6-4          | DC Current Ripple for Various Power Levels        | 169  |

| 6-5          | Power Circuit Efficiency at Various Power Levels  | 170  |

#### CHAPTER I

#### INTRODUCTION

The electric utility system is designed to provide a fundamental sinusoidal voltage waveform to linear loads that will, when so driven, draw fundamental sinusoidal currents. Under these conditions, the quality of the system's service can be controlled quite well. Not all of the system's loads are linear, however; some, when driven by a single frequency voltage, draw a current that is distorted. The harmonic currents created in this manner flow through the branches of the system's network and distort the voltage waveform that the utility delivers to its customers. This distortion degrades the performance of both the system and its load. Excessive dissipation, interference with communication and control signals, and overstressing of components are examples of the detrimental effects that can occur.

Motors and transformers are the original sources of harmonic distortion. Compared to their fundamental component, however, the percentage of harmonic currents these loads draw from the utility is small, and they have therefore seldomly caused serious distortion related problems. Installations of electronic power conditioning circuits, on the other hand, present a much more nonlinear load to the utility. The process by which these circuits change the utility's sinusoidal waveforms into those special waveforms required by their loads can also cause the current drawn from the utility to be substantially distorted.

Although power circuits are now only a small fraction of the

system's total load, there is great potential for their number and total power rating to grow. As this growth proceeds, the level of distortion in the utility will increase, and there is great concern that intolerable harm will result.

The analogy between the distortion of the utility and the pollution of an environmental system is often made. It is not completely correct. The purpose of the electric utility is to provide power, not pure fundamental waveforms. Its ability to do so is impaired by many of its loads. Some require a widely varying level of power, some are highly reactive, and now, with the advent of power conditioning, some draw substantial harmonic currents. All such loads degrade the operation of the system. Each must be accommodated, but none should be considered foreign.

The reference to pollution does have some proper connotations, however. We are in the beginning stages of what must be projected as a rapid growth of conditioned load. Although distortion related problems are relatively minor now, experience has shown that such growth will ultimately cause serious problems if no corrective actions are taken. The best time to investigate and propose solutions is certainly now, but much of what must be known to do so is elusive. As with other pollution problems, the interactions are complex, the important parameters are continually changing, and the situation of the future is difficult to predict. The questions grow more rapidly than the answers, and every corrective action found to be optimal in some respect is also found to have unlimited exceptions to its use.

The search for a solution must be more focused. The intangibles

must be set aside and the dilemmas must be resolved as well as is possible with our current understanding. As efforts are then devoted to more well defined goals, the knowledge and skills that can be brought to bear will be much more likely to reach a satisfactory solution to the harmonic distortion problem of the future.

This thesis proposes, and begins the effort of reaching, one possible goal: the development of a utility/dc power conditioning interface that draws very little harmonic current from the utility system. Active waveshaping techniques are used to achieve this effect.

The organization of this work is as follows. The first two chapters develop the goal. The salient issues of the harmonic distortion problem are discussed and the appropriateness of a specific solution, an ideal power conditioning interface, is argued. The second two chapters present the design of such an interface. One covers the circuit's topological aspects, the other discusses the issues of control. These are then followed by a chapter that presents the design and actual performance of a 6 kW ideal interface.

Nowhere in this work are all the details of all the aspects of the harmonic distortion issue discussed. If such an understanding is desired, a study of the literature will have to be made. To facilitate such a study, an extensive list of the papers published on the subject over the last several decades has been provided.

#### CHAPTER II

#### THE HARMONIC DISTORTION PROBLEM

Harmonic distortion threatens the quality of our electric utility service. This is not to say that distorted waveforms in the system are a recent development: motors and transformers have been present from the beginning and the first power conditioned loads were attached to the utility over fifty years ago. Nor does it mean that a distortion-free service would be sufficient: there are many other anomalies within the system and its load that make the utility's performance less than ideal. The threat is not even that distortion is the system's most undesirable problem, but rather that it is a growing one. Many of the difficulties faced by the utility will continue to be the same as they have always been. They can be handled with well understood and well practiced methods. Both the magnitude and character of the harmonic distortion problem are undergoing a significant change, however. The potential for harm due to this change is great.

The technical community is aware that a solution is needed and has begun the search. Many papers have been published in the last ten years. Some provide detailed analytical work or empirical results that improve our understanding of the magnitude of the problem. Most offer educational overviews that attempt to define and specify various aspects of the harmonic distortion issue. Technical organizations have set up committees to investigate the problem and suggest solutions. Government agencies have supported studies by industrial and academic institutions. Utility companies are developing the tools and awareness needed to

assess the present status of the problem. The work has only begun, however; there are still many uncertainties. A clearly defined policy has yet to be developed.

It is both the rapid growth and the changing character of the sources of harmonic current that impede the development of a clear and workable solution. Our present ability to solve distortion problems is based on features that will eventually be less prevalent. For example, the ability to relate a source of harmonic currents to its corresponding detrimental effects will diminish. The control over an installation of conditioned load will decrease. The development of a specific solution for a specific situation will be harder to achieve.

Unfortunately, while the features of the utility's future conditioned load make the straightforward corrective procedures of the past unusable, they do not readily indicate what should be done instead. To find solutions that are well suited to the coming situation, it is first necessary to know where our efforts should be directed. This, in turn, requires that we understand the nature of the change that is taking place.

The following sections of this chapter will help develop this understanding. The first will present the harmonic distortion problem as it now exists and the second will describe how conditioned load is changing. These will then be followed by a discussion of the difficulties caused by the change and a review of the technical community's reaction to these difficulties.

# II.a The Harmonic Distortion Problem Up To Now

Even though the number of power conditioned loads has steadily grown over the last several decades, the salient features of the harmonic distortion problem have changed very little. The difficulties we now experience and the solutions we impose are therefore much the same as they have always been. There are simply more occurrences.

Perhaps the most important feature of the harmonic issue today is the negligible level of distortion in most of the power system. We have not had to face a situation where harmonic problems occur throughout the system, from the lowest sector of the load to the generators. The total amount of conditioned load is not yet great enough to cause such an affect. Instead, the problems that do arise are isolated instances. Not every power circuit creates an intolerable situation, and those that do can be dealt with individually.

The problems we currently experience are caused by power circuits that condition high levels of power for heavy industrial loads. [19,20] Because the level of distortion created by these circuits decreases with distance through the network, the extent of the affected area is usually limited. Most harmonic currents are shunted at the first regulation capacitor; only the lowest frequency components continue to flow deeper into the network. Since much of the impedance seen by the power circuit is the result of nearby feeders and transformers, the extent of the voltage distortion is also limited to the locality. There are, in essence, islands of distortion within a network that is free of distortion. [18,106,111]

Because the distorted areas are limited in size, when harmonic problems are recognized, the offending sources are easy to locate. First, there are normally several complaints that help define the problem area. Second, due to the industrial nature of high-power conditioned load, there are only certain types, and usually small numbers, of facilities where the power circuit could be. Finally, once the potential offenders are located, it is often possible to turn each power circuit off to determine its contribution to the detrimental effects observed.

Once a harmonic related problem is recognized and the source of the distortion has been found, certain well defined steps can be taken. One is to use either phase-multiplication techniques or passive filters to limit the amount of injected harmonic current to acceptable levels. Another is to connect the power circuit directly to a higher power level, and therefore lower impedance, branch of the network to reduce the voltage distortion produced by the harmonic currents. Yet a third is to use either separate electric services or intervening filters to isolate the sensitive load from the distorted waveforms.

Each of these solutions has been applied in many high-power situations; each is well analyzed and documented. [8,16,17] There are difficulties and disadvantages associated with their implementation, but they are all capable of reaching the desired goal. The problem is really only a matter of deciding to what extent the corrective measures should be taken. To either over- or under-correct can waste material and effort.

A major portion of the research done to this day is directed

towards facilitating decisions about corrective measures. Modeling and analysis tools have been developed to predict the levels of distortion that will occur in a given situation. [4,194,196,197] Some are more sophisticated than others, but they all can determine the consequence of a small number of conditioned loads in a limited section of the system's network. Experiments have been conducted to relate the level of harm experienced by many typical loads to the magnitude and frequency spectrum of the distortion to which they are subjected. [68,79,92,99] Measurement tools have been developed to determine what levels of distortion already exist. [159,164] Whenever all these sources of information fail to be adequate, the existing wealth of experience in similar situations can often give a very good indication of what should be done.

Fortunately, the very nature of high-power conditioned load lends itself, in several ways, to the control of harmonic distortion. First, the cost and importance of the power circuit are great enough to cover the expense of a special engineering effort devoted to each particular case. Second, both the designer and the purchaser of the power circuit are very aware of the consequences of the installation. They know that the distortion can cause problems and that the greatest detrimental effects are likely to be experienced by the load within the same facility. They are anxious to avoid these problems and are willing to incorporate corrective measures from the beginning. Finally, whenever the problems are not handled by those who own the power circuit, the utility often has the ability, due to the industrial nature of the load, to exercise considerable control. The situation is quite different,

however, for low- and medium-power loads, as will be discussed next.

#### II.b How Conditioned Load Is Changing

There are several rapidly growing technologies that will increase the number, variety, and total power rating of conditioned load connected to the utility. One is the electronic industry. The number of electronic circuits we need and can afford is undergoing a tremendous growth. Although it is usually a secondary issue to both the designer and the user, each of these circuits will require a power conditioning interface with the utility. Other technologies that depend on power conditioning in a more direct way are also developing. Solar-photovoltaic installations will need utility interfaced converters for load balancing. Electric vehicles will need battery chargers. Automated assembly lines will need controllable and efficient motor drives.

The power electronic technology is keeping pace with these advancing technologies. A growing group of power electronic engineers is developing more sophisticated circuit topologies and control techniques. Better semiconductor devices continue to become more readily available at lower prices, and passive energy storage components have been improved. New fabrication techniques that make the production of power circuits easier are also available. The results of these developments are that a power circuit is now cheaper, lighter, smaller, more efficient, and more reliable than had previously been possible. These improvements are so substantial that they are, themselves, largely

responsible for the feasibility, and therefore rapid growth, of conditioned load.

The combined technological advancements are doing more than increasing the system's conditioned load, however; they are changing its character. Low-power loads that could once be neglected will become so numerous that they will begin to have an important combined effect. An emerging group of conditioned loads in the medium-power range will also be a new source of considerable concern. High-power loads will always retain their significant impact, simply because their power ratings are so substantial, but the time when all other loads could be completely ignored will come to an end.

Low- and medium-power conditioned loads have features that are distinctly different than those of high-power loads. It is, in fact, these differences, rather than the actual level of power flow, that distinguish the three classifications. These differences, described below, are the reason it is so difficult to know how to handle the harmonic distortion problems that can be expected in the future.

High-power conditioned loads are typified by the three-phase converters used for industrial processes, motor drives, and HVDC links. They are few in number but represent dominant fractions of the load in their locality. As discussed in the last section, they are individually designed and installed at specific sites. The percentage of distortion in the current they draw from the utility is small relative to that of low-power conditioned loads, but the impact that a single power circuit can have on the system and the local load is more significant. The extent of the harmonic related problems may vary from one situation to

the next, but each implementation of high-power conditioned load has the potential to produce major detrimental effects.

Low-power conditioned loads are exemplified by small computers, laboratory instruments, communication equipment, and home appliances. In contrast to high-power loads, they are connected to a single phase of the utility. The amount of distortion in their ac current waveform is very high; total harmonic distortion levels of 70% or more are common. They are mass-produced and widely distributed throughout the system. No single low-power conditioned load distorts the system to an appreciable level; they demand attention only as a collective group.

Medium-power conditioned loads require power in the 1 to 100 kW range, a level previously reserved for circuits designed along the lines of the high-power installations. Examples of such loads include motor drives, battery chargers, uninterruptable power supplies, and line-interfaced inverters. The technological advancements described above have created a need for, and the ability to provide, power circuits that can handle this level of power and still retain many of the attributes of low-power load. They are mass-produced and have the potential to be very numerous. They will be widely distributed throughout the residential, commercial, and light-industrial sectors of the system and will often operate from a single-phase service. Unlike low-power loads, however, each medium-power conditioned load has the capability of creating substantial levels of distortion on its own. As a group, they have great potential to cause harm.

# II.c The Difficulties Caused By This Change

If the amount of conditioned load were simply growing, the level of concern would not be as great as it is. Even as more high-power conditioned loads were installed, the corrective procedures that have always been used would be able to handle the problems that arose. The increased experience would even improve the skill with which the problems were solved. But the growth is bringing about a shift toward the low- and medium-power conditioned loads. These loads, by their distinct nature, present difficulties that are not well suited to the established methods of solution.

The mass-produced feature of the new conditioned loads will eliminate the close relationship between the designer and the user of a power circuit. The designer will know nothing about the installation site and will have no details about the topology and the impedance of the local network, or about the number and kind of sensitive loads that will be affected by the power circuit. Without this information, designers can not modify their circuits for each particular application. Designs must work satisfactorily in all situations, no matter where they are connected to the utility, no matter how many other power circuits are in the locality, and no matter how sensitive the local load is.

The users of the mass-produced conditioned loads are similarly distant from the details of the interfaces that are being installed. Customers no longer play an active role in specifying the power circuit's performance, but simply buy what is available. Their concerns are primarily with the requirements of the load and they may even be unaware of the problems that distortion can cause. Because they will

not normally have the expertise necessary to make decisions about what is installed, they can not be expected to play a role in the control of the electric system's distortion level.

The widely distributed nature of the new conditioned loads causes its own difficulties. One is that it will no longer be easy to locate, or even define, the significant sources of harmonic distortion. There will be too many of them, connected to every sector of the system's network, to allow any one power circuit's contribution to be separated from the others. All will be responsible for the detrimental effects to one degree or another. Corrective procedures cannot be brought to bear on any individual power circuit; they must be applied to the entire class of conditioned load instead.

A related consequence of the dispersed nature of the installation sites is the utility's inability to know where, and how many, power conditioned loads are connected to the network. The typical owners of low- and medium-power loads do not consume power at a level that allows the utility to justify close monitoring. But without such monitoring, the utility will not be able to exert control over the harmonic current sources once they have been installed.

The reduction from three-phase to single-phase operation is a third, and important, feature of the new conditioned loads. With only one phase to work from, phase multiplication techniques that can substantially reduce the harmonic content of the ac current are no longer possible. Harmonic reduction must be achieved in more complicated and expensive ways. For those power circuits that provide an interface to a dc system, single-phase operation also requires larger

dc side filter elements than would be needed in a three-phase power circuit. The added expense of these larger components consumes resources that might otherwise be applied toward the shaping of the ac current waveform.

# II.d The Reaction to the Changing Situation

The response to the evolving harmonic distortion issue is occurring on two levels. The first is the growing awareness that distortion is a problem and the development of more conservative attitudes toward the pollution of the utility system. The second is the direct effort to deal with exactly those difficulties that the changing character of conditioned load is introducing.

Harmonic distortion has become a much more familiar phenomenon than it used to be. Both the user and the manufacturer of sensitive loads such as computers and communication equipment are now aware of the harm that a distorted utility can cause. The customer is concerned when a conditioned load is installed nearby; the manufacturer realizes that efforts must be made to reduce the sensitivity of a product.

The manufacturers of conditioned loads are also beginning to understand that corrective efforts on their part are advantageous. Those who produce power circuits to control lights, heating, and electric motors are already installing filters in their products to remove the most damaging harmonic components from the ac current. This action is in direct response to the desires of the market place and is otherwise voluntary.

The change in attitude by all concerned does not solve the harmonic

distortion problem of the future, but it does affect the type of solutions that can be feasibly implemented. The more the problem is recognized and the more a solution is felt to be needed, the easier it is to propose corrective measures that require substantial cooperation.

There is not yet a direct answer to what those measures should be, however. Several concepts related to the character of the future harmonic distortion problem have been introduced by the technical community. Ideas such a stochastic cancellation of harmonic currents, centralized filters, and active harmonic filters are examples of what is being discussed. [122,154,155,156] These ideas have prompted interesting work, but they have not led to the formulation of a policy.

Instead, the most direct and prominent response to the emergence of low- and medium-power conditioned loads is the proposal of a limit for the level of distortion that will be allowed to exist in the utility's voltage waveform. The power system's voltage must already meet certain amplitude and frequency requirements; the addition of a harmonic distortion level regulation seems consistent and is widely discussed. [8,113,116] Such a standard does not always represent the optimal way to solve the distortion problem, but it does provide a specific goal toward which both the designer of the power circuit and the manufacturer of a sensitive component can work. With this goal, they should be able to come to well defined decisions about how their products must be designed.

The European governments proposed standards nearly ten years ago.

Their major concern was for the unrestricted trade of household appliances from one country to another. They wanted to provide

manufacturers the guarantee that their products would be accepted by other countries as long as they met the standards proposed. The allowable levels of distortion set in the regulation were low (5% THD of the voltage waveform) and subject to future change. [114]

These formal standards are most significant for the precedents they have set. The ideas that there should be regulation, that the standards should be based on the total harmonic distortion of the voltage waveform, and that the allowable level should be around 5% are often suggested.

The United States government has approached the harmonic distortion issue in a different manner. Regulation, although discussed, has not yet been seriously proposed. Instead, over the past five years the government has been heavily involved in the development of the new technologies most relevant to the growth of medium-power load: photovoltaic and wind powered energy generation, fuel cells for load balancing, and electric vehicles. Since the development of the required power circuits was an integral part of each program, the government has been able to direct research efforts into the harmonic distortion area. Several studies have been sponsored to determine what level of distortion is acceptable, what levels exist, and what levels can be expected as their programs reach the implementation stage. This is not to say that regulations have been ruled out in the United States. There is just a realization that time and resources are available to become more sure about what those regulations should be.

Whether or not regulation is the best, or even an appropriate, approach to the harmonic distortion problem of the future is still

unknown, however. Although it seems to provide a well defined solution, it also raises many questions that have not yet been answered. Some of these questions will be discussed in the next chapter.

#### CHAPTER III

## THE IDEAL UTILITY/DC INTERFACE: A VIABLE APPROACH FOR THE FUTURE

The specification of a standard for the harmonic content in the utility's voltage waveform is not intended as a solution to the future distortion problem. It is simply a declaration of what distortion level is tolerable. Unlike the management of the voltage's fundamental amplitude or frequency, however, the utility has very little means to control the distortion that exists in its waveform. If a single conditioned load were responsible for the intolerable level of voltage distortion, it might be possible for the utility to implement corrective procedures. But when the excessive level of distortion is reached only through the combined contributions of many conditioned loads, there is very little the utility can feasibly do.

For this reason, when harmonic standards are either contemplated or proposed, they are usually meant as restrictions on conditioned load rather than as requirements for the utility industry to meet. Presumably, only those loads that satisfy the requirements of the standards would be allowed to connect to the utility.

The standards proposed by the European agencies allow any single conditioned load to distort the system's voltage up to the limits specified. [114] The conditioned load under test is to be connected to a standard network consisting of a stiff voltage source and a representative impedance. As long as the harmonic components in the voltage at the terminals of the load remain within the regulated levels, the appliance is approved.

The problem with this approach is that it treats each source of harmonic current separately, with no regard for the contribution of the others. For the distortion problems of the past, where isolated high-power conditioned loads were the only concern, this policy would have been valid. But for the problems of the future, where many low- and medium-power conditioned loads combine to create harmful levels of distortion, the approach is inappropriate. For example, if the first electric vehicle battery charger in a residential area were allowed to create the maximum harmonic voltage levels, subsequent installations of the same power circuit would cause the levels to be exceeded. A regulation policy where individual power circuits are each allowed to cause the maximum tolerable voltage distortion can not escape this problem.

An alternate policy might be to restrict the amount of harmonic current each conditioned load could draw from the utility, regardless of the voltage that this level of current would cause. The point of this approach would be to anticipate the combined contributions of many conditioned loads and to control each such that voltage distortion they created as a group would remain within the levels that were acceptable. Such an approach would require not only that an acceptable level of voltage distortion be determined, but also that the total amount of harmonic current that would, for a typical network, give rise to this level be calculated. It would then be necessary to assign a limit, perhaps based on a per unit rating, to the harmonic currents each load could contribute.

While this approach might avoid the problems faced by the control-

of-harmonic-voltage approach, it does require a great deal of knowledge about the situation of the future. The question of how low the current limits must be set to guarantee that the acceptable level of voltage distortion will never be exceeded is difficult to answer. Too much depends on how many conditioned loads there are. Even if the growth of power conditioning installations could be reasonably predicted, situations where conditioned loads are much more concentrated than the average would suggest will always occur.

The true problem with both regulation policies is that, in declaring what threshold of distortion is tolerable, they suggest that it is not necessary to do still better. If, in response to such standards, the currently used power circuits that draw very distorted currents are to be replaced with circuits designed to draw less harmonic currents, a considerable effort will be required to do so. The emphasis of this effort should be more than the attainment of specified levels; the work should be devoted to reducing the harmonic currents as much as possible.

Rather than meeting unavoidably arbitrary standards, the goal should be to make the power circuit an ideal interface, a two port element that would condition power without allowing either the character of the power circuit or the nature of the system at one port to be imposed upon the system at the other. Such an interface, if feasible for the low- and medium-power conditioned loads, would be well suited to exactly those difficulties that the loads in these power ranges have introduced.

In the next section of this chapter, the arguments for and against

the ideal interface as a solution to the harmonic distortion problem of the future are discussed. These are then followed by a presentation of some basic issues on how the interface might be designed.

## III.a Arguments For and Against the Ideal Interface

The ideal interface is an appropriate way to deal with the widely distributed and diverse nature of the future conditioned load. All other approaches, whether they emphasize regulation of the harmonic current sources, alteration of the network impedance, or isolation of sensitive components, depend strongly on the number, power rating, and location of the conditioned load. These features of the load are hard to discern and are constantly changing. To be effective, the alternative approaches must either foresee all possible situations or be continually updated. Both tasks are difficult to accomplish. The ideal interface, in comparison, is a solution that does not depend on factors that are uncontrollable. Instead, it is a solution that always works, no matter where and how much conditioned load there might be.

The ideal interface also deals effectively with the problems caused by the mass-produced nature of low- and medium-power conditioned load. Because the power circuit's performance is not dependent on the character of the system's network, the designer does not need to know the details of the installation site. The purchaser is similarly free from concern, and does not need to be aware of potential problems, or to recognize actual detrimental effects, or to understand the details of corrective measures. Sensitive components located near the power circuit will not be adversely affected, no matter how many or what type

they are.

In essence, the ideal interface avoids all those problems that made the low- and medium-power conditioned load difficult to handle. There are no questions about what level of distortion is tolerable, what effect the distribution system will have, how and when corrective measures should be implemented, or how long the solution will remain satisfactory. These intangible aspects of the future harmonic distortion problem could never be adequately addressed. The ideal interface approach bypasses them and forces efforts to be focused on a fixed point: the power circuit. The problem and the goal therefore become well specified. This feature is, in itself, an important virtue of the ideal interface approach.

That the ideal interface is a permanent solution is also important. The power circuit, once developed, will benefit from the lack of need to change. Components intended specifically for the ideal interface can be produced. The design and the manufacturing process can be finely tuned. The market will require large numbers of identical units. As all these features help reduce the cost of the ideal interface, its feasibility will become much greater than the initial costs would suggest.

The cost of the ideal interface may be further offset by additional beneficial features that its design provides. As the next two chapters will show, the ideal interface is capable of presenting a unity power factor load to the utility; no compensation capacitors are needed. The ideal interface also requires far less energy storage within the power circuit than is possible with today's typical circuit designs. Besides reducing size, weight, and cost, this lower energy requirement allows a

much faster control of the power that is delivered to the load. All these features are useful and help to reduce the overall cost of the power circuit. The marginal cost that must be associated with the reduction of harmonic currents is therefore not as great as it would otherwise be.

Finally, it is appropriate that the ideal interface approach is a solution that requires the cause of the distortion to bear the cost of its correction. The designers of power circuits have long considered it necessary to provide their load with clean waveforms; their view of the utility system should adopt this same consideration.

There are shortcomings and limitations to the ideal interface approach. The following paragraphs discuss some of these points.

One argument against the ideal interface is that it is an extreme solution. It may be much more of an effort than is required. The rate at which conditioned load will grow is not certain. Many power circuits installed at any time in the near future may not remain in service long enough to take part in a combined contribution of significant harmonic distortion. There will always be situations where the extreme efforts required to obtain negligible harmonic distortion levels are not needed. But if the use of an ideal interface is left to choice, much of the value of the approach will be lost.

The ideal interface approach also forces a conservative, rather than an optimal, solution. No advantage is taken of natural cancellation between conditioned loads. Centralized solutions that exhibit economies of scale are not followed. There is no selective reduction of harmonic components based on the actual detrimental effects

observed. Corrective measures are always taken at the power level; a solution at the signal level, as might be possible in communication equipment for example, is no longer considered. The cost associated with the loss of an optimal solution can never be determined, but it should be recognized.

Finally, there is a technological limit to the ideal interface. The level of power that can be reached while maintaining an acceptably low level of distortion has an upper limit. This limit will improve with technological advancements, but it will never be possible to provide an ideal interface for all conditioned loads.

## III.b How to Obtain an Ideal Interface

Most applications of power conditioning circuits involve the transfer of energy between the utility and a dc load or source. Even when the load requires alternating waveforms, a dc link is often provided to separate the utility interface function from the inversion function. For this reason, the ideal interfaces developed in this and the following chapters will be dedicated to utility/dc power conversion.

The power circuits currently used to provide an interface between the utility and a dc system are able to meet the requirements of their dc systems quite well. It is the shaping of the ac current waveform into a fundamental sinusoid that is needed to make the power circuit an ideal interface.

One way to achieve the sinusoidal current waveform is to use passive waveshaping techniques. In this approach, the semiconductor devices of the power circuit perform only very basic functions: they

provide rectification and control of power level. Passive filters are then used to remove the unwanted components from the waveforms of both the ac and dc systems.

To remove the harmonic components from the ac current waveform, a collection of tuned shunt filters is commonly used for the lower frequencies. A damped low-pass filter is then provided to take care of the remaining components. Finally, to increase the impedance against which the tuned filters can work, an inductor is usually placed in series with the utility. For a given filter, the larger this series inductor, the more effective the tuned filters will be. No passive filter is completely effective, however. The better job of waveshaping the filter must do, the larger, more complicated, and expensive it will be.

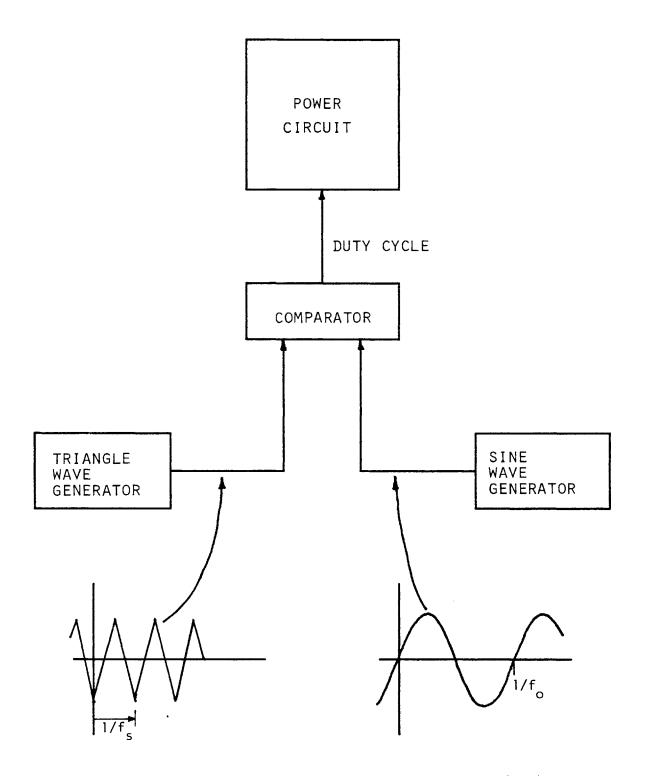

The other way to shape the ac current waveform is to use active waveshaping techniques. In this approach, the number of switch transitions per cycle is increased above the minimum level required. This increase can be accomplished by either the use of a few switches operated at a high frequency or the use of many switches, each of which is operated at a correspondingly lower frequency. By properly placing the switch transistions throughout the cycle, certain harmonic components can be removed from the ac current waveform. The more switch transitions there are, the more harmonic components that can be eliminated. Whatever components are left in the ac current waveform will be at high frequencies and can be easily removed with a simple and small low-pass filter.

The two approaches can be combined to any degree desired. The more

one approach accomplishes, the less the other must do.

### III.c Active vs. Passive Waveshaping

Each waveshaping technique has its advantanges and disadvantages. The passive approach is the one that has been traditionally used, simply because the available semiconductor devices have not been suitable for any active waveshaping technique beyond phase multiplication. This condition no longer exists for the low- and medium-power conditioned loads, however. As devices capable of high frequency operation become more readily available in these power ranges, the feasibility of the active waveshaping approach is improving. Compared to the fixed limitations of the passive waveshaping technique, the active technique is steadily becoming more desirable.

The following paragraphs outline the difficulties of the passive approach and discuss the ways in which the active waveshaping technique overcomes them.

A passive filter has certain design limitations that cannot be circumvented. The Q of each tuned, series shunt filter can not be made arbitrarily high; the filter would be too difficult to tune initially and would not remain tuned as temperature and age affected the component values. Low values of Q (20 or less) are needed, particularly if the product is to be mass-produced.

The low Q has disadvantanges, however. For a given characteristic impedance of the filter, the lower the Q, the higher the filter's series resistance. As this resistance is increased, the dissipation caused by both the filtered harmonic current and the fundamental current needed to

fulfill the reactive requirement of the capacitor becomes greater. More series resistance also means that the filter will have a higher impedance at its tuned frequency. To achieve the same level of filtering with this increased resistance, the inductor placed in series with the utility will have to be made correspondingly larger.

A passive filter with many tuned series branches is also complicated to design. Between each frequency at which the filter presents a low impedance to the power circuit there is a parallel resonance that gives a very high impedance. If the power circuit injects currents at any of these alternate frequencies, the filter will resonate. The harmonic voltage seen by the power circuit and the harmonic current injected into the utility under that condition could become very large. At these same parallel resonant frequencies, the filter appears as a low impedance from the utility side. Currents injected by other conditioned loads at these frequencies may therefore flow into the filter and over-stress its components.

It is important to make sure the parallel resonant frequencies are positioned such that these detrimental effects are not substantial. To do so is difficult, particularly as the number of filter branches is increased.

A passive filter provides reactive power flow correction as well as the removal of harmonic components. Since the correction is usually needed by the circuit, this is a beneficial feature that helps offset the cost of the filter. The level of reactive power drawn by the filter is fixed, however; it can not respond to changes in the operation of the power circuit. A nominal value of correction must be chosen instead.

Unless special disconnect switches are provided, the filter continues to draw this reactive power even when the power circuit is not operating. The losses produced by this power flow can significantly reduce the overall efficiency of the power circuit.

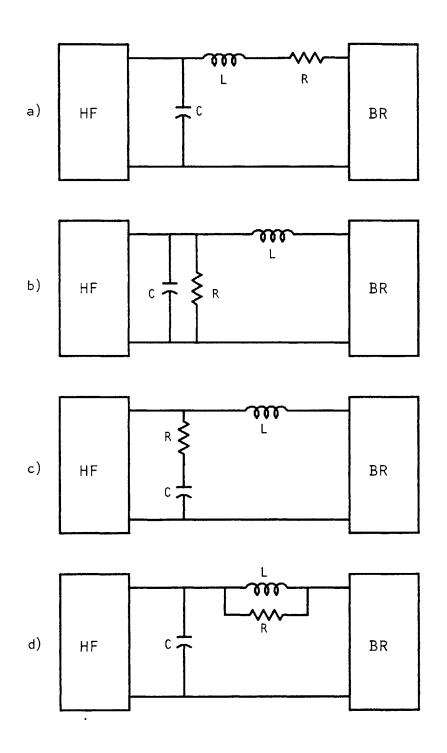

The active waveshaping technique, by it nature, avoids the problems faced by the passive approach. One advantage of an active waveshaping power circuit is its much simpler interaction with the utility. Only a high frequency, low-pass filter is needed between the circuit's switches and the line. The design of such a filter is straightforward. No tuning is required and there is no important dependence on the system's impedance.

Another advantage of the active approach is that power compensation capacitors are not needed. An active waveshaping power circuit has the ability to draw a unity power factor current from the utility at all times. As will be shown later, it is actually easier to make an ideal interface that operates at unity power factor than it is to make one that can work at an arbitrary power factor.

The design and implementation of an active ideal ac-dc interface are not free from complexity, however. The topology of the power circuit must be chosen to meet the requirements placed on the interface and the correct positions of the switch transitions must be determined. The issues and details concerning these two problems will be discussed in the following two chapters of this work.

#### CHAPTER IV

# TOPOLOGICAL FEATURES OF AN ACTIVE UTILITY/DC INTERFACE

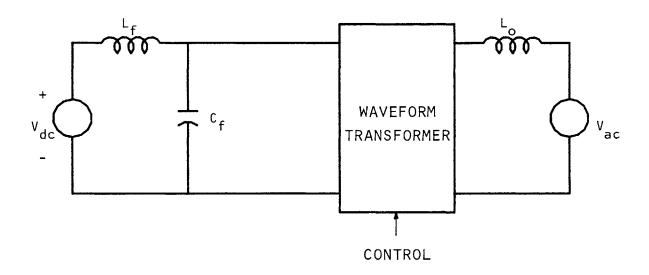

This chapter presents the salient topological features of an active ideal utility-to-dc system interface. It begins with the development of the circuit's basic element: a lossless waveform transformer that can couple a dc system to an ac system. The various topologies this transformer can assume as its requirements range from the most general to the very simple will be outlined and compared. In addition to the waveform transformer, the ideal interface also requires passive elements for load balancing energy storage and switch frequency filtering. Those factors that affect the optimal design of these parts of the interface will be identified. Although much of the discussion in this chapter will deal with single-phase interfaces, the extension to three-phase systems, presented in the final section, is straightforward and, in some ways, easier to implement.

The voltage present at the ac terminals of the ideal interface has a sinusoidal waveform whose magnitude and phase are a function of the impedance of the utility system and the current drawn by the interface. Because the general operation of the interface does not depend on the parameters of the voltage presented to it, the utility will be modeled as a perfect voltage source throughout this chapter. It is only in the design of the switch frequency filters that the actual impedance of the utility plays an important role. When these filters are discussed, this influence will be considered.

The dc system may be either a source, sink, or passive load.

#### IVa. The Basic Element: A Lossless Waveform Transformer

The heart of the ideal ac-dc interface is a power circuit composed only of semiconductor devices. It has two ports, stores no energy, and, in the ideal sense, has no dissipation. The power entering one port is always equal to the power leaving the other. However, even though the products of the respective voltages and currents must be equal at all times, the ratios of each port's variables can assume any value desired.

The simplest application of such a power circuit is a dc-dc converter. This type of converter is typically used to change a dc waveform, either voltage or current, from one level to another. The power circuit can be thought of as a waveform transformer that couples the two systems. For time periods long compared to a switch period, the ratio between the currents or voltages at the two ports is a function of how the semiconductor devices are switched. This ratio will be called the waveform transformation factor.

For dc-dc conversion, the waveform transformation factor is usually constant. It is adjusted only in response to changing load or source characteristics. It is possible, however, to purposefully alter the factor over time to generate a time-varying waveform from a dc waveform. If the transformer is capable of both positive and negative transformation factors, it is even possible to produce an ac waveform with freely controlled parameters.

There are two ways such a lossless waveform transformer could be used to make an ideal ac-dc interface. One approach assumes the dc system is a current source; the other assumes it is a voltage source. It does not matter whether the dc system is actually an active source or

sink, or whether it is simply a passive load. It is only important to distinguish between those systems that have either current or voltage source characteristics.

In the following discussion, that variable, current or voltage, which describes the dc system will be called the characteristic variable, the other will be called the companion variable. How a passive load assumes the characteristic of a current or voltage source will be discussed in the section on load balancing filter elements.

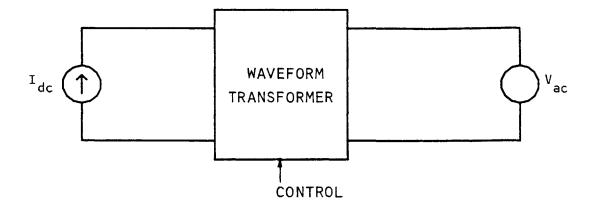

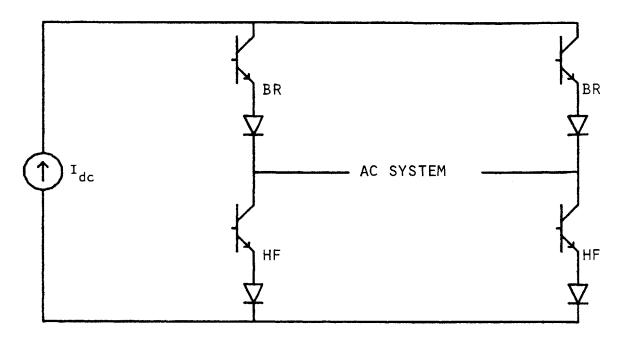

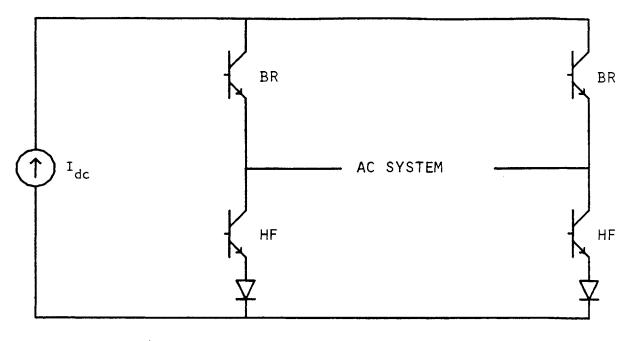

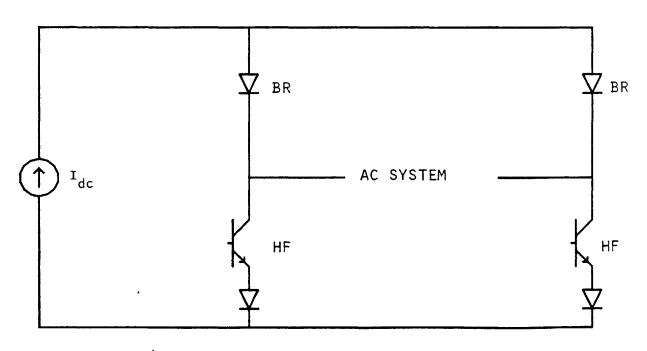

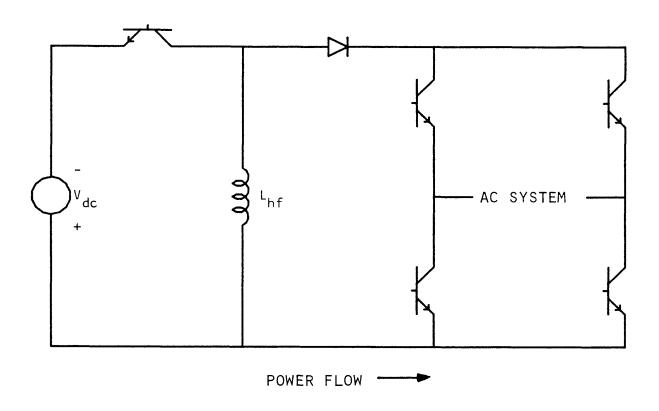

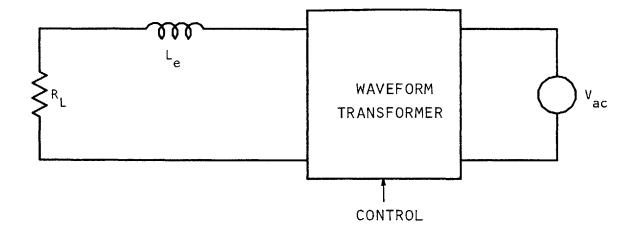

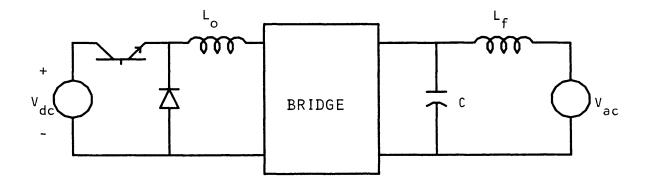

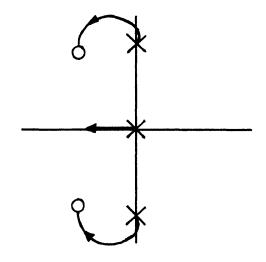

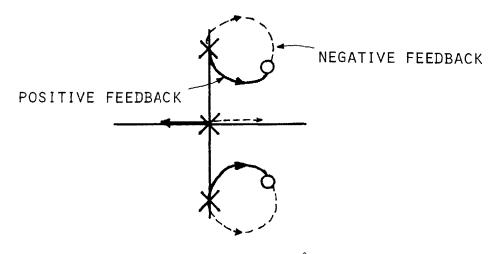

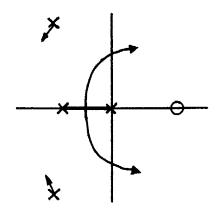

If the dc system is a current source, the waveform transformer is connected directly between the utility's ac voltage source and the dc system, as shown in Figure 4-1a. The switching pattern of the semiconducter devices is controlled to change the dc current waveform into a fundamental ac current waveform with whatever amplitude and phase are wanted. This implementation is the simplest form of the ideal ac-dc interface.

If the dc system has the characteristics of a voltage source, the waveform transformer will generate an ac voltage waveform, rather than current, at its output. Two ac voltage sources result: one, the utility, has features that are specified; the other, the output of the transformer, has features that are totally adjustable. An interconnecting inductor is placed between these two voltage sources as shown in Figure 4-1b. The amplitude and phase of the ac current flowing through this inductor and into the utility can then be controlled by adjusting the output waveform of the transformer. The more accurately and quickly this voltage waveform can be adjusted, the smaller the inductor may be.

a) For a Current Source DC System

b) For a Voltage Source DC System

Fig. 4-1: The Ideal Interface.

In many applications, the magnitude of the dc variable changes over time. For simplicity, this variation will be considered either as very slow compared to the fundamental ac period or as transient steps that are separated by long periods of steady-state operation.

# IV.b Semiconductor Requirements of the Waveform Transformer

Although a waveform transformer can be made to work from any non-zero characteristic dc variable, the discussion of this section will initially assume that the transformation factor can vary only between plus and minus one. The characteristic dc variable must therefore be greater than the peak of the corresponding ac variable. How the power circuit can be modified to remove this restriction will be discussed at the end of this section.

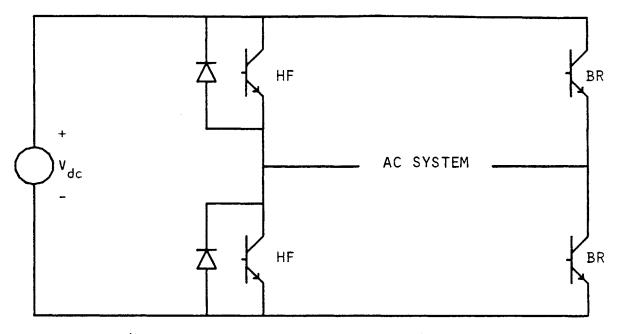

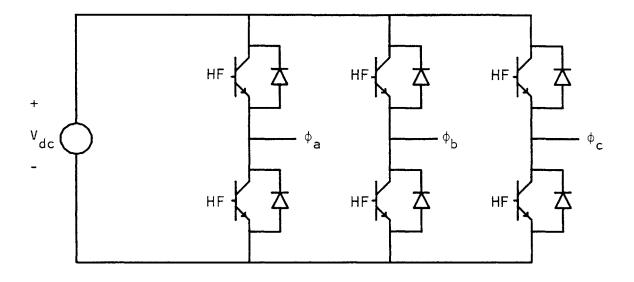

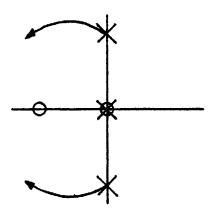

### The General Waveform Transformer

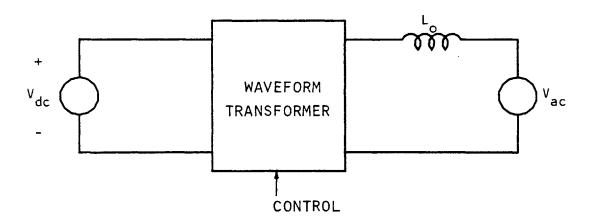

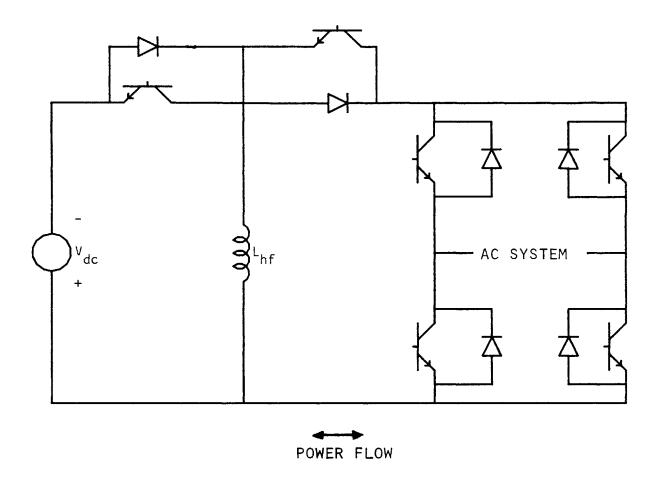

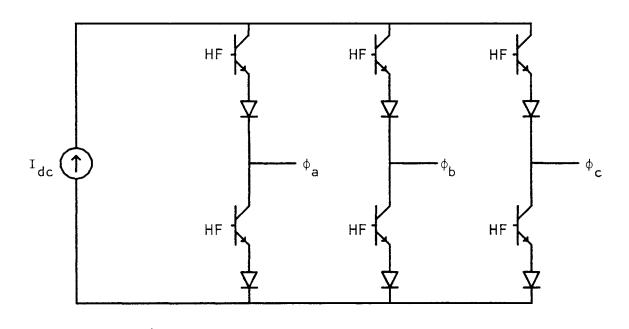

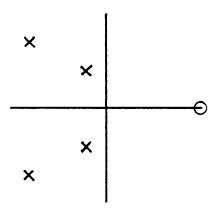

Figures 4-2a and 4-2b show actual implementations of a general waveform transformer. To allow four quadrant operation on both the ac and dc sides, the transformer needs four switches, each of which must carry a bipolar current and support a bipolar voltage. Each switch must withstand the larger of the transformer's input and output voltage and carry the larger of the input and output current. For a given power level, therefore, the closer the characteristic dc variable is to the peak of the corresponding ac waveform, the lower the requirements placed on the switches.

Two of the four switches, marked with the letters "HF" in the figures of this chapter, are turned on and off at high frequencies to

a) For a Current Source DC System

b) For a Voltage Source DC System

Fig. 4-2: The General Waveform Transformer.

provide the active waveshaping. The relative percentage of time during which each of these two switches conducts determines the transformation factor at that instant. The other two switches do not operate at high frequencies; they change state only when one of the four input and output variables changes polarity. Since they perform a low frequency bridge function, they are labeled with the letters "BR".

As can be seen from Figure 4-2, the position of the two types of switches depends on the characteristic of the dc system. The bridge switches in the current source case are responsible for changing the direction in which the current passes through the ac system. They are therefore placed on opposite branches of the topology. In the voltage source case, the bridge switches are used to change the polarity of the voltage presented to the ac system. To do this, they must be located on the same branch of the topology. In either case, the high frequency switches occupying the remaining two positions are able to control the average time during which the characteristic dc variable is presented to the ac system.

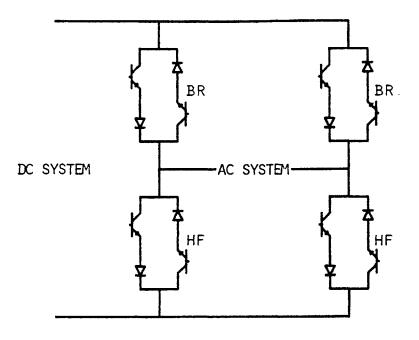

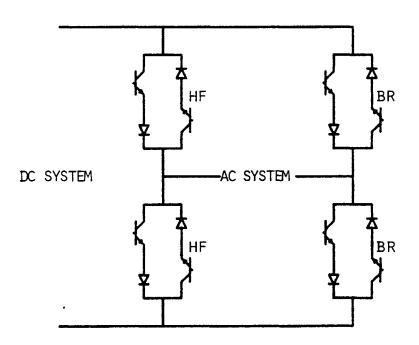

# Waveform Transformer for a Two Quadrant DC System

The double bipolar requirement of the four switches in the waveform transformer can be removed if four quadrant operation is not needed for the dc system. In many useful applications, the dc system operates in only two quadrants. The characteristic variable (voltage or current) remains unipolar while the companion variable changes polarity to give bidirectional power flow. For these situations, the four switches of the waveform transformer have bipolar requirements on only

a) For a Current Source DC System

Fig. 4-3: The Waveform Transformer for a Two Quadrant DC System.

one of their variables. In the current source case, the switches must withstand bipolar voltages when not conducting; in the voltage source case, the switches must carry bipolar currents.

Implementations for these two cases are shown in Figures 4-3a and 4-3b. The total number of semiconductor devices is half that needed for the more general waveform transformer. For the voltage source case, the number of devices in the conductive path at any one time, and therefore the amount of conduction losses, is also halved.

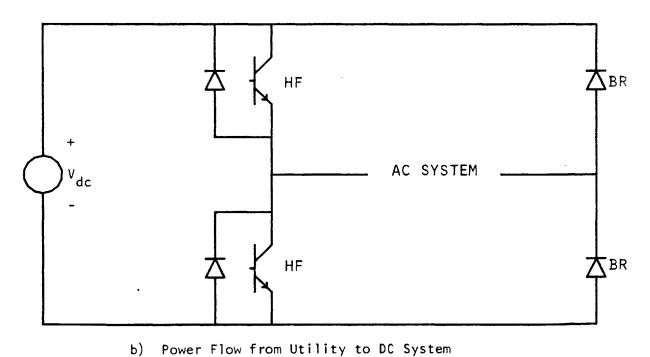

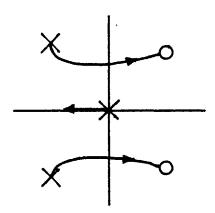

# Waveform Transformer for a One Quadrant DC System

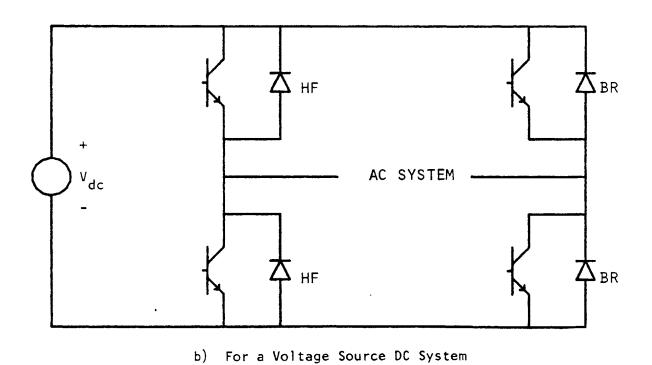

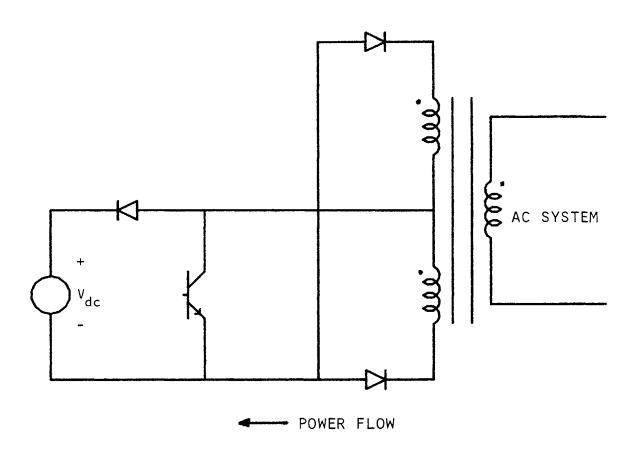

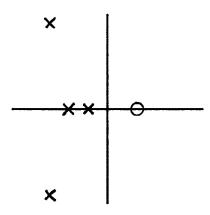

A great number of dc systems have power flow in only one direction. For those applications, the waveform transformer operates in only one quadrant on its dc side and two quadrants on the utility side. Since there is no provision to change the direction of power flow, the ac current waveform must have zero phase shift with respect to the voltage waveform at the transformer's output. In the current source case, this restriction implies unity power factor operation. In the voltage source case, there must be a slight phase shift between the utility's voltage and current to supply the reactive needs of the interconnecting inductor. The inductor is usually very small, however; the deviation from unity power factor is negligible.

The implementation of the waveform transformer when the power flow is unidirectional is shown in Figures 4-4 and 4-5. The first figure corresponds to the dc current source case; the second to the dc voltage source case. The two high frequency switches in each topology are identical to the previous topologies; they have one bipolar and one

a) Power Flow from DC System to Utility

b) Power Flow from Utility to DC System

Fig. 4-4: Waveform Transformer for a One Quadrant DC Current Source.

a) Power Flow from DC System to Utility

Fig. 4-5: Waveform Transformer for a One Quadrant DC Voltage Source.

unipolar variable. The two bridge switches have reduced requirements, however; each can now be implemented with a single semiconductor device. As can be seen from these topologies, an ideal interface designed to operate at unity power factor is actually simpler than one that can operate at an arbitrary power factor.

The nature of the bridge switches is determined by the direction of power flow. When power flows into the dc system, the switches are naturally turned off; diodes can be used. When power flows from the dc system into the utility, the switches must be actively turned off; transistors or other controlled semiconductor devices are needed. This feature of the bridge switch is easily verified for these unidirectional power flow cases. It also points out the mode of operation for the bridge switches in the bipolar power flow cases previously discussed.

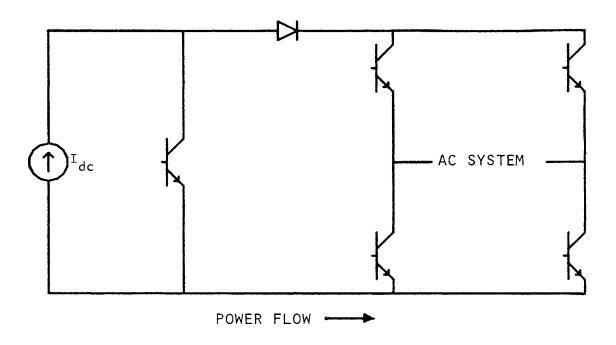

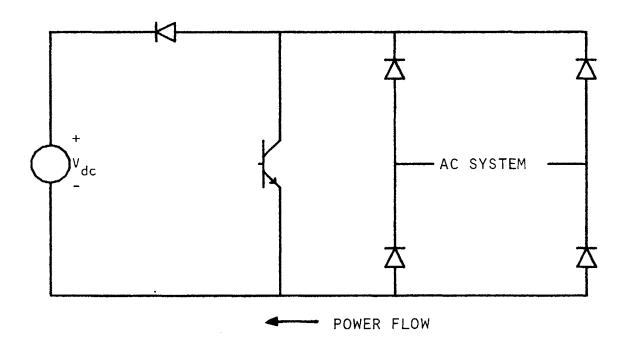

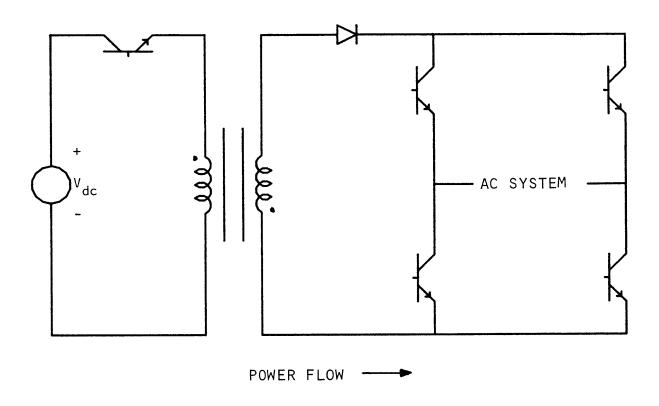

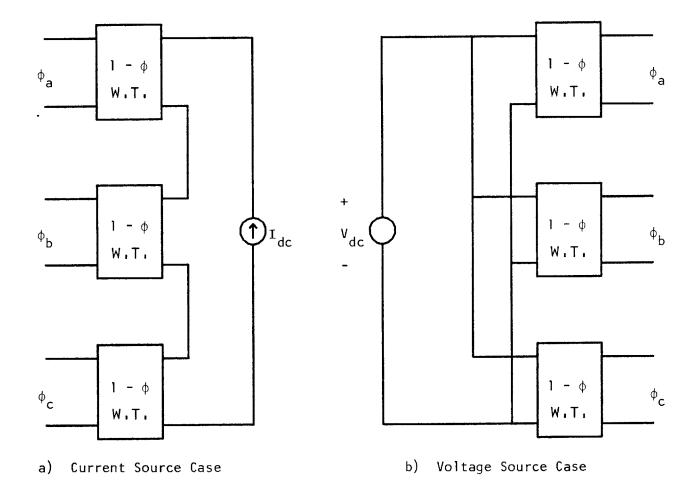

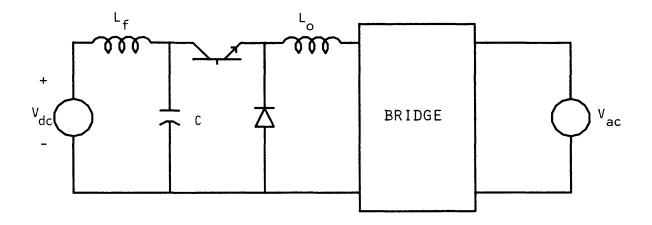

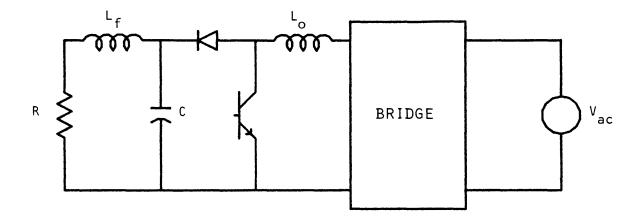

### A Separated Waveform Transformer

The high frequency waveshaping and the bridge functions can be separated into two sections of the power circuit. This separation requires twice as many bridge switches, but, for the unidirectional power flow case, the number of high frequency switches is halved. Since the high frequency switches are both more expensive and have higher losses than the bridge switches, the separation is typically well justified. Figures 4-6 and 4-7 show how a separated waveform transformer can be implemented.

The bridge switches in a separated waveform transformer have lowered power ratings. The peak voltage and current they must withstand are no longer determined by the larger of the transformer's input and

Fig. 4-6: A Separated Waveform Transformer for a DC Current Source.

Fig. 4-7: A Separated Waveform Transformer for a DC Voltage Source.

output variables; they are simply dependent on the peak ac waveform values. When the characteristic dc variable is such that the transformation factor is always substantially less than unity, the reduction in power ratings can be significant.

# Transformation Factors Greater Than Unity

For all the topologies presented so far, the waveform transformer has only been able to produce an ac variable that is lower than the characteristic dc variable. It is possible to add a small energy storage element to the high frequency switches so that the transformer can reach factors far greater than unity. Figure 4-8 shows the alteration that must be made to the unidirectional and separated power circuit given in Figure 4-7. The topology of the high frequency switches and the energy storage element is that of an up/down, or buck/boost, dc-dc converter.

When the power flow is bidirectional, the implementation of the up/down converter with only two bridge switches is difficult. It requires either four high frequency switches and an inductor or three high frequency switches and two inductors. For these applications it is better to separate the bridge and waveshaping functions, as shown in Figure 4-9. Although the number of bridge switches is again double that of the normal topologies, the separated power circuit requires only two high frequency switches and one inductor.

The ability to have transformation factors greater than unity does not come free; the semiconductor device ratings are substantially increased over those of the previous topologies. The high frequency

Fig. 4-8: A One Quadrant Waveform Transformer Capable of a Transformation Factor Greater Than Unity.

Fig. 4-9: A Two Quadrant Waveform Transformer Capable of a Transformation Factor Greater Than Unity.

54

switches must now withstand a voltage and carry a current whose values are the sum, instead of the larger, of the corresponding input and output variables. This penalty is so severe that the up/down converter topology should not be used unless it is actually needed.

### Electrical Isolation Between the AC and DC Systems

Very often the ideal interface is required to provide electrical isolation between the utility and the dc system. The simplest way to accomplish this isolation is to place a 60 Hz transformer at the utility connection. When the power flow is unidirectional and the functions of the waveform transformer have been separated, it is possible to maintain the original number of bridge switches by using a center-tapped isolation transformer. Figure 4-10 shows how this is done. The center-tapped transformer is less efficient in its use of copper, but the economy, efficiency, and reliability of fewer bridge switches can offset this disadvantage. The center-tapped approach is particularly advantageous when the direction of power flow requires actively controlled bridge switches since it reduces the number of drive systems needed.

It is also possible to achieve electrical isolation with a high frequency transformer. Various topologies can be used; many examples of high frequency links can be found in commercially available switching power supplies. Figure 4-11 shows one approach that incorporates a flyback converter. Because the volt-seconds applied to the isolation transformer in these topologies is much less than that of the 60 Hz utility waveform, the transformer is lighter and cheaper. Its flux

Fig. 4-10: A Separated Waveform Transformer with a 60 Hz Isolation Transformer in the Bridge.

.

Fig. 4-11: A Waveform Transformer with a High Frequency Isolation Transformer.

varies widely at the switching frequency, however; a laminated iron core cannot be used.

The high frequency isolation transformer's parasitic elements do cause problems with the transitions of the waveshaping switches. The leakage inductance affects the transition at turn-off; the coupling capacitance affects it at turn-on. Transformer designs that reduce one parasitic element cause the other to increase. Turn-on and turn-off snubbers will protect the semiconductor devices, but they are difficult to design because the switch's voltage and current levels vary so greatly. Snubbers that give adequate protection at the peak of the ac waveforms take a very long time to operate near the zero-crossings because the charging voltage and current levels are very small. Efforts must be made to keep the transformer's parasitic elements as small as possible to minimize this problem.

#### IV.c Load Balancing Filter Elements

The ideal utility/dc interface should deliver distortion free waveforms to both the utility and the dc system. The previous two sections have discussed how this requirement can be met on the ac side, but they have not addressed the waveforms that result on the dc side. The purpose of this section is to do so.

The waveform transformer insures that the utility current will have a fundamental sinusoid shape. The power flowing through the ac port of the interface therefore has a profile composed of two parts: a dc component and a 120 Hz sinusoidal component. Since the waveform transformer does not provide energy storage, the power flowing through

its do port will have the same profile.

With the characteristic variable contrained to be constant by the dc system, the companion variable at the dc port must therefore have both a dc and a 120 Hz sinusoidal component. If the interface is operating at unity power factor, the magnitude of the 120 Hz component is equal to that of the dc component; if reactive power flows, the 120 Hz component is larger.

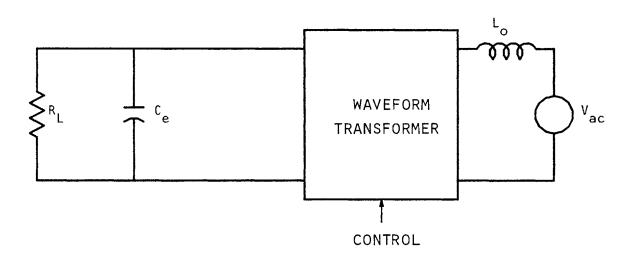

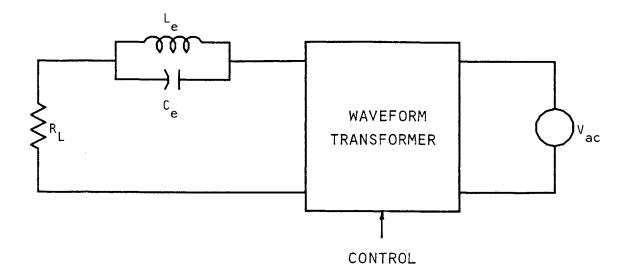

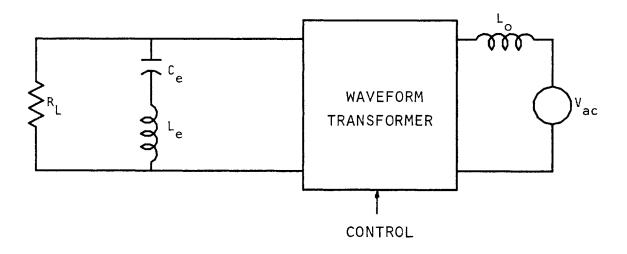

### A Single Element Filter

To remove the alternating component from the companion variable before it reaches the dc system, a passive filter is needed. If the dc system has the characteristics of a current source, an inductor placed in series with the source could absorb the 120 Hz voltage component. If the dc system is a voltage source, a parallel capacitor could shunt the 120 Hz current component.

If the dc system were actually a perfect current or voltage source, the filter element would not work. The series inductor needs a less than infinite current source impedance and the parallel capacitor must have a greater than zero voltage source impedance. Without these, the passive elements would have nothing to work against and the 120 Hz components would be presented to the dc system. In actual applications this requirement is often met, particularly when the dc system is a passive load. When it is not, such as in the case of a low impedance battery, and the dc system can not handle the large alternating component of the companion variable, the impedance of the source can be adjusted with additional reactive elements.

In most applications of the ideal interface, it is actually the passive filter element that gives the dc system its voltage or current characteristic. Figure 4-12 shows how this happens for a simple resistive load. A series inductor, if large enough, would hold the load's current constant; a parallel capacitor, if large enough, would constrain the voltage. Actually, the characteristic variable of the dc system would only be constant if the element value were infinite. A less than infinite value allows some 120 Hz ripple to occur.

With the filter element in place and designed to make the ripple of the dc system's characteristic and companion variables negligible, there is a mismatch in power flow between the dc and ac systems. This mismatch has a 120 Hz sinusoidal profile and requires a corresponding change in the energy stored within the interface. It is the dc side filter element that supplies this load balancing energy storage.

If load balancing were the only reason for the passive filter element, it would need to store a peak energy no greater than

$$E_{P_{\text{max}}} = \int_{0}^{\pi/2\omega_{o}} \frac{P_{dc}}{\cos\phi} \sin 2\omega_{o} t dt = \frac{P_{dc}}{\omega_{o}\cos\phi}$$

(4-1)

where  $\omega_{\rm O}$  = 377 rad/sec and  $\cos \varphi$  equals the power factor at the utility interface.

Because the value of the passive element must be chosen to provide the filtering needed, however, the peak energy stored in the passive element is much greater that which would be necessary for load balancing. For example, in the voltage source case, the parallel

a) Current Source

b) Voltage Source

Fig. 4-12: Load Balancing Element Specifies DC Load Characteristic.

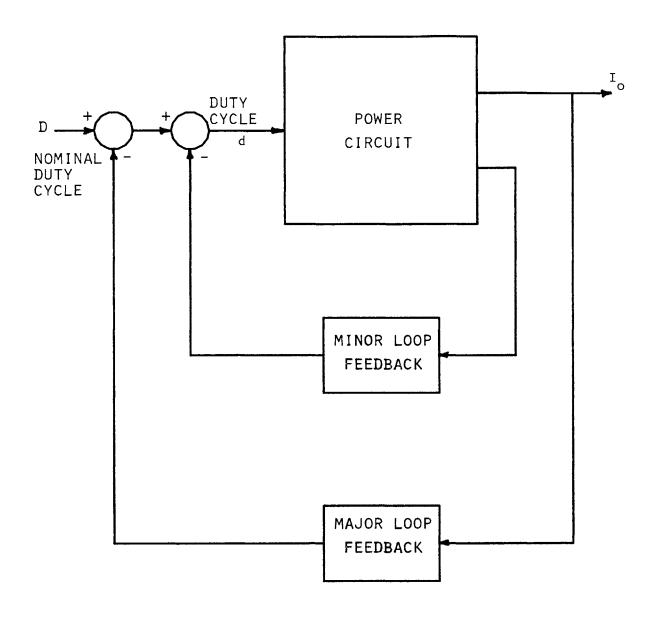

capacitor must carry a current of