### **Purdue University** Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

9-2012

## MoS2 Nanoribbon Transistors: Transition From Depletion Mode to Enhancement Mode by Channel-Width Trimming

Han Liu

Birck Nanotechnology Center, Purdue University, hanliu@purdue.edu

Jiangjiang Gu

Birck Nanotechnology Center, Purdue University, jjgu@purdue.edu

Peide D. Ye

Birck Nanotechnology Center, Purdue University, yep@purdue.edu

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Part of the <u>Nanoscience and Nanotechnology Commons</u>

Liu, Han; Gu, Jiangjiang; and Ye, Peide D., "MoS2 Nanoribbon Transistors: Transition From Depletion Mode to Enhancement Mode by Channel-Width Trimming" (2012). Birck and NCN Publications. Paper 1144. http://dx.doi.org/10.1109/LED.2012.2202630

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# MoS<sub>2</sub> Nanoribbon Transistors: Transition From Depletion Mode to Enhancement Mode by Channel-Width Trimming

Han Liu, Jiangjiang Gu, Member, IEEE, and Peide D. Ye, Senior Member, IEEE

Abstract—We study the channel width scaling of back-gated  ${\rm MoS}_2$  metal—oxide—semiconductor field-effect transistors from 2  $\mu{\rm m}$  down to 60 nm. We reveal that the channel conductance scales linearly with channel width, indicating no evident edge damage for  ${\rm MoS}_2$  nanoribbons with widths down to 60 nm as defined by plasma dry etching. However, these transistors show a strong positive threshold voltage  $(V_T)$  shift with narrow channel widths of less than 200 nm. Our results also show that transistors with thinner channel thicknesses have larger  $V_T$  shifts associated with width scaling. Devices fabricated on a 6-nm-thick  ${\rm MoS}_2$  crystal underwent the transition from depletion mode to enhancement mode.

Index Terms— ${

m MoS_2}$  nanoribbon, threshold voltage shift, width scaling.

#### I. Introduction

THE triumph of the aggressive scaling of silicon-based integrated circuits has dramatically changed our lifestyle in the past couple of decades. However, as the scaling of silicon approaches its physical limit, efforts in finding alternative channel materials have been made for the extension of the Moore's law. Of these materials, Ge and III-V materials are among the most promising candidates because of their high carrier mobilities. They have been widely studied for logic applications in the past years [1]-[4]. Although graphene, a single layer of carbon atoms having superior carrier mobilities of up to 200 000 cm<sup>2</sup>/V·s, has been recognized as another material candidate, its gapless nature limits its further application in logic devices [5]. Nevertheless, the discovery of graphene has spurred the research of other 2-D layered structures, including boron nitride, topological insulators (Bi<sub>2</sub>Te<sub>3</sub>, Bi<sub>2</sub>Se<sub>3</sub>, etc.), and transitional metal dichalcoginides (TMDs) [6]-[10]. TMDs, e.g., MoS<sub>2</sub>, have enjoyed several advantages in device applications because they have large bandgaps (usually > 1 eV), satisfactory electron mobilities of up to several hundreds, and good thermal stability and can be used to form ultrathin-body transistors with atomic layers, which make them a desirable channel material with superior immunity to short-channel effects [11]–[13]. The  $MoS_2$  devices are mostly n-type transistors in experimental observations, which might be attributed to the

Manuscript received May 8, 2012; accepted May 27, 2012. Date of publication July 13, 2012; date of current version August 21, 2012. This work was supported in part by the National Science Foundation under Grant CMMI-1120577. The review of this letter was arranged by Editor Z. Chen.

The authors are with the School of Electrical and Computer Engineering and the Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2202630

Fig. 1. (a) Schematic illustrations of device fabrication. (b) Optical image of one set of transistors (D1) fabricated on a 6-nm-thick  $MoS_2$  crystal. (Scale bar: 5  $\mu$ m.) (c) SEM image of another set of devices (D2). (Inset: Magnified image of the 60-nm-wide  $MoS_2$  nanoribbon transistor.)

stoichiometric composition in the channel [10], [15], [16]. Also, the charge neutrality level at the metal/MoS $_2$  interface could be in the vicinity of the conduction band  $(E_C)$ ; thus, n-type contacts are more easily made. The fabricated MoS $_2$  transistors behave as depletion-mode n-channel metal-oxide-semiconductor field-effect transistors (MOSFETs) with large negative threshold voltages [14]. The 2-D nature of MoS $_2$  (as well as other layered materials) makes it difficult to realize channel doping as a way to achieve a desirable positive  $V_T$  or enhancement-mode operation for various desirable circuitry configurations. Therefore, making an enhancement-mode MoS $_2$  MOSFET is quite challenging.

#### II. EXPERIMENTS

In this letter, we study the width scaling of MoS<sub>2</sub> transistors by forming nanoribbon channels and show that the  $V_T$  of MoS<sub>2</sub> transistors can be modulated to be both positive and negative through appropriate width selection. The fabrication process of sets of MoS<sub>2</sub> transistors is shown in Fig. 1(a), as described hereinafter. MoS<sub>2</sub> flakes were mechanically exfoliated from bulk ingot (SPI Supplies) and then transferred to a heavily p-doped silicon substrate (0.01–0.02  $\Omega$  · cm) with a 300-nm SiO<sub>2</sub> capping layer. The silicon substrate served as a global back gate, while the 300-nm SiO<sub>2</sub> served as the gate dielectric. After the flake transfer, we used electron beam lithography to pattern

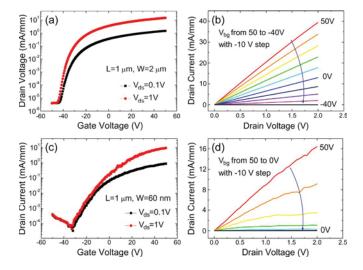

Fig. 2. (a) and (b) Transfer and output curves, respectively, of a transistor with a 2- $\mu$ m channel width on a 6-nm-thick MoS<sub>2</sub> crystal (D1s). (c) and (d) Transfer and output curves, respectively, of the transistor with a 60-nm channel width on the same crystal.

the flake, followed by plasma dry etching (BCl<sub>3</sub>: 15 sccm; Ar: 60 sccm; pressure: 0.6 Pa; RF source power: 100 W; RF bias power: 50 W; time: 5 min) to remove the excess parts of the flakes, leaving connected rectangles with a fixed length (2  $\mu$ m) but various widths to be used as device channels. The widths of these rectangles were varied from 2  $\mu$ m down to 60 nm. Finally, contacts were defined by electron beam lithography, followed by a 50-nm Au metallization by electron beam deposition. The contact bars were 1  $\mu$ m wide, centered on the edge between two neighboring channel areas. The final set of devices has a fixed channel length of 1  $\mu$ m and widths of 2  $\mu$ m, 1  $\mu$ m, 500 nm, 200 nm, 100 nm, 80 nm, and 60 nm. Three sets of devices were fabricated on three large flakes with thicknesses of 6, 6, and 11 nm, as determined by atomic force microscopy. The optical image and scanning electron microscopy (SEM) image of these sets of devices are shown in Fig. 1(b) and (c). The overetching of the MoS<sub>2</sub>, in order to guarantee complete removal of excess MoS<sub>2</sub> crystals, created a rectangular step in the SiO<sub>2</sub> capped substrate surrounding the flake and also created SiO2 sidewalls at the edges of the MoS<sub>2</sub> channels (Fig. 1(c) inset). Smooth edges without obvious damage by dry etching were observed at the MoS<sub>2</sub> nanoribbons.

Fig. 2(a)-(d) shows the transfer and output characteristics of the devices with 2-\mu m and 60-nm widths, selected from one of three sets of devices. These devices were fabricated using one of the 6-nm-thick crystals (D1). Fig. 2(a) shows well-behaved transfer curves from the 2- $\mu$ m-wide transistor. The current on/off ratio is approximately  $10^7$ , as the ultrathin MoS<sub>2</sub> crystal can be easily depleted at negative gate biases. The extrinsic field-effect mobility of this device is  $21.8 \text{ cm}^2/\text{V} \cdot \text{s}$ , which can be further improved by high-k dielectric passivation [10], [15]. The transfer curve of the 60-nm-wide nanoribbon device is shown in Fig. 2(c). Compared to Fig. 2(a), the transfer curves are noisy, due to fewer conduction modes in the nanoribbons, as well as an increased leakage current at negative bias. This increased gate leakage could be ascribed as dielectric degradation in SiO<sub>2</sub> by dry etching. We also observe a larger subthreshold swing (SS). The SS for the  $2-\mu$ m-wide device is around 2 V/dec; however, for the 60-nm-

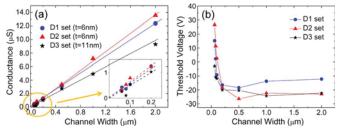

Fig. 3. (a) Extracted channel conductance of all sets of devices versus channel width. The dashed lines in the inset are guided by eye. (b) Extracted threshold voltage of all sets of devices versus channel width.

wide device, this value increases to almost 10 V/dec. The SS value of the 2- $\mu$ m-wide device indicates a reasonably good interface (interface trap density  $D_{\rm it} \sim 2.3 \times 10^{12}/{\rm cm}^2 {\rm \cdot eV})$ between the MoS<sub>2</sub> crystal and SiO<sub>2</sub> dielectric. If we replace the 300-nm SiO<sub>2</sub> layer with 5 nm of Al<sub>2</sub>O<sub>3</sub>, while assuming that  $D_{\mathrm{it}}$  remains unchanged, the SS would be significantly reduced to  $\sim$ 75 mV/dec by simply applying  $SS = kT/q(1 + C_{\rm it}/C_{\rm ox})$ , where k is the Boltzmann's constant, T is the temperature, and  $C_{\rm ox}$  and  $C_{\rm it}$  are capacitances modeling the oxide and interface traps, respectively. The differences in SS for the two devices are expected because edge roughness and defects play more important roles in nanoribbon transistors. We also observe a large difference in threshold voltages for these two devices. At a 2-V drain voltage with zero gate bias, the drain current for the  $2-\mu$ m-wide device is 13.0 mA/mm, showing a typical depletionmode operation. However, for the narrower device, the drain current is near zero with zero gate bias, indicating an obvious  $V_T$  shift to the positive side, signaling an enhancement-mode operation. At the same  $V_{\rm ds} = 2 \, {\rm V}$  and  $V_{\rm gs} = 50 \, {\rm V}$ , we achieve the highest drain current density to be 39.4 mA/mm for the 2- $\mu$ mwide device and 16.4 mA/mm for the 60-nm-wide device. This difference in normalized drain current suggests that  $V_T$  is different for these two devices, assuming that the current scales linearly with the channel width, which is verified hereinafter.

In order to confirm that the current scales linearly with various channel widths, we plot the total conductance (one over on-resistance) versus channel width for all three sets of devices, as shown in Fig. 3(a). The on-resistance  $(R_{\rm on})$  of the transistor has contributions from the contact resistance and channel resistance. Since the contact area and width for all transistors scale with channel width, the contact resistance should scale linearly with the channel width. The same is true for the channel resistance. After determining  $V_T$  via linear extrapolation from transfer characteristics,  $R_{\rm on}$  is extracted at the same reference voltage point  $V_{\rm gs} = V_T + 26$  V. Our result shows that the  $R_{\rm on}$  or total conductance scales linearly with channel width. As expected, MoS<sub>2</sub> acts as a conventional semiconductor, in great contrast to 3-D topological insulators such as Bi<sub>2</sub>Te<sub>3</sub> or Bi<sub>2</sub>Se<sub>3</sub>, where edge or surface conductance could be enhanced or dominate [17]. The width-dependent conductance is about 6–7  $\mu$ S/ $\mu$ m for the two 6-nm-thick devices (D1 and D2) and 5  $\mu$ S/ $\mu$ m for the 11-nm device (D3). We are not clear about why the thicker device has a lower conductance, and this result needs further investigation. As shown in the inset of Fig. 3(a), with much reduced channel widths, the extracted conductance becomes noisier as fewer conduction modes are available in the nanoribbons. However, the data points still fall along the scaling trend.

Lastly, we studied the  $V_T$  shift of all devices associated with the channel width. The  $V_T$  is extracted from the linear extrapolation method at a low drain voltage.  $V_T$  is calculated by  $V_T =$  $V_{\rm GSi} - V_{\rm ds}/2$ , where  $V_{\rm GSi}$  is the intercept gate voltage and  $V_{\rm ds}$ is the drain voltage [18]. Threshold voltages for all three sets of devices are plotted in Fig. 3(b). Similar trends can be observed for all sets of devices. The  $V_T$  remains constant for transistors with a wider channel width (W > 500 nm). As the width of the channel is narrowed down to 200 nm, we start to observe the  $V_T$  shift to positive values. Apparently, transistors with thinner bodies (D1 and D2) are more likely to be influenced by this effect. For one of the 6-nm-thick set of transistors (D2), the threshold voltage ultimately shifts from -20 to 30 V, indicating a clear transition from being a depletion-mode transistor to being an enhancement-mode operation just by trimming down the channel width. The geometry of these nanoribbon transistors with a channel width less than 100 nm has a similar structure to that of Si FinFETs, if we ignore that the MoS<sub>2</sub> channel is modulated only from the back gate. Similar trends of  $\mathcal{V}_T$  shift have also been observed in Si FinFETs as well as InGaAs nanowire transistors [19]. We believe that our  $V_T$  shift is due to edge depletion, similar to what has been observed in majority carrier GaN nanoribbon devices [20]. The edge depletion could be induced by either electric fields or ambient molecules (e.g., H<sub>2</sub>O) adsorbed at the MoS<sub>2</sub> surface. Given our previous surface study of atomic-layer-deposition growth on 2-D crystals, these polarized molecules can be strongly adsorbed at the MoS<sub>2</sub> surface and even persist at 300 °C-400 °C [21]. The geometrical edge effects could also lead  $V_T$  positive shift and SS degradation for nanoribbon transistors as observed in experiments [22]. As expected, the  $V_T$  of the devices fabricated on the thicker crystal (D3) shows relatively minor shifts compared to that of the devices with thinner flakes, as shown in the same figure. The observation of  $V_T$  shifts for MoS<sub>2</sub> transistors with width scaling is important. The 2-D nature of MoS<sub>2</sub> and other TMD-based transistors makes it difficult to engineer the channel through doping. This demonstrated approach, using the width to achieve  $V_T$ adjustments on the same starting channel material in order to realize both enhancement-mode and depletion-mode operations, is a simple and favorable method for circuit designs such as to realize an enhancement-mode/depletion-mode-based inverter.

#### III. CONCLUSION

In summary, we have studied the effect of width scaling on  $MoS_2$  transistors. We have demonstrated that the channel conductance scales linearly for the sets of devices with various channel widths down to 60 nm. We have also revealed that the threshold voltage has a significant shift from negative to positive for transistors with channel widths of less than 200 nm. As a result, these transistors have shown a clear transition from depletion-mode to enhancement-mode operation simply by channel-width trimming. Our result provides a new approach for threshold voltage engineering and is favorable for circuit applications based on large-area 2-D crystal nanomaterials [23]–[26].

#### ACKNOWLEDGMENT

The authors would like to thank N. Conrad for critical reading of the manuscript.

#### REFERENCES

- [1] R. Pillarisetty, "Academic and industry research progress in germanium nanodevices," *Nature*, vol. 479, no. 7373, pp. 324–328, Nov. 2011.

- [2] Y. Xuan, Y. Q. Wu, and P. D. Ye, "High-performance inversion-type enhancement-mode InGaAs MOSFET with maximum drain current exceeding 1 A/mm," *IEEE Electron Devices Lett.*, vol. 29, no. 4, pp. 294– 296, Apr. 2008.

- [3] H. Ko, K. Takei, R. Kapadia, S. Chuang, H. Fang, P. W. Leu, K. Ganapathi, E. Plis, H. S. Kim, S.-Y. Chen, M. Madsen, A. C. Ford, Y.-L. Chueh, S. Krishna, S. Salahuddin, and A. Javey, "Ultrathin compound semiconductor on insulator layers for high performance nanoscale transistors," *Nature*, vol. 468, no. 7321, pp. 286–289, Nov. 2010.

- [4] M. Xu, R. Wang, and P. D. Ye, "GaSb inversion-mode PMOSFETs with atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric," *IEEE Electron Devices Lett.*, vol. 32, no. 7, pp. 883–885, Jul. 2011.

- [5] Y. Zhang, J. W. Tan, H. L. Stormer, and P. Kim, "Experimental observation of the quantum Hall effect and Berry's phase in graphene," *Nature*, vol. 438, no. 7065, pp. 201–204, Nov. 2005.

- [6] K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, "Two-dimensional atomic crystals," *Proc. Nat. Acad. Sci. USA*, vol. 102, pp. 10451–12453, 2005.

- [7] H. Zhang, C. X. Liu, X. L. Qi, X. Dai, Z. Fang, and S. C. Zhang, "Topological insulators in Bi<sub>2</sub>Se<sub>3</sub>, Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> with a single Dirac cone on the surface," *Nat. Phys.*, vol. 5, pp. 438–442, Jun. 2009.

- [8] H. Liu and P. D. Ye, "Atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> on Bi<sub>2</sub>Te<sub>3</sub> for topological insulator field-effect transistors," *Appl. Phys. Lett.*, vol. 99, no. 5, p. 052 108, Aug. 2011.

- [9] V. Podzorov, M. E. Gershenson, C. Kloc, R. Zeis, and E. Bucher, "High-mobility field-effect transistors based on transition metal dichalcogenides," *Appl. Phys. Lett.*, vol. 84, no. 17, pp. 3301–3303, Apr. 2004.

- [10] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nat. Nanotechnol.*, vol. 6, no. 3, pp. 147– 150, Mar. 2011.

- [11] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, "Atomically thin MoS<sub>2</sub>: A new direct-gap semiconductor," *Phys. Rev. Lett.*, vol. 105, p. 136 805, Apr. 2010.

- [12] Y. Yoon, K. Ganapathi, and S. Salahuddin, "How good can monolayer MoS<sub>2</sub> transistors be?" *Nano Lett.*, vol. 11, no. 9, pp. 3768–3773, Sep. 2011.

- [13] H. Liu, A. T. Neal, and P. D. Ye, "Channel length scaling of MoS<sub>2</sub> MOSFETs," ACS Nano, 2012, submitted for publication.

- [14] B. L. Abrams and J. P. Wilcoxon, "Nanosize semiconductors for photooxidation," Crit. Rev. Solid State Mater. Sci., vol. 30, no. 3, pp. 153–182, 2005.

- [15] H. Liu and P. D. Ye, "MoS<sub>2</sub> dual-gate MOSFET with atomic layer deposited Al<sub>2</sub>O<sub>3</sub> as top-gate dielectric," *IEEE Electron Devices Lett.*, vol. 33, no. 4, pp. 546–548, Apr. 2012.

- [16] Z. Yin, H. Li, H. Li, L. Jiang, Y. Shi, Y. Sun, G. Lu, Q. Zhang, X. Chen, and H. Zhang, "Single-layer MoS<sub>2</sub> phototransistors," ACS Nano, vol. 6, no. 1, pp. 74–80, Jan. 2012.

- [17] J. G. Analytis, R. D. McDonald, S. C. Riggs, J.-H. Chu, G. S. Boebinger, and I. R. Fisher, "Two-dimensional surface state in the quantum limit of a topological insulator," *Nat. Phys.*, vol. 6, no. 12, pp. 960–964, Dec. 2010.

- [18] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd. New York: Wiley, 2006.

- [19] J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, "First experimental demonstration of gate-all-around III-V MOSFETs by top-down approach," in *IEDM Tech. Dig.*, 2011, pp. 769–772.

- [20] B. Lu, E. Matioli, and T. Palacios, "Tri-gate normally-off GaN power MIS-FET," IEEE Electron Device Lett., vol. 33, no. 3, pp. 360–362, Mar. 2012.

- [21] H. Liu, K. Xu, X. J. Zhang, and P. D. Ye, "The integration of high-k dielectric on two-dimensional crystals by atomic layer deposition," *Appl. Phys. Lett.*, vol. 100, no. 15, p. 152 115, Apr. 2012.

- [22] K. E. Kroell and G. K. Ackermann, "Threshold voltage of narrow channel field effect transistors," *Solid-State Electrons*, vol. 19, no. 1, pp. 77–81, Jan. 1976.

- [23] Y. Zhan, Z. Liu, S. Najmaei, P. M. Ajayan, and J. Lou, "Large-area vaporphase growth and characterization of MoS<sub>2</sub> atomic layers on a SiO<sub>2</sub> substrate," *Small*, vol. 8, no. 7, pp. 966–971, Apr. 2012.

- [24] K. Liu, W. Zhang, Y. Lee, Y. Lin, M. Chang, C. Su, C. Chang, H. Li, Y. Shi, H. Zhang, C. Lai, and L. Li, "Growth of large-area and highly crystalline MoS<sub>2</sub> thin layers on insulating substrates," *Nano Lett.*, vol. 12, pp. 1538–1544, 2012.

- [25] H. Li, Z. Yin, Q. He, H. Li, X. Huang, G. Lu, D. W. H. Fam, A. L. Y. Tok, Q. Zhang, and H. Zhang, "Fabrication of single- and multilayer MoS<sub>2</sub> film-based field-effect transistors for sensing NO at room temperature," *Small*, vol. 8, no. 1, pp. 63–67, 2012.

- [26] H. Li, G. Lu, Z. Yin, Q. He, H. Li, Q. Zhang, and H. Zhang, "Optical identification of single- and few-layer MoS<sub>2</sub> sheets," *Small*, vol. 8, no. 5, pp. 682–686, Mar. 2012.