Received 19 March 2015; revised 17 April 2015; accepted 20 April 2015. Date of publication xx xxx xxxx; date of current version xx xxxx 2015. The review of this paper was arranged by Editor M. Chan.

Digital Object Identifier 10.1109/JEDS.2015.2425959

# Heteroepitaxial Ge MOS Devices on Si Using Composite AlAs/GaAs Buffer

# PETER D. NGUYEN (Student Member, IEEE), MICHAEL BRIAN CLAVEL (Student Member, IEEE), PATRICK S. GOLEY (Student Member, IEEE), JHENG-SIN LIU (Student Member, IEEE), NOAH P. ALLEN (Student Member, IEEE), LOUIS J. GUIDO (Senior Member, IEEE), AND MANTU K. HUDAIT (Senior Member, IEEE)

Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061, USA CORRESPONDING AUTHOR: M. K. HUDAIT (e-mail: mantu.hudait@vt.edu)

This work was supported in part by the National Science Foundation under Grant ECCS-1348653, and in part by the Intel Corporation. The work of P. D. Nguyen was supported by the National Science Graduate Research Fellowship under Grant 478969. The work of P. S. Goley was supported by the National Science Graduate Research Fellowship under Grant 478969. The work of P. S. Goley was supported by the National Science Graduate Research Fellowship under Grant 478969. The work of P. S. Goley was supported by the National Science Graduate Research Fellowship under Grant DGE. 0822220.

**ABSTRACT** Structural and electrical characteristics of epitaxial germanium (Ge) heterogeneously integrated on silicon (Si) via a composite, large bandgap AlAs/GaAs buffer are investigated. Electrical characteristics of N-type metal-oxide-semiconductor (MOS) capacitors, fabricated from the aforementioned material stack are then presented. Simulated and experimental X-ray rocking curves show distinct Ge, AlAs, and GaAs epilayer peaks. Moreover, secondary ion mass spectrometry, energy dispersive X-ray spectroscopy (EDS) profile, and EDS line profile suggest limited interdiffusion of the underlying buffer into the Ge layer, which is further indicative of the successful growth of device-quality epitaxial Ge layer. The Ge MOS capacitor devices demonstrated low frequency dispersion of 1.80% per decade, low frequency-dependent flat-band voltage,  $V_{FB}$ , shift of 153 mV, efficient Fermi level movement, and limited C-V stretch out. Low interface state density ( $D_{it}$ ) from  $8.55 \times 10^{11}$  to  $1.09 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> is indicative of a high-quality oxide/Ge heterointerface, an effective electrical passivation of the Ge surface, and a Ge epitaxy with minimal defects. These superior electrical and material characteristics suggest the feasibility of utilizing large bandgap III-V buffers in the heterointegration of high-mobility channel materials on Si for future high-speed complementary metal-oxide semiconductor logic applications.

**INDEX TERMS** Germanium (Ge), heteroepitaxy, metal-oxide semiconductor (MOS) devices, silicon (Si), III-V materials.

### I. INTRODUCTION

Aggressive scaling of silicon (Si) complementary metaloxide-semiconductor (CMOS) transistors has resulted in an exponential increase in device density, and thus computing power, over the past four decades. To mitigate the increased power consumption as a result of increasing transistor density, supply voltage scaling is essential to maintain low-power device operation, but at the cost of significantly degrading transistor drive current due to the low carrier mobility of Si [1]. Overcoming the limitations of device and voltage scaling without degrading transistor drive current requires the adoption of narrow bandgap channel materials with superior transport properties. However, the use of such materials as bulk substrates is cost-prohibitive. Thus, another key technical challenge is the heterogeneous integration of high-mobility alternative channel materials on affordable and established Si technology platform.

Germanium (Ge) is an attractive candidate for nextgeneration low-power devices operating at low-voltage ( $\leq 0.5$  V) due to its high electron and high hole mobility ( $2 \times$  and  $4 \times$ , respectively, as compared to those of Si) [2]. Although Ge has been successfully integrated on GaAs substrate [3]–[8], it remains an important issue to integrate Ge on to Si substrate. Thus, numerous methods for the epitaxial growth of Ge on Si have been reported in order to demonstrate the device-quality Ge as a future channel

2168-6734 © 2015 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. material [9]. However, none of these methods have addressed the utilization of high conduction and valance band offsets in order to confine carriers within the Ge nor the elimination of parallel conduction within the buffer layers. Recently, we have demonstrated an innovative method to heterogeneously integrate device-quality epitaxial Ge on Si using a composite, large bandgap AlAs/GaAs buffer, where (i) the high-resistivity, large bandgap (2.15 eV) AlAs layer prevents parallel conduction to the active Ge layer, (ii) high conduction and valance band offsets between the Ge/AlAs heterojunction of  $\sim 1 \text{ eV}$  and  $\sim 0.5 \text{ eV}$  help confine electrons and holes, respectively, to the active Ge layer, and (iii) the GaAs buffer helps reduce dislocations within the active Ge layer, thereby acting as a virtual substrate for active layer integration on to the Si platform [10]. Although successful germanium on insulator (GeOI) pMOSFETs have been demonstrated [11], where the large bandgap of  $SiO_2$ (9.1 eV) is an attractive feature for low-power applications, the GeOI approach has several shortcomings compared with the direct heterogeneous approach in this study, namely (i) GeOI via bonding of Ge wafer onto Si wafer is not economically feasible for large diameter wafer production due to the size of Ge; (ii) due to the poor thermal conductivity of SiO<sub>2</sub>, a large density of thermal mismatch induced defects might occur inside the Ge layer due to the large difference in the thermal expansion coefficients of Ge  $(6 \times 10^{-6}/\text{K})$ and Si  $(2.6 \times 10^{-6}/\text{K})$ ; and (iii) GeOI wafers formed using the thermal-cut method results in non-uniform variation of Ge layer thicknesses. Thus, the AlAs/GaAs epilayers can act as a common buffer platform for next-generation n- and p-Ge CMOS devices heterogeneously integrated on Si. In this paper, we report on the structural characteristics of the Ge epitaxial layer heterogeneously integrated on Si using a composite III-V AlAs/GaAs buffer and on the electrical characteristics of metal-oxide-semiconductor capacitors (MOS-Cs) fabricated from the aforementioned material stack.

# **II. EXPERIMENT**

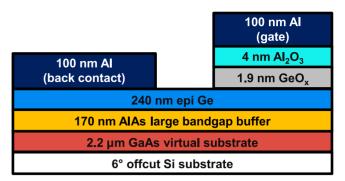

The 240 nm of unintentionally doped (UID) epitaxial Ge was grown *in-situ* on a composite III-V buffer heterogeneously integrated on (100) Si substrate with 6° offcut by solid source molecular beam epitaxy utilizing separate Ge and III-V growth chambers connected *via* an ultra-high vacuum transfer chamber. The lattice-matched, composite III-V buffer consist of (i) a large bandgap 170 nm AlAs barrier layer and (ii) a 2.2  $\mu$ m GaAs virtual substrate. Epitaxial Ge was grown at 400°C at a growth rate of ~ 0.1Å/s in order to minimize interdiffusion between the epitaxial Ge and the underlying AlAs/GaAs buffer layers. The Ge sheet concentration, as determined by Hall measurements utilizing the Van der Pauw technique, was measured to be on the order of 10<sup>14</sup> cm<sup>-2</sup>. Further details of the material growth are reported elsewhere [10].

N-type MOS-Cs were fabricated on the epitaxial Ge material stack. Fabrication of the devices began with a degrease

**FIGURE 1.** Cross-sectional schematic of the Al/Al<sub>2</sub>O<sub>3</sub>/GeOx/Ge MOS-C on Si via a composite AlAs/GaAs buffer architecture.

using acetone, isopropanol, and deionized (DI) water, followed by a three minute native oxide removal in dilute (1:10) hydrofluoric acid. A high-quality, native GeO<sub>x</sub> interfacial passivating layer was then formed by thermal oxidation at 450°C for 10 minutes in an O<sub>2</sub> ambient. Immediately afterwards, a 4 nm Al<sub>2</sub>O<sub>3</sub> gate oxide was deposited at 250°C using a Cambridge NanoTech atomic layer deposition (ALD) system with trimethylaluminum and DI water as precursors for Al and oxygen, respectively. The 100 nm Al gate electrodes and ohmic contacts were subsequently deposited using a Kurt J. Lesker PVD250 electron beam deposition chamber. The devices were then annealed at 250°C in forming gas (N<sub>2</sub>:H<sub>2</sub> 95%:5%) for two minutes. Fig. 1 shows a cross-sectional schematic of the Ge MOS-C device structure.

The structural quality and relaxation state of the epitaxial Ge and underlying AlAs/GaAs buffer were evaluated by high-resolution triple-axis x-ray rocking curve from highresolution x-ray diffraction (HR-XRD) using a Panalytical X-pert Pro system equipped with both PIXel and proportional detectors. Panalytical Epitaxy simulation software was used to simulate the triple-axis x-ray rocking curve. Dynamic secondary ion mass spectrometry (SIMS) was used to determine the depth profile of Al, As, Ga, Ge, and Si atoms at the interfaces of the Ge/AlAs/GaAs heterostructure grown on Si substrate. The SIMS analysis was performed using a Cameca IMS-7f GEO with 5 kV Cs<sup>+</sup> bombardment and MCs<sup>+</sup> detection to reduce matrix effects. To analyze the elemental composition of the Ge/AlAs/GaAs heterostructure grown on Si substrate, energy dispersive x-ray spectroscopy (EDS) was performed using a JEOL 2100 transmission electron microscope (TEM) operating in scanning TEM mode. The electron transparent foils required for EDS were prepared by mechanical polishing and subsequent low-temperature Ar<sup>+</sup> ion beam milling.

Low- and room-temperature multi-frequency capacitancevoltage (C-V) and conductance-voltage (G-V) measurements of the Ge MOS-Cs were performed using an HP4284A precision LCR meter with frequencies ranging from 1 kHz to 1 MHz. Accurate measurements were obtained with the removal of series resistance, as discussed in [12].

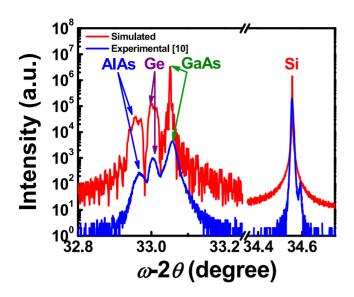

FIGURE 2. Simulated (red) and experimental [10] (blue) symmetric (004) X-ray rocking curve of the Ge/AlAs/GaAs heterostructure grown on Si substrate.

TCAD Sentaurus software was used to simulate highfrequency C-V curves to compare against the experimental data. To study the structural quality of the MOS-C interfaces, cross-sectional high-resolution TEM was performed using a JEOL 2100 TEM. The foils prepared for EDS were also used for cross-sectional high-resolution TEM.

#### **III. RESULTS AND DISCUSSION**

### A. STRAIN RELAXATION PROPERTIES

To determine the structural quality and relaxation state of the epitaxial Ge active layer on AlAs/GaAs buffer layers grown on Si, high-resolution triple-axis x-ray (004) rocking curves were measured. Fig. 2 shows both experimental and simulated symmetric (004) rocking curve for the Ge/AlAs/GaAs heterostructure grown on Si [10]. From the experimental rocking curve, shown in blue in Fig. 2, distinct peaks of the Ge, AlAs, and GaAs layers, with angular separations resulting from differences in their respective lattice plane spacing, are clearly observed. The GaAs is almost fully relaxed with respect to Si and thus, serves as a virtual substrate for the epitaxial Ge. Additionally, the guasi-lattice-matched nature of the Ge, AlAs, and GaAs layers is confirmed due to the Ge and AlAs peak positions with respect to GaAs. A simulated rocking curve, shown in red in Fig. 2, shows distinct Ge, AlAs, and GaAs peaks fitting well with the experimental peaks. The small peak on the right side of the experimentally measured Si peak is due to a measurement artifact. To ensure accuracy of the peak positions, the simulation takes into account the quasi-lattice matched nature ( $\sim 0.07\%$  lattice mismatch) of the Ge/GaAs heterostructure. However, the simulation also assumes that the AlAs/GaAs buffer layer is *fully* relaxed with respect to Si. Thus, the simulated GaAs peak has a much narrower full width at half maximum as compared to that in the experimental measurement. Furthermore, the close proximity of the measured

and simulated full width at half maximums (69.7 arcsec and 79.5 arcsec, respectively), where the simulation assumes a perfect Ge epitaxy, demonstrates that high-quality epitaxial Ge film growth was achieved.

## **B. SIMS DEPTH PROFILE AND EDS ANALYSIS**

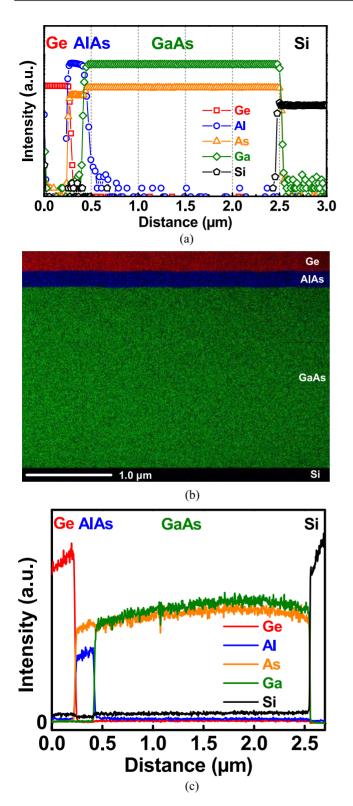

Dynamic SIMS depth profiling provides insight into the extent of elemental diffusion between the epitaxial Ge active layer and the underlying AlAs/GaAs buffer layers grown on Si. Higher growth temperature promotes diffusion of adatoms across surfaces and heterointerfaces. Thus, a low Ge growth temperature (400°C) was selected to allow epitaxial Ge growth with negligible interdiffusion of species at the Ge/AlAs heterointerface [10]. Low Ge growth temperatures  $(< 450^{\circ}C)$  have been demonstrated to yield high-quality Ge epitaxial films with limited interdiffusion between the Ge and corresponding buffer layers [5]. Such optimization of Ge growth temperatures minimizes the alteration of the doping characteristics of the undoped Ge layer as a result of interdiffusion of species in the underlying buffer layers. Fig. 3(a) shows the Ge, Al, As, Ga, and Si compositional profiles in the Ge/AlAs/GaAs heterostructure grown on Si substrate. Constant Ge, Al, As, and Ga intensities within each layer demonstrates good growth uniformity of the epitaxial Ge layer as well as the underlying AlAs and GaAs buffer layers. Moreover, very low levels of Al, As, and Ga are detected within the Ge and a sharp, abrupt Ge/AlAs heterointerface is observed. The apparent interdiffusion between each interface is due to cascade mixing and the matrix effect during SIMS analysis. Thus, both Ge outdiffusion into the underlying AlAs buffer layer as well as indiffusion of Al, As, and Ga into the Ge layer are minimal, further reinforcing the successful growth of a high-quality Ge epitaxial layer on AlAs/GaAs buffer layers grown on Si.

To obtain further insight into the elemental distribution and growth behavior of the Ge/AlAs/GaAs heterostructure grown on Si, EDS elemental mapping was performed. Fig. 3(b) shows a three-element overlay of Ge, Al, and Ga, where the red corresponds to the Ge content, blue corresponds to the Al content, and green corresponds to the Ga content. Four distinct, uniform color regions corresponding to the Ge (red), AlAs (blue), GaAs (green), and Si (black) layers are clearly visible with no evidence of interdiffusion between the heterointerfaces, which would have been signified by a mixing of colors. Fig. 3(c) shows the EDS line profile of the same Ge/AlAs/GaAs heterostructure, which depicts sharp transitions between the heterostructures as well as low levels of Al, As, and Ga within the epitaxial Ge layer. The apparent rise in the Ge and Si signal is an artifact of the EDS line profile scan.

## C. MOS CAPACITOR TEM

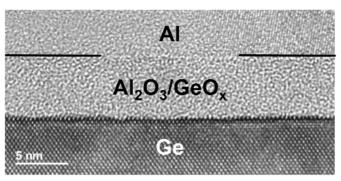

The structural quality of the oxide and Ge surface was investigated by HR-TEM. The TEM micrograph shown in Fig. 4 shows an atomically abrupt and uniform oxide-Ge heterointerface, suggesting minimal interdiffusion across

FIGURE 3. (a) SIMS profile. EDS (b) elemental mapping and (c) line profile of the Ge/AIAs/GaAs heterostructure grown on Si.

the interface, thereby minimizing the creation of interfacial defect states that would deleteriously affect device performance. Due to the low contrast in the TEM micrograph, there is no clear distinction between the ALD deposited Al<sub>2</sub>O<sub>3</sub> and

**FIGURE 4.** Cross-sectional TEM micrograph of the oxide-Ge heterointerface of the Al/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS-C on Si via a composite AlAs/GaAs buffer architecture after post-metal annealing.

the thermally grown  $\text{GeO}_x$  layer shown in Fig. 4. The total thickness of the bilayer oxide is about 5.9 nm, yielding an approximate  $\text{GeO}_x$  thickness of 1.9 nm.

# D. MOS CAPACITOR C-V AND CONDUCTANCE CHARACTERISTICS

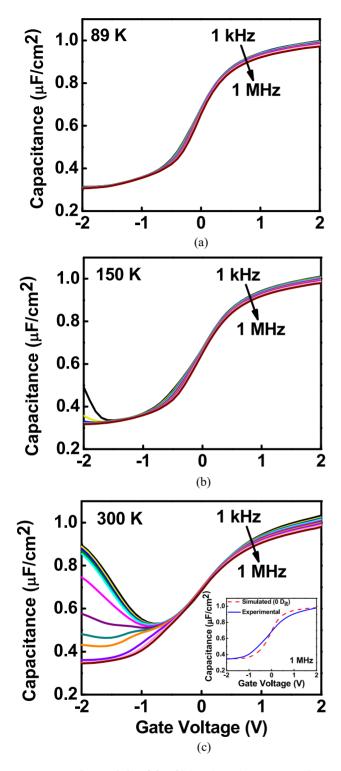

Fig. 5(a)–(c) shows the C-V characteristics of the Ge MOS-C at (a) 89 K, (b) 150 K, and (c) 300 K, respectively. The low-frequency weak inversion response due to minority carriers, a feature of narrow bandgap materials, is suppressed at 89 K, thus resembling room temperature Si MOS C-V characteristics [13]. A moderate flat-band voltage  $(V_{FR})$  shift in the overall C-V curves was observed across all temperatures, which was attributed to the high UID of the epitaxial Ge, as previously reported [10]. The devices demonstrated hysteresis in the 100 kHz C-V measurements of 0.485 V at 300 K, which reduces to 0.165 V at 89 K. The large hysteresis is a result of bulk oxide traps and is not related to the passivation of the oxide/Ge heterointerface [14], [15]. Furthermore, the bulk oxide traps may be due to different deposition techniques of high-k oxides, where the hysteresis in thermal ALD Al<sub>2</sub>O<sub>3</sub> on GeO<sub>x</sub>/Ge MOSCAPs [14], [15] is much higher as compared to that in plasma-enhanced ALD (PE-ALD) Al<sub>2</sub>O<sub>3</sub> on GeO<sub>x</sub>/Ge MOSCAPs [16]. We suspect that the reason for the discrepancy is that, unlike PE-ALD, thermal ALD requires water as a pre-cursor for oxygen. Since  $GeO_x$  is hygroscopic and thus, very susceptible to moisture, this might be a reason for the larger oxide charge trapping responsible for the hysteresis as a result of water exposure during thermal ALD. From the hysteresis, trapped oxide charge density  $(N_{ot})$  can be extracted using [12]

$$N_{ot} = \frac{\Delta V_{FB} C_{ox}}{q},\tag{1}$$

where  $\Delta V_{FB}$  is the  $V_{FB}$  shift (also known as hysteresis) between the bidirectional 100 kHz C-V sweep, q is the elementary charge, and  $C_{ox}$  is the oxide capacitance per unit area, which was calculated to be  $1.4\mu$ F/cm<sup>2</sup> using the Maserjian *et al.* method [17] accounting for quantization effects, corresponding to an EOT of 2.5 nm. From eq. 1,  $N_{ot}$  of  $4.25 \times 10^{12}$  cm<sup>-2</sup> and  $1.21 \times 10^{12}$  cm<sup>-2</sup> was

6

Log(Frequency (Hz)) Energy in bandgap (eV 2 0.61 5 0.60 0.59 0.58 1 0.57 89 K 3 -2 -1 0 1 (a) 6 Energy in bandgap (eV 2 Log(Frequency (Hz)) 0.56 5 0.54 0.52 1 0.50 150 K 3⊾ -2 0 -1 (b) 6 0.45 Cm 2 e< Log(Frequency (Hz)) 50 G<sub>p</sub>/qA<sub>@</sub> (10<sup>11</sup> eV<sup>-1</sup> Energy in bandga 1 10 0.40 5 5 1 0.35 0 10 0.30 300 K 3 -2 -1 0 1 Gate Voltage (V) (c)

**FIGURE 5.** C-V characteristics of the Al/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS-C on Si via a composite AlAs/GaAs buffer architecture at (a) 89 K, (b) 150 K, and (c) 300 K. (Inset) Comparison of 1 MHz simulated (with zero  $D_{it}$ ) and experimental curve showing limited C-V stretch-out.

extracted from 300 K and 89 K, respectively. Additionally, the MOS-Cs exhibited limited C-V stretch-out, as shown in the inset of Fig. 5(c), where a simulated 300 K 1 MHz curve with zero interface state density  $(D_{it})$  is shown compared to

**FIGURE 6.** Conductance  $(G_p/\omega)$  contours of the Al/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS-C on Si via a composite AlAs/GaAs buffer architecture at (a) 89 K, (b) 150 K, and (c) 300 K. All figures follow the color scale shown in Fig. 3(c).

the experimental 300 K 1 MHz curve. The parameters used for the simulated 1 MHz curve include a doping density of  $1.24 \times 10^{18}$  cm<sup>-3</sup>, as estimated from the maximum-minimum capacitance technique [12];  $N_{ot}$  of  $4.25 \times 10^{12}$  cm<sup>-2</sup>, as extracted earlier from the 300 K C-V data from eq. 1; and  $D_{it}$  of 0 cm<sup>-2</sup> eV<sup>-1</sup> uniformly distributed throughout the bandgap. Limited C-V stretch-out of the experimental C-V curve as compared to the simulated C-V curve is indicative of low interface states throughout the upper half of the Ge bandgap [18]. The MOS-C's also demonstrate low frequency dispersion in the accumulation regime of 1.80% per decade over three decades at 300 K, which reduces down to 0.87% per decade over three decades at 89 K. The low frequency dispersion of the MOS-C's at 300 K suggests low interface states near midgap [18]. We speculate that this reduction in frequency dispersion is a reflection of the weak temperature dependence of the supply of carriers to the accumulation layer. Suggestive of low interface states near the conduction band edge is a low frequency-dependent  $V_{FB}$  shift [18], [19], which was calculated to be 59 mV, 77 mV, and 153 mV for 89 K, 150 K, and 300 K C-V measurements, respectively. Finally, there is an apparent small frequency dispersion kink in the depletion regime due to interfacial traps, as observed clearly in Fig. 5(a) and (b).

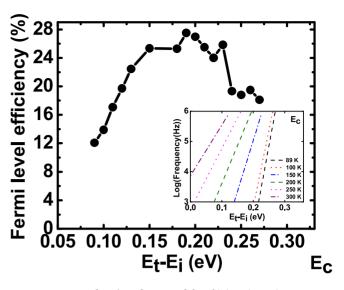

Fig. 6(a)–(c) shows the conductance contours corresponding to G-V sweeps measured at (a) 89 K, (b) 150 K, and (c) 300 K, respectively, which demonstrates the Fermi level efficiency (*FLE*) of the MOS-Cs. The Fermi level trace (dotted black line) at each measurement temperature follows the conductance peaks under different frequency and bias conditions. Efficient biasing of the Fermi level from near midgap to close to the conduction band edge is observed in the MOS-C, as demonstrated by the steepness of the Fermi level traces with respect to gate bias change. Quantitative calculation of the *FLE* [20] was performed using

$$FLE = \ln\left(\frac{f_2}{f_1}\right) \frac{\left[kT/q\right]}{(V_1 - V_2)}\%,$$

(2)

where  $f_1$  and  $f_2$  are the frequencies at which the depletion regime  $G_p/\omega$  peaks occur under bias  $V_1$  and  $V_2$ , respectively, k is the Boltzmann constant, T is temperature, and q is the elementary charge. Shockley–Read–Hall statistics can be applied to demonstrate *FLE* as a function of energy within the Ge bandgap using [21]

$$\tau_n = \frac{1}{2\pi f} = \frac{1}{\sigma_n v_{th} n_i} \exp\left(-\frac{E_t - E_i}{kT}\right),\tag{3}$$

where  $\tau_n$  is the time constant for electrons, f is the measurement frequency,  $\sigma_n$  is the electron capture cross section,  $v_{th}$  is the thermal velocity of electrons,  $n_i$  is the intrinsic carrier concentration of Ge,  $E_t$  is the trap energy level,  $E_i$  is the midgap energy level, k is the Boltzmann's constant, and T is temperature.  $\sigma_n$  was assumed to be a constant value [13] of  $10^{-16}$  cm<sup>-2</sup> [22]. Fig. 7 shows the FLE of the MOS-C as a function of  $E_t$  away from  $E_i$ , where  $E_C$  is the conduction band edge of Ge. A peak FLE of 27.5% was observed 0.19 eV away from  $E_i$ , which demonstrates good modulation of the Fermi level with respect to gate voltage, suggesting low  $D_{it}$  throughout the bandgap. The poor *FLE* closer to  $E_i$ ,

FIGURE 7. FLE as a function of energy of the Al/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS capacitor on Si via a composite AlAs/GaAs buffer architecture. (Inset) Ge bandgap energy ranges accessible at various measurement temperatures (89–300 K).

which is partially attributable to the additional conductance contribution by the minority carrier response [8], is clearly demonstrated by the horizontal "arcing" of the Fermi level trace, which can be clearly seen in Fig. 6(c). Conductance contours extracted from G-V measurements performed at various temperatures from 89 K - 300 K were utilized in the extraction of *FLE*, as each temperature allows the sampling of a limited region of the Ge bandgap, as shown in the inset of Fig. 7.

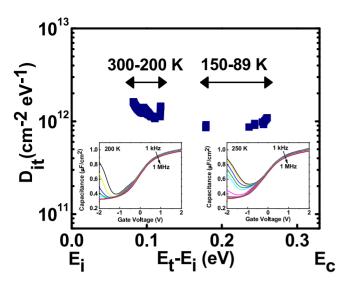

# E. MOS CAPACITOR DIT DISTRIBUTION

$D_{it}$  was extracted from the conductance method with surface potential fluctuation correction [23], [24] using

$$D_{it} = \left(\frac{G_p}{\omega}\right)_{\max} \left[f_D\left(\sigma_s\right) qA\right]^{-1},\tag{4}$$

where  $(G_p/\omega)_{\text{max}}$  is the maximum parallel conductance  $G_p$ normalized by angular frequency  $\omega$ , q is the charge,  $f_D(\sigma_s)$ is the universal function of the standard deviation of band bending  $\sigma_s$ , and A is the capacitor area. The conductance method was performed from 89 K-300 K to allow sampling of the  $D_{it}$  distribution at various ranges of the bandgap, where eq. 5 can be applied to show the distribution of  $D_{it}$  as a function of energy within the Ge bandgap.  $f_D(\sigma_s)$  is determined by fitting the approximate width of the conductance  $(G_n/\omega)$  plot to established metrics, as discussed in [23]. Fig. 8 shows the extracted  $D_{it}$  as a function of  $E_t - E_i$ . A peak  $D_{it}$  of  $1.09 \times 10^{12}$  cm<sup>-2</sup> ev<sup>-1</sup> was observed close to the conduction band edge,  $E_C$ , while a minimum  $D_{it}$  of  $8.55 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> was observed approximately 0.15 eV away from  $E_C$ . Moreover, the  $D_{it}$  numbers are consistent with the *FLE* calculations, with higher  $D_{it}$  being responsible for Fermi level pinning, and therefore a lower FLE.

**FIGURE 8.**  $D_{ft}$  as a function of energy of the Al/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS capacitor on Si via a composite AlAs/GaAs buffer architecture. (Insets) *C-V* measurement of the device at 200 and 250 K, showing inversion response.

Furthermore, the correlation between the extracted  $D_{it}$ and *FLE* are consistent with correlations reported elsewhere [19], [25]. The extracted  $D_{it}$  numbers are comparable to some of the values reported for the state-of-the-art bulk Ge MOS devices [26], which suggests both excellent passivation of the Ge surface as well as a defect-minimal Ge epitaxy on Si. The higher  $D_{it}$  extracted from the 200 K - 300 K measurements reflect an upper bound due to the temperature-dependent supply of minority carriers to the inversion layer which contribute to higher conductance, and thus lead to an overestimation of  $D_{it}$  [13], [22]. The insets of Fig. 8 show the inversion response of the device at both 200 and 250 K, which is due to the minority carrier response. The inversion response is also apparent from C-V measurements at 300 K, as shown in Fig. 5(c).

## **IV. CONCLUSION**

In summary, high-quality epitaxial Ge was grown on composite large bandgap AlAs/GaAs buffer heterogeneously integrated on Si substrate. NMOS capacitors were fabricated from the aforementioned material stack for the first time. Distinct, well-defined Ge, AlAs, and GaAs peaks were observed from simulated and experimental [10] x-ray rocking curves. In addition, negligible interdiffusion of the underlying buffer into the epitaxial Ge, as confirmed by SIMS, EDS elemental mapping, and EDS line profile, further demonstrate the successful growth of a high-quality epitaxial Ge layer. The fabricated NMOS devices demonstrated excellent electrical characteristics with efficient modulation of the Fermi level from midgap to near the conduction band edge and a peak FLE of 27.5% corresponding to the low  $D_{it}$  value of  $8.55 \times 10^{11}$  cm<sup>-2</sup> ev<sup>-1</sup> Moreover, 300 K frequency dispersion was found to be as low as 1.80% per decade and a low frequency-dependent  $V_{FB}$  shift

of 153 mV was observed, confirming low  $D_{it}$  near the conductance band edge. Furthermore, limited C-V stretch-out was observed confirming low  $D_{it}$  throughout the upper half of the Ge bandgap. The high-quality growth of epitaxial Ge on AlAs/GaAs buffer heterogeneously integrated on Si substrate and the superior electrical characteristics of the heterogeneously integrated Ge NMOS devices suggest the viability of future high-mobility channel material integration on Si *via* large bandgap buffer architectures for high-speed, low-voltage, high-performance CMOS logic applications.

#### ACKNOWLEDGMENT

The authors would like to thank the Virginia Tech Nanofabrication Laboratory and the Institute for Critical Technology and Applied Sciences' Nanoscale Characterization and Fabrication Laboratory for support in materials characterization and device fabrication.

#### REFERENCES

- M. K. Hudait, "Heterogeneously integrated III-V on silicon for future nanoelectronics," *ECS Trans.*, vol. 45, no. 3, pp. 581–594, May 2012.

R. Pillarisetty, "Academic and industry research progress in ger-

- [2] R. Pillarisetty, "Academic and industry research progress in germanium nanodevices," *Nature*, vol. 479, no. 7373, pp. 324–328, Nov. 2011.

- [3] M. Zhu, H. Chin, G. S. Samudra, and Y. Yeo, "Fabrication of p-MOSFETs on germanium epitaxially grown on gallium arsenide substrate by chemical vapor deposition," *J. Electrochem. Soc.*, vol. 155, no. 2, pp. H76–H79, 2008.

- [4] M. Bosi and G. Attolini, "Germanium: Epitaxy and its applications," *Progr. Cryst. Growth Charact. Mater.*, vol. 56, nos. 3–4, pp. 146–174, Sep./Dec. 2010.

- [5] M. K. Hudait, Y. Zhu, N. Jain, and J. L. Hunter, Jr., "Structural, morphological, and band alignment properties of GaAs/Ge/GaAs heterostructures on (100), (110), and (111)A GaAs substrates," J. Vac. Sci. Technol. B, vol. 31, no. 1, Jan./Feb. 2013, Art. ID 011206.

- [6] M. K. Hudait, Y. Zhu, N. Jain, and J. L. Hunter, Jr., "In situ grown Ge in an arsenic-free environment for GaAs/Ge/GaAs heterostructures on off-oriented (100) GaAs substrates using molecular beam epitaxy," *J. Vac. Sci. Technol. B*, vol. 30, no. 5, Sep. 2012, Art. ID 051205.

- [7] Y. Bai, K. E. Lee, C. Cheng, M. L. Lee, and E. A. Fitzgerald, "Growth of highly tensile-strained Ge on relaxed InxGa1xAs by metal-organic chemical vapor deposition," *J. Appl. Phys.*, vol. 104, no. 8, 2008, Art. ID 084518.

- [8] S. H. Tang *et al.*, "High quality Ge thin film growth by ultrahigh vacuum chemical vapor deposition on GaAs substrate," *Appl. Phys. Lett.*, vol. 98, no. 16, Apr. 2011, Art. ID 161905.

- [9] P. S. Goley and M. K. Hudait, "Germanium based field-effect transistors: Challenges and opportunities," *Materials*, vol. 7, no. 3, pp. 2301–2339, Mar. 2014.

- [10] M. K. Hudait, M. Clavel, P. Goley, N. Jain, and Y. Zhu, "Heterogeneous integration of epitaxial Ge on Si using AlAs/GaAs buffer architecture: Suitability for low-power fin field-effect transistors," *Sci. Rep.*, vol. 4, pp. 6964–6970, Nov. 2014.

- [11] L. Hutin *et al.*, "GeOI pMOSFETs scaled down to 30-nm gate length with record off-state current," *IEEE Electron Device Lett.*, vol. 31, no. 3, pp. 234–236, Mar. 2010.

- [12] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd ed. Hoboken, NJ, USA: Wiley, 2006.

- [13] K. Martens *et al.*, "On the correct extraction of interface trap density of MOS devices with high-mobility semiconductor substrates," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 547–556, Feb. 2008.

- [14] A. Delabie *et al.*, "Effective electrical passivation of Ge(100) for high-k gate dielectrics layers using germanium oxide," *Appl. Phys. Lett.*, vol. 91, no. 8, Aug. 2007, Art. ID 082904.

- [15] F. Bellenger et al., "Passivation of Ge(100)/GeO<sub>2</sub>/high-k gate stacks using thermal oxide treatments," J. Electrochem. Soc., vol. 155, no. 2, pp. G33–G38, 2008.

- [16] R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, "Highmobility Ge pMOSFET with 1-nm EOT Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stack fabricated by plasma post oxidation," *IEEE Trans. Electron Devices*, vol. 59, no. 2, pp. 335–341, Feb. 2012.

- [17] J. Maserjian, G. Peterson, and C. Svensson, "Saturation capacitance of thin oxide MOS structures and the effective surface state density of silicon," *Solid-State Electron.*, vol. 17, pp. 335–339, Apr. 1974.

- [18] C.-W. Cheng, G. Apostolopoulos, and E. A. Fitzgerald, "The effect of interface processing on the distribution of interfacial defect states and the C-V characteristics of III-V metal-oxide-semiconductor field effect transistors," J. Appl. Phys., vol. 102, no. 2, Jan. 2011, Art. ID 023714.

- [19] C. Lin *et al.*, "Achieving a low interfacial density of states with a flat distribution in high-k Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) directly deposited on Ge," *Appl. Phys. Exp.*, vol. 4, no. 11, Nov. 2011, Art. ID 111101.

- [20] H. C. Lin *et al.*, "The Fermi level efficiency method and its applications on high interface trap density oxide-semiconductor interfaces," *Appl. Phys. Lett.*, vol. 94, no. 15, Apr. 2009, Art. ID 153508.

- [21] W. Shockley and W. T. Read, "Statistics of the recombination of holes and electrons," *Phys. Rev.*, vol. 87, no. 5, pp. 835–842, Sep. 1952.

- [22] D. Kuzum, "Interface-engineered Ge MOSFETs for future high performance CMOS applications," Ph.D. dissertation, Dept. Electr. Eng., Stanford Univ., Stanford, CA, USA, Dec. 2009.

- [23] J. R. Brews, "Rapid interface parametrization using a single MOS conductance curve," *Solid State Electron.*, vol. 26, no. 8, pp. 711–716, Aug. 1983.

- [24] E. H. Nicollian and J. R. Brews, MOS Physics and Technology. Hoboken, NJ, USA: Wiley, 2003.

- [25] N. Miyata, A. Ohtake, M. Ichikawa, T. Mori, and T. Yasuda, "Electrical characteristics and thermal stability of HfO<sub>2</sub> metaloxide-semiconductor capacitors fabricated on clean reconstructed GaSb surfaces," *Appl. Phys. Lett.*, vol. 104, no. 23, Jun. 2014, Art. ID 232104.

- [26] Q. Xie et al., "Germanium surface passivation and atomic layer deposition of high-k dielectrics—A tutorial review on Ge-based MOS capacitors," *Semicond. Sci. Technol.*, vol. 27, no. 7, Jun. 2012, Art. ID 074012.

**PATRICK S. GOLEY** (S'10) received the B.S. degree in electrical engineering from Virginia Tech in 2013, where he is currently pursuing the M.S. degree with the Bradley Department of Electrical and Computer Engineering. His research interests include semiconductor lattice engineering, especially for integration of optoelectronics onto Si, and characterization of epitaxial layer structures by transmission electron microscopy.

JHENG-SIN LIU (S'15) received the B.S. degree in electrical engineering from the National Tsing Hua University, Hsingchu, Taiwan, in 2011, and the M.S. degree from the Graduate Institute of Photonics and Optoelectronics, National Taiwan University, Taiwan, in 2013. He is currently pursuing the Ph.D. degree with the Bradley Department of Electrical and Computer Engineering, Virginia Tech. His research interests include modeling and MBE growth of mixed arsenide/antimonide-based tunnel FETs heterogeneously integrated on Si for

ultralow power logic applications.

**NOAH P. ALLEN** (S'15) received the B.S. degree in electrical engineering from Georgia Tech in 2009, the M.S. degree in electrical engineering from the Bradley Department of Electrical and Computer Engineering, Virginia Tech in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering. His research interests include semiconductor device characterization and AlGaN/GaN HFET design and fabrication.

**PETER D. NGUYEN** (S'13) received the B.S. degree in electrical engineering from Virginia Tech in 2014, where he is currently pursuing the M.S. degree with the Bradley Department of Electrical and Computer Engineering. His research interests include design, characterization, and fabrication of Ge-based MOSFET and FinFET devices on novel buffer architectures heterogeneously integrated on Si for high mobility and low-power logic applications.

publication.

LOUIS J. GUIDO, photograph and biography not available at the time of

**MANTU K. HUDAIT** (M'08–SM'08) received the M.S. degree from the Indian Institute of technology, Kharagpur, India, and the Ph.D. degree from the Indian Institute of Science, Bangalore, in 1999, both in materials science and engineering. From 2000 to 2005, he was a Post-Doctoral Researcher with Ohio State University and worked on the mixed cation and mixed anion metamorphic buffer, low bandgap thermophotovoltaics, and heterogeneous integration of III-V solar cells on Si. From 2005 to 2009, he was a Senior Engineer with the

Advanced Transistor and Nanotechnology Group, Intel Corporation. His breakthrough research in low-power InGaAs quantum-well transistor on Si at Intel Corporation was press released in 2007 and 2009. In 2009, he joined the Bradley Department of Electrical and Computer Engineering, Virginia Tech, as an Associate Professor. His current research focuses on heterogeneous integration of compound semiconductors and Ge on Si for tunnel transistors, quantum-well transistors, tunable tensile strain Ge photonics, photovoltaics, III-V compound semiconductor epitaxy, metamorphic buffer and mixed As-Sb, and mixed As-P based devices. He has over 145 technical publications and refereed conference proceedings and holds 47 U.S. patents. He was a recipient of the Divisional Recognition Awards twice from Intel Corporation. He is a member of the American Vacuum Society and the American Society for Engineering Education.

**MICHAEL BRIAN CLAVEL** (S'09) received the B.S. degree in electrical engineering from Virginia Tech in 2013, where he is currently pursuing the Ph.D. degree with the Bradley Department of Electrical and Computer Engineering. His research interests include design and MBE growth of IV/III-V heterostructure tunnel FET structures, material characterization, device fabrication, and the heterogeneous integration of high mobility and low-power logic devices on Si for next-generation CMOS applications.