Received January 21, 2019, accepted February 8, 2019, date of publication February 28, 2019, date of current version March 18, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2902246

# Heterojunction Diode Shielded SiC Split-Gate Trench MOSFET With Optimized Reverse Recovery Characteristic and Low Switching Loss

## JUNJIE AN<sup>1</sup> AND SHENGDONG HU<sup>[]</sup>2,3

<sup>1</sup>Development Division, Device Development Department, Fuji Electric Co., Ltd., Nagano 390-0821, Japan

<sup>2</sup>Key Laboratory of Dependable Service Computing in Cyber Physical Society, Ministry of Education, College of Communication Engineering, Chongqing University, Chongqing 400044, China

<sup>3</sup>Chongqing Engineering Laboratory of High Performance Integrated Circuits, College of Communication Engineering, Chongqing University, Chongqing 400044, China

Corresponding author: Shengdong Hu (hushengdong@hotmail.com)

This work was supported in part by the National Natural Science Foundation of China under Grant 61574023 and Grant 61604024, in part by the Fundamental Research Funds for the Central Universities under Grant 2018CDXYTX0008, and in part by the Innovation Foundation of Radiation Application under Grant KFZC2018040207.

**ABSTRACT** A split-gate SiC trench MOSFET with a hetero-junction diode (HJD) is proposed and numerically analyzed in this paper. The proposed structure features the HJD to effectively suppress the turn-on of the parasitic body diode and reduce the depletion region in the JFET area. A P+ shielding layer surrounding the HJD and the gate oxide layer is used to alleviate the concentration of the electric field under the gate trench and improve the switching performance. As a result, not only the breakdown voltage is increased by 20.8% at the same level of the on-state resistance but also the miller charge and the switching loss of the proposed structure are reduced by 52% and 39.1%, respectively when compared with those of the conventional SiC trench MOSFET.

**INDEX TERMS** Silicon carbide, heterojunction diode, high breakdown voltage, low on-state resistance, low switching loss.

#### I. INTRODUCTION

Because of the high power density of the cell-pitch, silicon carbide (SiC) trench MOSFET with the ultra-low on-state resistance and excellent switching characteristic is commonly recognized as to be one of the best candidates used in the power systems [1]-[3]. Recently, many studies about the device structures have been conducted for SiC devices [4]–[9]. A critical issue for the SiC trench MOSFET is to increase the gate oxide reliability at the trench bottom but without increasing of the resistance of junction field-effect transistor (JFET) area. Conventional SiC trench MOSFET (C-TMOS) with the shielding structure and carrier spreading layer (CSL) by using a high doping P+ layer and n layer under the trench oxide layer and channel, respectively, is one of the solutions to get a tradeoff between gate reliability and JFET resistance. The advantage of the C-TMOS over the planar one has been experimental demonstrated in [10]-[13]. Usually, when the C-TMOS operates in the power system, a SiC Schottky barrier diode (SiC SBD) should be in parallel with it to prevent aged deterioration due to the bipolar operation of the parasitic body diode. This can lead to the extra chip cost, power system loss, and undesirable stray inductance. Those factors generate the new challenges to the design of the C-TMOS.

Several literatures about the optimized structures have been proposed recently by the experimental demonstration or the numerical analysis, aiming to decreasing power system loss, improving the reverse recovery characteristic and reducing the chip cost, such as the SiC MOSFET with the merged junction barrier controlled schottky rectifier [10], the SiC MOSFET with the built-in SBD [11] and the SiC split-gate MOSFET with merged SBD [12]. In addition, an SBD-wallintegrated SiC trench MOSFET (SWITCH-MOS) is provided in [13] and presents a result of the mitigation of the forward degradation under extremely high current density condition. However, those devices still face the problems of the complex and costly for the requirement of extra photolithography and fabrication process. Especially, the SBD structure closed to the gate electrode cannot avoid introducing the metallization

The associate editor coordinating the review of this manuscript and approving it for publication was Ramani Kannan.

contamination to the gate oxide layer, leading to the reliability and unstable problems for the gate oxide layer and threshold voltage [14].

Heterojunction diode (HJD) combined with the Poly-Si and SiC has considerable impact as regards of achieving the good reverse recovery because of unipolar action similar with that of the SiC SBD [15], [16]. The HJD is thus to be considered as a new option to not only improve the device performance but also reduce the whole power system cost.

In this paper, a novel split-gate SiC trench MOSFET with the P-poly/SiC heterojunction diode (HJD-STMOS) is proposed and analyzed by the numerical simulation. The proposed structure has a trench gate composed of the split-gate electrode and the thicker P-poly to reduce the total gate charge and optimize the switching performance. In order to further increase the breakdown voltage (BV) of the device and eliminate the dynamic degradation induced by the float P+ shielding layer [17], a grounded P+ shielding layer is introduced and surrounded the whole P-poly. Due to the merged HJD structure, the proposed device does not require an anti-parallel SiC SBD at reverse conduction. The simulation results show that this new structure greatly improves the on-state and the reverse recovery characteristics and decreases the power loss without increasing of the extra fabrication process compared with the C-TMOS.

#### **II. DEVICE STRUCTURE AND BASIC SETUP**

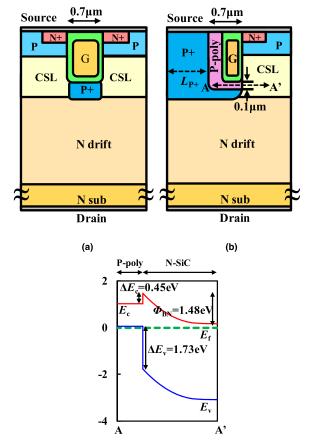

Figs. 1(a) and (b) show the schematic structure of the C-TMOS and the proposed HJD-STMOS. Compared with the C-TMOS, the proposed HJD-STMOS has a split gate and a HJD structure surrounding the gate oxide layer. The split gate means that only half of trench space is used for the gate electrode, and the other is thicker P-poly which is one part of the HJD structure. In order to classify the mechanism of the HJD structure, the Energy-band diagrams between the P-poly region and the SiC CSL in the thermal equilibrium state are shown in Fig. 1(c). The energy gaps of the HJD for conduction and valence bands are 0.45 eV and 1.73 eV, respectively. The barrier height  $\Phi_{BN}$  for electrons is determined by the Fermi level energy  $E_{\rm f}$  and the peak of the conduction band  $E_c$ , which is about 1.48 eV. This barrier height gives the HJD the small forward voltage  $(V_{\rm F})$  and high breakdown voltage (BV) when the device is forward and reverse biased, respectively, making the HJD operation as the SBD. In addition, a grounded P+ shielding layer is surrounded the whole P-poly and gate oxide layer to reduce the electric field in the P-poly and the gate oxide layer and to eliminate the dynamic degradation. In order to reduce the process defect to the device characteristics, the P+ shielding layer as well as the floating guard rings are formed at same time by a heavy dose aluminum implantation at 500 °C ambient temperature at first.

To make a fair comparison, the C-TMOS and the HJD-STMOS keep the same doping profiles and the closed device dimensions. The thickness and the doping concentration of the drift layer are 6.5  $\mu$ m and 7.5 × 10<sup>15</sup> cm<sup>-3</sup>, respectively,

FIGURE 1. Cross-sectional views of (a) C-TMOS, (b) HJD-STMOS, and (c) Band diagram along line AA.

for a 650 V rated BV. The thickness and the doping concentration of the channel layer are 0.6  $\mu$ m and 3 × 10<sup>17</sup> cm<sup>-3</sup>, respectively. The width and the depth of the trench are 0.7 and 1.2  $\mu$ m, respectively. The thickness of the gate oxide layer in the wall and bottom are 60 and 120 nm, respectively. The thickness of P-poly under the gate oxide layer is 0.1  $\mu$ m and the gate electrode for the HJD-STMOS is 0.3  $\mu$ m based on the process limitation. The doping concentration of CSL is  $2 \times 10^{16}$  cm<sup>-3</sup>.

Devices simulations using Sentaurus TCAD [18] are deployed to reveal the electric performances of the devices. While making the simulations, SRH, AUGER, OkutoCrowell are used as recombination models to describe the trap-assisted recombination, the non-radiative process involving three carriers and the breakdown analysis, respectively. At same time DopingDependence, HighFieldSaturation and Enormal are used as mobility models. In order to fit the real device process, the trap with the doping concentration of  $5 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  is uniformly distributed at the interface between SiO<sub>2</sub> and SiC for both devices.

#### **III. RESULTS AND DISCUSSION**

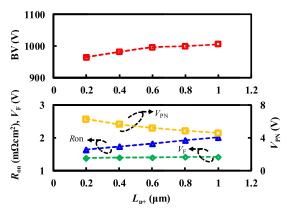

Fig. 2 shows the simulation results of the dependence of the BV, the specific on-resistance  $(R_{on})$ , the  $V_F$ , and the turn-on voltage of the parasitic body diode  $(V_{PN})$  on the width of the

**FIGURE 2.** The tradeoff results of  $L_{P+}$  as functions of the BV ( $V_{gs} = 0$  V), the  $R_{on}$  ( $V_{gs} = 15$  V), the  $V_F$  ( $V_{gs} = -5$  V) and the  $V_{PN}$  for the HJD-STMOS.

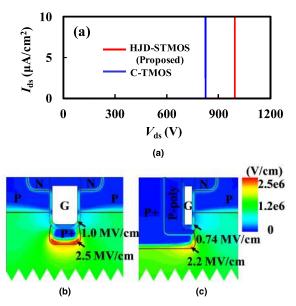

**FIGURE 3.** Breakdown characteristics of the C-TMOS and the HJD-STMOS. (a) The BVs of the C-TMOS and HJD-STMOS. (b) The electric field distribution for C-TMOS. (c) The electric field distribution for HJD-STMOS. For the electric field distributions, *V*<sub>ds</sub> is 650 V.

P+ shielding layer ( $L_{p+}$ ). As increase of the  $L_{p+}$ , the BV and  $R_{on}$  are increased while the opposite results can be achieved for the  $V_{PN}$ . The BV curve is gradually smooth when the  $L_{p+}$  increase to 0.6  $\mu$ m. This is because the electric field crowding is mainly located at the junction corner of the P+ shielding layer. This electric field concentration is no longer relieved when the  $L_{p+}$  increases to its limitation. The change of the  $V_F$  is not obvious with different  $L_{p+}$ . Although the thin P-poly of 0.1  $\mu$ m is used in the HJD-STMOS, the optimized  $V_{PN}$  of 5.2 V is over two times larger than the turn-on voltage of pn junction (~2.5V), indicating a good suppression in turn-on of the body diode.

The optimized  $L_{P+}$  for the HJD-TMOS is set to be 0.6  $\mu$ m. The BVs of two optimized devices are shown in Fig. 3 (a). As shown in Fig. 3(b) and (c), since the electric fields of both devices can be significantly reduced in the gate oxide layer at the drain-source voltage of 650 V, the electric field of the HJD-STMOS in P+ shielding layer is much lower compared with that of the C-TMOS due to the wider  $L_{p+}$ . In addition, the electric field of 0.74 MV/cm in the trench corner makes the proposed structure has a high level gate reliability.

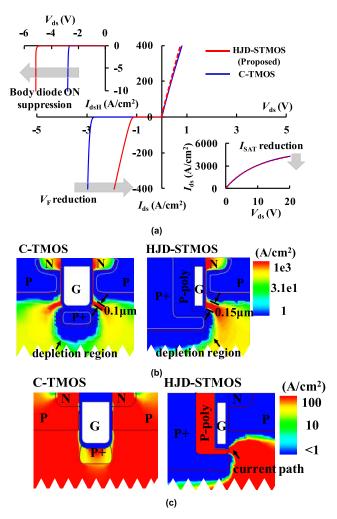

Fig. 4 (a) shows the first- and third-quadrant I-V characteristics of the C-TMOS and the HJD-STMOS at the gate voltage ( $V_{gs}$ ) of 15 and -5 V, respectively. Although the forward characteristic of the HJD-STMOS at current density of 100 A/cm<sup>2</sup> is better than that of the C-TMOS due to the optimized depletion area in the JFET region, which can be seen in Fig 4 (b), the saturation current of the proposed HJD-STMOS is smaller than that of the C-TMOS, leading to a promising short-circuit capability. As shown in Fig. 4 (c), because the current can flow from the HJD structure when device is reverse conduction, the reverse  $V_F$  of the HJD-STMOS is much lower than that of C-TMOS (body diode

**FIGURE 4.** (a) Forward I-V and reverse conduction characteristics of the two devices at  $V_{gs} = 15$  and -5 V, respectively. The  $I_{dsH}$  as a function of the  $V_{ds}$  in the insert picture shows a significant suppression in body diode ON and the saturation current for HJD-STMOS. The active area of each device is 1 cm<sup>2</sup>. (b) The current distribution of the two devices at current density of 100 A/cm<sup>2</sup> at  $V_{gs} = 15$  V. (c) The current distribution of the two devices at the two devices at current density of -100 A/cm<sup>2</sup> at  $V_{gs} = -5$  V.

operation), leading to the remarkable reduction in dead-time loss. Moreover, the drain hole current ( $I_{dsH}$ ) as a function of the  $V_{ds}$  in the insert picture shows that the  $V_F$  of the optimized HJD-STMOS is increased to -5.19 V at the  $I_{dsH}$  of 10 A/cm<sup>2</sup>, indicating a significant suppression of the turn-on of the P-well/N-drift junction.

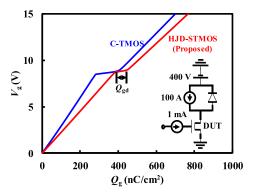

Gate charges for both devices extracted from numerical simulation are shown in the Fig. 5. Due to similar height of miller plateau, the both devices have similar threshold voltage. Since the gate charge required to reach the plateau voltage increases because of the shortened of distance of the gate and source electrodes, the ultra-small gate-to-drain charge ( $Q_{gd}$ ) of the proposed structure with 60 nC/cm<sup>2</sup>, which is 52% smaller than that of the C-TMOS (125 nC/cm<sup>2</sup>), resulting in a dramatic reduction in power loss. The electrical characteristics of the C-TMOS and the HJD-STMOS are summarized in Table 1.

**FIGURE 5.** Gate charge test of the C-TMOS and the HJD-STMOS. The insert picture is test circuit.

TABLE 1. Device characteristics.

| Symbol               | C-TMOS | HJD-STMOS<br>(Proposed) | Unit               |

|----------------------|--------|-------------------------|--------------------|

| BV                   | 824    | 993                     | V                  |

| ${R_{ m on}}^*$      | 1.87   | 1.82                    | $m\Omega$ · $cm^2$ |

| $Q_{ m GD}$          | 125    | 60                      | nC/cm <sup>2</sup> |

| $V_{\mathrm{F}}^{*}$ | 2.9    | 1.4                     | V                  |

\*  $I_{\rm ds}$ = 100/-100 A/cm<sup>2</sup>,  $V_{\rm gs}$ =15/ -5 V.

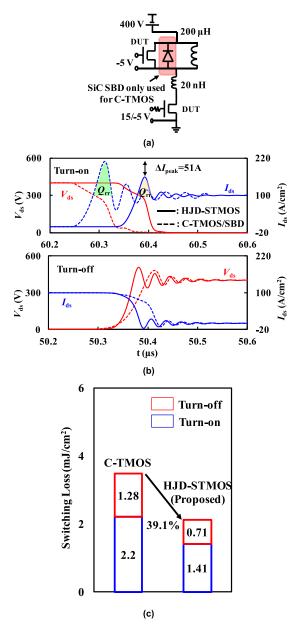

The switching test circuit and characteristics of the both devices are shown in Fig. 6. Although a SiC SBD is anti-paralleled with the C-TMOS, the reverse recovery charge  $(Q_{\rm rr})$  of the proposed HJD-STMOS is great reduced while the reverse recovery current spike of the proposed one is 51 A (24% reduction) smaller than that of the C-TMOS/SBD during the turn-on state. The switching loss of the C-TMOS and the HJD-STMOS are shown in Fig 6 (c). The switching loss of the proposed HJD-STMOS reduces 39.1% when compared with that of the C-TMOS. This is due to the smaller  $Q_{\rm gd}$  and excellent reverse recovery characteristic compared with the C-TMOS. Therefore, the merged HJD structure and the optimized P+ shielding layer play the critical roles to

**FIGURE 6.** (a) Double pulse test circuits and (b) switching waveforms of the C-TMOS/SBD and the HJD-STMOS at the drain current of 100 A/cm<sup>2</sup>. The minority carrier lifetime of each device is 1.2  $\mu$ s. The active area of anti-parallel SBD for the C-TMOS is 1 cm<sup>2</sup>.

contribute the device with the low switching loss, resulting in the advanced device performance.

#### **IV. CONCLUSIONS**

A novel SiC HJD-STMOS is proposed in this paper, which features a heterojunction diode and a high doping P+ type shielding layer with the grounded connection to reduce the JFET resistance and protect the gate oxide corner from the concentration of the electric field. The outstanding characteristics with the improved breakdown voltage, on-state resistance, reverse recovery characteristic and switching performance make the proposed HJD-STMOS to be a superior candidate for power system applications.

### REFERENCES

- T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices, and Applications. Singapore: Wiley, 2014.

- [2] M. Jin, Q. Gao, Y. Wang, and D. Xu, "A temperature-dependent SiC MOSFET modeling method based on MATLAB/simulink," *IEEE Access*, vol. 6, pp. 4497–4505, Nov. 2018.

- [3] J. Zhang, J. Zhao, Y. Zhang, and Y. Zhu, "A resonant gate driver for silicon carbide MOSFETs," *IEEE Access*, vol. 6, pp. 78394–78401, Dec. 2018.

- [4] J. An, M. Namai, H. Yano, and N. Iwamuro, "Investigation of robustness capability of -730 V P-channel vertical SiC power MOSFET for complementary inverter applications," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4219–4225, Oct. 2017.

- [5] H. Jiang, J. Wei, X. Dai, M. Ke, I. Deviny, and P. Mawby, "SiC trench MOSFET with shielded fin-shaped gate to reduce oxide field and switching loss," *IEEE Electron Device Lett.*, vol. 37, no. 10, pp. 1324–1327, Oct. 2016.

- [6] L. D. Benedetto, G. D. Licciardo, T. Erlbacher, A. J. Bauer, R. Liguori, and A. Rubino, "A model of electric field distribution in gate oxide and JFETregion of 4H-SiC DMOSFETs," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3795–3799, Sep. 2016.

- [7] S. Harada *et al.*, "3.3-kV-class 4H-SiC MeV-implanted UMOSFET with reduced gate oxide field," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 314–316, Mar. 2016.

- [8] Y. Wang, K. Tian, Y. Hao, C. Yu, and Y. Liu, "4H-SiC step trench gate power metal-oxide-semiconductor field-effect transistor," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 633–635, May 2016.

- [9] D. Bharti and A. Islam, "Optimization of SiC UMOSFET structure for improvement of breakdown voltage and ON-resistance," *IEEE Trans. Electron Devices*, vol. 65, no. 2, pp. 615–621, Feb. 2018.

- [10] F.-J. Hsu *et al.*, "High efficiency high reliability SiC MOSFET with monolithically integrated Schottky rectifier," in *Proc. IEEE 29th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Sapporo, Japan, May 2017, pp. 45–48.

- [11] W. Sung and B. J. Baliga, "Monolithically integrated 4H-SiC MOSFET and JBS diode (JBSFET) using a single ohmic/Schottky process scheme," *IEEE Electron Device Lett.*, vol. 37, no. 12, pp. 1605–1608, Dec. 2016.

- [12] H. Jiang, J. Wei, X. Dai, M. Ke, C. Zheng, and I. Deviny, "Silicon carbide split-gate MOSFET with merged Schottky barrier diode and reduced switching loss," in *Proc. IEEE 28th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Prague, Czech Republic, Jun. 2016, pp. 59–62.

- [13] Y. Kobayashi et al., "Body PiN diode inactivation with low on-resistance achieved by a 1.2 kV-class 4H-SiC SWITCH-MOS," in *IEDM Tech. Dig.*, San Francisco, CA, USA, 2017, pp. 9.1.1–9.1.4.

- [14] Y. Kobayashi, "Evaluation of Schottky barrier height on 4H-SiC m-face for Schottky barrier diode wall integrated trench MOSFET," *Jpn. J. Appl. Phys.*, vol. 56, no. 4s, p. 04CR08, Mar. 2017.

- [15] H. Tanaka, T. Hayashi, Y. Shimoida, S. Yamagami, S. Tanimoto, and M. Hoshi, "Ultra-low von and high voltage 4H-SiC heterojunction diode," in *Proc. IEEE 17th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Santa Barbara, CA, USA, May 2005, pp. 287–290.

- [16] W. Ni et al., "SiC trench MOSFET with an integrated low von unipolar heterojunction diode," *Mater. Sci. Forum*, vols. 778–780, pp. 923–926, Feb. 2014.

- [17] J. Wei, M. Zhang, H. Jiang, H. Wang, and K. J. Chen, "Dynamic degradation in SiC trench MOSFET with a floating p-shield revealed with numerical simulations," *IEEE Trans. Electron Devices*, vol. 64, no. 6, pp. 2592–2598, Jun. 2017.

- [18] TCAD Sentaurus Device Manual, Synopsys, Inc., Mountain View, CA, USA, 2016.

**JUNJIE AN** received the M.S. degree from the University of Electronic Science and Technology of China, Chengdu, China, and the Ph.D. degree from the University of Tsukuba, Tsukuba, Japan. He is currently a Researcher with Fuji Electric Co., Ltd., Matsumoto, Japan. His research interest includes the structure, process, and reliability of power semiconductor devices and their applications.

**SHENGDONG HU** received the M.S. degree in material science and engineering from Sichuan University, Sichuan, China, in 2005, and the Ph.D. degree in microelectronics from the University of Electronic Science and Technology of China, in 2010. Since 2010, he has been with Chongqing University, Chongqing, China. From 2011 to 2015, he was with the No.24 Research Institute of China Electronics Technology Group Corporation as a Postdoctoral Researcher. His current research

interest includes structure and reliability of power semiconductor devices and their applications.

...