This is an electronic reprint of the original article. This reprint may differ from the original in pagination and typographic detail.

Manessis, D.; Seckel, M.; Liu, Fu; Tsilipakos, O.; Pitilakis, A.; Tasolamprou, A.; Kossifos, K.; Varnava, G.; Liaskos, C.; Kafesaki, M.; Soukoulis, C. M.; Tretiakov, Sergei; Georgiou, J.; Ostmann, A.; Aschenbrenner, R.; Schneider-Ramelow, M.; Lang, K. D.

High frequency substrate technologies for the realisation of software programmable metasurfaces on pcb hardware platforms with integrated controller nodes

Published in: 2019 22nd European Microelectronics and Packaging Conference and Exhibition, EMPC 2019

DOI: 10.23919/EMPC44848.2019.8951834

Published: 16/09/2019

Document Version Peer reviewed version

Please cite the original version:

Manessis, D., Seckel, M., Liu, F., Tsilipakos, O., Pitilakis, A., Tasolamprou, A., Kossifos, K., Varnava, G., Liaskos, C., Kafesaki, M., Soukoulis, C. M., Tretiakov, S., Georgiou, J., Ostmann, A., Aschenbrenner, R., Schneider-Ramelow, M., & Lang, K. D. (2019). High frequency substrate technologies for the realisation of software programmable metasurfaces on pcb hardware platforms with integrated controller nodes. In *2019 22nd European Microelectronics and Packaging Conference and Exhibition, EMPC 2019* [8951834] (European Microelectronics and Packaging Conference). IEEE. https://doi.org/10.23919/EMPC44848.2019.8951834

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# High Frequency Substrate Technologies for the Realisation of Software Programmable Metasurfaces on PCB Hardware Platforms with Integrated Controller Nodes

D. Manessis<sup>1</sup>, M. Seckel<sup>1</sup>, L. Fu<sup>2</sup>, O. Tsilipakos<sup>3</sup>, A. Pitilakis<sup>3</sup>, A. Tasolamprou<sup>3</sup>, K. Kossifos<sup>4</sup>, G. Varnava<sup>4</sup>, C. Liaskos<sup>3</sup>, M. Kafesaki<sup>3</sup>, C. M. Soukoulis<sup>3</sup>, S. Tretyakov<sup>2</sup>, J. Georgiou<sup>4</sup>, A. Ostmann<sup>1</sup>, R. Aschenbrenner<sup>1</sup>, M. Schneider-Ramelow<sup>1</sup>, and K-D. Lang<sup>5</sup>

<sup>1</sup>Fraunhofer Institute for Reliability and Microintegration (IZM), Gustav-Meyer-Alle 25, 13355 Berlin, Germany <sup>2</sup>Aalta University, Dant of Flactronics & Nanoangingering, FL 00076 Aalta Finland

<sup>2</sup>Aalto University, Dept. of Electronics & Nanoengineering, FI-00076 Aalto, Finland <sup>3</sup> Foundation for Research & Technology – Hellas /FORTH, 71110 Heraklion, Crete

<sup>4</sup> University of Cyprus, Dept. of Electrical & Computer Engineering, 1678 Nicosia, Cyprus

<sup>5</sup>Technical University of Berlin, Gustav-Meyer-Alle 25, 13355 Berlin, Germany

Technical University of Berlin, Gustav-Meyer-Alle 25, 15555 Berlin, Germany

Corresponding Author: +49-30-46403788, Dionysios.Manessis@izm.fraunhofer.de

#### Abstract

The proposed work is performed in the framework of the FET-EU project "VISORSURF", which has undertaken research activities on the emerging concepts of metamaterials that can be software programmable and adapt their properties. In the realm of electromagnetism (EM), the field of metasurfaces (MSF) has reached significant breakthroughs in correlating the micro- or nano-structure of artificial planar materials to their end properties. MSFs exhibit physical properties not found in nature, such as negative or smaller-than-unity refraction index, allowing for EM cloaking of objects, reflection cancellation from a given surface and EM energy concentration in as-tight-as-possible spaces.

The VISORSURF main objective is the development of a hardware platform, the Hypersurface, whose electromagnetic behavior can be defined programmatically. The key enablers for this are the metasurfaces whose electromagnetic properties depend on their internal structure. The Hypersurface hardware platform will be a 4-layer build-up of high frequency PCB substrate materials and will merge the metasurfaces with custom electronic controller nodes at the bottom of the PCB hardware platform. These electronic controllers build a nanonetwork which receives external programmatic commands and alters the metasurface structure, yielding a desired electromagnetic behavior for the Hypersurface platform.

This paper will elaborate on how large scale PCB technologies are deployed for the economical manufacturing of the 4-layer Hypersurface PCB hardware platform with a size of 9"x12", having copper metasurface patches on the top of the board and the electronic controllers as 2mmx2mm WLCSP chips at  $400\mu m$  pitch assembled at the bottom of the platform. The PCB platform designs have stemmed from EM modeling iterations of the whole stack of high frequency laminates taking into account also the electronic features of the controller nodes. The manufacturing processes for the realization of the selected PCB architectures will be discussed in detail.

Key words: Metasurfaces, metamaterials, software defined materials, High frequency substrates.

# 1. Introduction

Metasurfaces (MSs), the two dimensional versions of metamaterials, are ultrathin periodic structures with designed, subwavelength building blocks enabling exotic functionalities [1-2]. The building blocks can consist of metallic, dielectric, semiconducting, and 2D material inclusions. Tunable metasurfaces can be realized by modifying the properties of the meta-atoms via an external stimulus, leading to adjustable and, in some cases, reconfigurable functions. The available tuning schemes can be classified as "global" or "local" depending on the ability to tune the unit cells collectively or independently. Global control of the

unit cells can, for example, enable tunable perfect absorption, whereas local control can provide more advanced functionalities such as wavefront manipulation, steering or focusing [3,4, 10-11]. An efficient control mechanism naturally suited to a *local* tuning scheme is that of *voltage-controlled* lumped electronic elements incorporated inside the meta-atom to provide control over the MS properties [5,6, 10-11]. In the framework of the VISORSURF project this is accomplished by specifically-designed integrated circuits (chips), embedded in the metaatoms. The control of the circuits can be softwaredriven and the behavior of the metasurface can be defined programmatically; this is the concept of the HyperSurface (HFS) [7]. In addition, the controllers can be nano-networked [7-9] enabling the broad vision of smart devices in the emerging Internet of Things paradigm. In this work, we present the concept of the Hypersurfaces with a focus on their electromagnetic aspects [10-11].

# 2. The Hypersurface Concept of The Visorsurf project

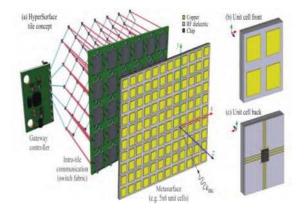

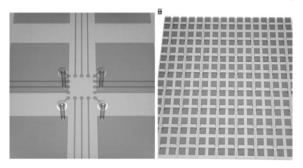

The functional and physical architecture of the Hypersurface tile is presented in Fig. 1(a) and it consists of a metasurface layer, an intra-tile control layer and a tile gateway controller. This paper focuses on the metasurface layer which realizes the electromagnetic functionalities. In the overall concept of the HFSs, there is a switch fabric design for operation in the microwave (GHz) regime.

The unit cell of the switch fabric is presented in Fig. 1(b). It consists of four copper patches (size is in millimeter range) residing on a low-loss dielectric substrate backed by a copper plate. A chip is attached in each unit cell, lying behind the copper plate, shown in Fig. 1(c), and its physical dimensions are also subwavelength. The chips are interconnected by means of communication tracks. The four patches are connected to the RF ports of the chip by means of through vias. When microwave radiation impinges on the chip-loaded unit cell, it induces local currents in the patches and the metallic substrate; in turn, the induced currents act as secondary electromagnetic sources modifying the scattered field which leads to the desired operation, when the aggregate effect of all unit cells of the metasurface is accounted for. Consequently, for the modification of the metasurface response, one needs to adjust dynamically the complex-valued surface impedance in each unit cell. This is achieved with the controller chip [Fig. 1(c)], which is judiciously placed behind the backplate in order to minimize interference with the impinging electromagnetic wave. By controlling the resistive and reactive contributions in each chip we can demonstrate an angle-tunable perfect absorber that can operate inside the 4.5-5.5 GHz range, and more advanced functionalities of wavefront manipulation such as anomalous reflection [10-11]. This paper describes in detail the manucturability of such large metasurface panels based on standard industrial PCB processes conducted in the Substrate line of Fraunhofer IZM.

Figure 1:(a) The HyperSurface tile. The switch state configuration setup provides the desired function. A controller intra-network communicates the relevant commands and the inter-tile and external communication are handled by standard gateway hardware, such as an FPGA. Unit cell of the metasurface: (b) front side with periodic square 2x2 patches pattern and (c) back side with controller chip (dark grey box) and communication lines.

# 3. Manufacturing feasibility study on 3-layer HSF substrate

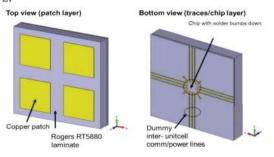

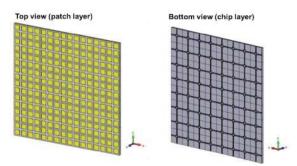

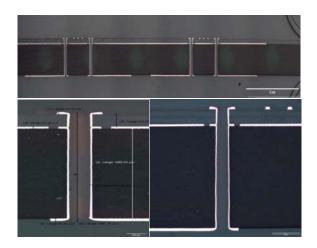

This Section presents the first manufacturing results of a 3-layer HSF substrate using a stack of a HF Rogers laminate material and a high-Tg FR4 The first 3-layer HSF substrate was material. constituted of a thick HF laminate based on Rogers RT5880 laminate and an underlying conventional high-Tg PCB prepreg. Figure 2 shows a perspective of a single unit cell from its top side which is the patch layer and its bottom side which is the chip layer. The copper patch is 4.2mm scquare; the space between them is 0.8mm. The HSF substrate consisted of 8 single unit cells with a final size of 96mmx96mm, and is shown in the bottom of Figure 2.

Figure 2: Perspective of a single unit cell and the whole HSF consisted of 8 single unit cells (96mmx96mm).

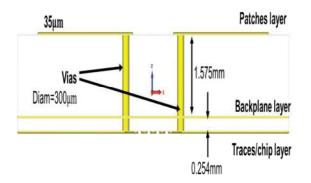

The geometrical design of the 3-layer board is shown in Figure 3 where the copper layer (1 st layer), the ground backplane layer ( $2^{nd}$  layer) and the chip/copper trace layer ( $3^{nd}$  layer) can be distinguished. The copper layers were  $35\mu$ m thick and the high frequency RT5880 laminate was 1.575 mm whereas the underlying Hitachi 679FGS prepreg was 0.254mm. The whole thickness of the HSF substrate was targeted to be 1.934mm. There were 4 through vias from the patch layer to the chip layer which were mechanically drilled and had a diameter of  $300\mu$ m.

### Figure 3: Geometrical cross section of the 3-layer HSF stack-up. Total estimated thickness is 1.934mm.

After the drilling of the vias, a typical permanganate desmear process was followed to clean the via from rest of the RT5880 material. However, such desmear process is not appropriate for RT5880 material and the copper has not really stuck to the via walls. No copper electroplating has taken place in the through vias.

Although repeated desmear processes were run with various parameters, the vias could not be cleaned efficiently and could not be electroplated at all. Therefore, the recommended process for Teflon based laminates was followed which is a plasma process. After 20 min plasma desmear, the through vias were cleaned efficiently and copper electroplating had been successful. Figure 4 shows cross sections of the 3-layer HSF after plasma desmear and electroplating. The copper wall thickness was increased to  $20\mu$ m as shown in Figure 4. Figure 5 shows the corresponding X-Ray from the 3-layer HSF substrate from the chip layer with the vias filled with copper (dark contrast).

Figure 4: Cross-sections of the 3-layer HSF board with the bottom RT5880 laminate layer and vias filled with copper. Vias were cleaned with plasma desmear.

Figure 5: X-Ray of the 3-layer HSF stack-up from the chip layer side view. The Chip and the 4 vias can be seen filled with copper (dark contrast) due to used plasma desmear processes in the RT5880 laminate. On the right side, a X-Ray perspective of the whole HSF substrate (96mmx96mm) is provided from the chip side.

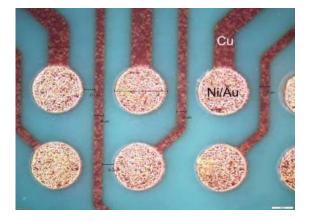

After structuring the first layer (patch layer) and the third layer (chip layer),  $5\mu$ m Ni/80nm Au was applied on both layers whereas solder mask was also coated on the chip layer. Figure 6 shows pictures of the copper patches and the chip bottom side.

# Figure 6: 3-layer HSF substrate 96mmx96mm in size.

The results provide ample evidence that the processing of RT5880 Teflon based laminate is quite challenging with conventional PCB processes and other alternative processes like plasma desmear should be employed, raising the cost of the process significantly. Furthermore, due to usage of different prepreg and laminate materials with respect to their thermal expansion coefficient, the 3-layer HSF board has shown a warpage of about 2mm, making the assembly of the controller chips on the third layer quite challenging. For these reasons, it was decided to deploy the Megtron 7N family of materials which are available both as laminates and prepregs. That would ensure the usage of uniform materials and the elimination of warpage at large production panels of 9"x12" (22cmx30cm) or 12"x12" (30cmx30cm) during the course of the project.

### 4. Manufacturing of 4-layer HSF substrate

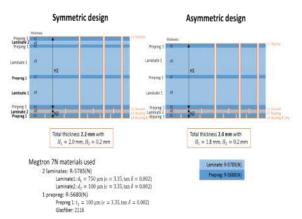

After the experience gained in the feasibility studies with the 3-layer stack and having evaluated the pros and cons of employing the Rogers RT5880 Teflon based material, the Consortium decided to switch to Megtron 7N materials which could become readily available both as prepregs and laminates and could be potentially processed with conventional PCB processes. The Megtron 7N materials were available as R-5785(N) laminates with a thickness of d<sub>1</sub>:750µm and d<sub>2</sub>: 100µm and as prepreg R-5680(N) with a glass fiber of type 2116 and a thickness of 100µm. It was decided to build a symmetric and a slightly asymmetric stack-up to evaluate the final warpage effect on a 9"x12" board. The actual PCB process sequence is not differentiated whether a symmetric or asymmetric stack up is chosen.

# Symmetric and asymmetric laminate designs for 4-layer substrate

Figure 7 shows the symmetric and asymmetric stack up next to each other for better comparison. The only slight difference between the two designs are the missing laminate  $(d_2)$  and a prepred  $(t_1)$  on top of the asymmetric design which makes it eventually slightly thinner than the symmetric one. Figure 7 shows the stack-ups used and the main vias for interconnectivity among layers; namely the L2-L3 and L1-L4 through vias as well the L4-L3 blind vias.

Figure 7: Symmetric and asymmetric stack-ups in comparison. Megtron 7N materials are being used.

# Process developments and flow for 4-layer substrate

The process flow was decided based on the design requirements and especially the fine line L/S for the chip layer where a thin copper should exist at the end of the electroplating process so as to achieve the fine L/S under the chip area. Figure 8 provides the process flow and some dimensional via details.

### Figure 8: Process flow for 4-layer HSF substrate.

# Manufacturing process results and challenges

The manufacturing of the 4-layer HSF substrate provided the first processing experience with Megtron 7N materials and yielded very good results and revealed the processing challenges that

need further developments before the launch of the next HSF substrates. Figure 9 shows a cross section of the symmetric 4-layer substrate after final processing. The thicknesses of the symmetric and asymmetric are 2.4 mm and 2.2 mm, respectively. Both values are  $200\mu$ m higher than the estimated ones, mainly attributed to deviation in prepreg and lamination thicknesses in the stack compared to nominal ones and from slightly higher copper thicknesses after electroplating on the copper layers.

Figure 9: Cross section of the 4-layer stack.

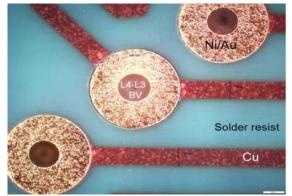

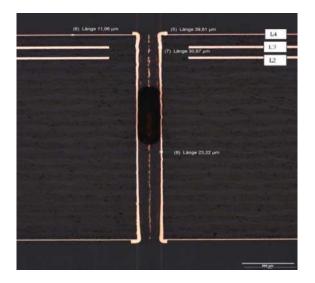

The major challenges for the 4-layer HSF substrate are the fine line structuring of the bottom chip layer, the opening of the L4-L3 blind vias and the electroplating of all vias. As shown in Figure 10, very fine L/S of  $45\mu$ m/55 $\mu$ m was successful with a copper thickness of  $15\mu$ m. The application of solder resist and the deposition of  $5\mu$ m Ni/80nm Au metallisation is also shown.

Figure 10 shows on the top the chip position where  $45\mu$ m/55 $\mu$ m Line/Spacing was achieved and at the bottom the L3-L4 blind vias and the structuring around it. A 100 $\mu$ m line was structured. The results provide ample evidence that such fine copper structuring especially under the chip area is feasible.

Figure 10: Bottom layer of HSF board at chip position. Fine line structures of 45µm/55µm L/S achieved. Structured bottom layer in proximity to L3-L4 blind vias.

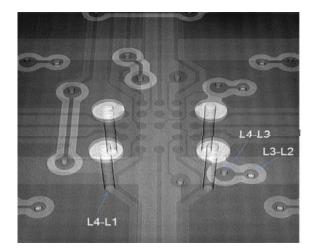

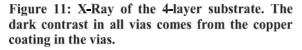

Figure 11 shows X-Ray pictures of the 4layer substrate where the copper filling of the L1-L4 vias, the L2-L3 vias and L4-L3 vias is witnessed with dark contrast. Via electroplating is successful.

The through vias L4-L1 were successfully electroplated, as shown in Figure 12. It can be seen that inside the via  $23\mu$ m were deposited and on the L1 and L4 layers the copper ring thickness was about  $40\mu$ m and away from the ring the copper remained at about  $11\mu$ m which is the ideal thickness for L1, L4 fine line structuring.

Figure 12: L4-L3-L2-L1 copper layers in a drilled through via of 250µm. Reinforced copper filling to achieve about 23µm in the via.

The blind vias L4-L3 were tried with the pico UV laser to reopen the blind vias which were initially opened by mechanical drilling. Some of the L4-L3 vias could not be efficiently opened by mechanical drilling. Few microns, around 10µm, were remaining to touch the L3 copper pad. That would be an ad-hoc solution for the boards, and mechanical drilling of all vias would be in any case preferable as a quick and economical industrial The laser was used to re-open and process. overshoot the blind vias and subsequently desmear and copper electroplating was performed. The results were very successful using the laser for the blind vias and the drilled board. In turn, the board was successfully electrically tested for continuity. Figure 13 shows the blind via, 150µm in diameter, opened with the UV laser to be also copper filled.

Figure 13: Blind via (L4-L3), 150µm in diameter, opened by UV laser and then copper coated.

The laser technology looks promising to solve the problem of drilled L4-L3 blind vias and is also compatible with filled Megtron 7N materials.

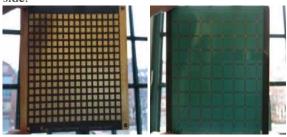

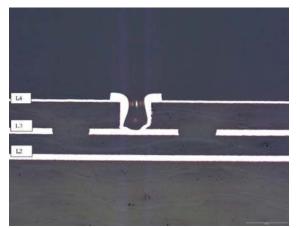

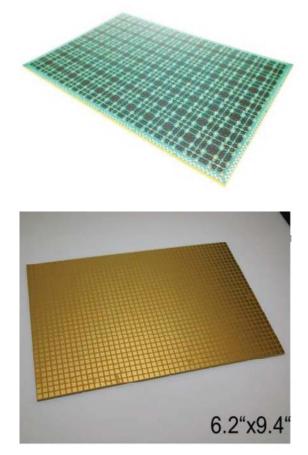

Figure 14 shows the 4-layer HSF substrate finished with solder resist on the bottom side. The warpage of the board, due to usage of uniform Megtron 7N materials, was less than  $100\mu$ m, much smaller than the warpage of the 3-layer RT5880 board and is considered minimal from EM considerations.

The resultant HSF prototype has a net area of 6.2"x9.4" and containts 384 unit cells. It is electrically functionable and proves that the 4-layer HSF is manufacturable.

Figure 14: Bottom side (chip layer) and HSF unit cell area with Ni/Au metallization (top layer) of the 4-layer HSF substrate (net area of 6.2"x9.4", 384 unit cells)

### Conclusions

This paper has presented the concept of Hypersurfaces, i.e., the approach of project VISORSURF to software-driven metasurfaces whose complex surface impedance can be locally modified with a set of programmable commands. The control is enabled by a network of voltagedriven electronic chips; they provide variable resistance and reactance values that modify the complex surface impedance of the metasurface in a local or a global manner. This paper also provides the first manufactured Hypersurfaces on panels employing industrial PCB processes. Hypersurfaces were made on a 3-layer and a 4-layer PCB consustruction which will be finally the HSF design for the project. The 3-layer substrate was made of a RT5880 Teflon laminate outstanding for its HF properties, but it was difficult to process with conventional chemical desmear processes and therefore the electroplating did not work. The usage of plasma desmear has solved the problem. The 3layer HSF substrate has shown high warpage due to usage of non-uniform laminates. Due to warpage and processability problems, it was decided to use Megtron 7N materials available as laminates and prepregs. A first version of the VISORSURF 4layer substrate is already manufactured. Very fine structuring of  $45\mu$ m/55 $\mu$ m L/S was successfully demonstrated at the chip level. Through vias were also successfully drilled and copper coated. Drilling of blind vias was not consistent and the results were not reliable. As a solution to solve the problem, pico UV laser has been employed successfully for the blind vias which were also copper coated. The warpage with the usage of uniform Megtron 7N materials remained under 100µm. Panels of 9"x12" were manufactured with a net area of 6.2"x9.4", consisted of 384 unit cells. The 4-layer HSF design is slightly modified and will be manufactured again in the next 2 months in the final size of 300mmx300mm (12"x12").

### Acknowledgements

This work was supported by European Union's Horizon 2020 Future Emerging Technologies call (FETOPEN-RIA) under grant agreement no. 736876 (project VISORSURF).

### References

- C. M. Soukoulis and M. Wegener, "Past achievements and future challenges in the development of three dimensional photonic metamaterials," *Nat. Photonics*, 5, pp. 523–530, 2011.

- [2] S. B. Glybovski, S. A. Tretyakov, P. A. Belov, Y. S. Kivshar and C. R. Simovski, "Metasurfaces: from microwave to visible," *Phys. Rep.*, 634, 1-72, 2016.

[3] O. Tsilipakos, A. C. Tasolamprou, Th.

- [3] O. Tsilipakos, A. C. Tasolamprou, Th. Koschny, M. Kafesaki, E. N. Economou and C. M. Soukoulis, "Pairing toroidal and magnetic dipole resonances in elliptic dielectric rod metasurfaces for reconfigurable wavefront manipulation in reflection," *Adv. Opt. Mater.* 6, 1800633, 2018.

- [4] F. Liu, O. Tsilipakos, A. Pitilakis, A.C. Tasolamprou, M. S. Mirmoosa, N. V. Kantartzis, D. H. Kwon, M. Kafesaki, C. M. Soukoulis, and S. A. Tretyakov, "Intelligent Metasurfaces with Continuously Tunable Local

Surface Impedance for Multiple Reconfigurable Functions," *Phys. Rev. Appl.*, accepted, 2019. *arXiv:1811.10082*, 2018.

- [5] T. J. Cui, M. Q. Qi, X. Wan, J. Zhao and Q. Cheng, "Coding metamaterials, digital metamaterials and programming metamaterials," *Light Sci. Appl.*, vol. 3, pp. 1-9, 2014.

- [6] H. Yang, X. Cao, F. Yang, J. Gao, S. Xu, M. Li, X. Chen, Y. Zhao, Y. Zheng and S. Li, "A programmable metasurface with dynamic polarization, scattering and focusing control," *Sci. Rep.*, vol. 6, 35692, 2016.

- [7] C. Liaskos, A. Tsioliaridou, A. Pitsillides et al., "Design and development of software defined metamaterials for nanonetworks," *IEEE Circuits Syst. Mag.*, vol. 15, no. 4, pp. 12–25, 2015.

- [8] S. Abadal, C. Liaskos, A. Tsioliaridou, S. Ioannidis, A. Pitsillides, J. Solé-Pareta, E. Alarcón and A. Cabellos-Aparicio, Computing and Communications for the Software-Defined Metamaterial Paradigm: A Context Analysis, *IEEE Access*, pp. 6225–6235, 2017.

- [9] H. Taghvaee, S. Abadal, J. Georgiou, A. Cabellos-Aparicio, E. Alarcón, Fault Tolerance in Programmable Metasurfaces: The Beam Steering Case, arXiv:1902.04509, 2019.

- [10] O.Tsilipakos et al., "Software-Defined Metasurfaces: The VISORSURF Project Approach", to be presented in 13<sup>th</sup> International Congress on Artificial Materials for Novel Wave Phenomena – Metamaterials 2019, Rome, Italy, Sept. 16<sup>th</sup> – Sept. 21<sup>st</sup>, 2019.

- Rome, Italy, Sept. 16<sup>th</sup> Sept. 21<sup>st</sup>, 2019.

[11] A. Tasolamprou et. al., "The Software-Defined Metasurfaces Concept and Electromagnetic Aspects", to be presented in META 2019, Lisbon Portugal, July 23 26, 2019.