## High hole mobility (≥ 500 cm<sup>2</sup>/Vs) polycrystalline Ge films on GeO<sub>2</sub>-coated glass and plastic substrates

Toshifumi Imajo, Kenta Moto, Ryota Yoshimine, Takashi Suemasu, and Kaoru Toko<sup>a)</sup>

Institute of Applied Physics, University of Tsukuba, 1-1-1 Tennodai, Tsukuba, Ibaraki 305-8573, Japan

The highest recorded hole mobility in semiconductor films on insulators has been updated significantly. We investigate the solid-phase crystallization of a densified amorphous Ge layer formed on GeO<sub>2</sub>-coated insulating substrates. The resulting polycrystalline Ge layer with a glass substrate consists of large grains (~10 µm) and exhibits a hole mobility as high as 620 cm<sup>2</sup>/Vs, despite a low process temperature (500 °C). Even for the Ge layer formed on a flexible polyimide substrate at 375 °C, the hole mobility reaches 500 cm<sup>2</sup>/Vs. These achievements will aid in realizing advanced electronics, simultaneously allowing for high performance, inexpensiveness, and flexibility.

<sup>a)</sup> Author to whom correspondence should be addressed. Electronic mail: toko@bk.tsukuba.ac.jp Monolithic integration of electronic and optoelectronic materials is a key technology for fabricating next-generation devices such as three-dimensional large-scale integrated circuits and multifunctional mobile terminals. Ge on insulator (GOI) is one of the most promising solutions for realizing advanced integrated devices because Ge has good compatibility with Si as well as high carrier mobility.<sup>1-4</sup> The process temperature for GOI is strictly limited by the thermal resistance of the substrates or underlying devices, which makes it challenging to achieve high-quality crystalline Ge thin films. So far, researchers have been investigating various techniques such as solid-phase crystallization (SPC),<sup>5-9</sup> laser annealing,<sup>10–13</sup> chemical vapor deposition,<sup>14,15</sup> flash lamp annealing,<sup>16</sup> and metal-induced crystallization.<sup>17–22</sup> However, the effective mobility of the Ge thin-film transistors (TFTs) has been no match for that of Si metal-oxide-semiconductor field-effect transistors (MOSFETs),<sup>8,9,13,16,22</sup> whereas the device technologies for Ge-MOSFETs have matured considerably.<sup>23–27</sup> Therefore, fabricating a high-quality Ge film with high carrier mobility is the most important issue to further improve Ge-TFTs.

SPC has many advantages over other methods, that is, no metal contamination, no melting-induced surface-ripples, and a simple process. However, for many years, the Hall hole mobility in conventional SPC-Ge on glass has been limited to 140 cm<sup>2</sup>/Vs by grain boundary scattering due to the small grains (< 1  $\mu$ m).<sup>5–9</sup> Since 2015, research on incorporating Sn in Ge has become active,<sup>28,29</sup> which lowered the grain boundary scattering and improved the hole mobility up to 380 cm<sup>2</sup>/Vs.<sup>30,31</sup> On the other hand, we recently found that the atomic density of amorphous Ge (a-Ge) significantly influenced subsequent SPC,<sup>32</sup> and updated the hole mobility to 450 cm<sup>2</sup>/Vs using a densified a-Ge.<sup>33</sup> This hole mobility was the highest ever recorded for a thin film directly grown on an insulator at temperatures below 900 °C.

In the present study, we focus on the underlayer material during SPC of the densified a-Ge. The crystallinity of Ge thin films is often influenced by interfacial materials, because heterogeneous nucleation at interfaces is dominant.<sup>21,29,34</sup> By using GeO<sub>2</sub>, which is also most suitable as a gate insulating material for Ge-MOSFETs,<sup>24–27</sup> we significantly break the existing record with a hole mobility of 620 cm<sup>2</sup>/Vs. Furthermore, we develop a flexible plastic substrate and achieve a hole mobility of 500 cm<sup>2</sup>/Vs even at a low temperature process up to  $375 \,^{\circ}$ C.

In the experiment, to investigate the effects of the underlayer material, we prepared a 50-nm-thick insulating layer (SiN, Al<sub>2</sub>O<sub>3</sub>, and GeO<sub>2</sub>) on a SiO<sub>2</sub> glass substrate using RF magnetron sputtering (base pressure:  $3.0 \times 10^{-4}$  Pa). After that, an a-Ge layer was prepared using a Knudsen cell of a molecular beam deposition system (base pressure:  $5 \times 10^{-7}$  Pa) while heating the samples at 150 °C. The thickness of the a-Ge layer, *t*, ranged from 100 to 600 nm. The samples were then loaded into a conventional tube furnace in a N<sub>2</sub> atmosphere and annealed to induce SPC. The growth temperature, *T<sub>g</sub>*, was 450 °C for 5 h and 375 °C for 150 h. After evaluating these samples, we performed post annealing (PA) at 500 °C for 5 h. For comparison, a sample without forming an insulating layer, called a SiO<sub>2</sub> sample, was also prepared. In addition, a sample with a GeO<sub>2</sub>-coated plastic substrate (125-µm-thick polyimide, Du Pont-Toray Co., Ltd.) was also prepared at 375 °C for 150 h.

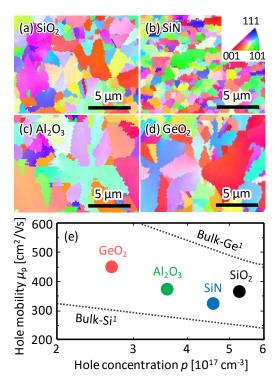

The electron backscattering diffraction (EBSD) images in Figs. 1(a)–1(d) show that the grain size of the SPC-Ge layer strongly depends on the kind of the underlayer. This suggests that the frequency of Ge nucleation was changed because of the change of the interfacial energy between Ge and the underlayer.<sup>21,29,34</sup> From the EBSD analyses, the average grain size was determined to be 2.9  $\mu$ m for SiO<sub>2</sub>, 1.4  $\mu$ m for SiN, 5.3  $\mu$ m for Al<sub>2</sub>O<sub>3</sub>, and 4.5  $\mu$ m for GeO<sub>2</sub>. We used Hall-effect measurements with the Van der Pauw method to evaluate the electrical properties of the SPC-Ge layers. All samples showed p-type conduction, similar to conventional undoped SPC-Ge on glass.<sup>5,6,32</sup> This is because the point defects in Ge provide shallow acceptor levels that generate holes at room temperature.<sup>35</sup> Figure 1(e) shows that the

hole concentration p and the hole mobility  $\mu_p$  also depend on the underlayer material. The GeO<sub>2</sub> sample exhibits the lowest p of 2.7×10<sup>17</sup> cm<sup>-3</sup> and the highest  $\mu_p$  of 440 cm<sup>2</sup>/Vs among these underlayer materials. This improvement of  $\mu_p$  likely reflects the reduction of grain boundary scattering and impurity scattering.<sup>32</sup> Therefore, we examined further improvement of carrier mobility focusing on the GeO<sub>2</sub> sample.

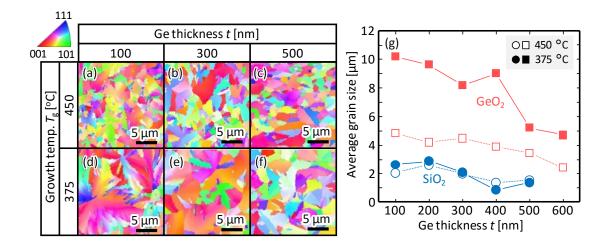

Figures 2(a)–2(f) show that the Ge grains of the GeO<sub>2</sub> sample are almost randomly oriented and that the grain size varies with both *t* and  $T_g$ . Figure 2(g) shows that the Ge grain size, as determined by the EBSD analyses, is significantly improved by the insertion of GeO<sub>2</sub>. The grain size decreases with increasing *t* for all the sample conditions, likely reflecting the increase in bulk nucleation with increasing *t*.<sup>30,33,35</sup> The lower  $T_g$  provides a larger grain size, which agrees with the conventional SPC.<sup>5,30</sup> This behavior, grain-size enlargement at lower temperature, is remarkable for the GeO<sub>2</sub> sample. The GeO<sub>2</sub> sample for *t* = 100 nm and  $T_g$  = 375 °C exhibits a grain size over 10 µm, which is the largest among SPC-Ge(Sn).<sup>30-33</sup>

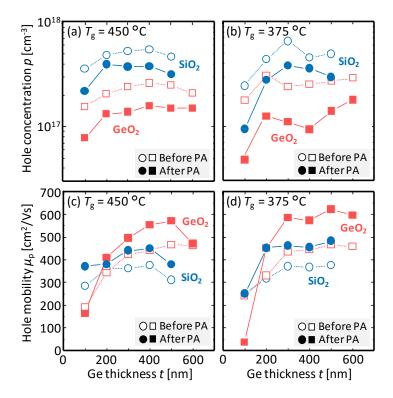

We evaluated p and  $\mu_p$  of the samples before PA. Figures 3(a) and 3(b) show that p decreases by inserting GeO<sub>2</sub> for all t and  $T_g$ . This behavior suggests that the GeO<sub>2</sub> insertion lowered the defects in Ge generating holes, i.e., improved Ge crystallinity. Figures 3(c) and 3(d) show that the larger t provides the higher  $\mu_p$  despite the grain becoming smaller (Fig. 2(g)). This behavior was also seen in previous studies and explained to be due to interface scattering.<sup>30,33</sup> For  $t \leq 200$  nm, the GeO<sub>2</sub> samples exhibit lower  $\mu_p$  than the SiO<sub>2</sub> samples despite the much larger grain size (Fig. 2(g)). These results suggest that current Ge/GeO<sub>2</sub> interface provides larger interface scattering than Ge/SiO<sub>2</sub> interface. Conversely, for t > 200 nm, the GeO<sub>2</sub> samples exhibit higher  $\mu_p$  than the SiO<sub>2</sub> samples. According to Matthiessen's rule and Irvin's curve,<sup>1</sup>  $\mu_p$  for t > 200 nm is determined by the balance between grain boundary scattering and impurity scattering.<sup>32,33</sup> Therefore,  $\mu_p$  enhancement by GeO<sub>2</sub> insertion

impurity scattering by *p* reduction.

PA at 500 °C was performed for all the samples to reduce the point defects in Ge and then decrease the impurity scattering. Figures 3(a) and 3(b) show that, for both GeO<sub>2</sub> and SiO<sub>2</sub> samples, *p* decreased after PA. This result suggests that the Ge atoms locally migrated via thermal diffusion and passivated point defects, generating holes, in the Ge layers. Figures 3(c) and 3(d) show that, for both GeO<sub>2</sub> and SiO<sub>2</sub> samples,  $\mu_p$  improves for  $t \ge 200$  nm, especially for  $T_g = 375$  °C. This reflects in reduction of *p*, that is, impurity scattering. The highest  $\mu_p$  of 620 cm<sup>2</sup>/Vs is recorded for the GeO<sub>2</sub> sample for t = 500 nm and  $T_g = 375$  °C after PA.

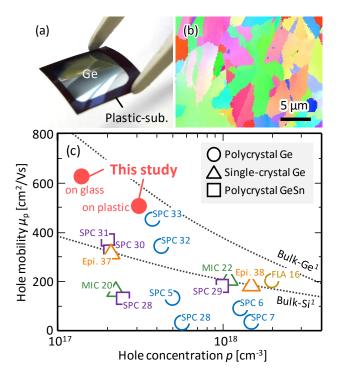

Thus, we found that a GeO<sub>2</sub> underlayer dramatically improves the crystal and electrical properties of the SPC-Ge layer. For application to flexible devices, we prepared a 400-nm-thick Ge layer on a GeO<sub>2</sub>-coated plastic substrate and induced SPC at  $T_g = 375$  °C. Figure 4(a) shows that a Ge layer is formed on a plastic substrate and maintains its flexibility after the heat treatment. As shown in Fig. 4(b), the SPC-Ge layer on the plastic substrate has large grains equivalent to the SPC-Ge layer formed on GeO<sub>2</sub>-coated glass (Fig. 2). The Ge layer exhibited *p* of  $3.1 \times 10^{17}$  cm<sup>-3</sup> and  $\mu_p$  of 500 cm<sup>2</sup>/Vs. This  $\mu_p$  is much higher than that of any other semiconductor films synthesized on a plastic substrate.

Figure 4(c) shows that the current SPC-Ge layer on GeO<sub>2</sub>-coated glass has the lowest p among poly-Ge(Sn) on insulators, indicating that the Ge layer contains relatively few defects. The resulting  $\mu_p$  of 620 cm<sup>2</sup>/Vs is higher than that for any other polycrystalline semiconductor layers, and even higher than that for single-crystal Ge layers epitaxially grown from Si-on-insulator substrates.<sup>37,38</sup> Moreover,  $\mu_p$  reached 500 cm<sup>2</sup>/Vs even on a plastic substrate, exceeding that of single-crystal Si wafers.<sup>1</sup> These results mean that single-crystal wafers are no longer necessary for fabricating semiconductor films with a high carrier mobility.

In conclusion, we significantly updated the highest recorded  $\mu_{\rm P}$  of semiconductor films

directly grown on insulators at low temperatures (< 900 °C). The SPC of a densified a-Ge layer formed on a GeO<sub>2</sub>-coated glass substrate provided  $\mu_p$  of 620 cm<sup>2</sup>/Vs, despite the temperature process being as low as 500 °C. This achievement was due to the reduction of both grain boundary scattering and impurity scattering owing to the grain size enlargement and the passivation of defect-induced acceptors. Even for Ge on a plastic substrate formed at 375 °C,  $\mu_p$  reached 500 cm<sup>2</sup>/Vs. Besides the advantages on carrier mobility and thermal budget, the process developed herein is simple enough for practical industrial applications. Therefore, these findings will aid in realizing advanced electronics, simultaneously allowing for high performance, inexpensiveness, and flexibility.

This work was financially supported by JSPS KAKENHI (No. 17H04918), Murata Science Foundation. The authors are grateful to Prof. T. Sakurai of the University of Tsukuba for assistance with the Hall effect measurement. Some experiments were conducted at the International Center for Young Scientists in NIMS.

## REFERENCES

- <sup>1</sup> J.C. Irvin and S.M. Sze, Solid State Electron. **11**, 599 (1968).

- <sup>2</sup> G. Taraschi, A. J. Pitera, and E. A. Fitzgerald, Solid. State. Electron. **48**, 1297 (2004).

- <sup>3</sup> A. Nayfeh, C. O. Chui, T. Yonehara, and K. C. Saraswat, IEEE Electron Device Lett. 26, 311 (2005).

- <sup>4</sup> D. P. Brunco, B. De Jaeger, G. Eneman, J. Mitard, G. Hellings, a. Satta, V. Terzieva, L. Souriau, F. E. Leys, G. Pourtois, M. Houssa, G. Winderickx, E. Vrancken, S. Sioncke, K. Opsomer, G. Nicholas, M. Caymax, a. Stesmans, J. Van Steenbergen, P. W. Mertens, M. Meuris, and M. M. Heyns, J. Electrochem. Soc. 155, H552 (2008).

- <sup>5</sup> K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid. State. Electron. **53**, 1159 (2009).

- <sup>6</sup> C.-Y. Tsao, J. Huang, X. Hao, P. Campbell, and M. A. Green, Sol. Energy Mater. Sol. Cells **95**, 981 (2011).

- <sup>7</sup> H.-W. Jung, W.-S. Jung, H.-Y. Yu, and J.-H. Park, J. Alloys Compd. **561**, 231 (2013).

- <sup>8</sup> T. Sadoh, H. Kamizuru, A. Kenjo, and M. Miyao, Appl. Phys. Lett. **89**, 192114 (2006).

- <sup>9</sup> S. Kabuyanagi, T. Nishimura, K. Nagashio, and A. Toriumi, Thin Solid Films 557, 334 (2014).

- <sup>10</sup> H. Watakabe, T. Sameshima, H. Kanno, and M. Miyao, Thin Solid Films **508**, 315 (2006).

- <sup>11</sup> W. Yeh, H. Chen, H. Huang, C. Hsiao, and J. Jeng, Appl. Phys. Lett. **93**, 94103 (2008).

- <sup>12</sup> K. Sakaike, S. Higashi, H. Murakami, and S. Miyazaki, Thin Solid Films **516**, 3595 (2008).

- <sup>13</sup> C.-Y. Liao, C.-Y. Huang, M.-H. Huang, W.-H. Huang, C.-H. Shen, J.-M. Shieh, and H.-C. Cheng, Jpn.

J. Appl. Phys. 56, 06GF08 (2017).

- <sup>14</sup> T. Matsui, M. Kondo, K. Ogata, T. Ozawa, and M. Isomura, Appl. Phys. Lett. **89**, 142115 (2006).

- <sup>15</sup> M. Tada, J.-H. Park, D. Kuzum, G. Thareja, J. R. Jain, Y. Nishi, and K. C. Saraswat, J. Electrochem. Soc. 157, H371 (2010).

- <sup>16</sup> K. Usuda, Y. Kamata, Y. Kamimuta, T. Mori, M. Koike, and T. Tezuka, Appl. Phys. Express 7, 56501 (2014).

- <sup>17</sup> Z. Wang, L. P. H. Jeurgens, W. Sigle, and E. J. Mittemeijer, Phys. Rev. Lett. **115**, 016102 (2015).

- <sup>18</sup> S. Hu, A. F. Marshall, and P. C. McIntyre, Appl. Phys. Lett. **97**, 82104 (2010).

- <sup>19</sup> K. Toko, R. Numata, N. Oya, N. Fukata, N. Usami, and T. Suemasu, Appl. Phys. Lett. **104**, 22106 (2014).

- <sup>20</sup> J.-H. Park, K. Kasahara, K. Hamaya, M. Miyao, and T. Sadoh, Appl. Phys. Lett. **104**, 252110 (2014).

- <sup>21</sup> K. Toko, K. Nakazawa, N. Saitoh, N. Yoshizawa, N. Usami, and T. Suemasu, CrystEngComm 16, 2578 (2014).

- <sup>22</sup> K. Kasahara, Y. Nagatomi, K. Yamamoto, H. Higashi, M. Nakano, S. Yamada, D. Wang, H. Nakashima, and K. Hamaya, Appl. Phys. Lett. **107**, 142102 (2015).

- <sup>23</sup> R. Pillarisetty, Nature **479**, 324 (2011).

- <sup>24</sup> R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, IEEE Trans. Electron Devices 59, 335 (2012).

- <sup>25</sup> K. Yamamoto, T. Sada, D. Wang, and H. Nakashima, Appl. Phys. Lett. **103**, 122106 (2013).

- <sup>26</sup> W. Mizubayashi, S. Noda, Y. Ishikawa, T. Nishi, A. Kikuchi, H. Ota, P.-H. Su, Y. Li, S. Samukawa, and K. Endo, Appl. Phys. Express 10, 026501 (2017).

- <sup>27</sup> A. Toriumi and T. Nishimura, Jpn. J. Appl. Phys. **57**, 010101 (2018).

- <sup>28</sup> W. Takeuchi, N. Taoka, M. Kurosawa, M. Sakashita, O. Nakatsuka, and S. Zaima, Appl. Phys. Lett. 107, 22103 (2015).

- <sup>29</sup> I. Yoshikawa, M. Kurosawa, W. Takeuchi, M. Sakashita, O. Nakatsuka, and S. Zaima, Mater. Sci. Semicond. Process. **70**, 151 (2017).

- <sup>30</sup> T. Sadoh, Y. Kai, R. Matsumura, K. Moto, and M. Miyao, Appl. Phys. Lett. **109**, 232106 (2016).

- <sup>31</sup> K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Sci. Rep. **8**, 14832 (2018).

- <sup>32</sup> K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- <sup>33</sup> R. Yoshimine, K. Moto, T. Suemasu, and K. Toko, Appl. Phys. Express **11**, 031302 (2018).

- <sup>34</sup> P. Germain, K. Zellama, S. Squelard, J.C. Bourgoin, and A. Gheorghiu, J. Appl. Phys. **50**, 6986 (1979).

- <sup>35</sup> H. Haesslein, R. Sielemann, and C. Zistl, Phys. Rev. Lett. **80**, 2626 (1998).

- <sup>36</sup> J.W.Y. Seto, J. Appl. Phys. **46**, 5247 (1975).

- <sup>37</sup> N. Hirashita, Y. Moriyama, S. Nakaharai, T. Irisawa, N. Sugiyama, and S. I. Takagi, Appl. Phys. Express 1, 1014011 (2008).

- <sup>38</sup> O. Nakatsuka, N. Tsutsui, Y. Shimura, S. Takeuchi, A. Sakai, and S. Zaima, Jpn. J. Appl. Phys. 49, 04DA10 (2010).

FIG. 1. Characteristics of the SPC-Ge layers for t = 300 nm and  $T_g = 450$  °C, grown on various underlayers (SiO<sub>2</sub>, SiN, Al<sub>2</sub>O<sub>3</sub>, and GeO<sub>2</sub>) formed on a glass substrate. (a)–(d) EBSD images of the Ge layers, where the colors indicate the crystal orientation, according to the inserted color key. (e) Comparison of hole mobility  $\mu_p$  and hole concentration p of the samples. The data for single-crystal bulk Si and Ge are shown by dotted lines [Ref. 1].

**FIG. 2.** Grain size of the SPC-Ge layers on a GeO<sub>2</sub>-coated glass substrate. (a)–(f) EBSD images as a matrix of *t* and  $T_g$ . The colors indicate the crystal orientation, according to the inserted color key. (g) Average grain size determined by the EBSD analyses with  $T_g = 450 \text{ °C}$  and 375 °C as a function of *t*. The data for the sample without GeO<sub>2</sub> (named SiO<sub>2</sub> sample) are shown for comparison.

**FIG. 3.** Electrical properties of the SPC-Ge layers before and after PA (500 °C) as a function of *t*. (a),(b) Hole concentration *p* and (c),(d) hole mobility  $\mu_p$  for the GeO<sub>2</sub> and SiO<sub>2</sub> samples where  $T_g = (a),(c) 450$  °C and (b),(d) 375 °C. The data before PA are shown by open symbols and after PA by closed symbols.

**FIG. 4.** (a) Photograph and (b) EBSD image of the SPC-Ge layer formed on a GeO<sub>2</sub>-coated plastic substrate where t = 400 nm and  $T_g = 375$  °C. (c) Comparison of the hole mobility  $\mu_p$  and hole concentration p of Ge(Sn) films on insulators. The growth method and the reference number are shown near each symbol. The data for single-crystal bulk Si and Ge are shown by dotted lines [Ref. 1].