# High input impedance voltage-mode universal filter and its modification as quadrature oscillator using VDDDAs

Sunti Tuntrakool<sup>a</sup>, Montree Kumngern<sup>a</sup>, Roman Sotner<sup>b</sup>, Norbert Herencsar<sup>c</sup>, Peerawut Suwanjan<sup>d</sup> & Winai Jaikla<sup>d</sup>\*

aDepartment of Telecommunications Engineering, Faculty of Engineering,

King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

bDepartment of Radio Electronics, Faculty of Electrical Engineering and Communication,

Brno University of Technology, Brno 61600, Czech Republic

cDepartment of Telecommunications, Faculty of Electrical Engineering and Communication,

Brno University of Technology, Brno 61600, Czech Republic

dDepartment of Engineering Education, Faculty of Industrial Education and Technology,

King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

Received 14 July 2016; revised 27 December 2016; accepted 3 January 2017

The second order universal voltage-mode filter using voltage differencing differential difference amplifiers (VDDDAs) has been proposed. It has high input impedance voltage-mode biquad filter with orthogonal tune of natural frequency and quality factor. The proposed filter simultaneously provides five filter responses: low-pass (LP), high-pass (HP), band-reject (BR), all-pass (AP) and band-pass (BP) in the same circuit topology. The natural frequency and quality factor can be tuned electronically and orthogonally dc bias current. The output impedance at output nodes HP, AP and BR has low impedance which can connect to other circuit without the use of voltage buffers. The proposed filter consists of three VDDDAs, one grounded resistor and two grounded capacitors. This makes the proposed filter suitable for integrated circuit development. With slightly modifying the proposed filter, the voltage-mode qudrature sinusoidal oscillator with low output impedance and independent control of condition of oscillation (CO) and frequency of oscillation (FO) has been achieved. The results shown in this paper are from PSPICE simulation and experiment to validate the proposed circuits.

Keywords: Analog filter, VDDDA, Voltage-mode, Single input-multiple output, Oscillator

### 1 Introduction

The oscillator circuit and analog active filter are popular and standard topic for circuit design. They are widely used for their important requirements for application in electrical and electronic system and also very popular in using for circuit design of continuous-time analog signal processing. There are many fields that using filters circuit such as communications, measurement, and instrumentation, and control systems<sup>1</sup>. Especially, researchers have been very considerably interest in several functions filter which is called universal filter or multifunction filter. The single-input multiple-output (SIMO) is the most popular analog filter where different output filter functions can be simultaneously realized by the same circuit topology<sup>2</sup>.

Using of active building block for circuit design is very popular in use. It gives the flexibility for designer to realize the high performance circuit using minimum number of active element<sup>3-7</sup>. With mentioned features, the principle of active building blocks for both current and voltage mode circuit are introduced by Biolek et al.6 Voltage differencing differential difference amplifier (VDDDA)<sup>8</sup> is one of the interests. It allows interesting utilization and design of more profitable or more exacting application especially the electronic controllability. From literature reviews, it is found that not much research using VDDDA has been published for instance the voltage-mode first order all pass filter<sup>8</sup>, oscillator8-10. The excellent multiple-input multipleoutput (MIMO) voltage-mode universal filter using VDDDA was proposed in literature 10-14. These filters can provide complete standard transfer functions with

<sup>\*</sup>Corresponding author (E-mail: winai.ja@kmitl.ac.th)

high inputs and low outputs impedance. The natural frequency and quality factor can be electronically and orthogonally controlled. However, these filters cannot be considered as universal filter because all five filter responses cannot be simultaneously provided. The multiple-input single-output (MISO) voltage mode filter was introduced by Herencsar *et al.* <sup>15</sup> This filter consists of single active building block, single MOS transistor and two floating capacitors. It can provide five filter responses depending on the appropriate selecting input voltage. The natural frequency and quality factor can be electronically tuned. However, this filter cannot be easy to cascade without the use of voltage buffers. Moreover, the use of floating capacitors is not attractive for integration.

This contribution presents a SIMO voltage-mode filter with high input impedance, emphasizing on use of VDDDAs. The proposed filter composes of three active elements, one grounded resistor and two grounded capacitors which are suitable for fabricating in monolithic chip or off-the-shelf implementation. The proposed filter can provide five standard functions such as low-pass, high-pass, band-reject, all-pass and band-pass. The quality factor and natural frequency can be electronically and orthogonally adjusted. With slight modification of the proposed filter, the voltage-mode quadrature oscillator with low output impedance is achieved.

### 2 Principle of Operation

## 2.1 VDDDA overview

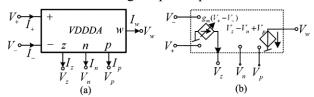

The principle of VDDDA was introduced by Biolek *et al.*<sup>6</sup> Later, Herencsar *et al.*<sup>8</sup> proposed the internal construction of VDDDA using CMOS technology. Symbol and equivalent circuit of VDDDA are shown in Fig. 1 (a) and (b), respectively, where  $V_+$  and  $V_-$  are the voltage input terminals which will be converted to be the current at z terminal by transconductance  $(g_m)$ . It is generally tuned by bias current and the differential voltage at terminal z, n and p will be send to w terminal with the unity voltage gain. For ideal VDDDA, it has low output impedance at w terminal and high input impedance at terminals

Fig. 1 — VDDDA (a) symbol and (b) equivalent circuit

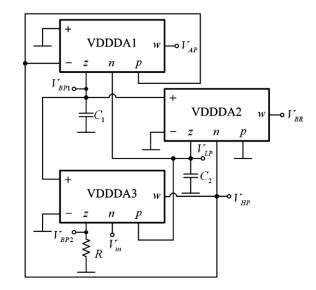

Fig. 2 – Presented voltage-mode filter

$V_+$ ,  $V_-$ , z, n and p. The characteristics matrix equation of ideal VDDDA is described below:

$$\begin{pmatrix}

I_{v+} \\

I_{v-} \\

I_{z} \\

I_{n} \\

I_{p} \\

V_{w}

\end{pmatrix} = \begin{pmatrix}

0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 \\

g_{m} & -g_{m} & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 1 & -1 & 1 & 0

\end{pmatrix} \begin{pmatrix}

V_{+} \\

V_{-} \\

V_{z} \\

V_{n} \\

V_{p} \\

I_{w}

\end{pmatrix} \dots (1)$$

### 2.2 High input impedance voltage-mode filter using VDDDAs

Figure 2 is the proposed second order filter consisted of three VDDDAs, one grounded resistor and two grounded capacitors. The proposed filter provides simultaneously five filter responses; *HP*, *LP*, *BR*, *AP* and *BP* (*BP*<sub>1</sub> and *BP*<sub>2</sub>) with high input impedance. Moreover, the output nodes for *HP*, *AP* and *BR* responses exhibit low output impedance. Considering an ideal VDDDA, routine analysis of the proposed filter provides the following voltage transfer functions:

$$HP(s) = \frac{V_{HP}}{V_{in}} = -\frac{s^2}{D(s)}$$

... (2)

$$LP(s) = \frac{V_{LP}}{V_{in}} = \frac{\frac{g_{m1}g_{m2}}{C_1C_2}}{D(s)} \qquad ... (3)$$

$$BR(s) = \frac{V_{BR}}{V_{in}} = \frac{s^2 + \frac{g_{m1}g_{m2}}{C_1C_2}}{D(s)} \qquad \dots (4)$$

$$AP(s) = \frac{V_{AP}}{V_{in}} = \frac{-\left(s^2 - \frac{g_{m1}}{C_1}s + \frac{g_{m1}g_{m2}}{C_1C_2}\right)}{D(s)} \qquad \dots (5)$$

$$BP_{1}(s) = \frac{V_{BP1}}{V_{in}} = \frac{\frac{g_{m1}}{C_{1}}s}{D(s)} \dots (6)$$

$$BP_2(s) = \frac{V_{BP2}}{V_{in}} = \frac{\frac{g_{m1}g_{m3}R}{C_1}s}{D(s)} \dots (7)$$

where

$$D(s) = s^{2} + \frac{g_{m1}g_{m3}R}{C_{1}}s + \frac{g_{m1}g_{m2}}{C_{1}C_{2}} \qquad ... (8)$$

It is found from Eqs (2-8) that the proposed filter is the unit gain filter, then, for any practical use, additional voltage amplifiers are needed to achieve gain from the active filter. However, the gain is probably obtained for  $BP_1$  only if specific quality factor (Q) is set. The natural frequency  $(\omega_0)$  and Q of each filter response can be expressed as following:

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}} \text{ and } Q = \frac{1}{g_{m3}R}\sqrt{\frac{C_1g_{m2}}{C_2g_{m1}}} \dots (9)$$

From Eq. (9), it is found that the quality factor can be electronically tuned via  $g_{m3}$  without affecting the natural frequency. Moreover, if  $g_{m1}$  is equal to  $g_{m2}$ , the natural frequency can be electronically adjusted without affecting the quality factor. However, it is found that the proposed circuit needs component matching conditions (i.e.,  $g_{m3}=1/R$ ) for realizing AP response. The relative sensitivities of the proposed filter can be found in Eq. (10):

$$S_{g_{m1}}^{\omega_{0}} = S_{g_{m2}}^{\omega_{0}} = \frac{1}{2}; \ S_{C_{1}}^{\omega_{0}} = S_{C_{2}}^{\omega_{0}} = -\frac{1}{2};$$

$$S_{R}^{Q_{0}} = S_{g_{m3}}^{Q_{0}} = -1; S_{C_{1}}^{Q_{0}} = S_{g_{m2}}^{Q_{0}} = \frac{1}{2}; \ S_{C_{2}}^{Q_{0}} = S_{g_{m1}}^{Q_{0}} = -\frac{1}{2}$$

...(10)

It is found that the active and passive sensitivities are equal or less than unity in magnitude.

### 3 Non-Ideal Case

Practically, the performances of the proposed filter are affected by the influences of voltage tracking error from the unity-value gain of internal differential voltage buffer and parasitic terminal impedances of VDDDA<sup>8</sup>. In this section, these parameters will be

taken into account. For non-ideal case the voltage at w terminal is rewritten as shown below:

$$V_{w} = \beta_{z}V_{z} - \beta_{n}V_{n} + \beta_{n}V_{n} \qquad \dots (11)$$

From Eq. (10),  $\beta_z$ ,  $\beta_n$ , and  $\beta_p^-$  are the voltage error gains from z, n, p terminals to w terminal, respectively. The influences of parasitic impedances of  $V_{-1}$ ,  $p_1$ ,  $n_2$  and  $n_3$  terminals will be negligible because of their connection to low-impedance outputs ( $w_3$  terminal) and input voltage source. The most importance parasitic impedances are the impedance at  $z_1$  ( $R_{z1}//C_{z1}$ ),  $n_1$  ( $R_{n1}//C_{n1}$ ),  $V_{+2}$  ( $R_{V+2}//C_{V+2}$ ),  $z_2$  ( $R_{z2}//C_{z2}$ ) and  $p_3$  ( $R_{p3}//C_{p3}$ ) terminals. However, the parasitic impedances at  $z_3$  terminal will be negligible but the operation frequency  $f_{op}$  should be more lower than  $1/\{C_{z3}(R_{z3}+R)\}$ . The voltage transfer functions for the circuit of Fig. 3 are given in Eqs (12-17):

$$\frac{V_{HP}^*}{V_{in}} = \frac{-\beta_{n3} \left[ s^2 C_1^* C_2^* + s \left( C_1^* G_2^* + C_2^* G_1^* \right) + G_1^* G_2^* \right]}{D^*(s)} \qquad \dots (12)$$

$$\frac{V_{LP}^*}{V_{in}} = \frac{\beta_{n3}g_{m1}g_{m2}}{C_1^*C_2^*} \dots (13)$$

$$V_{BR}^* = \frac{\beta_{n2}\beta_{n3} \left[ s^2 C_1^* C_2^* + s \left( C_1^* G_2^* + C_2^* G_1^* \right) + G_1^* G_2^* \right] + \frac{\beta_{z2}\beta_{n3}g_{m1}g_{m2}}{C_1^* C_2^*}}{D^*(s)} \dots (14)$$

$$\frac{V_{BP1}^*}{V_{in}} = \frac{\beta_{n3}g_{m1}\left(s\frac{1}{C_1^*} + \frac{G_2^*}{C_1^*C_2^*}\right)}{D^*(s)} \qquad \dots (15)$$

$$\frac{V_{BP2}^*}{V_{in}} = \frac{\beta_{n3} g_{m1} g_{m3} R \left( s \frac{1}{C_1^*} + \frac{G_2^*}{C_1^* C_2^*} \right)}{D^*(s)} \qquad \dots (16)$$

$$V_{AP}^{*} = \frac{-\left\{\beta_{n3}\left[s^{2}C_{1}^{*}C_{2}^{*} + s\left(C_{1}^{*}G_{2}^{*} + C_{2}^{*}G_{1}^{*}\right) + G_{1}^{*}G_{2}^{*}\right] - \left\{\beta_{z1}\beta_{n3}g_{m1}\left(s\frac{1}{C_{1}^{*}} + \frac{G_{2}^{*}}{C_{1}^{*}C_{2}^{*}}\right) + \frac{\beta_{n3}g_{m1}g_{m2}}{C_{1}^{*}C_{2}^{*}}\right\}}{D^{*}(s)} \dots (17)\right\}$$

where

$$D^{*}(s) = \begin{bmatrix} s^{2} + s \left( \frac{G_{2}^{*}}{C_{2}^{*}} + \frac{G_{1}^{*}}{C_{1}^{*}} + \frac{\beta_{z3}g_{m1}g_{m3}R}{C_{1}^{*}} \right) + \\ \frac{G_{1}^{*}G_{2}^{*} + \beta_{z3}g_{m1}g_{m3}RG_{2}^{*} + \beta_{p3}g_{m1}g_{m2}}{C_{1}^{*}C_{2}^{*}} \end{bmatrix} \dots (18)$$

$C_1^* = C_1 + C_{z1} + C_{v+2} + C_{v+3}$ ,  $C_2^* = C_2 + C_{z2} + C_{n1} + C_{p3}$ ,  $G_1^* = G_{z1} + G_{v+2} + G_{v+3}$  and  $G_2^* = G_{z2} + G_{n1} + G_{p3}$ . Also nonideal values of  $\omega_0$  and Q are found in Eqs (19) and (20), respectively:

$$\omega_0^* = \sqrt{\frac{G_1^* G_2^* + \beta_{z3} g_{m1} g_{m3} R G_2^* + \beta_{p3} g_{m1} g_{m2}}{C_1^* C_2^*}} \qquad \dots (19)$$

$$Q^* = \frac{1}{\begin{pmatrix} C_1^* G_2^* + C_2^* G_1^* + \\ \beta_{z3} C_2^* g_{m1} g_{m3} R \end{pmatrix}} \sqrt{C_1^* C_2^* \begin{pmatrix} G_1^* G_2^* + \beta_{z3} g_{m1} g_{m3} R G_2^* + \\ \beta_{p3} g_{m1} g_{m2} \end{pmatrix}} \dots (20)$$

### **4 Simulations Results**

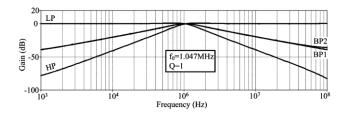

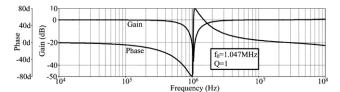

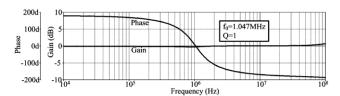

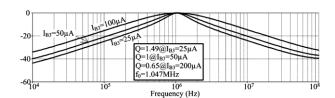

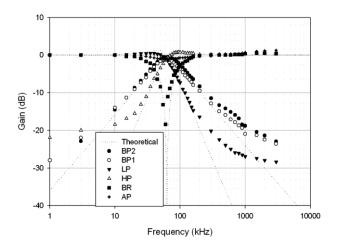

PSPICE simulations of the proposed filter in Fig. 2 were performed. The implementation of the CMOS VDDDA was same as described elsewhere<sup>8</sup>. Parameters of a 0.18 µm TSMC CMO Stechnology<sup>16</sup> (level 7) with  $\pm 0.9$  V voltage supply and  $V_B = -0.35$  V was used for simulation of PMOS and NMOS transistors. From Table 1, aspect ratios of PMOS and NMOS transistor are listed. It is seen that the parasitic resistances at terminals  $V_+$ ,  $V_-$ , n, and p ( $R_{\nu+}$ ,  $R_{\nu-}$ ,  $R_n$ and  $R_p$ ) exhibit high because they are gate resistance. Other simulated parasitic element values for each terminal ( $I_B = 50 \mu A$ ) are  $C_{\nu+} = 55.5 \text{ fF}$ ,  $C_{\nu-} = 53.2 \text{ fF}$ ,  $R_z = 570.54 \text{ k}\Omega$ ,  $C_z = 15.4 \text{ fF}$ ,  $C_n = 4.24 \text{ fF}$  and  $C_p = 4.25$  fF. The simulated voltage error gains,  $\beta_z$ ,  $\beta_n$ , and  $\beta_p$  are equal to 0.997. The filter was designed with the parameters of its components as follows:  $C_1 = C_2 = 47$ pF,  $R = 3.3 \text{ k}\Omega$ ,  $I_{B1} = I_{B2} = I_{B3} = 50 \text{ }\mu\text{A}$ . It yields the natural frequency of 1.047 MHz and quality factor of 1. The theoretical pole frequency is about 1.058 MHz. From the results, the gains responses for LP,  $BP_1$ ,  $BP_2$  and HP of the proposed filter obtained from Fig. 2 are shown in Figs 3-5 which are the gain response and phase response of BR and AP responses, respectively. It is obviously that the proposed filter can simultaneously provide low-pass, high-pass, band-pass, band-reject and all-pass functions without modifying circuit topology. The gain response of  $BP_2$ difference  $I_{\rm B3}$  is shown in Fig. 6, where  $I_{\rm B3}$  was set to 20 µA, 50 µA and 200 µA. The quality factor evaluated based on the simulation results was 1.49, 1, and 0.65, respectively. This is confirmed by Eq. (9) that the quality factor can be electronically tuned by  $I_{\rm B3}$  without affecting the natural frequency. High Qvalue can be achieved by setting  $I_{B3}$  as low as possible. The highest simulated Q is 26.66 ( $I_{B3}$ = 1  $\mu$ A) and the lowest simulated Q is 0.384 ( $I_{B3} = 400 \mu A$ ).

| Table 1 – Dimensions of the transistors |            |            |            |  |  |  |  |  |  |

|-----------------------------------------|------------|------------|------------|--|--|--|--|--|--|

| Transistor                              | $W(\mu m)$ | $L(\mu m)$ | $L(\mu m)$ |  |  |  |  |  |  |

| M1-M2, NMOS (AGC)                       | 9          | 1.08       |            |  |  |  |  |  |  |

| M3-M4                                   | 3.96       | 1.08       |            |  |  |  |  |  |  |

| M5-M7                                   | 3.6        | 1.8        |            |  |  |  |  |  |  |

| M8-M11                                  | 0.72       | 1.08       |            |  |  |  |  |  |  |

| M12-M14                                 | 2.16       | 1.08       |            |  |  |  |  |  |  |

Fig. 3 – Frequency responses of proposed filter LP,  $BP_1$ ,  $BP_2$  and HP

Fig. 4 – Gain and phase response of BR

Fig. 5 – Gain and phase response of AP

Fig.  $6 - BP_2$  responses for difference  $I_{B3}$

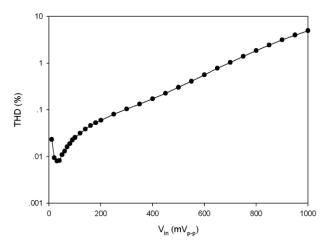

Figure 7 shows the dependence of the THD of LP filter on input voltage level. The THD is not over 1% when the input signal is lower 650 mV. In this test, sinusoidal signal with 100 kHz in-band frequency was fed into the proposed filter.

# 5 Comparison with Existing SIMO Voltage-Mode Filters

The proposed SIMO voltage-mode filter in Fig. 2 is compared with several SIMO voltage-mode filters from 17-44. It is found from Table 2 that there are VM

MISO structures having even some low-output impedance outputs<sup>25,29,32,38,42</sup>. However, their other drawbacks are in missing possibility for electronic control, requirements for floating passive elements and higher number of active elements (4 or 5).

Fig. 7 – Dependence of output harmonic distortion of LP filter on the input voltage

All these problems are solved in solution presented in this paper.

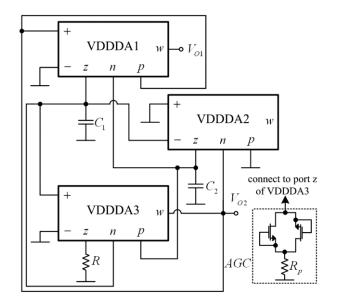

# 6 Modification of Proposed Filter as Quadrature Oscillator

By connecting node  $V_{\rm BP1}$  to  $V_{\rm in}$  and interconnecting terminal  $V_+$  and  $V_-$  of VDDDA1 and VDDDA2 of the circuit in Fig. 2 according to the principle reported in earlier study<sup>45</sup> as illustrated in Fig. 8, the voltage-mode quadrature oscillator with low output impedance can be achieved. The characteristic equation of the oscillator in Fig. 8 is obtained as:

$$s^{2} + (1 - g_{m3}R) \frac{g_{m1}}{C_{1}} s + \frac{g_{m1}g_{m2}}{C_{1}C_{2}} = 0 \qquad \dots (21)$$

According to Eq. (21), the frequency of oscillator (FO) and condition of oscillation (CO) is written as:

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}}$$

, and  $1 \le g_{m3}R$  ... (22)

|           | Table 2 – Comparison of various SIMO voltage-mode filters |     |     |          |           |              |                    |             |            |               |  |  |

|-----------|-----------------------------------------------------------|-----|-----|----------|-----------|--------------|--------------------|-------------|------------|---------------|--|--|

| Reference | ABB                                                       | No. | No. | Grounded | High inpu | t Electronic | c Orthogonal       | Five filter | Low        | Technology    |  |  |

|           |                                                           | of  | of  | elements | impedance |              | tune of            | responses   |            | C.            |  |  |

|           |                                                           | ABB | R+C | only     |           |              | $Q$ and $\omega_0$ |             | impedances |               |  |  |

| 17        | DVCC                                                      | 3   | 3+2 | yes      | yes       | no           | no                 | yes         | no         | CMOS          |  |  |

| 18        | DVCC                                                      | 3   | 3+2 | no       | yes       | no           | yes                | yes         | no         | CMOS          |  |  |

| 19        | DVCC                                                      | 2   | 3+2 | no       | no        | no           | yes                | yes         | no         | CMOS          |  |  |

| 20        | FDCCII (Fig. 3)                                           | 1   | 2+2 | yes      | yes       | no           | no                 | no          | no         | CMOS          |  |  |

| 21        | DDCC                                                      | 2   | 3+2 | no       | no        | no           | no                 | yes         | no         | CMOS          |  |  |

| 22        | DDCC                                                      | 3   | 2+2 | no       | no        | no           | no                 | yes         | no         | CMOS          |  |  |

| 23        | DDCC & OTA                                                | 2   | 1+2 | yes      | yes       | yes          | no                 | no          | no         | CMOS          |  |  |

| 24        | OTA                                                       | 8   | 0+2 | yes      | yes       | yes          | yes                | no          | no         | CMOS          |  |  |

| 25        | CFOA                                                      | 1   | 3+2 | no       | no        | no           | yes                | no          | LP         | commercial IC |  |  |

| 26        | DDCCTA                                                    | 1   | 1+2 | yes      | yes       | yes          | no                 | no          | no         | CMOS          |  |  |

| 27        | DDCCTA                                                    | 2   | 2+2 | yes      | yes       | yes          | no                 | yes         | no         | CMOS          |  |  |

| 28        | OTA                                                       | 8   | 0+2 | yes      | yes       | yes          | yes                | no          | no         | CMOS          |  |  |

| 29        | DDCCTA                                                    | 3   | 0+2 | yes      | yes       | yes          | no                 | yes         | AP         | CMOS          |  |  |

| 30        | CCCCTA                                                    | 1   | 1+3 | no       | no        | yes          | yes                | no          | no         | BJT           |  |  |

| 31        | DDCCTA                                                    | 1   | 2+2 | no       | no        | yes          | no                 | no          | no         | CMOS          |  |  |

| 32        | DDCCTA                                                    | 2   | 2+2 | yes      | yes       | yes          | no                 | yes         | AP         | CMOS          |  |  |

| 33        | FDCCII                                                    | 1   | 3+2 | no       | no        | no           | no                 | yes         | no         | CMOS          |  |  |

| 34        | DVCC                                                      | 4   | 5+2 | yes      | yes       | no           | yes                | no          | no         | CMOS          |  |  |

| 35        | ICCII                                                     | 2   | 4+2 | no       | no        | no           | no                 | no          | no         | CMOS          |  |  |

| 36        | DVCC                                                      | 2   | 2+3 | no       | no        | no           | no                 | no          | no         | CMOS          |  |  |

| 37        | DDCCTA                                                    | 2   | 2+2 | no       | yes       | yes          | yes                | yes         | no         | CMOS          |  |  |

| 38        | VD-DIBA                                                   | 2   | 0+2 | yes      | yes       | yes          | no                 | no          | HP         | commercial IC |  |  |

| 39        | VDCC (Fig. 3)                                             | 1   | 2+2 | yes      | no        | yes          | yes                | no          | no         | CMOS          |  |  |

| 40        | VDCC                                                      | 1   | 2+2 | no       | no        | yes          | yes                | no          | no         | BJT           |  |  |

| 41        | CCII                                                      | 2   | 3+2 | no       | yes       | no           | no                 | no          | no         | CMOS          |  |  |

| 42        | DDCCTA                                                    | 2   | 3+2 | yes      | yes       | yes          | yes                | yes         | AP         | CMOS          |  |  |

| 43        | VDTA (Fig. 5)                                             | 1   | 0+2 | yes      | yes       | yes          | no                 | no          | no         | CMOS          |  |  |

| 44        | CCII                                                      | 4   | 5+2 | no       | yes       | no           | yes                | yes         | no         | commercial IC |  |  |

| Present   | VDDDA                                                     | 3   | 1+2 | yes      | yes       | yes          | yes                | yes         | HP, AP, BR |               |  |  |

| work      |                                                           |     |     |          |           |              |                    |             |            | commercial IC |  |  |

Fig. 8 – Voltage-mode quadrature oscillator with low output impedance

Fig. 9 – Quadrature output waveform

It is found from Eq. (22) that the FO and CO are independently and electronically controlled. The relationship of  $V_{\rm O2}$  and  $V_{\rm O1}$  is follows:

$$\frac{V_{O2}}{V_{O1}} = \frac{sC_1}{g_{m1}g_{m3}} \qquad \dots (23)$$

At oscillation frequency ( $\omega_0$ ), the magnitude of  $V_{\rm O2}/V_{\rm O1}$  is written as:

$$\left| \frac{V_{O2}}{V_{O1}} \right|_{o_0} = \frac{1}{g_{m3}} \sqrt{\frac{C_1 g_{m2}}{C_2 g_{m1}}} \qquad \dots (24)$$

It is found from Eq. (24) that the changing of  $g_{\rm ml}$  or  $g_{\rm m2}$  for controlling the FO causes change of amplitude  $V_{\rm O2}$  and  $V_{\rm O1}$  during tuning process. This phenomenon will increase the THD if amplitude reaches high levels due to the limits of dynamical range of VDDDA. However, this can be alleviated by simultaneously changing  $g_{\rm ml}$  and  $g_{\rm m2}$  ( $I_{\rm B1} = I_{\rm B2}$ ). As stated above, the amplitude of quadrature output

Fig. 10 – Output spectrum

Fig. 11 – Tuning of FO by adjusting  $I_{B1}$  and  $I_{B2}$

voltage  $V_{01}$  and  $V_{02}$  is equal for all frequency. However, to unify unbalance of produced amplitudes  $V_{01}$  and  $V_{02}$  as well as to reduce the THD, the simple AGC circuit for amplitude stabilization can be easily applied to terminal z of VDDDA3.

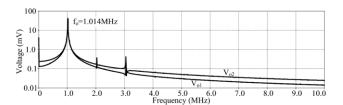

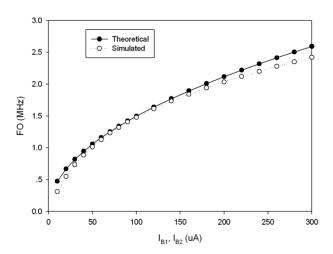

The proposed oscillator in Fig. 8 was simulated with the parameters of its components;  $C_1 = C_2 = 47 \text{ pF}$ ,  $R = 3.3 \text{ k}\Omega, R_p = 330 \text{ k}\Omega, I_{B1} = I_{B2} = 50 \text{ }\mu\text{A} \text{ and}$  $I_{\text{B3}} = 51.5 \,\mu\text{A}$ . The W/L of NMOS in AGC is 9  $\mu$ s /1.08  $\mu$ m. It yields the FO of 1.014 MHz. The theoretical FO is about 1.058 MHz. The results of this simulation are, respectively, shown in Figs 9 and 10. The total harmonic distortion for  $V_{O1}$  and  $V_{O2}$  are 0.68 % and 76 %, respectively. Tuning of simulated and theoretical FO is shown in Fig. 11, where  $I_{\rm B1}$  and  $I_{\rm B2}$  are equal and were adjusted from 10  $\mu A - 300 \,\mu A$ . The range of FO controlled from 0.31 MHz -2.42 MHz was obtained. It is found that there is some deviation between theoretical and simulated value due to the parasitic element as analyzed in Eq. (19). The tuning of  $g_m$  by adjusting  $I_B$  will change the value of parasitic elements.

### 7 Experimental Results

The performances of the proposed filter and oscillator were also experimentally investigated. The

Fig. 12 – Internal construction of VDDDA constructed from an available commercial ICs

Fig. 13 – Experimental gain responses of the proposed filter

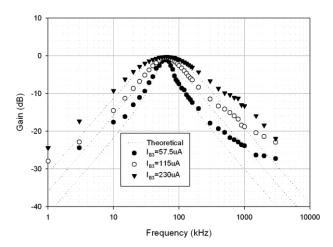

Fig. 14 – Experimental gain response of BP<sub>2</sub> for different value of  $I_{B3}$

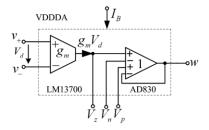

VDDDA was constructed from the available commercial ICs, AD830 and LM13700 as illustrated in Fig. 12. The transconductance of LM13700 is  $g_m = I_B / 2V_T$  where  $V_T$  is thermal voltage ( $V_T \cong 26$  mV at room temperature). The proposed filter was firstly tested with following conditions; the supply voltage  $\pm 5$  V,  $C_1 = C_2 = 5.6$  nF,  $I_{B1} = I_{B2} = I_{B3} = 115$   $\mu$ A

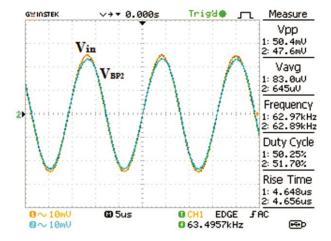

Fig. 15 – Measurement of  $V_{\rm BP2}$  at frequency 63 kHz

Fig. 16 – Measurement of output voltage and its spectrum where  $I_{BI} = I_{B2} = 115 \mu A$

$(g_{m1} = g_{m2} = g_{m3} = 2.211 \text{ mA/V})$  and  $R = 0.45 \text{ k}\Omega$ . With these conditions, the natural frequency and quality factor are 62.853 kHz and 1, respectively. The experimental gain response of  $BP_2$ ,  $BP_1$ , LP, HP, BR and AP is shown in Fig. 13. The experimental natural frequency is about 61 kHz which was about 2.948 % deviated from theoretical value. The tuning of Q without affecting natural frequency is confirmed by the experimental result of  $BP_2$  filter in Fig. 14 where the value of  $I_{B3}$  was changed to 57.5 μA, 115 μA and 230 μA. The measurements of output voltage  $V_{BP2}$  is also shown in Fig. 15 where the 50 mV sinusoidal voltage with 63 kHz of frequency was applied as input signal.

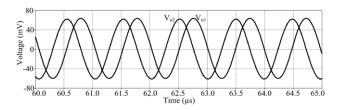

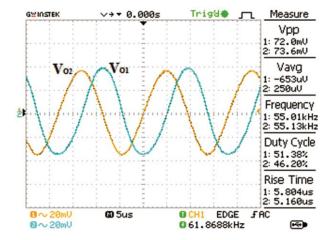

The proposed oscillator in Fig. 8 was tested with following conditions; the supply voltage  $\pm 5 \text{ V}$ ,  $C_1 = C_2 = 5.6 \text{ nF}$ ,  $I_{\text{B1}} = I_{\text{B2}} = I_{\text{B3}} = 115 \text{ }\mu\text{A}$   $(g_{\text{m1}} = g_{\text{m2}} = g_{\text{m3}} = 2.211 \text{ mA/V})$  and  $R = 0.54 \text{ }k\Omega$ .

With these conditions, the FO is 62.9 kHz. Figure 16 shows the measured output voltage where the experimental FO was about 61.86 kHz which was about 1.579 % deviated from theoretical value. It is also found that the output voltages  $V_{\rm ol}$  and  $V_{\rm o2}$  are quadrature sinusoidal signal.

### **8 Conclusions**

Voltage-mode bi-quad filter has been proposed in this study. The advantages of the proposed filter are as follows. Firstly, it can perform variety of filters, i.e., low-pass, high-pass, band-pass, band-reject and all-pass functions. Secondly, the quality factor and the natural frequency can be electronically orthogonally controlled. Finally, the filter has high input impedance. Moreover, the output voltage terminals for functions high-pass, band-reject and allpass are low output impedance. The proposed filter consists of three VDDDAs, one grounded resistor and two grounded capacitors, which are attractive for either IC implementation. With slightly modifying the proposed filter, the voltage-mode quadrature oscillator low output impedances is achieved. The CO and FO can be independently and electronically tuned. Moreover, the ratio of amplitudes  $V_{O1}$  and  $V_{O2}$ is constant on the tuning of FO if  $I_{B1}$  and  $I_{B2}$  are simultaneously tuned. Simulation results confirmed theoretical anticipation and validity of the synthesis. The power consumption for proposed filter is 0.343 mW and for proposed oscillator (with AGC circuit) is 0.346 mW. Moreover, the experimental results using available commercial ICs (AD830 and LM13700) are included and they meet very well with theoretical presumptions.

# Acknowledgement

This work was supported by the King Mongkut's Institute of Technology Ladkrobong (KMITL), National Research Council of Thailand (NRCT), Research described in this paper was financed by Czech Ministry of Education in frame of National Sustainability Program under grant LO1401. For research, infrastructure of the SIX Center was used. Research described in the paper was supported by Czech Science Foundation projects under No. 16-11460Y.

#### References

- Sedra A S & Smith K C, Microelectronic circuits, 6<sup>th</sup> Edn, (Oxford University Press, USA), 2011.

- 2 Psychalinos C, Analog Integr Circuits Signal Process, 67 (2011) 201.

- 3 Jantakun A & Jaikla W, Indian J Pure Appl Phys, 53 (2015) 557.

- 4 Chaichana A, Jantakun A, Kumngern M & Jaikla W, *Indian J Pure Appl* Phys, 53 (2015) 470.

- 5 Yuce E & Minaei S, Int J Circuits Theory Appl, 42 (2014) 659.

- 6 Biolek D, Senani R, Biolkova V & Kolka Z, Radioengineering, 17 (2008) 15.

- 7 Kubanek D, Khateb F, Tsirimokou G & Psychalinos C, Circuits Syst Signal Process, 35 (2016) 2003.

- 8 Herencsar N, Sotner R, Metin B, Koton J & Vrba K, VDDDA New 'voltage differencing' device for analog signal processing, International Conference on Electrical and Electronics Engineering, Bursa, Turkey, 2013.

- 9 Chaichana A, Jaikla W, Suwanjan, P & Tuntrakool S, A new quadrature sinusoidal oscillator for telecommunication system using VDDDAs, International Conference on Intelligent Informatics and Biomedical Sciences (ICIIBMS), 2015.

- Tuntrakool S, Kumngern M & Jaikla W, VDDDAs-based voltage-mode multiphase sinusoidal oscillator, International Conference on Industrial Application Engineering, 2016.

- 11 Koton J, Herencsar N, Vrba K & Metin B, The VDDDA in multifunction filter with mutually independent Q and ω<sub>0</sub> control feature, International Conference on Electrical and Electronics Engineering (ELECO), 2013.

- 12 Koton J, Herencsar N, Vrba K & Metin B, Analog Integr Circuits Signal Process, 81 (2014) 53.

- 13 Sangyaem S, Siripongdee S, Jaikla W & Khateb F, Optik, 128 (2016) 14.

- 14 Siripongdee S & Jaikla W, Single VDDDA-based voltagmode multifunction second order filter for analog signal processing, International Conference on Intelligent Informatics and Biomedical Sciences (ICIIBMS), 2015.

- Herencsar N, Cicekoglu O, Sotner R, Koton J & Vrba K, Analog Integr Circuits Signal Process, 76 (2013) 251.

- 16 http://lgjohn.ecen.ceat.okstate.edu/5263/processparam/t4bk\_ lo\_epi-params.html

- 17 Minaei S & Yuce E, Circuits Syst Signal Process, 29 (2010) 295.

- 18 Chiu W Y, Horng J W, Lee H & Huang C C, IEEE International Symposium on Electronic Design, Test and Applications, Ho Chi Minh City, Vietnam, 2010.

- 19 Horng J W, Analog Integr Circuits Signal Process, 62 (2010) 407.

- 20 Chiu W Y & Horng J W, *Indian J Eng Mater Sci*, 18 (2011) 97.

- 21 Kacar F & Yesil A, Analog Integr Circuits Signal Process, 63 (2010) 137.

- 22 Chiu W Y, Horng J W, Guo Y S & Tseng C Y, DDCCs based voltage-mode one input five outputs biquadratic filter with high input impedance, International Symposium on Integrated Circuits, Singapore, 2011.

- 23 Udorn N, Duangmalai D & Noppakarn A, High input impedance current controlled voltage-mode universal filter using DDCC and OTA, IEEE International Conference on Vehicular Electronics and Safety (ICVES), 2011.

- 24 Kumngern M, Suwanjan P & Dejhan K, Electronically tunable voltage-mode SIMO OTA-C universal biquad filter, Asia-Pacific Conference on Communications (APCC2011), 2011.

- 25 Horng J W, Hou C L, Huang W S & Yang D Y, Circuits Syst, 2 (2011) 60.

- 26 Tangsrirat W & Channumsin O, Radioengineering 20 (2011) 905.

- 27 Channumsin O, Pukkalanun T & Tangsrirat W. Microelectron J, 43 (2012) 555.

- 28 Kumngern M, Suwanjan P & Dejhan K, Int J Electron, 100 (2013) 1118.

- 29 Tangsrirat W, Channumsim O & Pukkalanun T, Microelectron J, 44 (2013) 210.

- 30 Singh, S V, Maheshwari S, Tomar R S & Chauhan D S, Single input four output voltage-mode biquad filter with electronic tuning, International Conference on Multimedia Signal Processing and Communication Technologies, 2013.

- 31 Channumsin O & Tangsrirat W, Microelectron J, 44 (2013) 1084.

- 32 Chen H P, IET Circuits Dev Syst, 8 (2014) 280.

- 33 Mohan J, Chaturvedi B & Maheshwari, S, Adv Electr Eng, (2014) Article ID 514019.

- 34 Ismail M U & Arif B, Single input multi output digitally reconfigurable biquadratic analog filter, International Conference on Systems Informatics, Modelling and Simulation, 2014.

- 35 Chen H P, Voltage-mode multifunction biquadratic filter with one input and six outputs using two ICCIIs, Scientific World J, (2014) Article ID 432570.

- 36 Chen H P, Chiu Y L, Chung C K & Chou C C, Voltage-mode multifunction filter with single input and three outputs based on single plus-type DVCC, International Conference on

- Information Science, Electronics and Electrical Engineering, (2014) 1838-1841.

- 37 Chen H P, Wang S F, Huang W Y & Hsieh M Y, *IEICE Electron Express*, 11 (2014) 20140234.

- 38 Jaikla W, Biolek D, Siripongdee S & Bajer J, Radioengineering, 14(3) (2014) 914.

- 39 Kacar F, Yesil A & Gurkan K, Indian J Pure Appl Phys, 53 (2015) 341.

- 40 Sagbas M, Ayten U E, Koksal M & Herencsar N, Electronically tunable universal biquad using a single active component, International Conference on Telecommunications and Signal Processing (TSP), 2015.

- 41 Yucel F & Yuce E, J Circuits Syst Comput, 24(4) (2015), 1550047.

- 42 Chen H P & Wang S P, AEU Int J Electron Commun, 70 (2016) 491.

- 43 Alaybeyoglu, E & Kuntman, H, *Analog Integr Circuits Signal Process*, 89 (2016) 675.

- 44 Horng J W & Chiu W Y, *Indian J Pure Appl Phys*, 54 (2016) 557.

- 45 Bajer J, Vavra J, Biolek D & Hajek K, Low-distortion current-mode quadrature oscillator for low-voltage low-power applications with non-linear noninertial automatic gain control. (Linkoping, Sweden), 2011