# High-k Dielectric Double Gate Junctionless (DG-JL) MOSFET for Ultra Low Power Applications-Analytical Model

#### **Prashant Kumar**

JC Bose University of Science and Technology

#### Munish Vashishath

JC Bose University of Science and Technology

# Neeraj Gupta ( In neeraj singla 007@gmail.com )

Amity University Amity Education Valley Campus: Amity University - Haryana Campus https://orcid.org/0000-0002-6719-2743

# Rashmi Gupta

Amity University Amity Education Valley Campus: Amity University - Haryana Campus

#### Research Article

Keywords: Junctionless MOSFET, Gate stack, DIBL, SS, SCEs

Posted Date: October 21st, 2021

**DOI:** https://doi.org/10.21203/rs.3.rs-989803/v1

**License:** © (i) This work is licensed under a Creative Commons Attribution 4.0 International License.

Read Full License

**Version of Record:** A version of this preprint was published at Silicon on January 4th, 2022. See the published version at https://doi.org/10.1007/s12633-021-01525-2.

# High-k Dielectric Double Gate Junctionless (DG-JL) MOSFET for Ultra Low Power Applications- Analytical Model

Prashant Kumar<sup>a</sup>, Munish Vashishath<sup>a</sup>, Neeraj Gupta<sup>b\*</sup>, Rashmi Gupta<sup>c</sup>

<sup>a</sup>Department of Electronics & Communication Engineering, J.C. Bose University of Science & Technology, YMCA, Sector 6, Faridabad-121006, India

<sup>b</sup>Department of Electronics & Communication Engineering, Amity University Haryana, Gurugram-122413, India

<sup>c</sup>Department of Computer Science & Engineering, Amity University Haryana, Gurugram-122413, India

neerajsingla007@gmail.com, pk.vlsi@gmail.com

#### **Abstract**

This paper describes the impression of low-k/high-k dielectric on the performance of Double Gate Junction less (DG-JL) MOSFET. An analytical model of the threshold voltage of DG-JLFET has been presented. Poisson's equation is solved using the parabolic approximation to find out the threshold voltage. The effect of high-k on various performance parameters of N-type DG-JLFET is explored. The comparative analysis has been carried out between conventional gate oxide, multi oxide and high-k oxide in terms of Drain Induced Barrier Lowering (DIBL), threshold voltage, figure of merit (I<sub>ON</sub>/I<sub>OFF</sub>) and sub-threshold slope (SS). The high-k oxide has shown superlative performance as compared to others. The results are further analyzed for various device structures. The DG-JLFET with HfO<sub>2</sub> exhibits excellent attainment by mitigating the Short Channel Effects (SCEs). The significant reduction in off current makes the device suitable for ultra-low power applications. There is a 61.9 % and 34.29% improvement in the figure of merit and sub-threshold slope in the proposed device as compared to other devices. The simulation of DG-JLFET is carried out using the Silvaco TCAD tool.

**Keywords:** Junctionless MOSFET, Gate stack, DIBL, SS, SCEs.

#### 1. INTRODUCTION

The MOSFET has been introducing in the field of electronics for more than 50 years. MOSFET is used to make an integrated circuit to act as a switch. Aggressive downscaling of gate oxide leads to more leakage current in the device. The scaling of MOSFET produces new challenges and opportunities for the device engineer. The short channel effects occur at a nanoscale size which mitigates the device performance. Many new device structures have been investigated to reduce the SCEs. Multigate devices have been preferred over single gate MOSFET due to their scalability. The necessity of abrupt p-n junctions between source/drain region and channel put the challenges in doping profile technique. Junctionless design is proposed by Colinge et al. [1] The absence of p-n junction between source/drain and the channel region is due to zero doping concentration gradient implies the presence of same doping in source/channel/drain regions increases effective channel length which reduces the short channel effects in Junctionless MOSFET [2-6].

To improve the performance in DG-JLFET for the parameters such as off current, on current, transconductance, DIBL and threshold voltage, many gate and channel engineering approaches are adopted [7-10]. The gate dielectric materials are required mainly for having good insulating properties and high capacitance value [11-13]. The gate dielectric materials should be able to prevent the diffusion of dopants. It should have good thermal stability and very good interface adhesion with the substrate.

However, the utilization of high-k materials improves the control of the gate and results in the reduction of SCEs along with all the above qualities [14-15]. The Lombardi CVT, Shockley-Read-Hall and Drift-diffusion model is utilized for the mobility, recombination and energy transport during the simulation. The Newton method is used for the numerical solution.

An analytical model of DG-JLFET is presented in Section 2. The numerical solution of DG-JLFET using TCAD is described in Section 3. The comparative analyses of DG-JLFET with SiO<sub>2</sub>, Multi oxide and HfO<sub>2</sub> have been portraits in Section 4.

# 2. ANALYTICAL MODELING

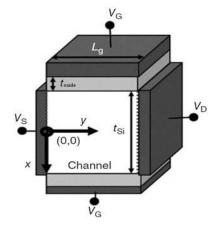

The cross-sectional view of short channel DG-JLFET is shown in Figure 1.

Fig. 1 – Short-channel DG-JLFET.

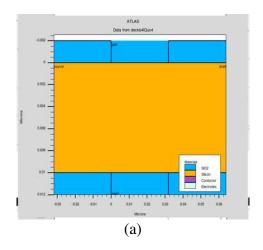

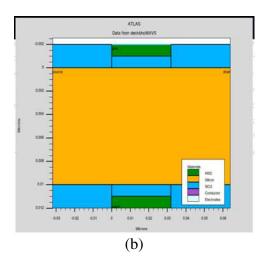

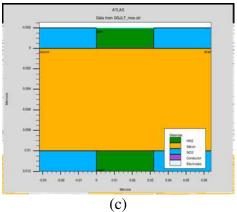

The N-type DG-JLFETs at 32nm with (a) SiO<sub>2</sub> as dielectric material (b) Multi oxide (SiO<sub>2</sub>+HfO<sub>2</sub>) as dielectric material and (c) HfO<sub>2</sub> as dielectric material are shown in Figure 2.

Fig. 2- The N-type DG-JLFETs at 32nm with a dielectric material as (a) SiO<sub>2</sub> (b) Multi oxide (SiO<sub>2</sub>+HfO<sub>2</sub>) and (c) HfO<sub>2</sub>

The Poisson's Equation for the short-channel DGJLFETs is given as.

$$\frac{\partial^2 \Psi(x,y)}{\partial x^2} + \frac{\partial^2 \Psi(x,y)}{\partial y^2} = -\frac{\rho}{\epsilon_{Si}}$$

(1)

The parabolic potential approximation is taken in x-direction [16].

$$\Psi(x,y) = \alpha_0(y) + \alpha_1(y)x + \alpha_2(y)x^2 \tag{2}$$

The value of a2 can be found assuming continuity of electric displacement vector we have

$$-C_{\text{OXIDE}}(V_{\text{G}} - V_{\text{F}} - \Psi_{\text{S,b}}) = -\epsilon_{\text{Si}} \frac{d\Psi(\frac{t_{\text{Si}}}{2}, y)}{dx} = -\epsilon_{\text{Si}} t_{\text{Si}} \alpha_{2}(y)$$

Equation (2) was modified by putting the value of  $\alpha$ 2. (3)

$$\Psi(x,y) = \Psi_0(y) + \frac{c_{OXIDE}}{\epsilon_{Si}t_{Si}} (V_G - V_F - \Psi_S(y)) y^2$$

(4)

The relation between the central potential and the surface potential can be represented as

$$\Psi(\frac{t_{Si}}{2}, y) = \Psi_{S}(y) = \Psi_{0}(y) + \frac{c_{OXIDE}t_{Si}}{4\epsilon_{Si}} (V_{G} - V_{F} - \Psi_{S}(y))$$

(5)

The surface potential can be obtained by simplifying the above equation as

$$\Psi_{S}(y) = \frac{\Psi_{0}(y) + \frac{C_{OXIDE}t_{Si}}{4 \epsilon_{Si}} (V_{G} - V_{F})}{1 + \frac{C_{OXIDE}t_{Si}}{4 \epsilon_{Si}}}$$

By putting the value of  $\Psi$ S from equation (6) to equation (4) we get

$$\Psi(\mathbf{x}, \mathbf{y}) = \Psi_0(\mathbf{y}) + \frac{c_{\text{OXIDE}}}{\epsilon_{\text{Si}} t_{\text{Si}}} \left( V_{\text{G}} - V_{\text{F}} - \frac{\frac{t_{\text{Si}} c_{\text{OXIDE}}}{4\epsilon_{\text{Si}}} (V_{\text{G}} - V_{\text{F}}) + \Psi_0(\mathbf{y})}{1 + \frac{t_{\text{Si}} c_{\text{OXIDE}}}{4\epsilon_{\text{Si}}}} \right) \mathbf{y}^2$$

$$(7)$$

Modifying the equation (1) from the value obtained in equation (7) as

$$\frac{\partial^{2} \Psi_{0}(y)}{\partial y^{2}} - \frac{8C_{OXIDE}}{C_{OXIDE}t_{Si}^{2} + 4\epsilon_{Si}t_{Si}} \left( \Psi_{0}(y) - V_{G} - V_{F} + \frac{qN_{D}t_{Si}}{2C_{OXIDE}} + \frac{qN_{D}t_{Si}^{2}}{8\epsilon_{Si}} \right) = 0$$

(8)

The equation (8) can be simplified by considering  $1/L_2^2 = 8C_{\text{oxide}}/(4\epsilon_{\text{Si}}*t_{\text{Si}} + C_{\text{oxide}}t_{\text{Si}}^2)$ ,  $\xi_0 = V_G - \gamma_2$  and  $\gamma_2 = V_F - [(qN_At_{Si})/2C_{oxide}] - (qN_Dt_{Si}^2)/8\epsilon_{Si}$  Here L<sub>2</sub> is the natural length of DG-JLFET,  $\xi_0$  is long channel central potential. The above equation can be simplified as

$$\frac{\partial^2 \Psi_0(y)}{\partial x^2} - \frac{1}{L_2^2} (\Psi_0(y) - \xi_0) = 0 \tag{9}$$

The solution of this differential equation is as

$$\Psi_0(y) = \xi_0 + a_1 e^{\frac{y}{L_2}} + a_2 e^{-\frac{y}{L_2}} \tag{10}$$

The value of a<sub>1</sub> and a<sub>2</sub> can be obtained by using boundary conditions which state that the surface potential is the potential at the Silicon-silicon oxide interface, the electric field at the center of the DG-JLFET should be zero due to its symmetric nature and the electrical displacement vector is continuous near to the top and bottom gate at the silicon-silicon oxide interface hence we have

$$\Psi_0(y=0) = V_S = 0 \tag{11}$$

$$\Psi_0(y = L_g) = V_D = V_{DS} \tag{12}$$

Hence the value of a<sub>1</sub> and a<sub>2</sub> are

$$a_1 = \beta_1 V_G + \beta_2 \tag{13}$$

$$a_2 = \beta_3 V_G + \beta_4$$

Here the value of  $\beta_1$ ,  $\beta_4$ ,  $\beta_3$  and  $\beta_4$  can be specified as

$$\beta_1 = \frac{e^{-\frac{L_g}{L_2} - 1}}{2\sinh(\frac{L_g}{L_2})} \tag{15}$$

$$\beta_2 = \frac{V_{DS} - \gamma_2 \left(e^{-\frac{L_g}{L_2}} - 1\right)}{2 \sinh\left(\frac{L_g}{L_2}\right)} \tag{16}$$

$$\beta_3 = \frac{\frac{L_g}{L_2}}{2\sinh\left(\frac{L_g}{L_2}\right)} \tag{17}$$

$$\beta_{3} = \frac{\frac{L_{g}}{1 - e^{\frac{L_{g}}{L_{2}}}}}{2 \sinh(\frac{L_{g}}{L_{2}})}$$

$$\beta_{4} = \frac{-V_{DS} + \gamma_{2} \left(e^{-\frac{L_{g}}{L_{2}} - 1}\right)}{2 \sinh(\frac{L_{g}}{L_{2}})}$$

(18)

After calculating the value of a<sub>1</sub> and a<sub>2</sub>, the expression for analytical relation can be solved. The minimum central potential location can be found by differentiating equation (10). The y<sub>min</sub> is the location of the minimum central potential can be found as [17]

$$y_{\min} = \frac{L_2}{2} \ln(\frac{a_2}{a_1}) \tag{19}$$

By putting the value of  $y_{min}$  in equation (10), the minimum central potential is

$$\Psi_0(y_{\min}) = \sqrt{a_1 a_2} + \xi_0 \tag{20}$$

As in JLFET, when a gate voltage is equal to threshold voltage the channel starts to open [18-20]. Hence at threshold voltage the  $\Psi_0(y_{min})=0$ . For short-channel DG-JLFETs threshold voltage is given

$$V_{\text{Th}} = \frac{2(\beta_2\beta_3 + \beta_1\beta_4) + \gamma_2 + \sqrt{(2(\beta_2\beta_3 + \beta_1\beta_4) + \gamma_2)^2 - (1 - 4\beta_1\beta_3)(\gamma_2 - 4\beta_2\beta_4)}}{(1 - 4\beta_1\beta_3)}$$

(21)

The analytical modeling solution for the threshold voltage for short channel DG-JLFETs is given by Equation (21). In the case of long channel DG-JLFETs, the value of  $\beta$  and  $\gamma = 0$ . Hence, the threshold voltage for short channel DG-JLFET tends to ω2, which is equal to the threshold voltage obtained for long channel DG-JLFET. The effect of high-k material on Threshold voltage in DG-JLFET has been analyzed.

#### 3. RESULTS & DISCUSSION

The numerical simulation of DG-JLFET at 32nm technology node is carried out using the Silvaco TCAD tool. The performance of the DG-JLFET device can be further enhanced by introducing high-k dielectric gate materials. The structures considered for numerical simulations are having the gate oxide as SiO<sub>2</sub>, HfO<sub>2</sub> and stack architecture of SiO<sub>2</sub> and HfO<sub>2</sub>. These numerical simulations are done with the intention to analyse the characteristics of the device. The physical thickness of oxide is taken as 2nm (in the case of multi oxide 1nm for SiO<sub>2</sub> and 1nm for HfO<sub>2</sub>). The work function of both gate materials is taken as 5.2ev. The silicon material is uniformly doped with n-type material with the doping density in the range of 1.5e-19 cm<sup>-3</sup>. The permittivity of the HfO<sub>2</sub> is taken as 21 and the permittivity of the SiO<sub>2</sub> is taken as 3.9. The results were obtained using the Atlas device simulator and plotted on Tonyplot [21].

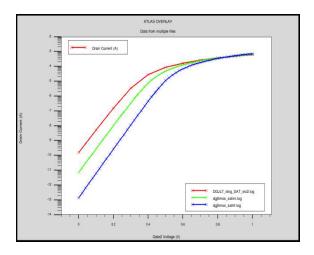

#### 3.1 TRANSFER CHARACTERISTICS

Figure 3 depicts the characteristics of drain current in saturation (high  $V_{DS}$ ) on a logarithmic scale for different oxide materials. The characteristics of  $SiO_2$  as the dielectric for gate oxide are shown with the red line, the green line shows the characteristics of multi-oxide as a dielectric material for the gate oxide and the blue line shows the characteristics of  $HfO_2$  as a dielectric material for the gate oxide. It can be seen from Figure 3 that N-type DG-JLFETs architecture having  $HfO_2$  (oxide permittivity=21) as dielectric material (blue line) has the lowest value of off current. The multi oxide has better off current properties than a device made only with  $SiO_2$ . It can also be observed that the oncurrent of all the devices is of the same order. The sub-threshold slope of the device can also be deduced from Figure 3 and the device having  $HfO_2$  as a gate dielectric has the minimum sub-threshold slope among all compared here.

**Fig. 3-** 32nm N-type DG-JLFETs transfer characteristics with SiO<sub>2</sub>, Multi oxide and HfO<sub>2</sub> as gate dielectric materials.

The detailed comparisons for the different dielectric materials obtained from numerical simulation are given in Table 1.

Table 1: 32nm N-type DG-JLFETs Characteristics with Different Oxide

| Device                            | DG JLT with SiO <sub>2</sub> | DG JLT with<br>Multi oxide | DG JLT with HfO <sub>2</sub> |

|-----------------------------------|------------------------------|----------------------------|------------------------------|

| $V_{tsat}$                        | 0.293049                     | 0.367348                   | 0.456414                     |

| $SS_{sat}$                        | 0.0661216                    | 0.0628691                  | 0.06094                      |

| Ion                               | 0.000613                     | 0.00066889                 | 0.000737                     |

| $I_{ m off}$                      | 1.587 e-10                   | 7.08627 e-12               | 1.4025 e-13                  |

| I <sub>on</sub> /I <sub>off</sub> | 3.86 e+6                     | 9.4 e+7                    | 5.25 e+9                     |

| V <sub>tlin</sub>                 | 0.324705                     | 0.3987                     | 0.474328                     |

| SS <sub>lin</sub>                 | 0.0664907                    | 0.0632479                  | 0.0611267                    |

| DIBL                              | 0.033322                     | 0.03302                    | 0.0188568                    |

#### 3.2 Effect of High-k Material on Various Parameters for N-type DG-JLFETs

Table 1 shows the effects of high-k materials/ high-k materials in stack architecture for N-type DG-SOI MOSFET at 32nm. Some of the variations of characteristics parameters are analyzed as under.

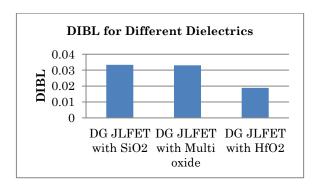

#### 3.2.1 **DIBL**

The Drain Induced Barrier Lowering or DIBL is given by equation (22).

$$DIBL = \frac{V_{Th_{lin}} - V_{Th_{sat}}}{V_{sat} - V_{lin}}$$

(22)

Fig. 4- DIBL for 32nm N-type DG-JLFETs with different dielectric materials.

DG-JLFET with HfO<sub>2</sub> as gate dielectric indicates a lower value of DIBL because of its high value of dielectric constant which in turn enhances the control of gate over the channel and provides low leakage current resulting in lower DIBL.

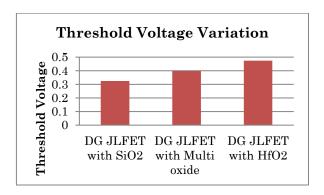

# 3.2.2 Threshold Voltage

In JLTFETs when the gate voltage is increased from zero, the channel starts to open. At a particular voltage, the un-depleted region in the middle of the channel vanishes due to the merging of the depleted region; this voltage is called threshold voltage for JLTFETs. It has been observed that at the threshold

voltage the inversion layer carrier density is equal to the bulk carrier concentration. The threshold voltage can be represented by equation (21). Figure 5 depicts the threshold voltage variation for the different dielectric. The percentage enhancement in threshold voltage is 31.54 % for DG-JLFET with HfO<sub>2</sub> compared to DG-JLFET with SiO<sub>2</sub> and 15.94% compared to DG-JLFET with Multi oxide. The device with more value of threshold voltage will produce a low leakage current and will be useful for low power applications.

**Fig. 5-** Threshold voltage variation with different dielectrics.

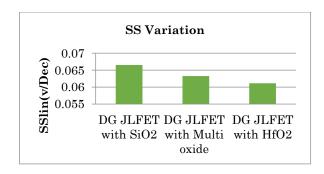

# 3.2.3 Sub-threshold Slope

The sub-threshold slope (SS) is a significant design parameter related to MOSFET, it is usually described how fast a device can turn off from the on-state. The SS can be calculated as given by equation (23)

$$SS = \left(\frac{kT}{q}\right) \ln_{10} \left(1 + \left(\frac{C_D}{C_{\text{oxide}}}\right)\right) \tag{23}$$

SS depends on the first term only and has a value of 60 mV/decade [22]. The effect of high- k materials on the sub-threshold slope of the 32nm DG-JLFETs is shown in Figure 6. The percentage improvement in SS is 8.06 % for DG-JLFET with HfO<sub>2</sub> compared to DG-JLFET with SiO<sub>2</sub> and 3.35% compared to DG-JLFET with Multi oxide. The value of SS is very low points out to a diminution in SCEs.

**Fig. 6-** Sub-threshold slope variation with different dielectrics.

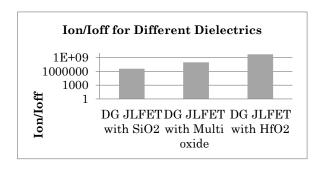

#### 3.2.4 Ion/Ioff Ratio

The I<sub>ON</sub>/I<sub>OFF</sub> ratio is also known as the figure of merit. I<sub>ON</sub> means the current driving capability of the device and I<sub>OFF</sub> contribute to the power dissipation. The variation of I<sub>ON</sub>/I<sub>OFF</sub> with different dielectric materials for 32nm N-type DG-JLFETs is shown in Figure 7. Figure 7 depicts DG-JLFETs with SiO<sub>2</sub>

dielectric have a smaller value of I<sub>ON</sub>/I<sub>OFF</sub> ratio as compared to DG-JLFETs with high-k dielectric materials which can be attributed to the fact that strong depletion of a channel occurs with higher barrier potential in high-k devices [23].

Fig. 7- Variation of I<sub>ON</sub>/I<sub>OFF</sub> for DG-JLFETs with different dielectric materials

The high-K dielectric mitigates the leakage current in MOSFET. The DG-JLFETs provide better electrostatic control of the gate on the channel. This will enhance the on-current of the device. So overall, it will increase the I<sub>ON</sub>/I<sub>OFF</sub> value as compared to low dielectric constant materials.

#### 4. COMPARATIVE ANALYSIS

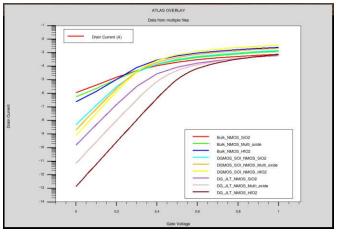

The comparisons of transfer characteristics for all the structures of MOSFET viz. Bulk MOSFET, DG-SOI MOSFET and DG-JLTFET for various oxide viz. SiO<sub>2</sub>, Multi oxide and HfO<sub>2</sub> are shown in Figure 8.

Fig. 8- Transfer characteristics for all the structures for various oxides

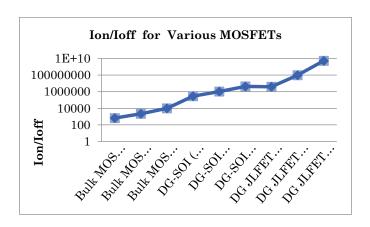

Comparison of simulation results in Figure 8 was plotted on the Tonyplot tool of Silvaco. It can be seen from Figure 8 that the MOSFET made using DG-JLTs will give minimum off current and best slope among all compared for about the same order of on current. The DG-JLT MOSFET having gate dielectric is showing the best characteristics for the off current. Hence, the circuit made with DG-JLT MOSFET is expected to give minimum power dissipation. Figure 9 depicts the I<sub>on</sub>/I<sub>off</sub> ratio for various structures having different oxides as a gate dielectric.

Fig. 9- I<sub>on</sub>/I<sub>off</sub> ratio for all the MOS structures

It can be seen from Figure 9 that the MOSFET made with DG-JLT having HfO<sub>2</sub> as dielectric giving a maximum on to off current ratio. A 61.9% enhancement in I<sub>on</sub>/I<sub>off</sub> ratio is envisaged in DG-JLT with HfO<sub>2</sub> in contrast to conventional junction less DG-MOSFET [24].

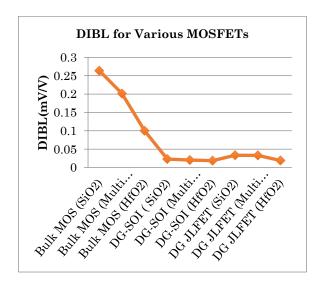

Figure 10 depicts the DIBL for various structures having different oxides as a gate dielectric. MOS structure made with DG-JLT and DG-SOI having almost the same minimum DIBL among the compared structures. DG-JLT reveals significant mitigation in DIBL as compared to DIBL reported as 0.4965 V by Mohd. Bavir [25] and 0.24 V by P. Wang [26]. This makes the device suitable for ultralow-power range applications. The results are validated by comparing with existing results.

Fig. 10- DIBL for various MOSFETs structures

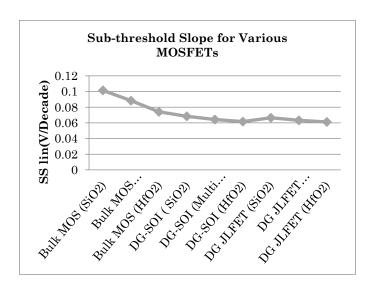

Figure 11 depicts the sub-threshold slope for various structures having different oxides as a gate dielectric. MOS structure made with DG-JLT and DG-SOI having almost the same minimum sub-threshold slope close to perfect (60mv/Decade) among the compared structures. DG-JLT depicts a significant improvement of 7.4 % in SS as compared to SS reported by Mohd. Bavir [25] and 34.29 % by P Wang [26]. It is a clear indication of improvement in the short channel behavior of the device.

Fig. 11- Sub-threshold slope for various MOSFETs structures

#### 5. CONCLUSION

The analytical modeling for threshold voltage is developed using parabolic approximation in this paper. The numerical simulation of JLFET is also carried out using TCAD Silvaco. The simulation includes the application of SiO<sub>2</sub>, HfO<sub>2</sub> and multi-oxide (SiO<sub>2</sub>+HfO<sub>2</sub>) as gate dielectric to analyze the characteristics of JLTs. The behavior of DG-JLT was found to be very interesting as compared to bulk and DG-SOI MOSFET. In bulk MOSFET with SiO<sub>2</sub>, I<sub>on</sub>/I<sub>off</sub> ratio is 661.86. This ratio increases with an increase in dielectric constant due to the reduction in leakage current. It is scrutinized that the substitution of SiO<sub>2</sub> with high-k dielectric materials in DG-JLT is beneficial for future devices. Moreover, the consequences of SiO<sub>2</sub>, HfO<sub>2</sub> and multi-oxide on DG-JLT short channel parameters are studied. HfO<sub>2</sub> as gate oxide reveals a lower value of DIBL and SS as compared to other gate dielectrics on the application of high drain bias. Further, a comparison has been carried out between bulk, DG-SOI and DG-JLT MOSFET to evaluate the performance of the devices with SiO<sub>2</sub>, HfO<sub>2</sub> and multi-oxide. DG-JLT with HfO<sub>2</sub> exhibits excellent immunity against SCEs. The leakage current is a very crucial factor in power dissipation. The leakage current is very less for DG-JLT with HfO<sub>2</sub> that makes it a more appropriate device for ultra-low power applications.

#### Acknowledgment

Not applicable

#### **Declarations**

#### **Funding**

No funding was received for conducting this study.

#### Conflicts of interest/Competing interests

The authors declare that there is no conflict of interest regarding the content of this article.

## Availability of data and material

The datasets generated and analyzed during the current study are not publicly available but may be available from the corresponding author on reasonable request.

#### **Code availability**

The code used during this work is not available.

#### **Authors' contributions**

The idea of the research was conceptualized by Prashant Kumar and Neeraj Gupta carried out the analytical modeling and simulation of Junctionless MOSFET. The formal analysis and resources for the research were arranged by Munish Vashisht and Rashmi Gupta. Prashant Kumar also prepared the original draft of the paper and Neeraj Gupta did the review, proofreading and necessary editing in the article.

### **Ethics approval**

Not applicable

# **Consent to participate**

All authors are agreed.

#### **Consent for publication**

There are no details on an individual reported in the manuscript.

#### REFERENCES

- [1] Colinge J P (2012) Junctionless transistors. IEEE International Meeting for Future of Electron Devices, Kansai, Osaka, 2012, pp. 1-2.

- [2] Baruah RK, Roy PP (2014) A Dual-Material Gate Junctionless Transistor with High-k Spacer for Enhanced Analog Performance. IEEE Trans. Electron Devices 61(1):123-128. https://doi.org/10.1109/TED.2013.2292852

- [3] Ganesh A, Goel K, Mayall JS, Rewari S (2021) Subthreshold Analytical Model of Asymmetric Gate Stack Triple Metal Gate all Around MOSFET (AGSTMGAAFET) for Improved Analog Applications. Silicon. https://doi.org/10.1007/s12633-021-01173-6

- [4] Goel A, Rewari S, Verma S, Gupta RS (2019) GaN-based Dual-Metal Gate Stack Engineered Junctionless-Surrounding-Gate (DMSEJSG) MOSFET for High Power Applications. IEEE 16th India Council International Conference (INDICON):1-4. https://doi.org/10.1109/INDI-CON47234.2019.9030261.

- [5] Goel A, Rewari S, Verma S, Deswal SS, Gupta RS (2021) Dielectric Modulated Junctionless Biotube FET (DM-JL-BT-FET) Bio-Sensor. IEEE Sensors Journal 21(5): 16731-16743. https://doi.org/10.1109/JSEN.2021.3077540.

- [6] Xie Q, Wang Z, Taur Y (2017) Analysis of Short-Channel Effects in Junctionless DG MOSFET. IEEE Trans. Electron Devices 64(8): 3511-3514. https://doi.org/10.1109/TED.2017.2716969

- [7] Sharma A, Jain A, Pratap Y, Gupta RS (2016) Effect of High-K and vacuum dielectrics as gate stack on junction less cylindrical surrounding gate MOSFET. Solid-State Electron 123:26–32. https://doi.org/10.1016/j.sse.2016.05.016

- [8] Goel A, Rewari S, Verma S, Gupta RS (2021) Modeling of shallow extension engineered dual metal surrounding gate (SEE-DM-SG) MOSFET gate-induced drain leakage (GIDL). Indian J Physics 95(2): 299-308. https://doi.org/10.1007/s12648-020-01704-8.

- [9] Nandi S, Srivastava S, Rewari S (2019) Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high-frequency application. Microsystem Technologies. https://doi.org/10.1007/s00542-019-04577-y

- [10] Goel A, Rewari S, Verma S, Gupta RS (2018) Dielectric Modulated Triple Metal Gate All Around MOSFET (TMGAA)for DNA Bio-Molecule Detection. IEEE Electron Devices Kolkata Conference (EDKCON):337-340. https://doi.org/10.1109/EDKCON.2018.8770406.

- [11] Gupta N, Patel JB, Raghav AK (2015) A Study of Conventional and Junctionless MOSFET Using TCAD Simulations. IEEE Conference on Advanced Computing & Communication Technologies, Haryana, pp. 53-56. https://doi.org/10.1109/ACCT.2015.51

- [12] Goel A, Rewari S, Verma S, Gupta RS (2020) Novel dual-metal Junctionless nanotube field-effect transistors for improved analog and low-noise applications. J Electron Mater 50:108–119. https://doi.org/10.1007/s11664-020-08541-9

- [13] Goel A, Rewari S, Verma S, Gupta RS (2019) High-K spacer dual metal gate stack Underlap Junctionless gate all around (HKDMGS-JGAA) MOSFET for high-frequency applications. Microsyst Technol 26:1697–1705. https://doi.org/10.1007/s00542-019-04715-6

- [14] Rewari S (2020) Core-Shell Nanowire Junctionless Accumulation Mode Field-Effect Transistor (CSN-JAM-FET) for High-Frequency Applications Analytical Study. Silicon. https://doi.org/10.1007/s12633-020-00744-3.

- [15] Goel A, Rewari S, Verma S, Gupta RS (2019) Shallow Extension Engineered Dual Material Surrounding Gate (SEE-DM-SG) MOSFET for improved gate leakages, analysis of circuit and noise performance. AEU Int J Electron Commun, 111:1-9. https://doi.org/10.1016/j.aeue.2019.152924

- [16] Rewari S, Haldar S, Nath V, Deswal SS, Gupta RS (2016) Numerical modeling of the subthreshold region of junctionless double surrounding gate MOSFET (JLDSG). Superlattice Microstruct 90:8–19. https://doi.org/10.1016/j.spmi. 2015.11.026

- [17] Trevisoli RD, Doria RT, Souza MD, Das S, Ferain I, Pavanello MA (2012) Surface-Potential-Based Drain Current Analytical Model for Triple-Gate Junction-less Nanowire Transistors. IEEE Tran. Electron Devices 59(12):3510-3518. https://doi.org/10.1109/TED.2012.2219055

- [18] Trevisoli RD, Doria RT, Souza MD, Pavanello MA (2013) A physically-based threshold voltage definition, extraction, and analytical model for junction-less nanowire transistors. Solid-State Electronics 90:12–17. https://doi.org/10.1016/j.sse.2013.02.059

- [19] Goel A, Rewari S, Verma S, Gupta RS (2019) Temperature-dependent gate-induced drain leakages assessment of dual-metal nanowire field-effect transistor—analytical model. IEEE Trans Electron Devices 66(5):2437–2445. https://doi.org/10.1109/TED.2019.2898444

- [20] Goel A, Rewari S, Verma S, Gupta RS (2020) Physics-based analytic modeling and simulation of gate-induced drain leakage and linearity assessment in dual-metal junctionless accumulation nanotube FET (DM-JAM-TFET). Applied Physics A 126:1-14. https://doi. org/10.1007/s00339-020-03520-7

- [21] (2020) ATLAS: 3D device simulator, SILVACO International

- [22] Kumar P, Vashisht M., Gupta N, Gupta R (2021) Subthreshold Current Modeling of Stacked Dielectric Triple Material Cylindrical Gate All Around (SD-TM-CGAA) Junctionless MOSFET for Low Power Applications. Silicon 13(9):1-9. https://doi.org/10.1007/s12633-021-01399-4

- [23] Darwin S, Samuel TA (2019) A holistic approach on Junctionless dual material double gate (DMDG) MOSFET with high k gate stack for low power digital applications. Silicon 12:393-403. https://doi.org/10.1007/s12633-019-00128-2

- [24] Ambika, Dhiman G (2019) Investigation of Junction-less Double Gate MOSFET With High-k Gate-oxide and Metal Gate Layers. Int J Innovative Tech Exploring Engineering 8(6S3):289-292.

- [25] Mohammad Bavir, Abdollah Abbasi and Ali Asghar Orouji, "A Simulation Study of Junctionless Double-Gate Metal-Oxide-Semiconductor Field-Effect Transistor with Symmetrical Side Gates", Silicon, pp. 1-10, 2019

- [26] Wang P, Zhuang Y, Li C, Liu Y, Jiang Z (2015) Potential-based threshold voltage and subthreshold swing models for junctionless double-gate metal-oxide-semiconductor field-effect transistor with dual-material gate. Int J Numerical Model Electron Networks Devices Fields 29(2):230–242. https://doi.org/10.1002/jnm.2067